# Evaluation Methodology for DC Line Fault Clearance Techniques in a Point-to-Point VSC-HVDC Transmission System

By:

#### Zhibo Wang

A Thesis submitted to the Faculty of Graduate Studies of

The University of Manitoba

in partial fulfillment of the requirements for the degree of:

#### **Master of Science**

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg, Manitoba

© Copyright by Zhibo Wang, 2022

## Acknowledgements

I would like to express my sincere appreciation to Prof. Shaahin Filizadeh, my academic advisor, and Dr. David Jacobson, my technical advisor, for their patience and support throughout my thesis research. Your encouragement, guidance, inspiration, and support all contributed to this thesis's continuous improvement. Prof. Filizadeh taught me undergraduate and graduate courses that laid the groundwork for my career in electrical machines and power electronics. It is both a pleasure and an honor for me to be a master's student under your supervision.

Many thanks to Dr. David Jacobson of Manitoba Hydro for his technical mentorship at work and as technical advisor during my thesis research. This thesis was made possible by your insightful idea, which prompted my technical investigation into DC fault clearance in VSC HVDC.

I am grateful to my Manitoba Hydro supervisor, Mr. Kelvin Kent, for guiding and supervising me throughout my career in HVDC and throughout my life.

Additionally, I would like to thank Dr. Hui Ding and Mr. Don Menzies for their discussion and recommendations regarding the development of my PSCAD models.

I would like to express my heartfelt appreciation to Ms. Amy Dario for her continuous assistance throughout my research.

Finally, I would like to thank Mr. Pei Wang, who is an inspiring mentor, an amazing leader, and a loving big brother. You were loved by all and will be missed by many!

## **Dedication**

To

My family for their support:

my dear mother, my great father,

my lovely wife,

and our four year old son

Henry,

## **Abstract**

This thesis examines and compares various DC fault clearance methods that can be used for the VSC-HVDC transmission system, specifically in the context of a point-to-point VSC HVDC transmission system. The newest conceptual research, prototype development, and real implementations are described in depth through the literature review. An analytical evaluation methodology is developed to compare the performance, capability, losses, and cost of different DC fault clearing techniques. Finally, a comparative analysis is conducted to evaluate the DC fault clearing solution using a full-bridge modular multilevel converter and a half-bridge modular multilevel converter with DC breakers using PSCAD/EMTDC software.

## **Table of Contents**

| Acknowledge    | ements                                        | i   |

|----------------|-----------------------------------------------|-----|

| Dedication     |                                               | iii |

| Abstract       |                                               | iv  |

| Table of Cont  | tents                                         | . v |

| List of Figure | es                                            | ix  |

| List of Tables | S                                             | iii |

| List of Symbo  | olsx                                          | ίv  |

| Copyright Dis  | sclaimer                                      | 16  |

| Chapter 1.     | Introduction                                  | . 1 |

| 1.1. VSC       | C-HVDC Overview                               | . 1 |

| 1.1.1.         | Technology                                    | . 1 |

| 1.1.2.         | VSC Converter Topology                        | . 3 |

| 1.1.3.         | System Configurations                         | . 7 |

| 1.1.1.         | Converter Configurations                      | . 9 |

| 1.2. DC        | Line Fault for Point-to-Point VSC-HVDC System | 11  |

| 1.3. Rese      | earch Objectives                              | 14  |

| 1.4.    | Motivations for Research                                    | 15 |

|---------|-------------------------------------------------------------|----|

| 1.5.    | Summary and Thesis Organization                             | 16 |

| Chapter | 2. DC Faults in VSC-HVDC Systems                            | 18 |

| 2.1.    | Introduction                                                | 18 |

| 2.2.    | Pole-to-Ground Faults                                       | 19 |

| 2.3.    | Pole-to-Pole Faults                                         | 22 |

| 2.4.    | Summary                                                     | 24 |

| Chapter | 3. MMC Submodule Designs for DC Fault Clearance             | 25 |

| 3.1.    | Introduction                                                | 25 |

| 3.2.    | Full-Bridge Submodule design                                | 25 |

| 3.3.    | Clamp-Double Submodule Design                               | 27 |

| 3.4.    | Summary                                                     | 28 |

| Chapter | r 4. HVDC Breakers                                          | 30 |

| 4.1.    | Introduction                                                | 30 |

| 4.2.    | Standard Fault Current Interruption Process and Definitions | 32 |

| 4.3.    | Mechanical Circuit Breaker                                  | 35 |

| 4.3     | 3.1. Passive Oscillation Mechanical Circuit Breaker         | 35 |

| 4.3     | 3.2. Active Current Injection Circuit Breaker               | 38 |

| 4.4.    | Power-Electronic Circuit Breaker                            | 50 |

| 4.5.    | Proactive Mechanical and Power Electronic Hybrid CB         | 51 |

| 4.5.1.     | Operating Principle and Basic Functionality           | 52  |

|------------|-------------------------------------------------------|-----|

| 4.5.2.     | Example Prototype Designs                             | 55  |

| 4.6. Sum   | mary                                                  | 66  |

| 4.6.1.     | Short Circuit Current Interruption Capability         | 68  |

| 4.6.2.     | Internal Current Commutation Time                     | 68  |

| 4.6.3.     | Calculated Rate of Rise of Fault Current              | 69  |

| 4.6.4.     | On-State Losses                                       | 70  |

| 4.6.5.     | Total Cost                                            | 70  |

| Chapter 5. | Evaluation Methodology and Case Study                 | 72  |

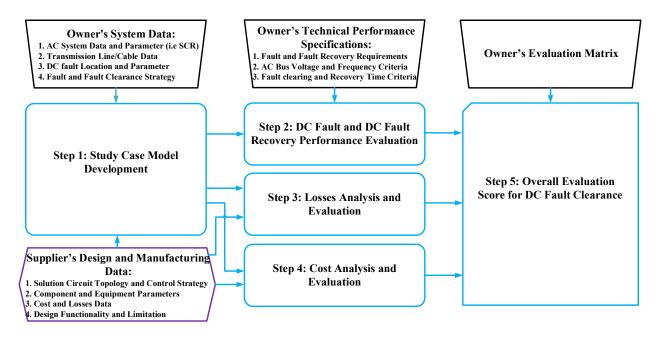

| 5.1. DC    | Fault Clearance Evaluation Methodology                | 72  |

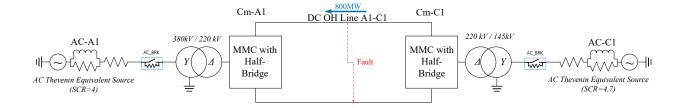

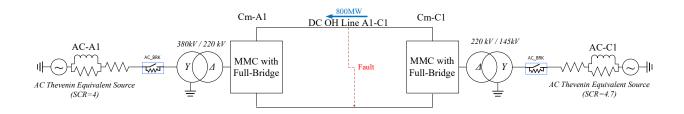

| 5.2. Desc  | cription of the System Models                         | 76  |

| 5.3. DC 1  | Breaker Model Description                             | 80  |

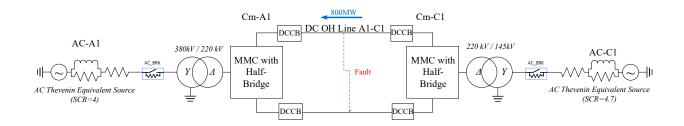

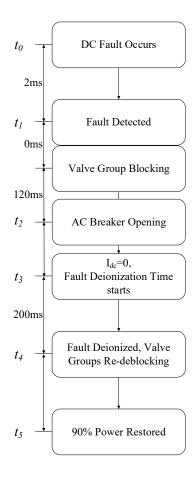

| 5.4. DC 1  | Fault Clearance Strategy                              | 81  |

| 5.5. Sim   | ulation Case Study Results and Evaluation             | 85  |

| 5.5.1.     | Half-Bridge Base Case Model                           | 85  |

| 5.5.2.     | Solution with Full-Bridge MMC                         | 88  |

| 5.5.3.     | Solution with Half-bridge MMC and DC Breakers         | 91  |

| 5.5.4.     | DC Fault and DC Fault Recovery Performance Evaluation | 96  |

| 5.5.5.     | Analysis of Losses and Evaluation                     | 98  |

| 5.5.6.     | Cost Analysis and Evaluation                          | 101 |

| 5.6.      | Summary                                                            | 101 |

|-----------|--------------------------------------------------------------------|-----|

| Chapter   | 6. Contributions, Conclusions, and Recommendations for Future Work | 103 |

| 6.1.      | Contributions                                                      | 103 |

| 6.2.      | Conclusions                                                        | 103 |

| 6.3.      | Suggestions for Future Research                                    | 105 |

| Reference | ces                                                                | 106 |

## List of Figures

| Figure 1-1: VSC Valve Circuit Schematic with IGBT and FWD                                         |

|---------------------------------------------------------------------------------------------------|

| Figure 1-2: VSC Converter Technologies: a) VSC-HVDC 2 Level Converter Station; b) VSC-            |

| HVDC 3 Level Converter Station [2]                                                                |

| Figure 1-3: Main Circuit Principle Diagram of MMC with Half-Bridge and Full Bridge Sub-           |

| Modules [2] [6]                                                                                   |

| Figure 1-4: Sample Point-to-Point and Multi-Terminal Configurations:                              |

| Figure 1-5: Converter Valve Configurations: (a) Asymmetrical Monopole Configuration; (b)          |

| Symmetrical Monopole Configuration; (c) Bipolar Configuration. [1] [2] [13]                       |

| Figure 1-6: Conceptual VSC diagram for Current Flow during DC Faults                              |

| Figure 1-7: System Layout for DC Fault Clearance Techniques                                       |

| Figure 1-8: Manitoba Hydro Nelson River Three-Bipole HVDC system [22]                             |

| Figure 2-1: Equivalent Circuit Diagram of VSC DC Pole-to-Ground Fault [24] [25]                   |

| Figure 2-2: Equivalent Circuit of DC Capacitor Discharging for Pole-to-Ground Faults [24] 20      |

| Figure 2-3: Equivalent Circuit of AC Network Feeding Stage for Pole-to-Ground Faults [24] [25]    |

| 21                                                                                                |

| Figure 2-4: Equivalent Circuit Diagram of VSC DC Pole-to-Pole Fault [25] [26]                     |

| Figure 2-5: Equivalent Circuit of DC Capacitor Discharging for Pole-to-Pole Faults [25] [26] . 23 |

| Figure 2-6: Equivalent Circuit Diagram of Full-Bridge VSC for Pole-to-Pole Fault [13] [28] 24     |

| Figure 3-1: Full-bridge Submodule and Operation States                                            |

| Figure 3-2: Clamp-Double Submodule of an MMC Valve                                                |

| Figure 4-1: Conceptual Topology of a DCCB                                                         |

| Figure 4-2: Schematic of a Fault Current Interruption Process [16]                                   |

|------------------------------------------------------------------------------------------------------|

| Figure 4-3: Passive Oscillation DC Breaker Operating Principle [16] [42]                             |

| Figure 4-4: Schematic of Passive Oscillation CB Prototype 1 [44]                                     |

| Figure 4-5: Schematic of Passive Oscillation CB Prototype 2 [45]                                     |

| Figure 4-6: Active Injection DC Breaker Operating Principle [38]                                     |

| Figure 4-7: DC Current Interruption Process by Active Injection CB [16]                              |

| Figure 4-8: Schematic Circuit Diagram of an Active Current Injection DC Circuit Breaker              |

| Prototype designed by Mitsubishi Electric [47]                                                       |

| Figure 4-9: Schematic Circuit Diagram of HVDC Circuit Breaker with Double Breaks and its             |

| Testing Results at 145kV 16kA Conditions [47]                                                        |

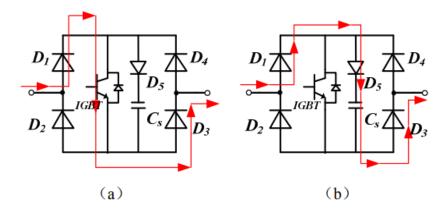

| Figure 4-10: (a) Detail layout of Current Injection DC Circuit Breaker Designed for Nan'ao Multi-    |

| Terminal HVDC system; (b) Photo of a Design Prototype [48]                                           |

| Figure 4-11: (a) Monopole Layout of a Proposed Current Injection CB (b) Bipolar Layout of the        |

| Proposed Current Injection CB [50]                                                                   |

| Figure 4-12: Detailed Layout of the Proposed Current Injection DC CB [50]                            |

| Figure 4-13: (a) Simulation Results Switching Current (b) Simulation Results for Switch Voltage      |

| [50]                                                                                                 |

| Figure 4-14: Basic Layout of a Power Electronic Circuit Breaker                                      |

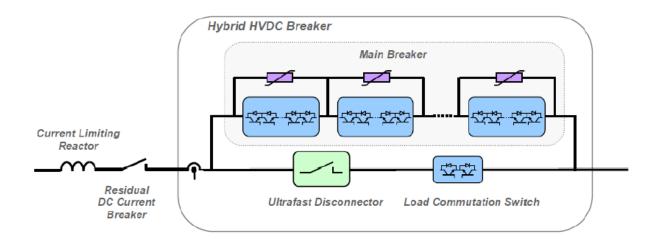

| Figure 4-15: Basic Layout of a Proactive Mechanical and Power Electronic Hybrid CB 52                |

| Figure 4-16: Overall Fault Current Interruption Process for PMPH CB                                  |

| Figure 4-17: Basic Circuit Diagram of the MPH CB [59]                                                |

| Figure 4-18: a) Schematic Block Diagram for PMPH CB in Zhoushan HVDC System; b)                      |

| Operation Principle top-left: regular operation; top-right: current transfer into commutation branch |

| bottom-left: energy dissipation in energy absorption branch; c) Overload Capacity wi  | th Different  |

|---------------------------------------------------------------------------------------|---------------|

| Current Levels [60]                                                                   | 57            |

| Figure 4-19: Schematic Diagram of PMPH CB in Zhangbei HVDC System and                 | the Power     |

| Electronic Switch Module Topologies [61]                                              | 58            |

| Figure 4-20: Operation Principle of Diode Based Full-bridge Module: (a) Conducting    | ng State; (b) |

| Blocking State [61]                                                                   | 59            |

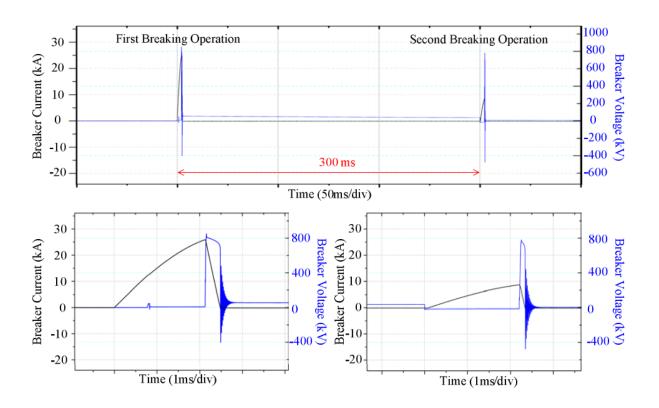

| Figure 4-21: Tests Results of Reclosing Operations with Current (black) and Voltage ( | blue) across  |

| the CB [61]                                                                           | 60            |

| Figure 4-22: Schematic Diagram of ABB's PMPH HVDC CB [64]                             | 61            |

| Figure 4-23: Tests Results of Current Interruption Showing Current (Red) and Voltage  | ge (Blue) of  |

| ABB PMPH CB [64]                                                                      | 62            |

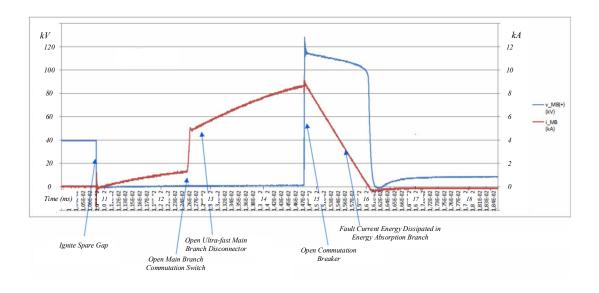

| Figure 4-24: Conceptual Schematic Design of GE Alstom's PMPH HVDC CB [66]             | 63            |

| Figure 4-25: Tests Results of Current Interruption Showing Prospective (Green) and    | Interrupted   |

| Current (Blue), Current Through the Surge Arrester (Red) and Voltage Across the DC    | CB (Purple)   |

| of GE Alstom PMPH CB [66]                                                             | 65            |

| Figure 5-1: Evaluation Methodology Flowchart for DC Fault Clearing Solutions          | 73            |

| Figure 5-2: Point-to-Point Monopolar HVDC with Different DC Faults Clearance Tec      | chniques: (a) |

| With Half-Bridge MMC and AC Circuit Breaker for DC Fault Clearance; (b) With          | Full-Bridge   |

| MMC; (c) With Half-Bridge MMC and DC Circuit Breakers                                 | 79            |

| Figure 5-3: DC Faults Clearance Strategy Flowchart for Base Case Model                | 82            |

| Figure 5-4: DC Faults Clearance Strategy Flowcharts (a) For Full-Bridge Solution      | (b)For        |

| Half-Bridge with DC Breakers Solution                                                 | 83            |

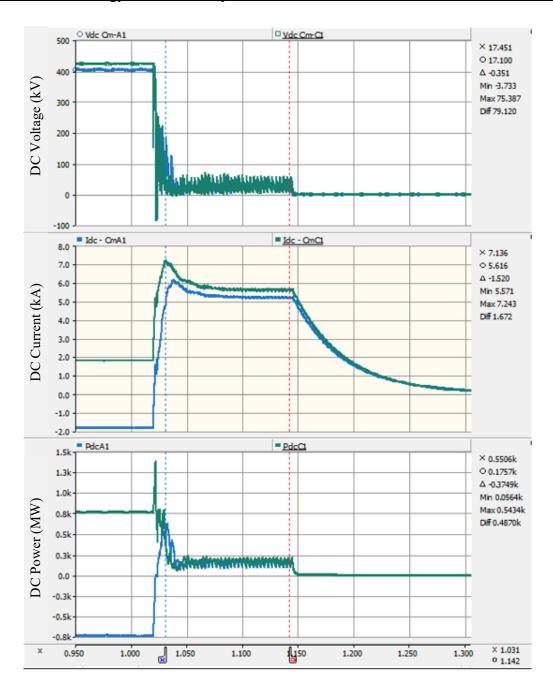

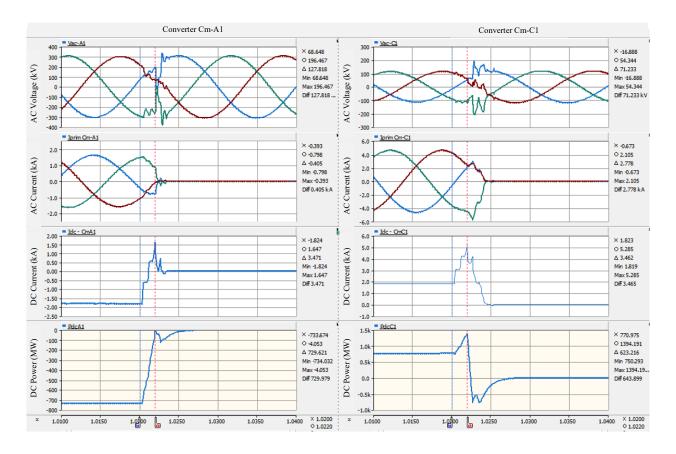

| Figure 5-5: Dynamic DC System Response of the Base Case Model                         | 86            |

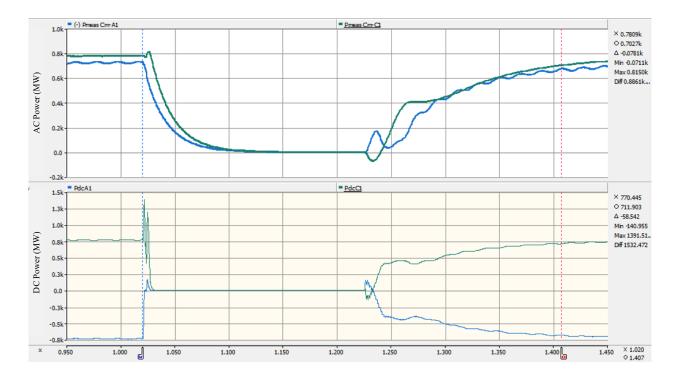

| Figure 5-6: Dynamic ac System Response of Base Case Model                                  | 7 |

|--------------------------------------------------------------------------------------------|---|

| Figure 5-7: System Recovering after DC Fault for Base Case Model                           | 7 |

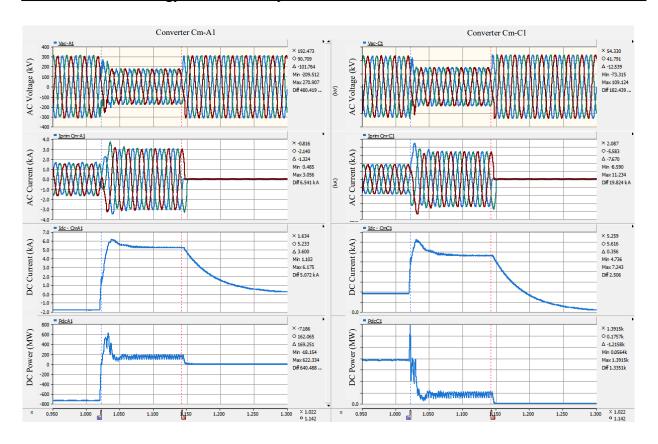

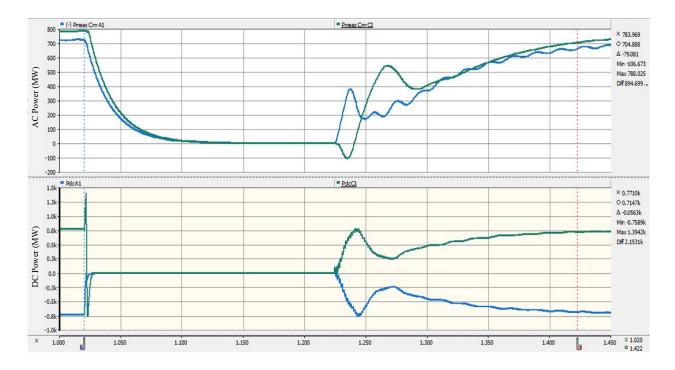

| Figure 5-8: Dynamic DC System Response of the Full-Bridge MMC Solution                     | 9 |

| Figure 5-9: Dynamic ac System Response of the Full-Bridge MMC Solution                     | 0 |

| Figure 5-10: System Recovering after DC Fault for Full-Bridge MMC Solution                 | 1 |

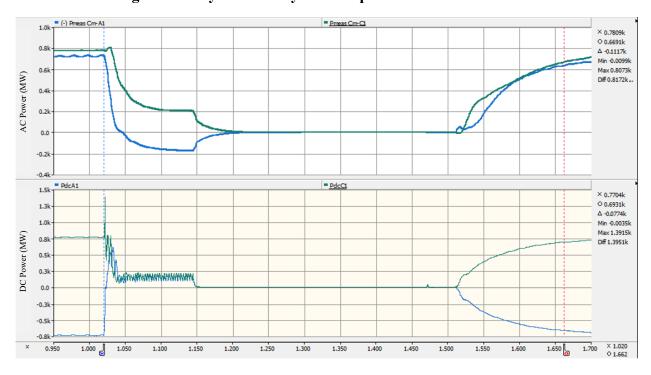

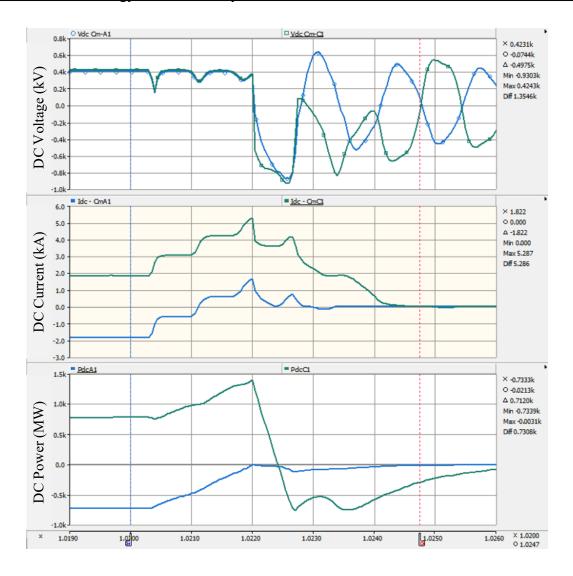

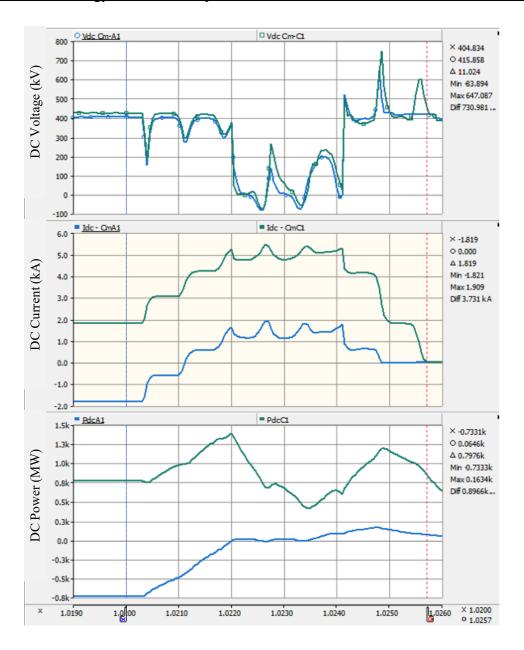

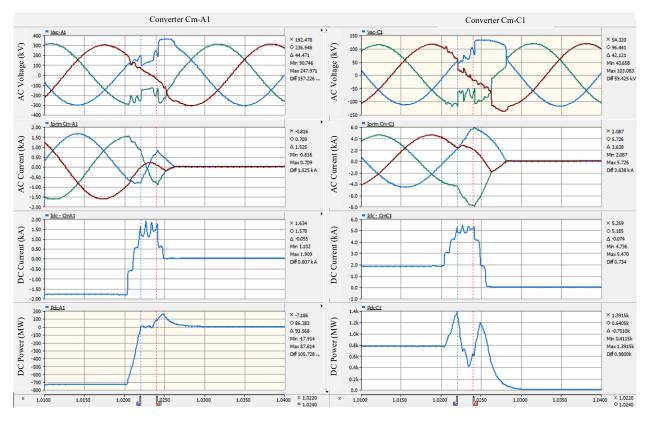

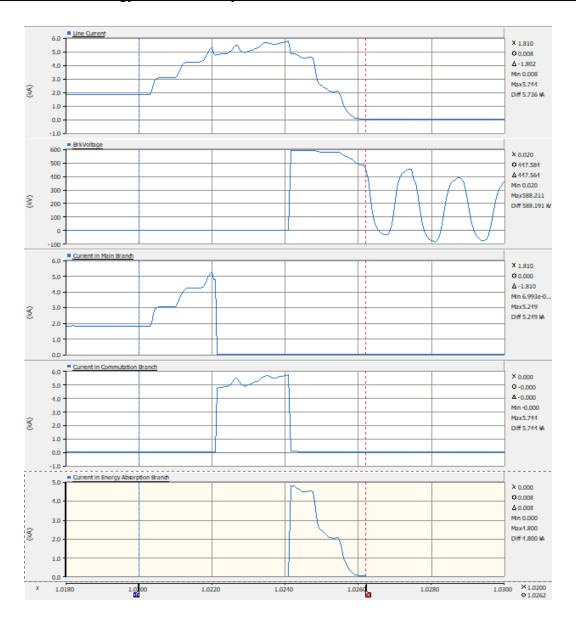

| Figure 5-11: Dynamic DC System Response of the Half-Bridge MMC with DC Breaker 92          | 2 |

| Figure 5-12: Dynamic ac System Response of the Half-Bridge MMC with DC Breaker Solution    | n |

| 92                                                                                         | 3 |

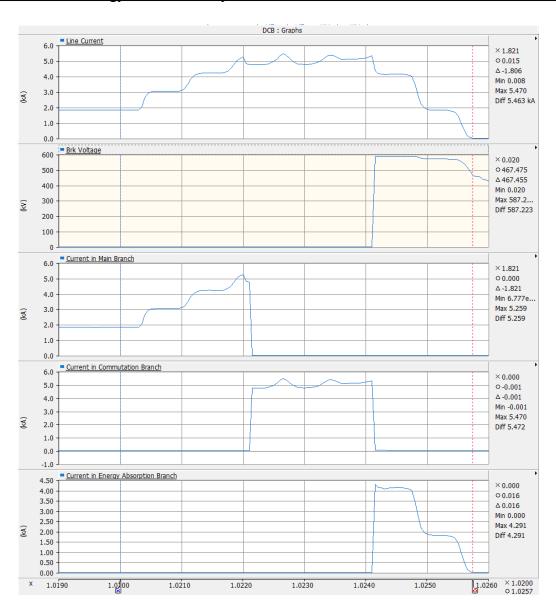

| Figure 5-13: DC Breaker Current and Voltage Waveforms                                      | 4 |

| Figure 5-14: System Recovering after DC Fault for Half-Bridge MMC with DC Breaker Solution | n |

| 9                                                                                          | 5 |

| Figure 5-15: DC Breaker Current and Voltage Waveforms (Cm-C1 SCR set to 47)                | 6 |

## List of Tables

| Table 3-1: Switching States of Clamp-Double Submodule                         | 28  |

|-------------------------------------------------------------------------------|-----|

| Table 3-2: Comparison of Submodule Designs                                    | 29  |

| Table 4-1: Fault Current Interruption Process Definitions [16]                | 34  |

| Table 4-2: Specification Summary of Passive Oscillation CB Example Prototypes | 38  |

| Table 4-3: Specification Summary of Active Current Injection Circuit Breakers | 49  |

| Table 4-4: Specification Summary of PMPH HVDC Circuit Breakers                | 66  |

| Table 4-5: DC Circuit Breaker Prototypes Performance Comparison Summary       | 67  |

| Table 5-1: DC Fault and DC Fault Recovery Performance Evaluation Criteria     | 76  |

| Table 5-2: Study Base Model Common System Data Summary                        | 77  |

| Table 5-3: DC Breaker Model Data Summary                                      | 81  |

| Table 5-4: Case Study Performance Comparisons Table                           | 97  |

| Table 5-5: Requiring IGBTs Count with Different MMC Submodule Topologies      | 98  |

| Table 5-6: Requiring IGBT Count for DC Breaker                                | 99  |

| Table 5-7: Power Losses Comparison to Base Model Case per Station             | 100 |

| Table 5-8: Overall Evaluation Summary                                         | 102 |

## List of Symbols

α Thyristor Firing Angle ac Alternating Current

BIGT Bi-Mode Insulated Gate Transistor

CSC Current Source Converter, also known as line commutated converter

DB Damping Branches

dc Direct Current

DCCB Dc Circuit Breaker

ETT Electrically Triggered Thyristors

FWD Free-Wheeling Diode

GTT Gate Turn-Off Thyristors

HB Hybrid Breaking Units

HSMS High-Speed Making Switch

HV High Voltage

HVDC High Voltage Direct Current

IGBT Insulated-Gate Bipolar Transistor

IGCT Integrated Gate Commutated Thyristors

LCC-HVDC Line Commutated Converter HVDC

LTT Light Triggered Thyristors

LV Low Voltage

MMC Modular Multilevel Converter

MOSA Metal Oxide Surge Arrester

MOV Metal Oxide Varistor

MPH Mechanical and Power Electronic Hybrid

MT HVDC Multi-Terminal HVDC

PG Pulse Generator

PMPH Proactive Mechanical and Power Electronic Hybrid

pu Per-Unit

PWM Pulse-Width Modulation

SCR Short-Circuit Ratio

SF6 Sulfur Hexafluoride

TIV Transient Interruption Voltage

TRV Transient Recovery Voltage

UPS Uninterruptible Power System

VSC-HVDC Voltage Source Converter HVDC

## Copyright Disclaimer

In this thesis, copyright of the following image/figure and tables are reproduced with the permission from IEEE an CIGRE.

In reference to IEEE copyrighted material, which is used with permission in this thesis, the IEEE does not endorse any of University of Manitoba's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to following link to learn how to obtain a license from RightsLink: http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html.

The following figures are adapted or reproduced with IEEE's permission:

- Figure 4-4: Schematic of Passive Oscillation CB Prototype 1, Bachman et al. 1985 [44]

- Figure 4-5: Schematic of Passive Oscillation CB Prototype 2, Lee et al, 1985 [45]

- Figure 4-6: Active Injection DC Breaker Operating Principle, Mohammadi et al, 2021 [38]

- Figure 4-8: Schematic Circuit Diagram of an Active Current Injection DC Circuit Breaker Prototype designed by Mitsubishi Electric, Tokoyoda et al, 2019 [47]

- Figure 4-9: Schematic Circuit Diagram of HVDC Circuit Breaker with Double Breaks and its Testing Results at 145kV 16kA Conditions, Tokoyoda et al, 2019 [47]

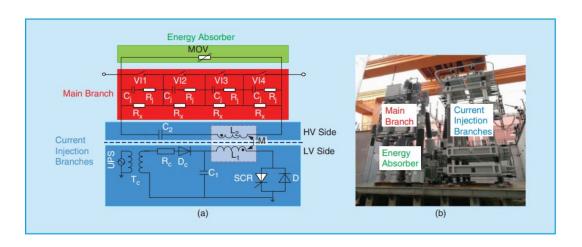

- Figure 4-10: (a) Detail layout of Current Injection DC Circuit Breaker Designed for Nan'ao Multi-Terminal HVDC system; (b) Photo of a Design Prototype, Jovcic et al, 2019 [48]

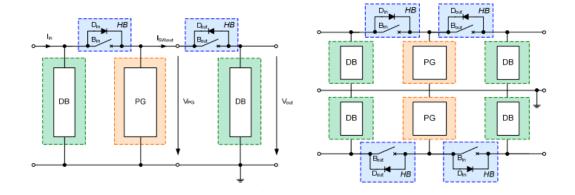

- Figure 4-11: (a) Monopole Layout of a Proposed Current Injection CB (b) Bipolar Layout of the Proposed Current Injection CB, Wang et al, 2013 [50]

- Figure 4-12: Detailed Layout of the Proposed Current Injection DC CB, Wang et al, 2013 [50]

- Figure 4-13: (a) Simulation Results Switching Current (b) Simulation Results for Switch Voltage, Wang et al, 2013 [50]

- Figure 4-17: Basic Circuit Diagram of the MPH CB, Magnusson et al, 2014 [59]

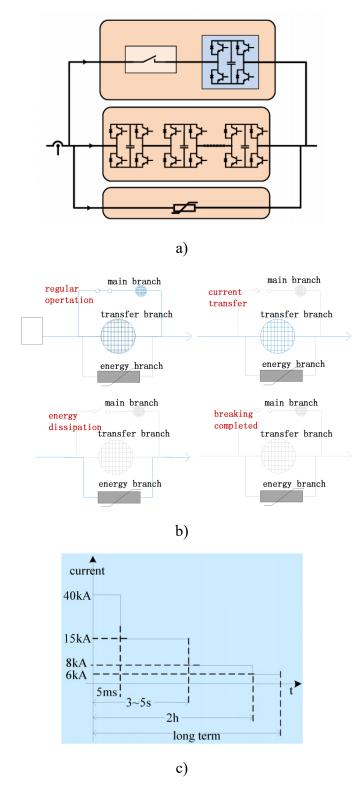

- Figure 4-18: a) Schematic Block Diagram for PMPH CB in Zhoushan HVDC System; b) Operation Principle top-left: regular operation; top-right: current transfer into commutation branch; bottom-left: energy dissipation in energy absorption branch; c) Overload Capacity with Different Current Levels, Jie et al, 2016 [60]

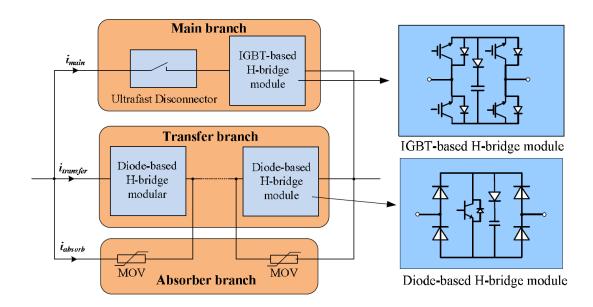

- Figure 4-19: Schematic Diagram of PMPH CB in Zhangbei HVDC System and the Power Electric Switch Module Topologies, Pang et al, 2018 [61]

- Figure 4-20: Operation Principle of Diode Based Full-bridge Module: (a) Conducting State; (b) Blocking State, Pang et al, 2018 [61]

- Figure 4-21: Tests Results of Reclosing Operations with Current (black) and Voltage (blue) across the CB,Pang et al, 2018 [61]

The following figures and table are adapted from Cigré, and reprinted with permission from Cigré:

- Figure 4-2: Schematic of a Fault Current Interruption Process, Cigré JWG A3/B4.34, 2017 [16], reprinted with permission from CIGRE, *<Technical Brochure N°683: Technical requirements and specifications of state-of-the-art hvdc switching equipment JWG A3/B4.34 (2017)>*, © *<2017>*.

- Figure 4-7: DC Current Interruption Process by Active Injection CB, Cigré JWG A3/B4.34, 2017 [16], reprinted with permission from CIGRE, <*Technical Brochure N°683: Technical requirements and specifications of state-of-the-art hvdc switching equipment JWG A3/B4.34 (2017)*>, © <2017>.

- Figure 4-22: Schematic Diagram of ABB's PMPH HVDC CB, Derakhshanfar et al, 2014 [64], reprinted with permission from CIGRE, <Session paper B4\_304\_2014: Hybrid HVDC breaker A solution for future HVDC system>, © <2014>.

- Figure 4-23: Tests Results of Current Interruption Showing Current (Red) and Voltage (Blue) of ABB PMPH CB, Derakhshanfar et al, 2014 [64], reprinted with permission from CIGRE, <Session paper B4\_304\_2014: Hybrid HVDC breaker A solution for future HVDC system>, © <2014>.

- Figure 4-24: Conceptual Schematic Design of GE Alstom's PMPH HVDC CB, Grieshaber et al, 2014 [66], reprinted with permission from CIGRE, *Session paper B4\_301\_2014: Development and test of a 120 kV direct current circuit breaker>*, © *<2014>*.

- Figure 4-25: Tests Results of Current Interruption Showing Prospective (Green) and Interrupted Current (Blue), Current Through the Surge Arrester (Red) and Voltage Across the DCCB (Purple) of GE Alstom PMPH CB, Grieshaber et al, 2014 [66], reprinted with permission from CIGRE, <Session paper B4\_301\_2014: Development and test of a 120 kV direct current circuit breaker>, © <2014>.

## Chapter 1.

### Introduction

In this chapter, voltage source converter technology and its topologies are introduced, by comparing with the line-commutated converter, as key important background references with an emphasis on advancements in the topology of the voltage source converter. Although only point-to-point high voltage direct current transmission systems are examined in this thesis, conceptual high voltage direct current transmission system configurations are briefly discussed. Three techniques based on literature reviews are presented for dc fault clearance. Following these introductions and reviews of the literature, this chapter has discussed the research motivations and objectives before concluding with an overview of the thesis organization.

#### 1.1. VSC-HVDC Overview

#### 1.1.1. Technology

Since its introduction into commercial use in 1954, *High Voltage Direct Current* (HVDC) transmission has been widely employed to enable long-distance power transmission, under water cable transmission, coupling of asynchronous ac networks, and connection of *alternative current* (ac) systems with different frequencies [1]. Conventional HVDC systems are based on the *line*-

commutated converters (LCCs) technology that utilizes thyristor as the key component to convert ac to direct current (dc). Through this conversion which is reliant on the ac (line) voltage, the thyristor valve is commanded to "turn on", and can only be "turned off" when the current through it drops to zero [2] [3]. With its robust design, high reliability, and improving semiconductor technology development, the LCC, also known as "Classic" or Current Source Converter (CSC), has a high level of maturity and long history of success [3]. According to the Cigré B4 compendium, there are 109 known LCC-HVDC systems installed around the world, with 10 more in planning or construction stages [4]. The LCC, on the flip side, has some operational constraints because its current commutation is driven by ac voltage. It necessitates proper ac system conditions, such as a minimum ac system strength, a sufficient reactive power supply, and low-order harmonic filters installed near the converters.

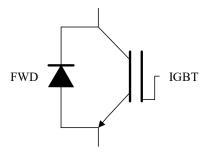

Voltage Source Converter (VSC), contrastingly, is based on fully controllable semiconductor switches, which allow the valve not only to be "turned on", but also to be "turned off" independently of the current that passes through the valve [2]. VSC is able to self-commutate and work around the LCC restrictions listed above because of this distinction. The LCC will also suffer commutation failure and a brief and temporary power interruption during system disturbances when the ac system voltage waveform is significantly distorted [5] [6]. Thanks to its self-driven capability, VSC, on the other hand, is unaffected by this failure. The VSC valve design incorporates fully controllable semiconductors such as insulated-gate bipolar transistors (IGBTs) together with an antiparallel freewheeling diode (FWD) for bi-directional current flow, as shown in Figure 1-1 [1] [2] [3].

Figure 1-1: VSC Valve Circuit Schematic with IGBT and FWD

VSC technology has evolved significantly since the first VSC-HVDC transmission scheme began operation in 1997 [2] [7]. According to the Cigré B4 compendium, 33 VSC-HVDC systems have been installed worldwide, with another 21 planned or under construction [4]. VSC's superior performance properties not only enable it becoming a viable competitor over LCC for long distance point-to-point transmission solutions, but also offer a range of possible new applications, including the following [1] [2]:

- Transmission to/from weak ac systems,

- Supply of passive networks with black-start capability,

- Connection to renewable generations such as wind, wave, or solar power systems,

- And, establishment of multi-terminal system or HVDC networks.

#### 1.1.2. VSC Converter Topology

The converter's fundamental objective is to connect and transmit energy in both directions between ac and dc systems. To date, IGBTs are commonly used in the design of VSCs as converter valves (or referred to as switches) with *Pulse-Wide Modulation* (PWM) control methods, in which two,

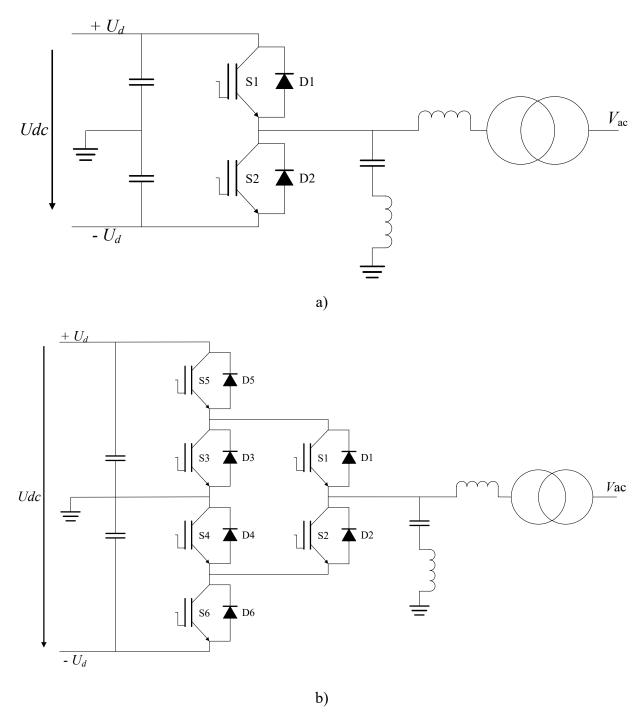

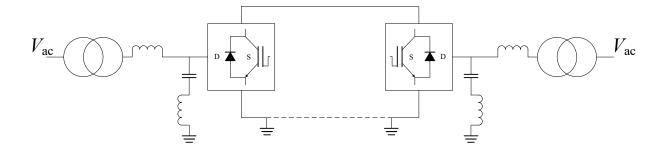

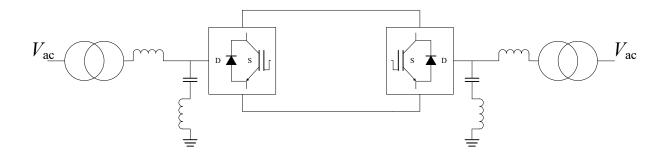

three, or multilevel converter topologies are used to implement the VSC converters [3]. A two-level converter is formed with two alternately operating valves, as illustrated in Figure 1-2(a) for a single-phase converter configuration, the ac bus voltage  $V_{ac}$  varies between the positive dc voltage  $+U_d$  and negative dc voltage  $-U_d$  [2]. An additional intermediate voltage level is available in a three-level converter with subdivided dc capacitor, or additional dc capacitor added. The term "multi-level" refers to the topology of a converter in which the ac bus can be varied to generate three or more distinct voltage levels [2]. Although a number of early VSC installations used two-level or three-level designs, the *modular multilevel converter* (MMC) with cascaded connection has become the most common solution to date for VSC-HVDC systems [2]. In comparison to the two- or three-level converters design, MMC does not use a common capacitor connecting between dc buses; instead, it functions as a voltage source composed of a large number of controllable submodules, each operating independently as a controllable voltage "building block" forming an approximate sine wave. MMC is extendable without requiring excessively complex control systems, which makes it flexible on the system specified converter voltage level.

Figure 1-2: VSC Converter Technologies: a) VSC-HVDC 2 Level Converter Station; b) VSC-HVDC 3 Level Converter Station [2]

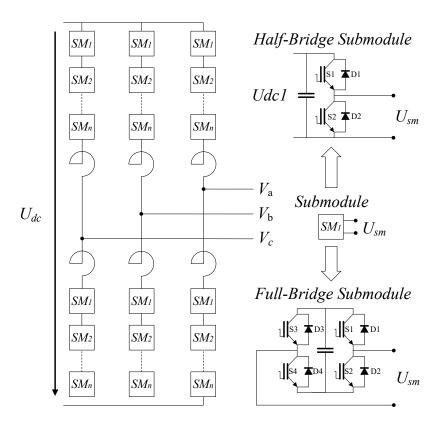

There are two common types of MMC submodule designs, half-bridge design and full-bridge design, which are illustrated in Figure 1-3 [2] [6]. The MMC using half-bridge submodules was

originally invented by Marquardt and his colleagues [8] [9], and this submodule designed with two terminal is series connected to form a converter phase arm in the MMC, each of which features IGBTs and capacitors. The capacitor in the submodule can be charged or discharged depending on the direction of the current; or bypassed by turning on both IGBTs [10]. Each full-bridge submodule can generate three different voltage levels: positive voltage, zero voltage, and negative voltage. During a dc short circuit fault, the additional zero voltage and negative voltage stages of a full-bridge MMC module can be utilized to interrupt or suppress fault current by reversing the voltage polarity and producing a counter electromotive force. [11].

Figure 1-3: Main Circuit Principle Diagram of MMC with Half-Bridge and Full Bridge Sub-Modules [2] [6]

Conduction and switching losses are the two primary forms of losses related with power electronic switches in VSC [1][2]. Conduction losses are proportional to the number of IGBTs, the conduction resistance of the IGBT and FWD pair, and the dc current. Additionally, switching losses are proportional to the regulated switching frequency based on the control scheme, dc current, and voltage measured at pre- and post-switching event [12]. VSC based on two- or three-level converters requires a higher switching frequency than VSC based on MMC, owing to MMC's significantly reduced switching frequency [13]. The topology of the full-bridge submodule is made up of two parallel half-bridge submodules. As a result, the conduction losses and equipment investment costs associated with the converter's total number of IGBTs are greater than those associated with the half-bridge topology.

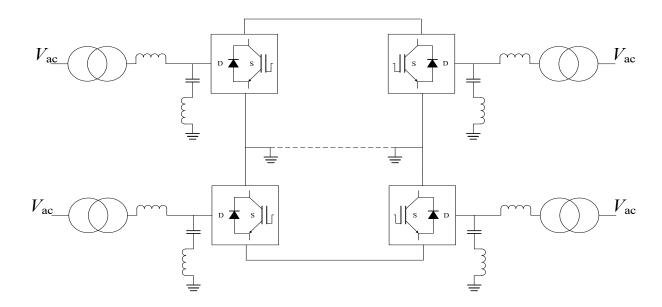

#### 1.1.3. System Configurations

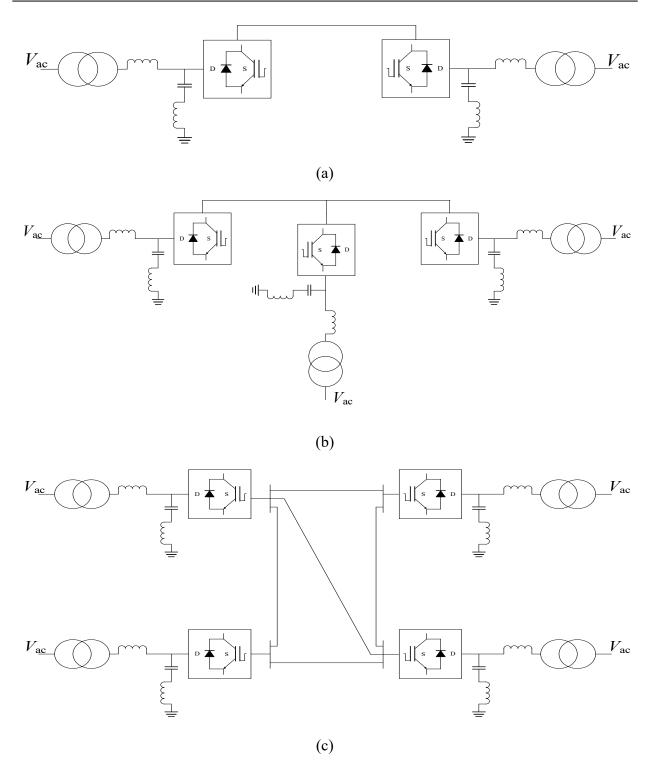

A point-to-point HVDC system, as shown in Figure 1-4a, consists of two converter stations: a rectifier station that converts alternating current to direct current and an inverter station that converts direct current to alternating current for one directional power transfer. The point-to-point HVDC transmission system is connected via long transmission lines or cables, with unidirectional or bidirectional power transmission possibilities. When more than two converter station terminals are connected, a multi-terminal HVDC system with increased power transmission flexibility is formed, as opposed to point-to-point HVDC systems. A multi-terminal HVDC system consists of three or more converter stations, each of which contains at least one rectifier and one inverter. The multi-terminal HVDC system can be configured as a "tapping" system (Figure 1-4b) or as a "meshed" system (Figure 1-4c), which is a more complex configuration that operates like an ac network grid.

Figure 1-4: Sample Point-to-Point and Multi-Terminal Configurations:

- (a) Point-to Point Configuration; (b) Tapping Configuration with Three Terminals;

- (c) Meshed Configuration with Four Terminals [1] [2] [6] [9]

#### 1.1.1. Converter Configurations

Figure 1-5a shows an asymmetrical monopole converter configuration, which is also called a monopolar HVDC system with ground return [1]. The converters are connected between ground and a high voltage dc pole, and current is flowing from the converter through the high voltage pole to the high voltage pole on the opposite station and returning through the ground electrodes or dedicated metallic neutral return conductor.

Figure 1-5b shows a symmetrical monopolar configuration, in which the converter is connected between two high voltage poles with opposite polarity on the dc side. This configuration which is mainly used for VSC-HVDC does not have the ground reference on the dc lines, but the ground reference can be provided through the high impedance reactors on the ac side or through resistive voltage divider on the dc side to provide a closed path for dc leakage current, due to small voltage unbalance between positive and negative poles [1] [14]. Alternative grounding circuit arrangements are suggested in [14] and [15] to utilize high resistance grounding at star configured converter interfacing transformer secondary wingdings for limiting pole to ground fault current, and preventing transformer saturation during the fault and converter energization.

In a monopolar configuration, dc current flows through the two conductors to transmit power, therefore they are operated dependently. If one conductor is out of service, or any dc fault in a monopole system would lead to a loss of power [16]. A bipolar configuration, as shown in Figure 1-5c, is formed by two asymmetrical monopole systems and provides both fail-redundancy and operational flexibility due to the independent operable and controllable poles. Following a dc side fault or pole loss, the remaining pole can operate as an asymmetrical monopole through earth return or metallic return (dedicated conductor) with reduced dc power capacity.

#### (a) Asymmetrical Monopole Configuration

#### (b) Symmetrical Monopole Configuration

(c) Bipolar Configuration

Figure 1-5: Converter Valve Configurations: (a) Asymmetrical Monopole Configuration; (b) Symmetrical Monopole Configuration; (c) Bipolar Configuration. [1] [2] [13]

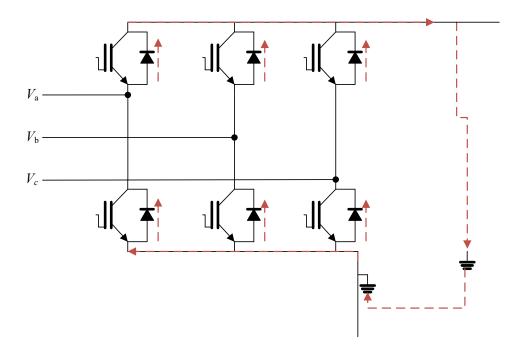

#### 1.2. DC Line Fault for Point-to-Point VSC-HVDC System

For LCC, when the dc line fault occurs, the current control function can be used to limit the fault current and the valve control and protection can be used to clear the fault current with multiple attempts at different voltage levels. This control sequence takes approximately 20 to 40 milliseconds [17] [18]. While VSC has a number of advantages over LCC they do have one disadvantage, IGBTs can be blocked for self-protection in the event of a dc fault, the FWDs connected in parallel with the IGBTs operate as an uncontrolled bridge rectifier, continuously feeding the fault from the ac system via the formed diodes rectifier bridge [1] [19], as illustrated in Figure 1-6. If the dc system is entirely composed of cables, a fault is highly improbable [2]. For overhead lines, however, dc line faults are highly probable. The fault current from ac systems is limited by the ac network's short-circuit impedance, the transformer's reactance, the phase reactor's reactance, and resistance in the circuit. For the case where dc Circuit Breaker (DCCB) or other fault clearing device is not available on the dc side, the short-circuit current is eliminated solely by tripping the ac-side breakers. While tripping the ac-side breaker may appear to be the simplest dc line fault response, due to fault detection and operation delays, the converter will not be isolated immediately following the fault, resulting in fault contribution from ac systems, causing further disturbance to the ac system network.

Figure 1-6: Conceptual VSC diagram for Current Flow during DC Faults

A dc line fault in VSC-HVDC appears to be a remote fault to the connected ac system; if the fault current relies on ac side circuit breakers to clear, it will take at least a few hundred milliseconds to interrupt and extinguish the fault current [19] [20]. Depending on the dc transmission power capacity, a dc line fault may pose a significant transient stability risk to the connected ac networks. An example of a system study case is Manitoba Hydro's dc line fault performance studies for Bipole III using half-bridge MMC with overhead transmission lines. As in a such case, the ac system voltage at the inverter station was reduced to 0.72 per-unit (pu) following a dc line fault prior to utilizing ac breakers to clear the dc fault [21]. Due to the electrical proximity of the other two existing LCC Bipoles (Bipoles I&II), the study also demonstrated that a dc line fault at Bipole III's inverter end would propagate to the common connected inverter ac bus for Bipole I and Bipole II, resulting in a maximum voltage depression of 25% at the Bipoles I&IIs' inverter ac bus voltage level, which caused in commutation failures of Bipoles I&II LCC HVDC systems. Additionally,

use of ac-side circuit breakers also can result in a much longer power delivery interruption and a further impact on ac system voltage stability because of the time required to re-close in the breakers, and large inrush current generated when re-energizing the converter transformers after the fault clears. After a temporary dc line fault, Manitoba Hydro's study found that it took up to 800 milliseconds for dc power to recover to 90% of its pre-fault dc transmitting power level. [21]. Due to the large potential inrush current generated by transformer energization, the associated ac system voltage level may also be hugely affected during the re-energizing process. Finally, dc faults usually occur temporarily on overhead transmission line when lightning strikes the line or when objects, such as trees, collide with the line. Therefore, in an LCC HVDC system, multiple system restoration can be attempted to ensure dc fault is cleared to improve system availability before transmission system is permanently locked out. However, using ac breaker in this manner is not feasible due to the prolonged recovering time and ac system impact during transformer energization.

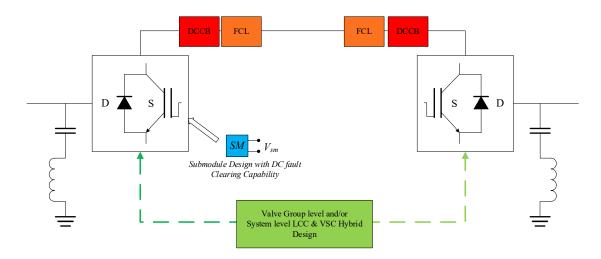

As a result, in order to match the LCC dc line fault clearance performance and ensure the connected ac system's stability and availability, a DCCB or other means of interrupting dc faults is a critical requirement for supporting VSC-HVDC technology. Through the literature review, there are a number of techniques available and proposed for dc fault clearance in a VSC scheme which are comparable in speed to a pure LCC scheme utilizing current control. These strategies include the following:

- a) Employing dc breakers with or without fault current limiters

- b) Modifying VSC MMC submodule topologies to include dc fault clearing capability

- c) Utilizing hybrid configuration of LCC and VSC in valve group/system level design

Figure 1-7: System Layout for DC Fault Clearance Techniques

#### 1.3. Research Objectives

The purpose of this thesis is to develop a comprehensive list of different dc fault clearance techniques and an analytical evaluation methodology for comparing alternative dc line fault clearing techniques in a point-to-point VSC HVDC scheme. In the majority of VSC schemes, the default dc fault clearing mechanism is based on ac breakers, which, as previously explained, is slow in respect of fault clearance and dc link restoration. Given the number of options proposed and becoming available, how would a utility engineer compare and select a preferred method? This thesis will identify important factors such as losses, cost, and performance for evaluating dc fault clearance techniques for point-to-point VSC HVDC scheme.

Two PSCAD-EMTDC models will be developed based on leading options to assess fault clearing performance.

- i) Half-bridge VSC MMC with Hybrid dc breaker

- ii) Full-bridge VSC MMC converter

#### 1.4. Motivations for Research

The Manitoba Hydro transmission system was developed and operated as an integrated system, with the Nelson River HVDC system serving as the backbone, as shown in the Figure 1-8, transporting over 70% of Manitoba Hydro's electric power from northern generating stations to southern load centers as well as for export [22]. Each of the three Bipoles was built with Line Communicated Converter (LCC) technology.

Bipole III, the latest Bipole, entered commercial service in July 2018. VSC technology with half-bridge MMC was studied and investigated during the Bipole III's planning stage as a possible alternative to LCC technology [7] [21] [23]. Studies indicated that dc line fault recovery for a

HVDC transmission capacity: ~ 70%

Bipole I: 890km, ±463.5kV, 1854MW, LCC.

- Pole 1 valves replaced using ETT, valve group control was replaced with analog controls in 1992,

- Pole 2 valves were replaced with LTT interfaced with original group control in 2004.

Bipole II: 930km, ±500kV, 2000MW, LCC.

Original valves and controls are still in service up to today.

Bipole III: 1,386km, ±500kV, 2000MW, LCC

Contract was awarded to SIEMENS, ISD 2018

Figure 1-8: Manitoba Hydro Nelson River Three-Bipole HVDC system [22]

VSC was found to be slower than LCC when fault clearing via ac breakers was assumed, requiring six cycles interruption time with a worst case fault current of 30kA, system restart may not be feasible due to the transformer re-energization causing subsequent communication failures of Bipoles I&II, and suggested further investigation of different dc line fault clearing methods [7]. At the time, there was no comprehensive list of different dc faults clearing techniques with analytical comparisons methodology. The development of such a list and evaluation methodology, along with sample PSCAD-EMTDC models, will aid transmission operators and utilities in evaluating future technology selection and conducting system studies comparing available techniques for VSC fault clearance.

#### 1.5. Summary and Thesis Organization

The review and comparison of various dc fault clearing methods requires an understanding of the VSC-HVDC topology, its major components, and the characteristics of dc line faults. This introduction chapter provides pertinent background information, defines the research motivation and primary objectives. The structure of remaining chapters in this thesis is organized in the following order:

<u>Chapter 2</u> reviews the characteristics of dc line faults for a point-to-point VSC-HVDC scheme with overhead transmission line, before delving into generic configurations using mathematical derivations of current and voltage behavior.

<u>Chapter 3</u> discusses the various MMC submodule topologies that support dc fault clearing.

<u>Chapter 4</u> discusses the various DCCB topologies, including the mechanical type, pure power electronic type, and hybrid mechanical/power electronic type, as well as the fault interruption process.

<u>Chapter 5</u> introduces an evaluation methodology which is used to analyze and compare two solutions: full-bridge MMC and half-bridge MMC with dc breakers in detail using cases studies on PSCAD-EMTDC. The study case models are reviewed in detail and an extensive systematic analysis of performance comparison together with losses and cost evaluations are also presented base on the case study models.

<u>Chapter 6</u> presents the conclusions, summarizes the contributions of this thesis, and makes recommendations for future work.

While this thesis cannot possibly include or reference every pertinent work, it presents the essential principles underlying the different dc line fault clearance approaches available to date in a systematic manner. The author's intention is to lay the groundwork for readers interested in identifying and further evaluating the most appropriate methodology for their research and study objectives, as well as determining where to go from here.

## Chapter 2.

# DC Faults in VSC-HVDC Systems

### 2.1. Introduction

Generally speaking, voltage source converter with two level, three level or MMC using half-bridge submodule design is susceptible to dc faults, due to its freewheeling diodes connected anti-parallel with controllable power electronic devices such as IGBTs. During the fault, while it is possible to disable the IGBTs for self-protection, doing so does not interrupt the fault current. A typical twolevel, three-level, or half-bridge MMC will act as an uncontrolled ac rectifier through the freewheeling diodes, which draw the fault current from the ac network through the converter. A converter using submodules with fault current interruption capability, such as full-bridge MMC topology, can block the fault current contribution from the ac network and limit the fault current within the transient phase [2] [16], which will be discussed further in the Chapter 3. According to this research, the current characteristics of a dc fault are crucial for the design of system components, for fault detection, for the coordination of protection strategy, and for the evaluation of clearance techniques. DC faults can be classified into two types based on the nature of their occurrence: pole-to-pole faults and pole-to-ground faults with a ground connection. The behavior of the VSC converter during the occurrence of pole-to-ground faults and pole-to-pole faults is discussed in detail in this chapter.

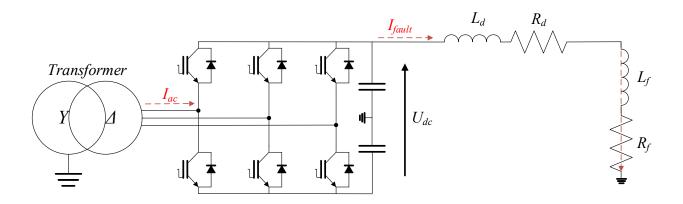

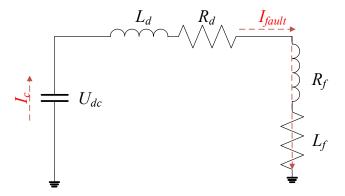

### 2.2. Pole-to-Ground Faults

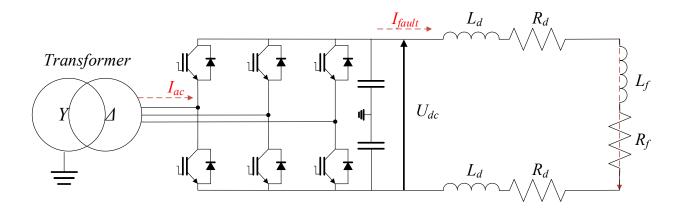

A dc pole-to-ground fault occurs when the positive or negative line conductor is shorted to the ground [16]. This fault can occur temporarily on overhead transmission lines when lightning strikes the line causing voltage surge and flashover across the insulator string through the ionized air [1] or when objects, such as trees, collide with the line; or permanently on a cable conductor due to insulation breakdown. When a pole-to-ground fault occurs on the dc line of a VSC-HVDC, a ground loop is generated between the grounding locations, for example, between the high resistance grounding at the converter transformer's star configurated winding and the ground fault point [24]. In Figure 2-1, an equivalent circuit of the VSC-HVDC with a two-level topology is shown with its positive pole shorted to ground in order to demonstrate the converter's behavior during the fault condition. In this diagram,  $R_f$  and  $L_f$  represent the fault resistance and inductance, respectively, while  $R_d$  and  $L_d$  represent the dc line model's equivalent resistance and inductance, respectively, while  $R_d$  and  $L_d$  represents the dc line model's equivalent resistance and inductance, represents the dc fault current,  $U_{dc}$  represents the voltage across the dc-side capacitor, and  $I_{ac}$  represents the ac grid-side current.

Figure 2-1: Equivalent Circuit Diagram of VSC DC Pole-to-Ground Fault [24] [25]

During the initial transient stage after the fault occurs, the pre-fault dc voltage  $U_{dc}$  is larger than the ac line to line voltage. Therefore, the dc fault current at this stage is mostly from dc capacitor discharging current, and the system can be represented using the equivalent circuit shown in Figure 2-2 [24]. In this initial stage, the capacitance of dc capacitor, filter elements, dc lines, the resistance and reactance associated with dc lines, distance of the fault location, the fault impedance, and the dc reactor size will influence the fault current behavior [24]. The amplitude of the fault current increases with larger capacitance in the equivalent circuit, whereas the resistance in the equivalent circuit provides positive damping to the fault current amplitude [25]. The inductance in the loop will reduce the rate of rise of the fault current. The second-order mathematic representation of the equivalent circuit is given by [24] [25]:

$$(L_d + L_f)C\frac{d^2U_{dc}}{dt^2} + (R_d + R_f)C\frac{dU_{dc}}{dt} + U_{dc} = 0$$

(2.1)

Figure 2-2: Equivalent Circuit of DC Capacitor Discharging for Pole-to-Ground Faults [24]

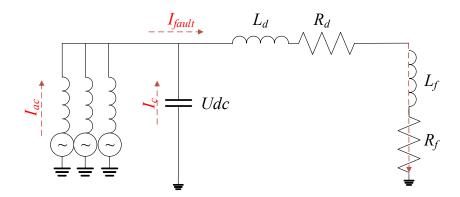

As the discharge of the dc capacitor continues, the dc voltage begins to rapidly decrease. When the ac voltage exceeds the dc voltage, the fault current begins to flow through the converter, triggering self-protective blocking of the IGBTs when the overcurrent exceeds the protective settings of the IGBTs. In this case, it results in the converter operating as an uncontrollable freewheeling rectifier, which draws the fault current from the ac network. During this stage, the fault current increases even more, and its behavior is determined by the ac network short circuit strength, the location of the fault, the converter topology and its configurations, and the impedance associated with the converter transformer and dc lines [10] [16]. The equivalent circuit in the ac network feeding stage is shown in Figure 2-3.

Figure 2-3: Equivalent Circuit of AC Network Feeding Stage for Pole-to-Ground Faults [24] [25]

Similar to the initial capacitor discharging stage, the resistance in the formed current loop will limit the amplitude of the fault current. If the converter employs full-bridge MMC or other submodule topologies with fault interruption capability, fault current from the ac network can be blocked, limited or controlled based on the control scheme for dc fault [2] [10] [13]. For asymmetrical monopole configuration with the converter transformer ungrounded on the converter

side, since there is no grounding current path for a pole-to-ground fault, additional transient ac fault current is only drawn from ac system when ac voltage is greater than the dc voltage. Once the voltage levels between the poles have been rebalanced, the fault current draw from the ac system will cease [16].

### 2.3. Pole-to-Pole Faults

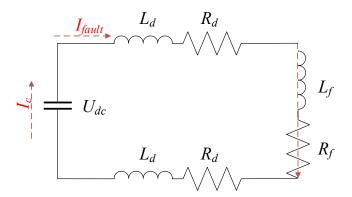

Pole-to-pole faults can occur at where the two pole conductors make contact or when insulation breakdown causing a fault across positive and negative poles. Its equivalent circuit can be represented as shown in Figure 2-4. The fault current flows from the positive pole through the fault impedance and returns to the negative pole via the negative line.

Figure 2-4: Equivalent Circuit Diagram of VSC DC Pole-to-Pole Fault [25] [26]

During the initial stage following the fault, the dc capacitor discharges, resulting in a rapid dc voltage collapse. As shown in Figure 2-5, the fault current profile is influenced by the L/R/C

characteristic of the dc networks. The reduction of the dc voltage leads to the fault current being drawn from the ac network and flowing to the fault through the converter's freewheeling diodes.

Figure 2-5: Equivalent Circuit of DC Capacitor Discharging for Pole-to-Pole Faults [25] [26]

A pole-to-pole fault current during the transient initial stage behaves in a similar manner to a pole-to-ground fault, both of which are dominated by the discharging of the dc capacitor. However, as compared to a pole-to-ground fault, a pole-to-pole fault can be more severe, resulting in a higher fault current and greater impact on the connected system, because of the lower fault resistance of a pole-to-pole fault when compared to a pole-to-ground fault [16] [27].

In a full-bridge MMC, after the fault is detected and submodules are blocked, the fault current momentarily continuous to feed the fault through the FWDs (D1 and D4) as shown in an equivalent circuit diagram Figure 2-6, where a possible fault current path flows across a and b phase through the top and bottom phase arms of the converter. After the energy in the ac arm inductors is discharged, the fault current will decay to zero due to the greater dc voltage  $2U_c$  ( $U_c$  representing the voltage of the half phase arm's equivalent capacitors) in comparison to the ac line-to-line voltage ( $V_{ab}$ ) [28].

Figure 2-6: Equivalent Circuit Diagram of Full-Bridge VSC for Pole-to-Pole Fault [13] [28]

## 2.4. Summary

This chapter analyzes and discusses the behavior of dc line faults in a point-to-point VSC-HVDC transmission system, specifically pole-to-pole faults and pole-to-ground faults with a ground connection. Through this review, system and design parameters were found such as inductance, resistance, fault location on the dc network and ac system strength would affect and determine the fault current behavior. A pole-to-pole fault is regarded more severe compared to a pole-to-ground fault, but less likely to occur in a point-to-point HVDC transmission system utilizing overhead transmission lines. To avoid damage to converter equipment due to excessive fault current and to ensure the stability and availability of interconnected ac networks, the system and design parameters identified in this chapter should be properly considered in dc fault clearance techniques, and in conjunction with properly designed protection strategies.

# Chapter 3.

# MMC Submodule Designs for DC

## Fault Clearance

### 3.1. Introduction

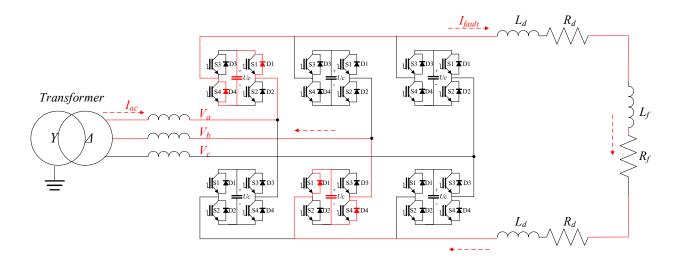

When implementing a VSC-HVDC design, half-bridge topology is the straightforward and cost-effective option for MMC converter design, and thus the most common type of submodule [29]. However, during a dc line fault, the IGBTs in half-bridge submodules are blocked forming a short circuit that allows continuous fault current to feed into the dc side fault until the ac-side breaker is tripped or, if available, the DCCB is activated. To address the dc fault handling capability, the full-bridge submodule topology was implemented in conjunction with other submodule design variations to enable dc fault clearance [29]. Sections 3.2-3 of this chapter go over the design, operation principle, and dc fault handling capability of the full-bridge and clamp-double submodule designs.

## 3.2. Full-Bridge Submodule design

Each full-bridge submodule in the MMC topology is controlled individually to generate the approximate sine wave shape shown in Figure 3-1. Its four operational modes are as follows:

a) Blocking mode: With all IGBTs turned off,

- b) Bypassed mode: When S1 and S3 are activated, or when S2 and S4 are activated, the submodule is bypassed.

- c) Positive insertion: When S1 and S4 are turned on, the capacitor inserts its voltage  $+U_c$ , and the capacitor is charged or discharged depending on the direction of the current i.

- d) Negative insertion: With S2 and S3 are turned on, the capacitor inserts its voltage in the reverse polarity  $-U_c$ , and the capacitor is charged or discharged depending on the direction of the current i.

During a DC fault, the fault current can be controlled/managed by inserting a voltage opposite the ac line voltage; and by blocking all the IGBTs, the submodule naturally blocks the voltage of the same magnitude as the charged submodule capacitor [29].

Figure 3-1: Full-bridge Submodule and Operation States

Research and studies have also suggested that respecting the full-bridge submodule operability maintaining current control during a dc line fault, fault current can be suppressed to zero while the converter remains synchronized and connected to the ac system in reactive power control. Both dc and ac system can benefit from a timely post-fault power recovery in the event of the transient dc fault [30]. However, as previously stated, a full-bridge submodule design requires twice the number of IGBTs as a half-bridge design, significantly increasing converter losses and cost.

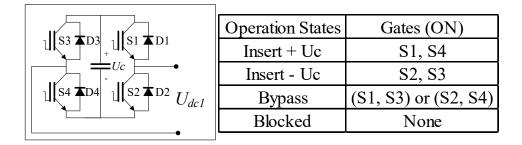

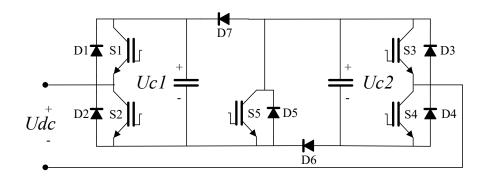

## 3.3. Clamp-Double Submodule Design

Full-bridge MMC has an additional switching state with the negative voltage insertion; however, it is also a drawback using double the number of IGBTs with double the conduction losses during normal operation. As a result, novel submodule topologies are designed to offer fault current blocking and handling capabilities while also minimizing normal conduction losses through the use of fewer semiconductors. Clamp-double submodules were introduced as an alternative topology to the full-bridge submodule to reduce power losses and to incorporate dc line fault handling capability [31]. The clamp-double submodule, as illustrated in Figure 3-2, is essentially two half-bridge submodules clamped together in series through two additional clamping diodes and one additional IGBT. According to Table 3-1, in normal operations it is equivalent to two halfbridge submodules in normal operation, with an additional IGBT (S5) and three distinct voltage levels across the submodule terminals. During a dc line fault, all IGBTs are switched off, both capacitors for voltage clamping are inserted, and the fault current is reduced to zero. Despite the fact that the clamp-double MMC is capable of blocking the dc side fault, it can only generate half the reverse voltage generated by the full-bridge MMC. Therefore, if the grid voltage is sufficiently high, the fault current can flow [29] [32].

Figure 3-2: Clamp-Double Submodule of an MMC Valve

Table 3-1: Switching States of Clamp-Double Submodule

| Operation States         | Gates (ON) |

|--------------------------|------------|

| Insert $+U_{c1}$         | S1, S3, S5 |

| Insert $+U_{c2}$         | S2, S4, S5 |

| Insert $(U_{c1}+U_{c2})$ | S1, S4, S5 |

| Bypass                   | S2, S3, S5 |

| Blocked                  | none       |

## 3.4. Summary

This chapter discussed the full-bridge and clamp-double submodule designs. Their component counts and performance were compared to those of half-bridge submodule designs, as summarized in Table 3-2. For the purposes of this comparison, it is assumed that there are a fixed number (*M*) of capacitors per MMC arm. Calculations are made for the number of capacitors and IGBT switches, as well as the average number of IGBT switches in normal operation stages. The clamp-double submodule has a higher conduction loss than the half-bridge submodule but a lower conduction loss than the full-bridge submodule. A clamp-double or full bridge based MMC has both dc fault blocking and fault control capabilities; however, due to the clamp-double based MMC's half equivalent dc reserve voltage, its fault control capability is limited in comparison to a full-bridge based MMC.

**Table 3-2: Comparison of Submodule Designs**

| Submodule Design | NC | NS           | NON          | DC Fault Blocking | Losses   | Voltage Levels           |

|------------------|----|--------------|--------------|-------------------|----------|--------------------------|

| Half-bridge      | M  | 2M           | M            | No                | Low      | 0, <i>U</i> <sub>c</sub> |

| Full-bridge      | M  | 4 <i>M</i>   | 2 <i>M</i>   | Yes               | High     | $0$ , $\pm U_c$          |

| Clamp-Double     | M  | 2.5 <i>M</i> | 1.5 <i>M</i> | Yes               | Moderate | $0, \pm 1/2U_c, U_c$     |

NC: Total number of Capacitors per arm

NS: Total number of IGBTs per arm

NON: Average Number of IGBTs connected during normal operation

$U_c$ : Equivalent voltage across one submodule terminals

M: Number of capacitors per MMC arm

Due to the thesis's scope and limitations, additional submodule design variations are listed for reference but are not reviewed in detail: a unipolar-voltage full-bridge submodule design based on a full-bridge submodule with S3 replaced by a FWD will reduce the cost and switching power losses associated with a full-bridge submodule design [33] [29]; to further improve the clampdouble submodule design's dc fault handling capability, a five-level cross-connected submodule was proposed in [34]; to further reduce switching power losses, a three-level cross-connected submodule was introduced in [33]; and finally, a number of researchers have focused on hybrid submodule topologies using half-bridge mixed with full-bridge, clamp-double or other submodule designs with dc fault blocking capabilities to reduce the cost and power losses [33] [35] [36] [37]. In conclusion, depending on the scope and specification of the project, a full-bridge based MMC provides a better performance defined by shortest fault clearing time during a dc side fault with a higher equivalent dc reverse voltage for VSC-HVDC systems, disregarding the cost and losses. Additionally, new topologies and hybrid submodule configurations are being introduced and developed with a goal to provide the same level of fault handling capability while featuring lower power losses.

# Chapter 4.

## **HVDC** Breakers

### 4.1. Introduction

The fundamental difference in realizing dc breakers compared to ac breakers is the absence of the current zero crossing [13]. Additionally, when compared to ac systems, dc systems have a low damping factor. As a result, a dc fault current has a much higher rate of rise, necessitating a fast control and protection system together with a rapid means of interrupting the fault current, such as dc breaker. Consequently, the dc breakers must meet the following requirements [7] [9] [23]:

- 1) Generating a zero current for fault interruption,

- 2) Absorbing or dissipating the energy stored in system inductance,

- 3) Rapid current interruption,

- 4) Low losses during normal operation, and

- 5) Ability to tolerate the network's voltage response following current interruptions.

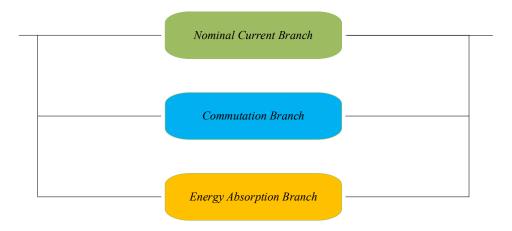

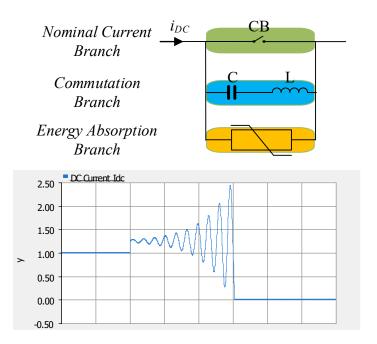

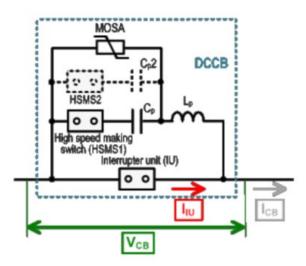

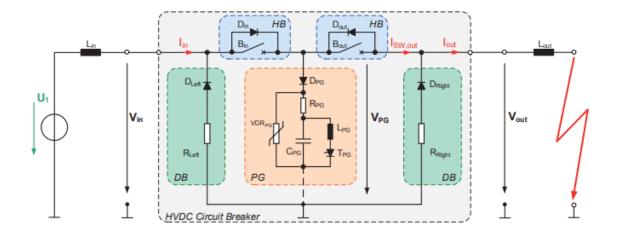

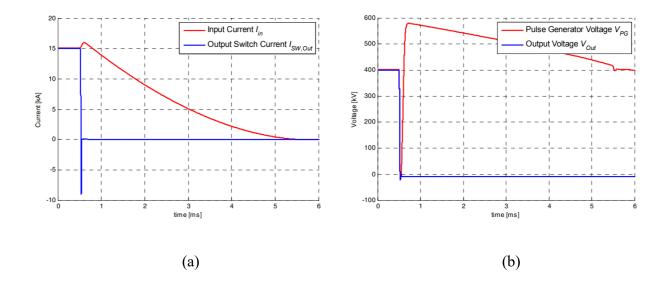

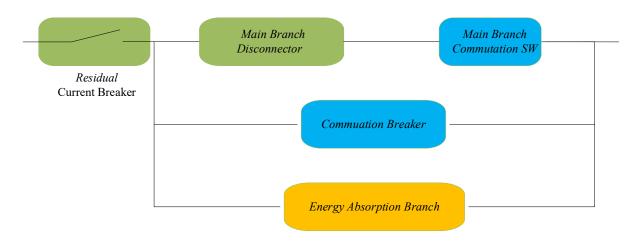

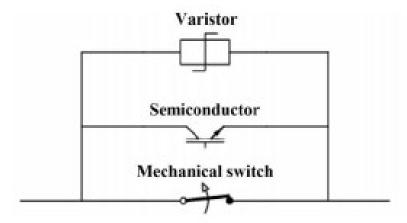

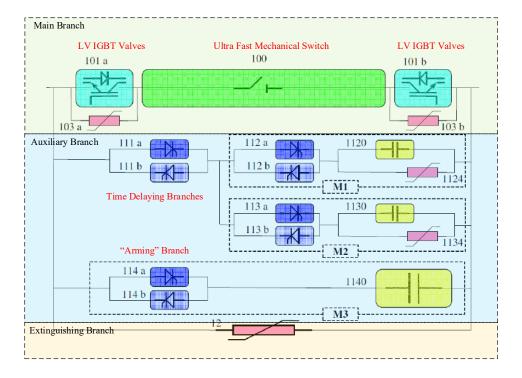

The first two requirements are particularly difficult to fulfil with a single component; however, multiple parallel paths within a breaker assembly can be used to assign the requirements to different elements [19]. A conceptual DCCB arrangement is demonstrated in Figure 4-1, illustrating a typical DCCB configuration, which consists of a nominal current path, a commutation path, and an energy absorption path.

Figure 4-1: Conceptual Topology of a DCCB

The nominal current path is comprised of a low-loss main branch interrupter in the closed position.

During a dc line fault, the commutation path assists in fault current interruption and commutates line current into the parallel energy absorption path for dissipating the system's inductive energy.

Current can be suppressed to zero in a dc system by generating a counter voltage greater than the system voltage [19]. The greater the counter voltage, the faster the fault current decays to zero and the shorter the time required for an interruption. Different technologies have been used to generate this counter voltage. Three different breaker technologies are discussed in this chapter: mechanical circuit breakers, power-electronic breakers, and proactive hybrid mechanical and power-electronic breakers. The working principle of each circuit breaker type will be presented first, followed by sample prototypes, installation, and research concepts. Finally, their relative advantages and disadvantages are evaluated referencing to published technical papers.

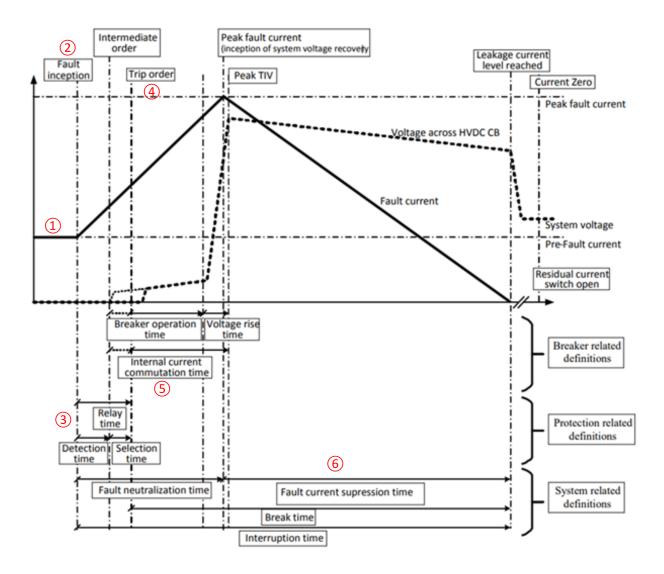

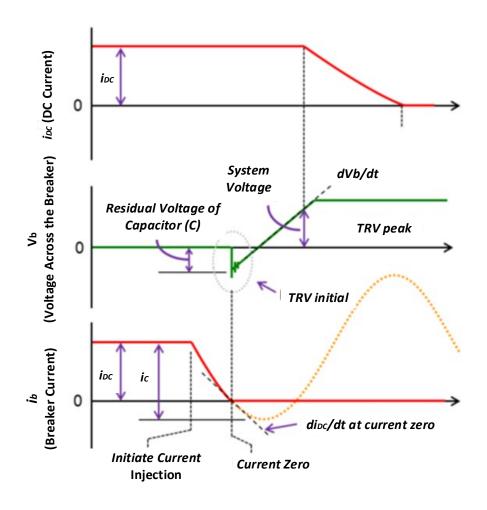

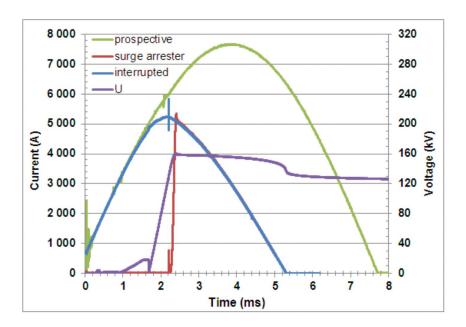

# 4.2. Standard Fault Current Interruption Process and Definitions

CIGRÉ joint working group A3/B4.34 Technical Brochure No. 683 [16] established a standard dc fault current interruption process and also definitions for comparing DCCBs and other clearance methods analytically. Figure 4-2 adapted from [16] illustrates a standardized overview of a fault interruption process, irrespective of breaker type, topology, or design.

1) Prior to the fault inception, the flat line represents the pre-fault current, which is plotted as a solid line, and the voltage across the dc circuit breaker is plotted as a dashed line; 2) The vertical dashed-dotted line with remark of fault inception indicates the instance when the fault occurs; 3) A protection relay needs to detect the fault (detection time) and select faulty line (selection time) before a trip command will be initiated to the circuit breaker. If the proactive type of circuit breaker is used, an intermediate order could also be issued prior to the trip initiating the interruption process; 4) The breaker begins commuting the current from the nominal branch to the energy absorption branch upon receipt of the trip order; 5) During the time required for internal current commutation, the voltage across the dc circuit breaker increases to its peak Transient Interruption Voltage (TIV). The fault current reaches its peak value and begins to decrease as the voltage across the dc circuit breaker builds up to counter the system voltage at the breaker location. 6) The inductive energy in the faulted system is dissipated during the fault current suppression time, and the fault current reduces to the leakage current level, at which a residual current breaker can open to interrupt the fault if it is equipped.

Figure 4-2: Schematic of a Fault Current Interruption Process [16]

The critical timing parameters and their definitions are included in Table 4-1. These well-established industry parameters and definitions will be used throughout this thesis for HVDC breaker operating principle descriptions, examination, and evaluation of fault current interrupting performance. Internal current commutation time and fault current interruption capability have been identified as critical technical specifications for evaluating different breaker design topologies. Even though published technical papers and technical references [38] [39] have indicated that the

total interruption time should be within 5ms. Based on the industry recommended guidelines [16] the dc protection system such as dc breaker should be able to clear the dc line fault within 20-40ms, which is comparable with LCC-HVDC; correspondingly, any dc breaker topology investigated in this thesis must have an internal current commutation time of less than 10 milliseconds to meet the HVDC fault clearance requirement, ensuring equipment safety and interconnected ac system stability.

**Table 4-1: Fault Current Interruption Process Definitions [16]**

| Parameters                           | Definitions                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Detection Time                       | The time for protection or control system to detect the fault using sensing device and embedded protection calculation algorithm. The time required for detection is included in the relay time.                                            |  |  |  |  |  |  |

| BRK Operation Time                   | Between the reception of the trip command and the commencement of the DCCB interruption voltage increase, this time interval is defined as part of the internal current commutation time.                                                   |  |  |  |  |  |  |

| Voltage Rise Time                    | This time period is also included in the internal current commutation time, which ends when the transient interruption voltage (TIV) reaches its peak value.                                                                                |  |  |  |  |  |  |

| Internal Current<br>Commutation Time | It is the total of the Breaker Operation Time and Voltage Rise Time, beginning with the receipt of the trip order and ending with the peak TIV across the DCCB.                                                                             |  |  |  |  |  |  |

| Fault Neutralization<br>Time         | It is the time interval between the occurrence of a fault and the moment at which the fault current reaches its maximum value.                                                                                                              |  |  |  |  |  |  |

| Fault Current<br>Suppression Time    | It begins with the maximum value of the fault current and ends with<br>the fault current being decreased to the leakage current level (or<br>below).                                                                                        |  |  |  |  |  |  |

| Break Time                           | It is the combination of the Internal Current Commutation Time and<br>the Fault Current Suppression Time; from the time the trip order is<br>received to the time the fault current is decreased to the leakage<br>current level (or below) |  |  |  |  |  |  |

| Interruption Time                    | It is the total time required to interrupt the fault current from the time the fault occurs to the time the fault current is reduced to the leakage current level (or below)                                                                |  |  |  |  |  |  |

| Intermediate Order(s)                | Any proactive order issued prior to the trip initiating the interruption process particularly for the proactive type hybrid DCCB types                                                                                                      |  |  |  |  |  |  |

### 4.3. Mechanical Circuit Breaker

Mechanical dc circuit breakers are frequently used in point-to-point LCC HVDC converter stations for a variety of switching functions, including high-speed bypass switch (HSBS), neutral bus switch (NBS), neutral bus ground switch (NBGS), parallel line switch (PLS), earth/metal/ground return transfer switches (ERTS, MRTS, GRTS), and isolation switches [16] [19]. To meet the specific needs of a high voltage dc fault clearance, two methods, namely passive oscillation and active current injection, are used to interrupt dc fault currents when the current is forced to a zero crossing.

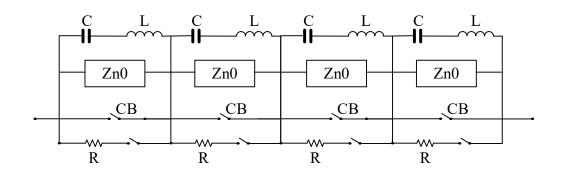

#### 4.3.1. Passive Oscillation Mechanical Circuit Breaker

### 4.3.1.1. Operating Principle and Basic Functionality

A passive oscillation-type mechanical dc circuit breaker, illustrated in Figure 4-3, is composed of a primary mechanical interrupter, a parallel coupled oscillating circuit consisting of an inductor and a capacitor, and an energy dissipation element. When the main interrupter is opened in response to a trip command, an electric arc forms between the contacts, and a circuit loop consisting of the mechanical interrupter, inductor, and capacitor experiences a negatively damped resonance oscillation. As the amplitude of the oscillation rises, a current zero eventually occurs in the nominal current path presenting an opportunity to interrupt dc current [9] [16] [40] [41].

Figure 4-3: Passive Oscillation DC Breaker Operating Principle [16] [42]

The selection and design of the inductance (L) and capacitance (C) values define the oscillation frequency, while the counter arc voltage created by the main interrupter opening determines the oscillation amplitude [16]. Following interruption in the nominal current branch, the dc fault current is commutated to the commutation branch and charges the capacitor, while the surge arresters in the energy absorption branch limits the capacitor's maximum voltage to the clipping voltage of the arresters; once the clipping voltage is reached, the current is commutated to the energy absorption branch and dissipated via the low dynamic resistance, effectively reducing the dc current to zero [16] [42] [43].

Internal current commutation time is determined in this design by the dimensions of the L-C components, which are also closely related to the interrupter selection and its arc voltage characteristic [16]. The interrupters' arc voltage characteristic is critical in generating the current

oscillation required to obtain current zeros. While the surge arresters in the energy absorption path have no effect on the commutation time, their clipping voltage level has an effect on the fault current suppression time as part of the overall break and interruption times that influence the voltage stability of the connected ac system [16].

### 4.3.1.2. Example Prototype Designs

Two prototypes of passive oscillation dc circuit breakers were designed in the late 1980s [42] [44] [45], and both prototypes were field-tested at the Celilo station of the Pacific Interconnection HVDC scheme. Cigré's joint working group A3/B4.34 reviewed and summarized the design details, component electrical dimensions, and performance in [16]; they are referenced in Table 4-2.

Figure 4-4: Schematic of Passive Oscillation CB Prototype 1 [44]

Figure 4-5: Schematic of Passive Oscillation CB Prototype 2 [45]

Table 4-2: Specification Summary of Passive Oscillation CB Example Prototypes

| Prototype | Main<br>Interrupter<br>Type | Num.<br>of<br>Modules | Rated<br>Voltage<br>(kV) | Rated<br>Current<br>(kA) | L<br>( <i>u</i> H) | C<br>( <i>u</i> f) | f<br>(kHz) | Arrester<br>Type | Arrester<br>Clipping<br>Voltage<br>(kV) | Internal Current Commutation Time | Break<br>Time<br>(mS) |

|-----------|-----------------------------|-----------------------|--------------------------|--------------------------|--------------------|--------------------|------------|------------------|-----------------------------------------|-----------------------------------|-----------------------|

| 1         | Airblast                    | 4                     | 500                      | 4.4                      | 400                | 1.25               | 7          | ZnO              | 200*                                    | 12                                | 30-50**               |

| 2         | SF6                         | 4                     | 500                      | 2.2                      | 40                 | 3                  | 14.5       | ZnO              | 175*                                    | 14                                | 30-50**               |

<sup>\*</sup> Rating per module

Prototype 1 is rated at 500 kV and 4.4 kA with a modular design, consisting of four modules connected in series using ac air-blast circuit breakers, and zinc oxide discs for energy absorption [44]. In the laboratory, this prototype design was tested and found to have an internal current commutation time of 12 ms with a current interruption capability up to 5.5 kA [16]. Instead of using air-blast circuit breakers, example prototype 2 was designed using modified ac Sulfur Hexafluoride (SF6) puffer interrupters. This second topology has a comparable internal current commutation time to prototype 1 but was rated and tested at half of the 2.2 kA rated current. The passive oscillation circuit is commonly used as transfer switch or commutation switch in LCC-HVDC, but this design topology with a break time of over 30 ms, and internal commutation time larger than 10 ms does not meet the technical requirement for dc fault clearing application as defined in the Section 4.2.

### 4.3.2. Active Current Injection Circuit Breaker

### 4.3.2.1. Operating Principle and Basic Functionality

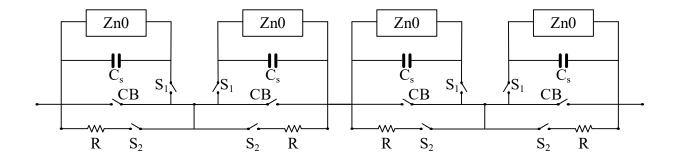

In comparison to passive oscillation dc circuit breakers, active current injection mechanical circuit breakers generate the counter oscillating current by actively switching in a commutation branch of

<sup>\*\*</sup> Value estimated based on references [44] [45]

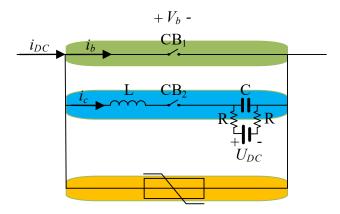

pre-charged capacitor and an inductor using a high-speed switch [16]. Under normal load conditions, referring to Figure 4-6, only the main interrupter CB<sub>1</sub> in nominal current branch is closed while CB<sub>2</sub> remains open. A station service source may be used to provide a negative pre-charged voltage to the capacitor C in commutation branch [39]. When the interrupting process begins, the main interrupter CB<sub>1</sub> is commanded to open in response to a dc fault. Simultaneously, CB<sub>2</sub> is closed, the pre-charged capacitor C is oscillatory discharging through the inductor L in a manner similar to that of a passive oscillation mechanical dc breaker, but with faster and higher successful interruption rate due to a larger oscillation amplitude caused by activity switching a pre-charged capacitor [16] [45] [46].

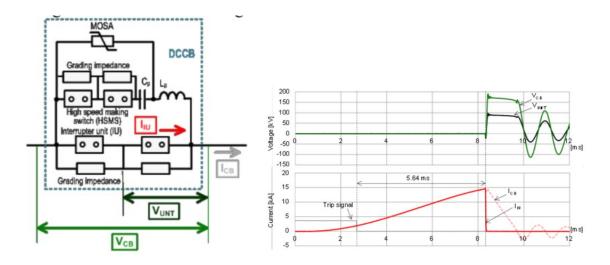

Figure 4-6: Active Injection DC Breaker Operating Principle [38]

The key functional and design distinction opposed to a passive oscillation type is that an active injection scheme imposes a discharging current in the opposite direction and of higher magnitude than the dc current to be interrupted. "Almost instantly, a counter voltage is created" effectively suppressing the fault current to zero noted by Cigré joint working group A3/B4 [16, p. 173]. The process of dc current interruption using an active current injection HVDC CB is illustrated Figure

4-7 [16]. Equations (4.1) to (4.4) are excerpted from [16] [46] and re-stated below to express the dc current injection phenomenon.

$$i_c = \frac{U_{DC}}{\sqrt{L/C}} \tag{4.1}$$

$$f_c = \frac{1}{2\pi\sqrt{L*C}} \tag{4.2}$$

$$\frac{di_c}{dt} = \frac{U_{DC}}{L} cos(\frac{t}{\sqrt{L*C}})$$

(4.3)

$$\frac{dV_b}{dt} = \frac{i_{DC}}{C} \tag{4.4}$$

where:

$U_{DC}$ : pre-charging voltage

*L*: reactance in commutation path*C*: capacitance in commutation path

f<sub>c</sub> : oscillating frequency

i<sub>c</sub> : discharging current

$V_b$ : voltage across the breaker

$i_{DC}$ : dc line current

$i_b$  : current through the circuit breaker  $di_c/dt$  : discharging current rate of change

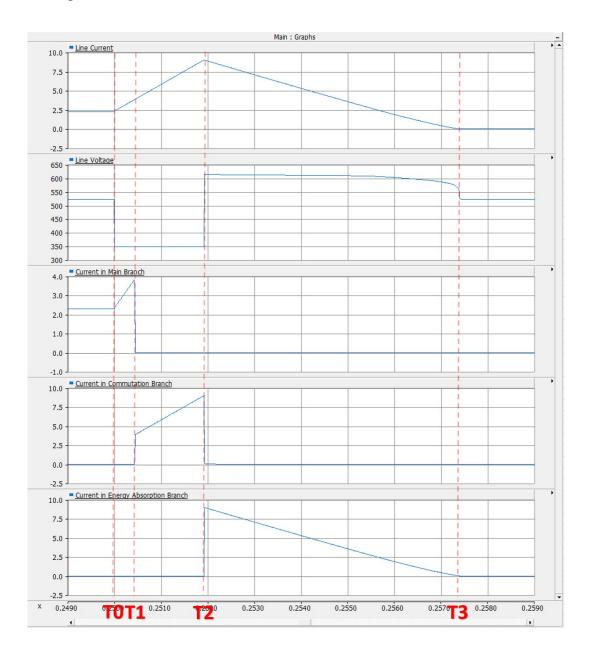

$dV_b/dt$ : transient recovery voltage rate of change