# A GRAPH BASED HEURISTIC CHANNEL ROUTER

by

Cheung-Lai Tse

A thesis

presented to the University of Manitoba

in partial fulfillment of the

requirements of the degree of

Master of Science

in

Electrical Engineering

Winnipeg, Manitoba, Canada © Cheung-Lai Tse, 1987 Permission has been granted to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film.

The author (copyright owner) has reserved other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without his/her written permission.

L'autorisation a été accordée à la Bibliothèque nationale du Canada de microfilmer cette thèse et de prêter oude vendre des exemplaires du film.

L'auteur (titulaire du droit d'auteur) se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation écrite.

ISBN 0-315-37294-X

#### A GRAPH BASED HEURISTIC CHANNEL ROUTER

BY

#### CHEUNG-LAI TSE

A thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements of the degree of

MASTER OF SCIENCE

#### © 1987

Permission has been granted to the LIBRARY OF THE UNIVER-SITY OF MANITOBA to lend or sell copies of this thesis, to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

### **ABSTRACT**

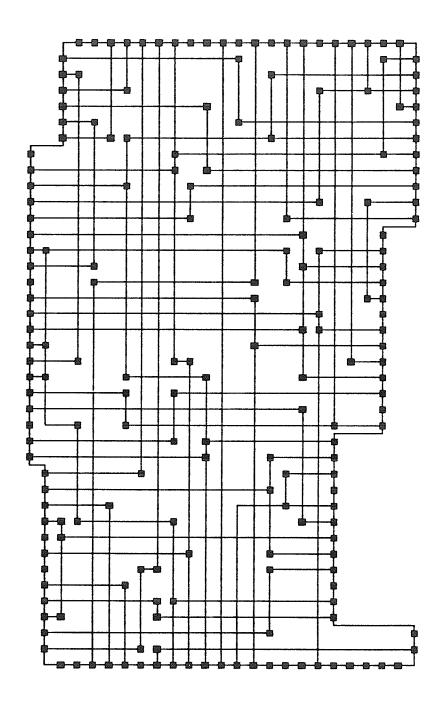

The VLSI channel routing problem is addressed in this thesis. First, major classes of routing algorithms, including maze-running, line-search, and channel routing algorithms, as well as other routing approaches, including hardware routers, expert routers, and the simulated annealing technique are described. Then, the development and implementation of a graph-based heuristic (non-exhaustive search) non-dogleg channel routing algorithm is described. The algorithm is capable of generating optimal or near optimal solutions for an important class of channels that arises frequently in gate array, standard cell, and building block layout designs. The efficiency of the algorithm has been demonstrated through twelve examples obtained from published literature. The algorithm produces optimal non-dogleg solutions for nine of the twelve examples using a single set of parameters. In particular, Deutsch's Difficult Example was routed in 28 tracks, which only a related router of Yoshimuro and Kuh was able to obtain

In order to produce routing solutions at or near channel densities (the least lower bound on channel heights), and to cope with channels with vertical constraint loops, the non-dogleg algorithm was extended to allow doglegging at terminal positions. The extended algorithm routed nine of the twelve examples in density, and Deutsch's Difficult Example in 20 tracks, which is the same as the best published result from channel routers of the same nature (dogleg at terminal positions only). In addition, the extended algorithm is able to handle a large class of channels with vertical constraint loops.

## **ACKNOWLEDGEMENTS**

I wish to express my sincere thanks to my advisor, Dr. W. Kinsner, for his excellent guidance, endurable motivation and consistent support throughout the course of this research, and for his suggestion of this research topic.

I would also like to thank all the students and staff in the Industrial Applications of Microelectronics Centre, Inc., Winnipeg, Manitoba, Canada, for their support throughout my stay in the Centre. In particular, I would like to thank Joe Silva and Scott Handford for their help in using the Optimate PCB layout design package on the Apollo workstation. In addition, I would like to thank Dr. W. L. Kocay for his comment on NP-completeness.

Finally, the partial financial support from the University of Manitoba Graduate Fellowship, the National Sciences and Engineering Research Council (NSERC) of Canada and Manitoba Strategic Research Contract through Dr. W. Kinsner's grants, and the Industrial Applications of Microelectronics Centre, Inc., is gratefully acknowledged.

# TABLE OF CONTENTS

|                                            |                 |                                                 | Page |

|--------------------------------------------|-----------------|-------------------------------------------------|------|

| ABSTRACTACKNOWLEDGEMENTS TABLE OF CONTENTS |                 |                                                 | ii   |

|                                            |                 |                                                 | iii  |

|                                            |                 |                                                 | iv   |

| LI5                                        | LIST OF FIGURES |                                                 |      |

| LIS                                        | I OF T          | ABLES                                           | X    |

| DEF                                        | INITIC          | ON OF TERMS                                     | Xi   |

|                                            |                 |                                                 |      |

| 1.                                         | INTRODUCTION    |                                                 | 1    |

|                                            | 1.1             | VLSI Layout Design                              | 2    |

|                                            | 1.2             | VLSI Layout Strategies                          | 4    |

|                                            | 1.3             | Placement                                       |      |

|                                            | 1.4             | Routing                                         | 10   |

|                                            | 1.5             | Motivation                                      | 11   |

|                                            | 1.6             | Thesis Objectives                               |      |

|                                            | 1.7             | Thesis Structure                                |      |

|                                            | VLS             | I ROUTING ALGORITHMS                            | 15   |

|                                            | 2.1             | Maze-Running and Line-Search Routing Algorithms | 15   |

|                                            |                 | 2.1.1 Maze-Running Routing Algorithms           | 16   |

|                                            |                 | Lee Algorithm                                   | 16   |

|                                            |                 | Extensions of the Lee Algorithm                 |      |

|                                            |                 | Storage Reduction Techniques                    |      |

|                                            |                 | Speed-Up Techniques                             |      |

|                                            |                 | Multi-Terminal Net Extension                    |      |

|                                            |                 | Multi-Layer Extension                           |      |

|                                            |                 | Summary                                         |      |

|                                            |                 | 2.1.2 Line-Search Routing Algorithms            | 33   |

|                                            |                 | Hightower Algorithm                             |      |

|                                            |                 | Line-Expansion Algorithm                        | 43   |

|                                            |                 | Summary                                         | 47   |

|      | 2.2                         | Channel Routing Algorithms                                 |  |

|------|-----------------------------|------------------------------------------------------------|--|

|      |                             | 2.2.1 Loose Routing                                        |  |

|      |                             | Channel Definition                                         |  |

|      |                             | Channel Assignment                                         |  |

|      |                             | Routing Order Determination                                |  |

|      |                             | Optimization                                               |  |

|      |                             | 2.2.2 Detailed Routing                                     |  |

|      |                             | Regular Channel Routing Algorithms                         |  |

|      |                             | Line Packing/Left Edge Algorithm                           |  |

|      |                             | Net Merging Algorithm                                      |  |

|      |                             | Dogleg Channel Router                                      |  |

|      |                             | Greedy Channel Router                                      |  |

|      |                             | YACR-II                                                    |  |

|      |                             | Rectilinear Channel Routing Algorithms                     |  |

|      |                             | Switchbox Routing                                          |  |

|      |                             | Detour                                                     |  |

|      |                             | General Rectilinear Channel Routing                        |  |

|      |                             | MIGHTY                                                     |  |

|      |                             | 2.2.3 Summary                                              |  |

|      | 2.3                         | Other VLSI Routing Approaches                              |  |

|      |                             | 2.3.1 Hardware Routers                                     |  |

|      |                             | 2.3.2 Expert Routers                                       |  |

|      |                             | 2.3.3 Simulated Annealing                                  |  |

|      |                             | 2.2.4 Summary                                              |  |

|      |                             |                                                            |  |

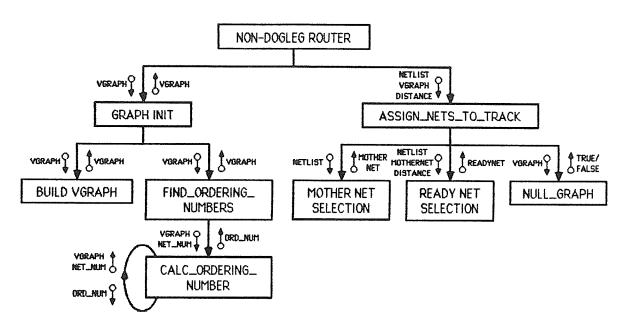

| 111. | A NON-DOGLEG CHANNEL ROUTER |                                                            |  |

|      | 3.1                         | Definitions                                                |  |

|      |                             | 3.1.1 Non-Dogleg Channel Routing Problem                   |  |

|      |                             | 3.1.2 Dogleg                                               |  |

|      | •                           | 3.1.3 Net List Representation of a Channel Routing Problem |  |

|      |                             | 3.1.4 Vertical Constraint Graph                            |  |

|      |                             | 3.1.5 Horizontal Constraint Graph                          |  |

|      |                             | 3.1.6 Density, Ordering, and Channel Height Lower Bounds   |  |

|      | 3.2                         | ***************************************                    |  |

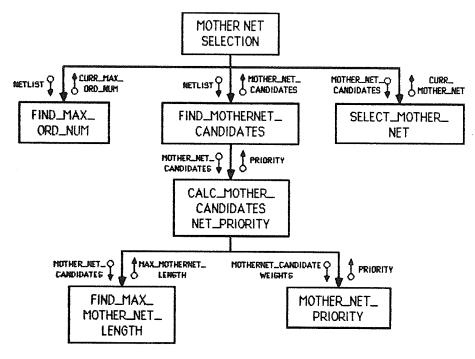

|      |                             | 3.2.1 Mother Net Selection1                                |  |

| APPENDIX B DOGLEG CHANNEL ROUTER PROGRAM LISTING |            |                                                 |             |

|--------------------------------------------------|------------|-------------------------------------------------|-------------|

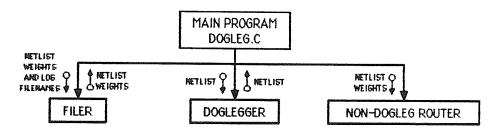

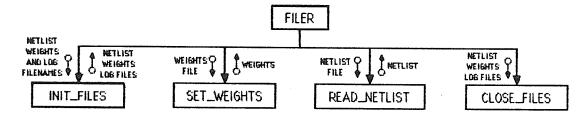

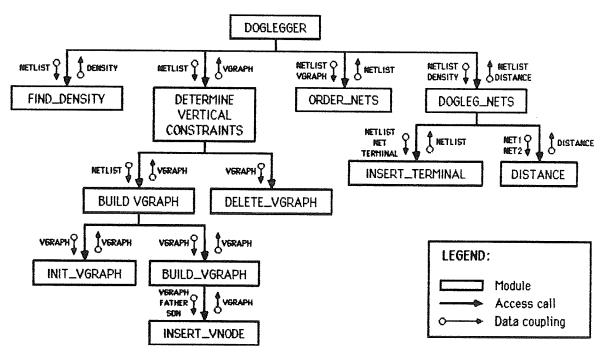

| APP                                              | ENDIX      | A DOGLEG ROUTER PROGRAM STRUCTURE               | ••••        |

| REF                                              | ERENC      | ES                                              | •••         |

| ٧.                                               | CON        | CLUSIONS AND RECOMMENDATIONS                    |             |

|                                                  | 4.7        | Summary                                         | <del></del> |

|                                                  |            | 4.6.1 Applicability of the Algorithm            |             |

|                                                  | 4.6        | Vertical Constraint Loop Handling               | ••••        |

|                                                  | 4.5        | Experimental Results                            |             |

|                                                  | 4.4        | Efficiency of the Dogleg Routing Algorithm      | ****        |

|                                                  | 4.3        | Implementation                                  |             |

|                                                  |            | 4.2.4 Complete Dogleg Channel Routing Algorithm |             |

|                                                  |            | 4.2.3 Net and Terminal Selection                |             |

|                                                  |            | 4.2.2 Net Ordering                              |             |

|                                                  | 4.2        | Dogleg Detailed Channel Routing Algorithm       |             |

|                                                  | 4.1        | Motivation and Tradeoffs of Introducing Doglegs |             |

| IV.                                              |            | LEG EXTENSION                                   |             |

|                                                  | ₩. ſ       |                                                 |             |

|                                                  | 3.7        | DiscussionsSummary                              |             |

|                                                  | ა.ა<br>3.6 | Experimental Results                            |             |

|                                                  | 3.5        | 3.4.3 Execution Time Versus Channel Complexity  |             |

|                                                  |            | 3.4.2 Example 2                                 | ·····       |

|                                                  |            | 3.4.1 Example 1                                 |             |

|                                                  | 3.4        | Efficiency of the Non-Dogleg Routing Algorithm  |             |

|                                                  | 3.3        | Implementation                                  |             |

|                                                  |            | 3.2.4 Track Assignment and Graph Update         | ••••        |

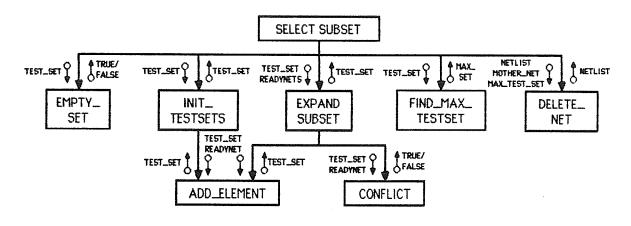

|                                                  |            | 3.2.3 Maximal Subset Selection                  |             |

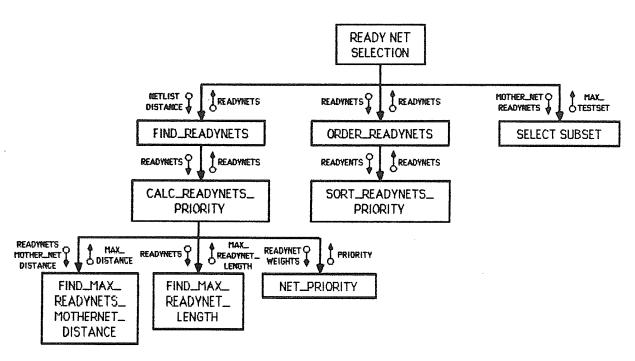

|                                                  |            | 3.2.2 Ready Net Set Creation                    |             |

## LIST OF FIGURES

| <u>Figure</u> |                                                                | <u>Page</u> |

|---------------|----------------------------------------------------------------|-------------|

| 1.            | Lee algorithm routing example                                  | 17          |

| 2.            | Storage reduction techniques                                   | 25          |

| 3.            | Speed up techniques                                            | 28          |

| 4.            | Multi-terminal net routing example                             | 30          |

| 5.            | Multi-layer extension                                          | 32          |

| 6.            | An illustration of definitions used in the Hightower algorithm | 35          |

| 7.            | Hightower algorithm routing example                            | 36          |

| 8.            | An illustration of the escape processes                        | 38          |

| 9.            | Two path refinement techniques                                 | 40          |

| 10.           | Expansion of a line in the upward direction                    | 45          |

| 11.           | Line expansion algorithm                                       | 46          |

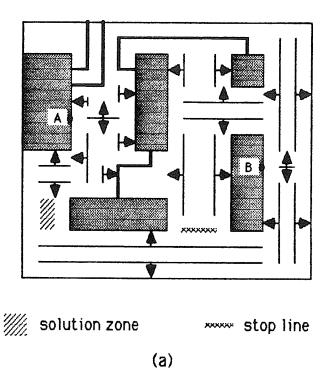

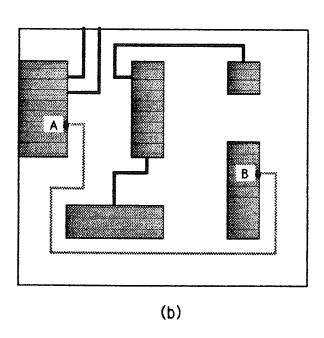

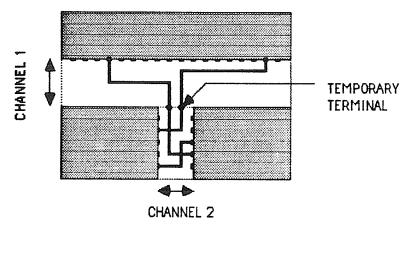

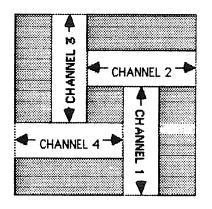

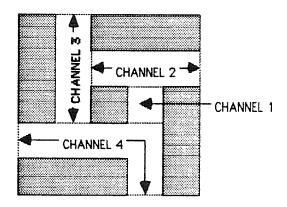

| 12.           | Examples of channel definitions                                | 51          |

| 13.           | Channel ordering                                               | 54          |

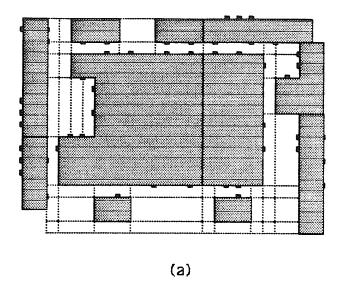

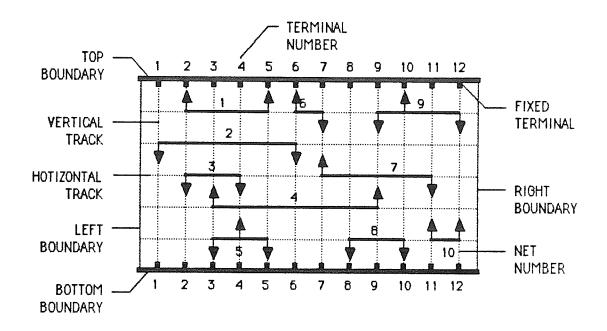

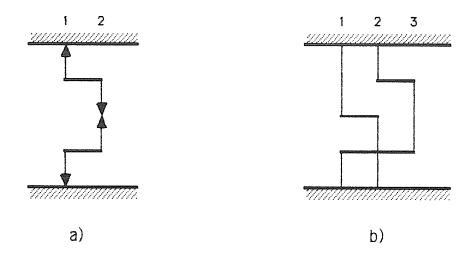

| 14.           | An illustration of the channel routing model                   | 57          |

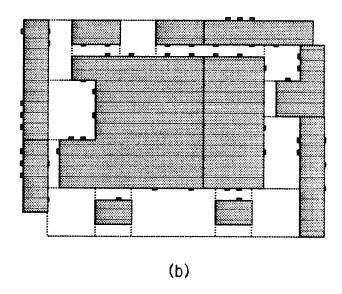

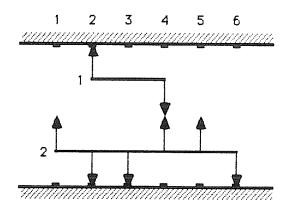

| 15.           | Channel routing illustrations                                  | 58          |

| 16.           | Switchbox routing                                              | 69          |

| 17.           | General rectilinear channel routing                            | 73          |

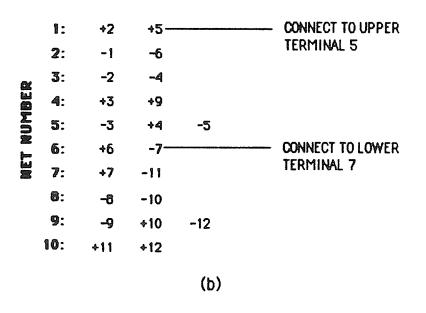

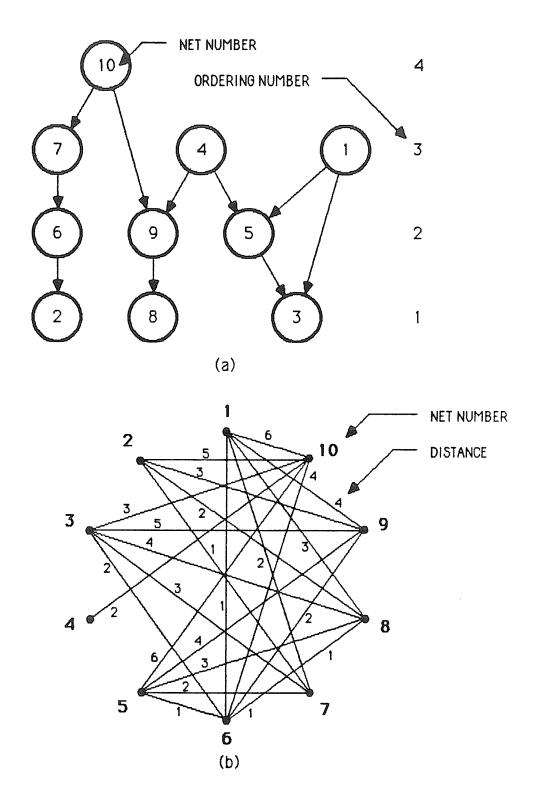

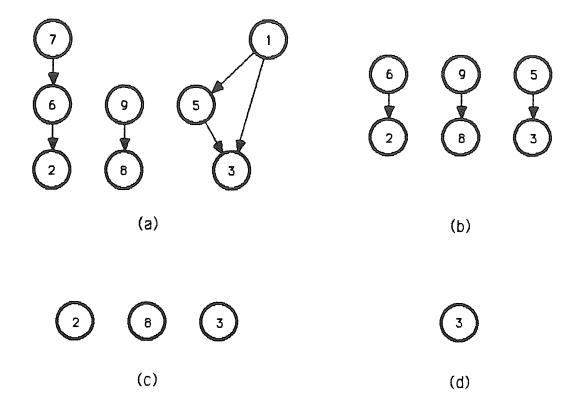

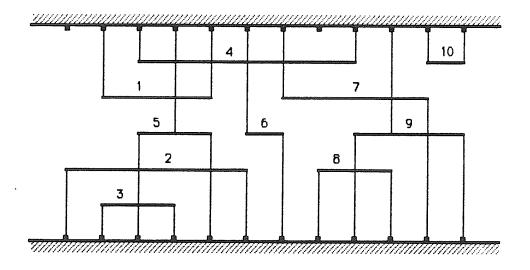

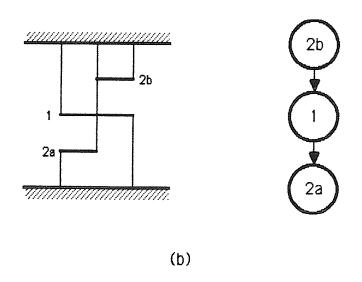

| 18.           | Channel Representations                                        | 92          |

| 19.           | Constraint graphs for the channel in Figure 14                 | 96          |

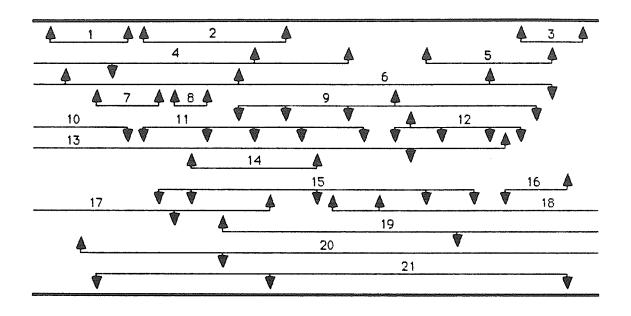

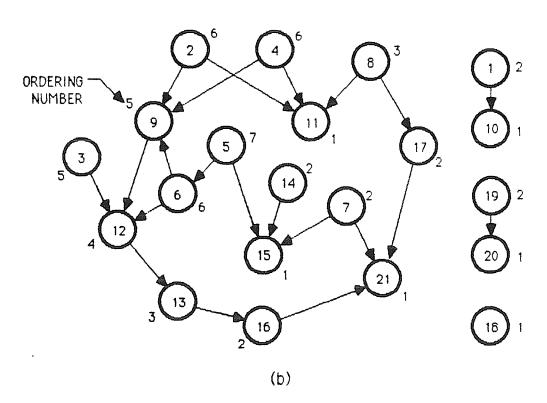

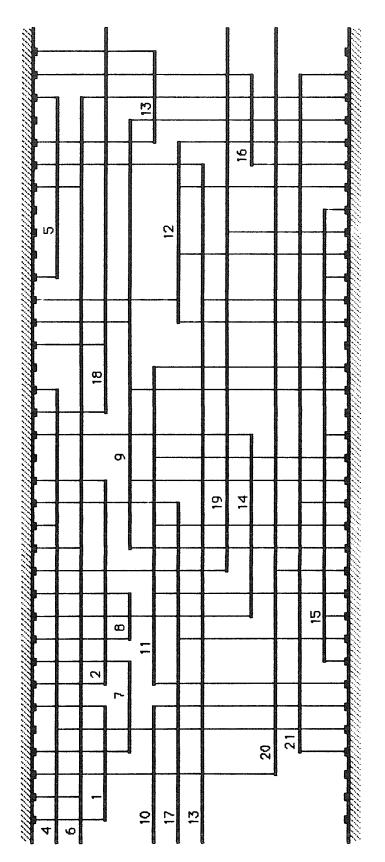

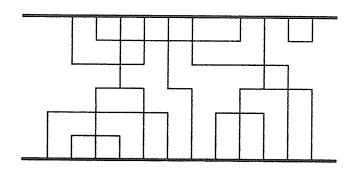

| 20.           | Reduced vertical constraint graphs for Example 1               | 108         |

| 21.         | Realization of Example 1                                  | 1  |

|-------------|-----------------------------------------------------------|----|

| 22.         | Representation and vertical constraint graph of Example 2 | 1  |

| 23.         | Realization of Example 2                                  | 1  |

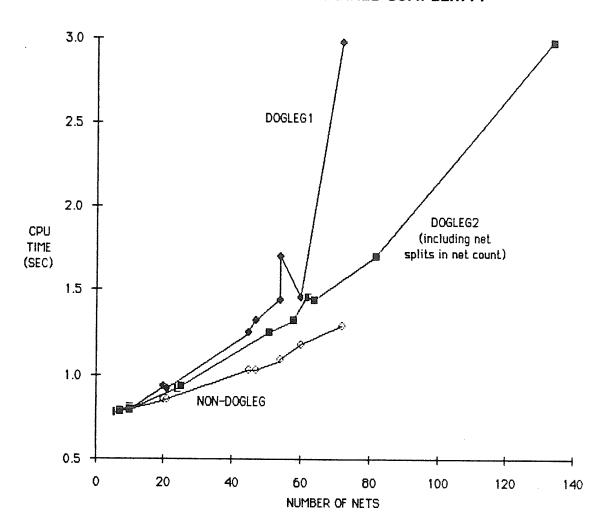

| 24.         | CPU time vs. channel complexity                           | 1  |

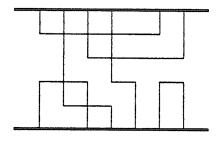

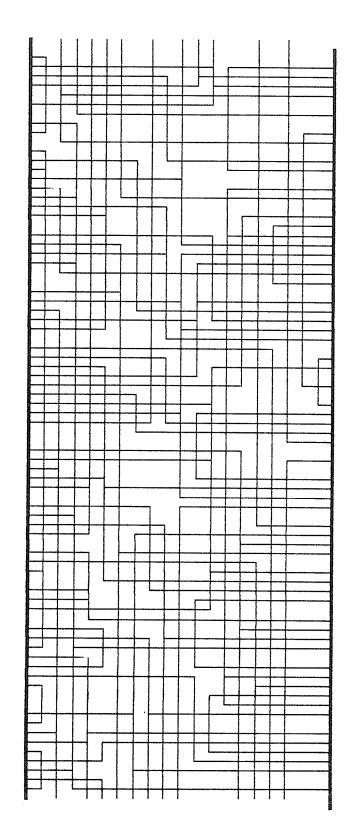

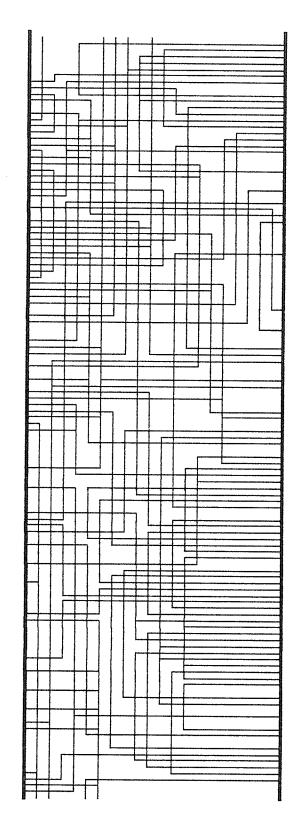

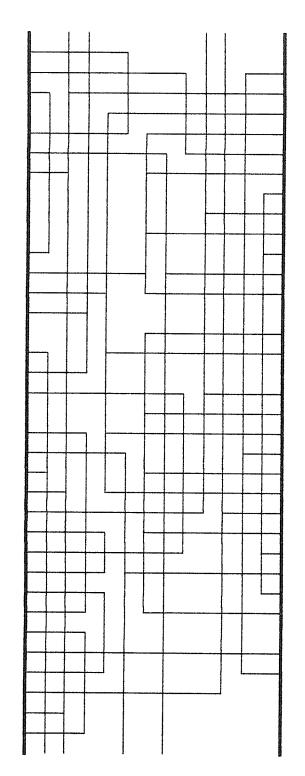

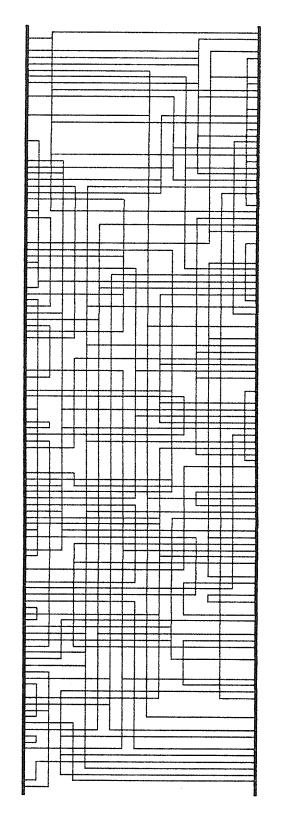

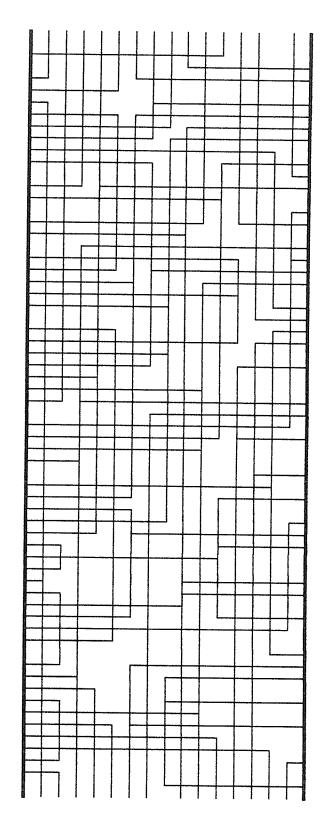

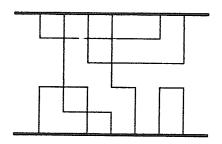

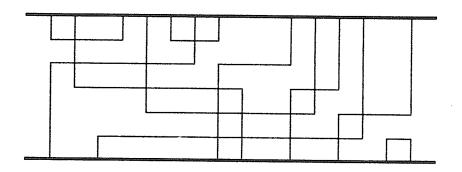

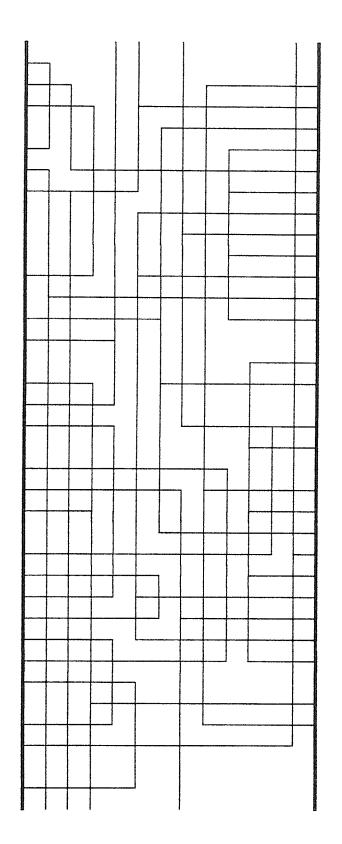

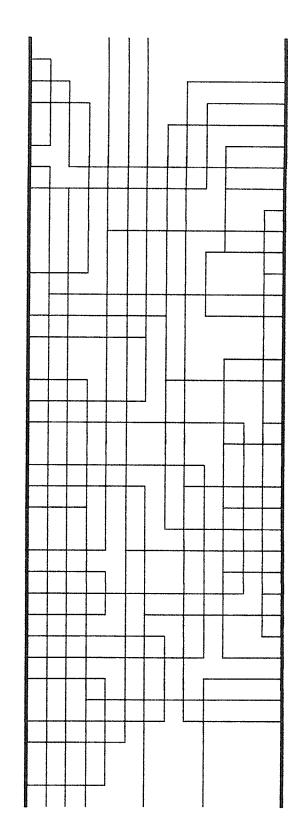

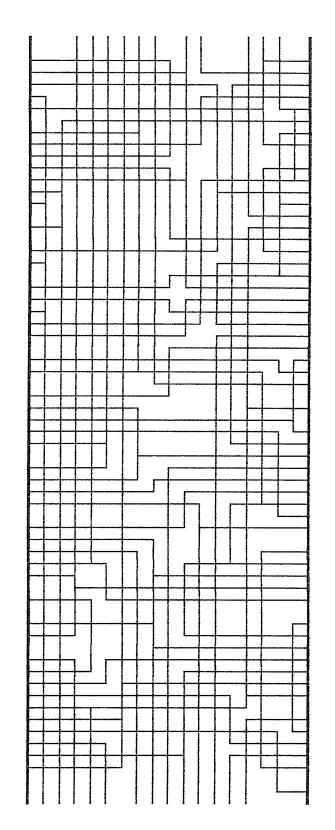

| 25.         | Non-dogleg realization of Example 1                       | 1  |

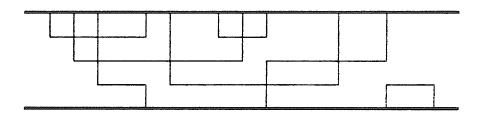

| 26.         | Non-dogleg realization of Example 2                       | 1  |

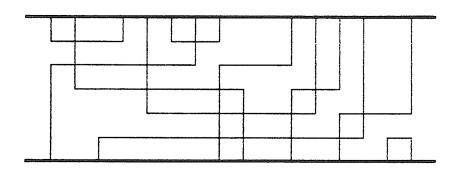

| 27.         | Non-dogleg realization of Example 3                       | 1  |

| 28.         | Non-dogleg realization of Example 4                       | 1  |

| 29.         | Non-dogleg realization of Example 5                       | 12 |

| <b>3</b> 0. | Non-dogleg realization of Example 6                       | 12 |

| 31.         | Non-dogleg realization of Example 7                       | 12 |

| <b>32</b> . | Non-dogleg realization of Example 8                       | 12 |

| 33.         | Non-dogleg realization of Example 9                       | 12 |

| 34.         | Non-dogleg realization of Example 10                      | 12 |

| <b>3</b> 5. | Non-dogleg realization of Example 11                      | 12 |

| <b>3</b> 6. | Non-dogleg realization of Example 12                      | 12 |

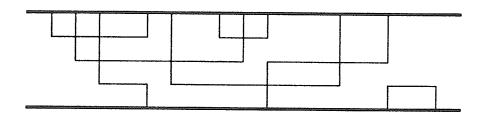

| 37.         | An example illustrating the advantages of doglegs         | 1  |

| <b>3</b> 8. | An example unroutable without dogleg                      | 13 |

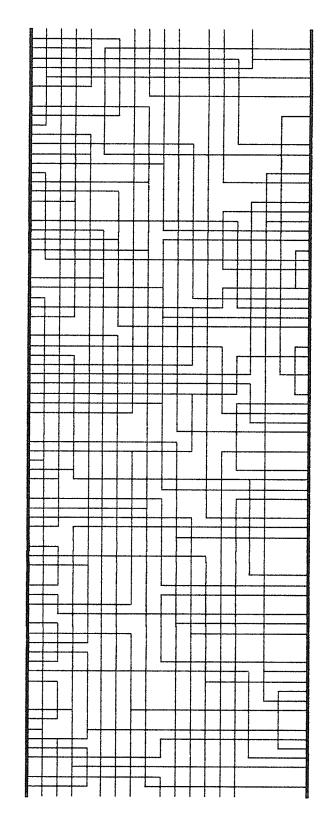

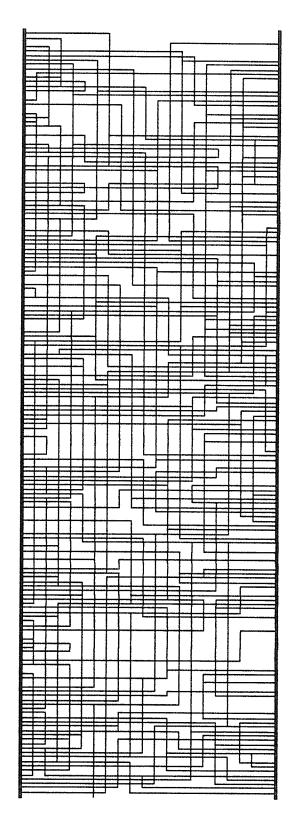

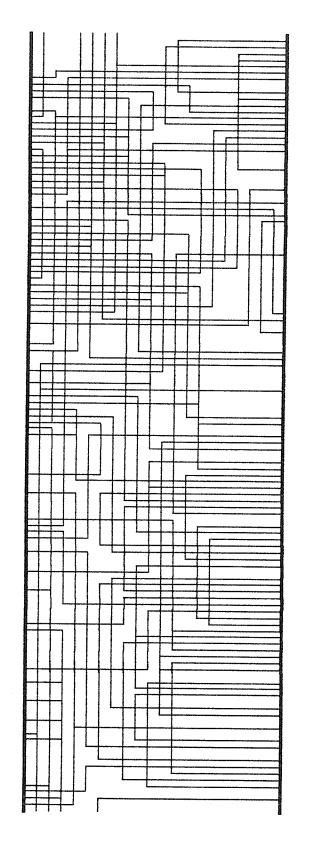

| <b>39</b> . | Dogleg realization of Example 1                           | 1  |

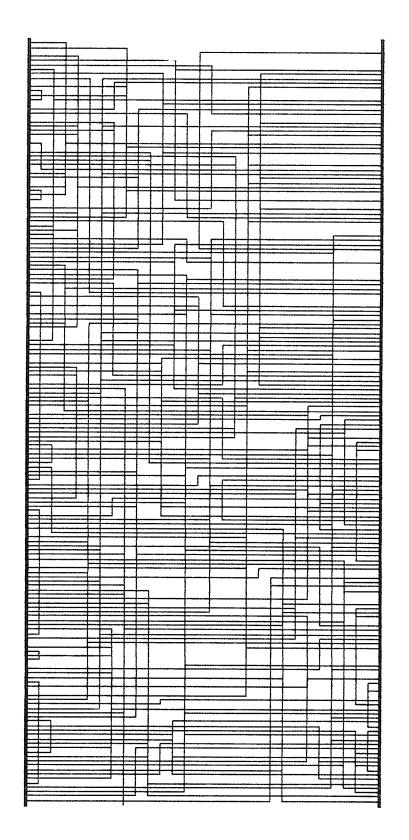

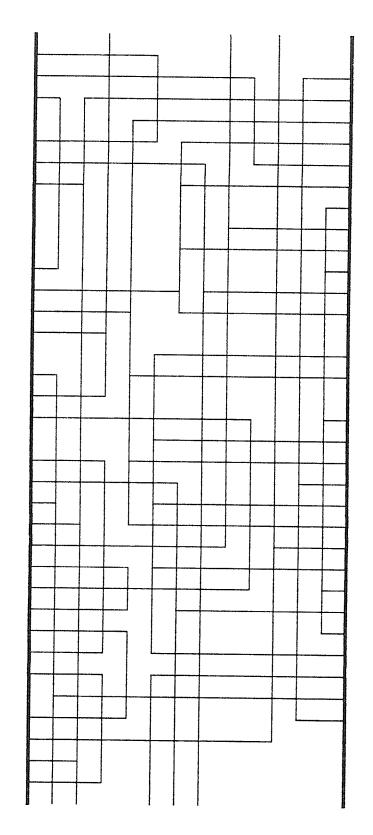

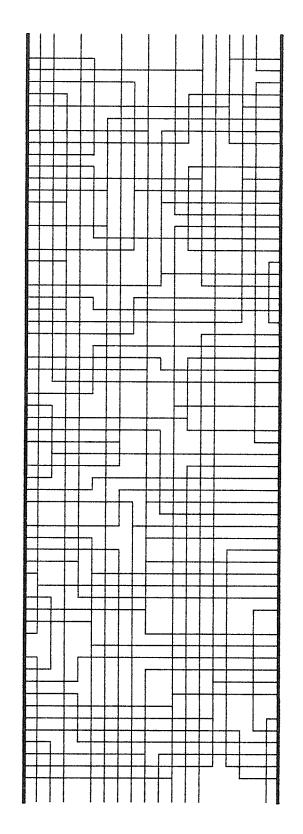

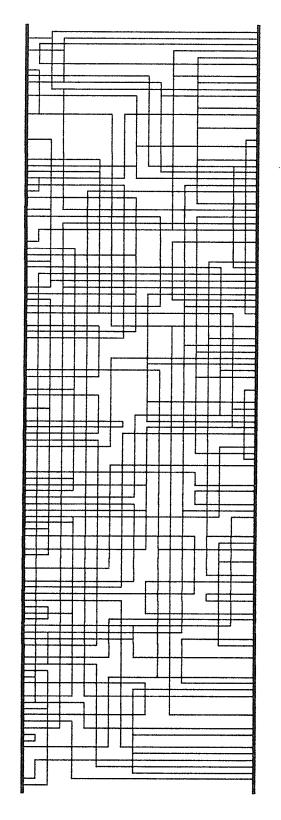

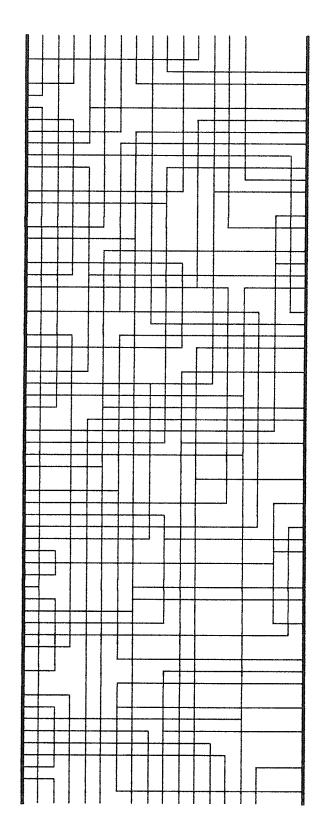

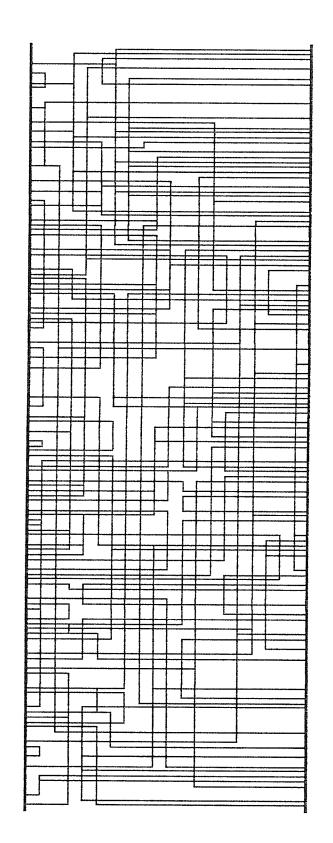

| <b>4</b> 0. | Dogleg realization of Example 2                           | 1  |

| 41.         | Dogleg realization of Example 3                           | 1  |

| <b>42</b> . | Dogleg realization of Example 4                           | 1  |

| 43.         | Dogleg realization of Example 5                           | 14 |

| 44.         | Dogleg realization of Example 6                              | 148 |

|-------------|--------------------------------------------------------------|-----|

| <b>4</b> 5. | Dogleg realization of Example 7                              | 149 |

| <b>4</b> 6. | Dogleg realization of Example 8                              | 150 |

| <b>4</b> 7. | Dogleg realization of Example 9                              | 151 |

| 48.         | Dogleg realization of Example 10                             | 152 |

| <b>49</b> . | Dogleg realization of Example 11                             | 153 |

| 50.         | Dogleg realization of Example 12                             | 154 |

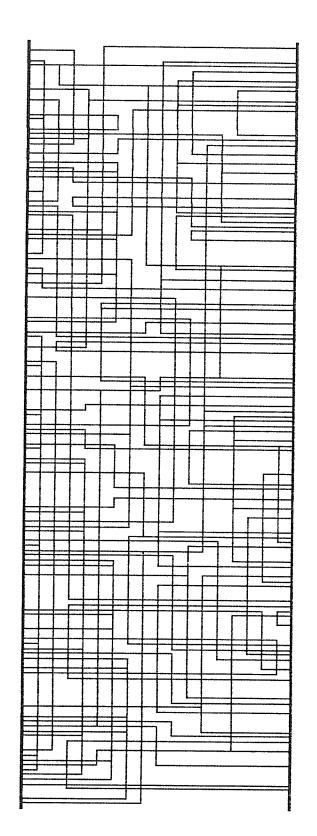

| 51.         | Dogleg realization of Example 13                             | 158 |

| <b>5</b> 2. | Dogleg realization of Example 14                             | 159 |

| <b>5</b> 3. | A channel unroutable by the new dogleg channel router        | 161 |

| 54.         | An illustration of constraining and unconstraining terminals | 161 |

## LIST OF TABLES

| <u>Table</u> |                                                                | <u>Page</u> |  |

|--------------|----------------------------------------------------------------|-------------|--|

| 1.           | Routing of Example 2                                           | 113         |  |

| 2.           | Characteristics and resulting channel heights of the Examples  | 117         |  |

| 3.           | Comparison of net ordering schemes                             | 139         |  |

| 4.           | Results of the new dogleg channel routing algorithm            | 144         |  |

| 5.           | Results of the new dogleg channel router with no density check | 157         |  |

### **DEFINITION OF TERMS**

Algorithm

An algorithm is a finite sequence of instructions, each of which has a clear meaning and can be performed with a finite amount of effort in a finite length of time [AHO83].

greedy A greedy algorithm attempts to obtain the optimal solution by selecting at each step the option that is locally optimal. The solution is not necessarily optimal.

heuristic A heuristic algorithm utilizes rules or experience from similar types of problems to quickly produce good but not necessarily optimal solutions.

**Building Block** With the building block design method, circuit modules are grouped into blocks. Placement and routing are performed in the block level only.

**Channel** A routing area formed between circuit modules.

density The maximum number of wire traces that crosses a vertical track in a channel. This is the least lower bound on the channel height.

ordering The maximum ordering number in vertical constraint graph of the channel. This is a lower bound on the channel height.

rectilinear A general rectilinear channel is a channel that has a rectilinear boundary (not necessarily rectangular) and terminals located on any or all sides.

regular A regular channel is a channel that has a rectangular boundary and terminals located on two opposite sides only.

switchbox A switchbox is a special rectilinear channel that has a rectangular boundary and terminals located on any or all four sides.

**Circuit Layout** A circuit layout is the physical representation of the corresponding structural representation of a circuit.

**Doglegging** Doglegging is the bending of an otherwise straight wire.

Expert System An expert system is a computer program that embodies the expertise of one or more experts in some domain and applies this knowledge to make useful inferences for the user of the system [HAY83].

Gate arrays consist of a matrix of identical components or functional elements (cells) that has passed through all the steps in the fabrication process except the final interconnection stage (metalization).

**Graph**

A graph consists of a set of points called vertices, and lines connecting the points, called edges.

directed

A directed graph, G=(V,E), consists of a set of vertices V and a set of edges E, where the edges are ordered pairs of vertices (v,w) or  $v\rightarrow w$ .

undirected An undirected graph, G=(V,E), consists of a set of vertices V and a set of edges E, where the edges are unordered pair of vertices.

Horizontal Constraint Graph An undirected graph representing the horizontal constraint relationships between the nets in a channel.

Layout Compactor A layout compactor spaces the circuit elements and interconnections to pack the circuit element as tightly as possible without violating constraints defined by the user and the design rules.

MIMD

Multiple Instruction Multiple Data. A mode of parallel processing where each node processor follows its own instruction stream.

Net

A net consists of a set of terminals and connections that makes the terminals electrically common and isolated from other nets or circuit modules. A net is realized as a collection of wire segments connecting the set of specified terminals in the layout design process through

the routing process. Net = {terminals, connections} [KIN86a].

**Net List**

A net list is the list of all the nets and their associated terminals in a circuit.

NP-Completeness A decision problem is a problem with a yes or no answer. A polynomial (P) problem is a decision problem for which there is an algorithm which will solve (i.e., answer yes or no) any instance of the problem in a polynomial number of steps. A certificate for a decision problem whose answer is yes is a character string which demonstrates the answer (e.g., for the problem: Is there a routing with channel height \( \cdot 20\), a certificate could be the actual routing). A non-deterministic polynomial (NP) problem is a decision problem such that for every instance of the problem whose answer is yes, there is a certificate which can be verified in a polynomial number of steps. Every P problem is also an NP problem. problem is NP-complete if it is an NP problem and all NP problem is polynomial-time reducible to it. The algorithm for an NP-complete problem is universal, in that all other NP problems can be solved using such an algorithm. An NP-complete problem is very hard and probably has no polynomial time algorithm [SHI86, PAP821.

Overflow

An overflow is a connection that cannot be routed under the given routing constraints (specification) [KIN86a].

Placement

Placement is the process of arranging all the components within a two-dimensional area such that the placement configuration will facilitate the routing process [KIN86a].

**Pseudo Language** A pseudo language is a combination of the constructs of a programming language together with informal English statements [AHO83].

Routing

Routing is the process of converting the set of intended connections into physical wires within the routing region using one or more routing layers, provided that physical and electrical constraints are satisfied [KIN86a].

detailed

Detailed routing is the last step of the complete routing process. It defines the exact geometry of the wires in terms of layer, via, and track assignments.

loose

Loose routing (or global routing) is the preliminary step of the complete routing process. It calls for a routing plan in which each net is assigned to particular routing regions without specifying the exact geometry of the interconnecting wires.

**Routing Algorithm** A routing algorithm is a method of tracing wires on a routing medium according to the specified constraints [KIN86a].

maze-running A class of sequential methods of tracing wires along an expanding area, from the starting point to the end point. A path between the two points can always be found if such a path exists. The method was first introduced by Lee.

line-search A class of sequential methods of tracing wires along straight lines until a blockage is encountered. The method was originally developed by Hightower.

channel A class of sequential methods of tracing wires along channels formed by modules or components. The first phase of the channel routing algorithm is a global assignment of nets to channels, followed by the second phase of local assignment of nets to tracks within the channels. The method was first introduced by Hashimoto and Stevens.

**Router** A router is the software or hardware implementation of a routing algorithm.

**expert** An expert router utilizes an expert system to perform routing. See also Expert System.

**grid** A grid router performs routing on a grid. Wire segments are constrained to lay only on the grid.

**gridless** A gridless router performs routing without the constraint of a grid.

hardware A hardware router implements a routing algorithm in hardware.

**Routing Void** A routing void is the area in the routing region where traces cannot be placed.

SIMD Single Instruction Multiple Data. A mode of parallel processing where instructions are broadcasted to all node processors. Thus each node processor executes the same instruction but operates on different local data.

**Simulated Annealing** A multivariate optimization technique analogous to the cooling of a fluid into a low energy state.

Standard Cell The standard cell design method is based on a library of predesigned functional cells, each of which has been fully characterized in both electrical and performance terms.

**Terminal** A terminal is the endpoint of a connection [KIN86a].

Trace

A trace is the physical representation of a connection that makes different points in a circuit electrically common. A trace can only be defined on a single layer.

To connect traces on different layers vias are required.

Traces and vias together constitute wires [KIN86a].

**Vertical Constraint Graph** A directed graph representing the vertical constraint relationships between the nets in a channel.

Vertical Constraint Loop A directed cycle in the vertical constraint graph. A channel with vertical constraint loops is unroutable without doglegs.

Via

A via is a feed-through or a contact where wire segments on different layers are connected together. It contributes to the creation of wires.

Wire

A wire is the physical realization of a net which makes different points in a circuit electrically common. A wire includes at least one trace and two terminals. If the traces are located on different layers, the wire also includes at least one via. Wire = {terminals, traces, vias} [KIN86a].

# CHAPTER I INTRODUCTION

The design of electronic circuits can, in general, be considered as the transformation of a behavioural description of the circuit concepts into a physical description for implementation. For complex systems such as very large scale integrated circuits (VLSI), the transformation process is achieved by a hierarchical decomposition from behavioural descriptions to structural descriptions, then to physical descriptions.

A behavioural description is the textual or mathematical description of a system. It gives a precise definition of the system behaviour with no concern in its actual implementation. For example, the addition of two multi-digit binary numbers A and B could be described behaviourally as A+B. However, how the operation is actually implemented, for example, whether sequentially with a one bit adder or simultaneously with a multi-bit parallel adder, is not described. It is the structural description that defines the translation of the behavioural description into interconnecting functional blocks in the form of, for example, data-flow diagrams and structural charts. A more detailed structural description could include circuit schematics for the hardware, and software description language specifications for the software and firmware. With the higher level descriptions specified, the physical representation of a system is the final stage of the design by which structures are translated into physical layouts. Many different form of layout styles are possible. Common methods include the use of standard components mounted on printed circuit boards (PCBs) or surface mount boards (SMBs), and

semi-custom or full-custom integrated circuits fabricated on silicon dies.

Continuing advances in integrated circuit technology are driving circuit densities to higher and higher levels. This ever increasing circuit complexity has rendered the already tedious, error-prone, and time-consuming layout process almost impossible to be handled manually. Compounding the problem is the requirement of very high quality layouts that must consider complex physical constraints such as ringings, crosstalks [WEX85, POL86], current surges and heat dissipations [KIN86c]. One typical example of manual layout design was the Z8000 microprocessor. In its design, very little computer aids were used. As a result, 50% of the whole design effort, or 6600 man-hours, was devoted to the layout design phase alone [RIC80].

As the design gets more complex, the design effort and turnaround time increase at a higher rate, particularly in the layout design phase. Consequently, a large amount of effort has been devoted to providing computer aids to the human designer with the layout design problem. Such layout design aids fall into the general category of computer-aided design (CAD) and computer-aided engineering (CAE) tools.

#### 1.1 VLSI Layout Design

The design of VLSI circuits, being a branch of electronic circuit design, involves the process of transforming a given circuit behaviour into a circuit laid out on a silicon die. The first phase of this transformation, as with any electronic designs, is the behavioural design phase. It converts circuit concepts into formally defined behavioural descriptions. The second phase of the transformation is the structural design phase in which a network of

interconnecting components or modules is designed realizing the specified behaviour. The modules may be large functional blocks such as ALUs or PLAs, logic gates such as NAND or NOR gates, or even isolated transistors or resistors. The interconnections, on the other hand, are usually specified as nets connecting terminals of the modules. Note that at this stage of the design, modules and interconnections are still conceptual units. It is in the final physical or layout design phase that the network of functional blocks is mapped onto the surface of a silicon die giving the precise geometry and position of its constituent modules and interconnecting wires.

The VLSI layout problem can be described as follows: A number of circuit modules are to be arranged in a given area such that there are no overlaps between the modules, and all interconnecting terminals are to be connected by mutually noninterfering wires laid out in designated routing regions. More precisely, the modules of a given circuit are to be placed within a two dimensional region in such a way that each module takes on a unique area in the region and the arrangement of the modules is such that it facilitates the routing of interconnections. Furthermore, for a given interconnection list (net list) and module placement configuration, all electrical connections must be converted into physical connections within designated routing regions satisfying design constraints including electrical constrains such as maximum signal delays and design rule constraints such as minimum feature clearances.

The layout design problem, like many design automation problems such as logic synthesis, testing, and partitioning, is widely known to be NP-complete [UED86, KIN87]. The optimal solution to this problem requires running times that grows exponentially with the size of the problem. It is

highly unlikely that an efficient polynomial time algorithm exists [BRE76]. With circuit complexities pushing into upwards of a million transistors per die, the layout design problem has grown beyond the capability of today's computers. For example, just arranging the modules of a 20,000 gate circuit using the commercial placement program COSMIC [SCH83] requires over 300 CPU hours [UED86], a time approaching the mean time to failure of many complex computing systems. Even the recent increases in computing power coupled with efficient and reliable software still cannot guarantee that the densest VLSI circuits can be laid out completely in a reasonable time and storage [LUD83].

#### 1.2 <u>VLSI Layout Strategies</u>

Various simplification methods have been used to reduce the VLSI layout problem into more manageable sub-problems. Traditionally, the method of partitioning is used to simplify the problem by dividing the layout design process into two separate steps, namely placement and routing. In the placement step circuit modules are assigned to physical locations on the die. Then, in the routing step nets are realized as wire traces connecting the terminals. Both of these subproblems, though simpler, are still NP-complete [SHI86]. But the overall reduction in complexity is significant enough to allowed many previously unmanageable designs to be tackled.

Partitioning of the layout design problem into two separate and disjoint steps has, however, necessitated the use of iterative processes involving repeated application of the placement and routing steps. The reason for this cyclic phenomenon is the intrinsic mutual dependency of the

placement and routing processes. If a placement configuration does not allow a reasonable level of routing completion, it would be necessary to repeat the placement process and then re-do the routing based on the new placement configuration. This cycle must be repeated until an acceptable layout is generated.

So far, most computer-aided layout systems have taken this separate placement and routing approach. However, as both steps are so critically dependent on each other, there are problems with such an iterative method, particularly as the scale of the design extends more into the VLSI area:

- Placing the modules with no knowledge of how the routing process will

route the interconnecting wires makes the placement process

particularly difficult to generate the optimum placement configuration.

- Dividing the layout process into two disjoint steps with no communication between the placement and the routing processes unnecessarily increases the number of iterations required. The inability for the routing process to provide feedbacks to the placement process in exactly why routing was failed in case of an incompletion essentially makes the placement process a blind process. The placement process does not know what is required by the routing process. When routing fails, it simple generates another placement configuration and hope that it will find an acceptable solution in a reasonable number of trials.

In light of these problems, attempts have been made to combine the placement and routing process [LOO79, SOU79, BUR85, SZE86]. However the research is still in its infancy and no significant results have been reported. The attempts reported so far have been primarily concerned with highly

regular structures such as gate arrays, and the improvements in the layout were too small to justify the enormous running time [SOU79].

In addition to the above method of partitioning the VLSI layout design process into placement and routing, another approach is to begin with a rough placement of the circuit modules and routing of the interconnections, and then perform a layout compaction to optimize the layout. The initial rough layout could be the result of a symbolic (stick) layout design [MEA80] to be translated into final mask layout, or the result of a placement/routing process requiring a further optimization. In any case, once the initial design is completed, a compaction process is applied to optimize the design. In this approach, the initial rough placement configuration represents only the topological arrangement of the modules, that is, the relative positions of the modules only. The actual physical placement of the modules are determined by the compactor according to the process design rules and user defined constraints such predefined module locations. In the compaction process, the interconnecting wires are considered as stretchable. That is, without changing the topology of the routing, the compactor is free to shrink or stretch any wire [LIA83].

Most compactors use minimum area or maximum density as their main goal. In other words, their goal is to achieve the minimum die size for a circuit given the design rules, the components, the interconnections, and the user defined constraints. Although minimum area may not be the only requirement, it well reflects many others, for example minimum signal delays and maximum yield.

The general layout compaction problem has also been proven to be

NP-complete [SAT83, TAY84]. A mathematical representation of the layout compaction process is: minimize the product, Area = Max(x)Max(y), where x and y are horizontal and vertical dimensions of the die. This formulation results in a quadratic problem that is very difficult to solve [GAR79]. In fact, for all but very small cases, its solution is unreasonable on today's computers. To make the problem manageable, the following assumption is made: minimization of the layout is achieved when the layout in each dimension is minimized. The implication here is that the original twodimensional compaction problem can be decomposed into two one-dimensional problems. each of which can be solved independently using simpler algorithms. The new formulation results in a linear problem that minimizes the vertical or horizontal dimension subject to the given constraints. But, because the layout design problem is two-dimensional, and because linear compactors minimize each dimension separately, the order in which compaction is performed, that is, a horizontal compaction first or a vertical compaction first, becomes important [TAY84].

Encouraging results have been reported with the compaction approach to layout design [OHT86]. However, this layout style is still relatively new and no significant results have been reported. Therefore, not until better compaction algorithms, particularly two-dimensional compaction algorithms, are developed, this method remains primarily as a research.

In this thesis, the common approach of partitioning the layout design problem into placement and routing will be used. In the next two sections, a brief overview of the placement and routing process will be presented.

#### 1.3 Placement

In general, VLSI placement is the process of arranging all circuit modules within the die area such that the resulting placement configuration will facilitate the routing process [KIN86a]. Although the modules are placed on the die according to a number of constraints such as heat dissipations and signal crosstalks, the main objective of the placement process is to generate a placement configuration that would allow 100% routing within the given area [SOU81]. Other constraints represent merely secondary objectives that impose additional requirements on how some modules must be placed. For example, due to heat dissipation considerations some modules may have to be placed in certain fixed positions, or in order to reduce signal crosstalks some modules may have to be placed next to some specific modules. But the ultimate objective is still to generate a 100% routable placement configuration that satisfies those constraints. Such an objective is, however, not mathematically well defined. It is very difficult to predict whether 100% routing can be achieved without performing the actual routing.

To access the quality of a placement configuration, pre-routing (post-placement) analysis schemes and routability indicators have been reported in literature [S073, F0S75, HEL77, KON86, SAS86]. Although they usually do not require as much running time as the actual routing process, a comprehensive analysis still requires an appreciable amount of time. Therefore, such analyses are normally used to access the quality of the final placement configuration only and not the intermediate configurations. In particular, it is commonly used to choose between alternative placement configurations, or to identify congested areas so that they can be avoided early in the routing process.

In order to guide the placement process towards a final solution, a simplified objective function is used. The assumption is that if the simplified objective function is improved, the routability is also improved. Various simplified objective functions have been proposed. The three most representative ones are the total routing length, the maximum cut line, and the maximum density [GOT86].

Regardless of the specific objective function selected, most of the placement algorithms can be classified as either constructive or iterative [HAN72, SOU81, GOT86]. Constructive algorithms produce a solution using heuristic rules, often in a sequential and deterministic manner [GOT86]. Iterative algorithms, on the other hand, produce a solution by successive modification of the initial solution. In most CAD/CAE layout design systems, algorithms from both of these classes are employed. Usually an initial solution is obtained using a constructive algorithm and the solution is improved gradually with an iterative algorithm.

For constructive placement algorithms the placement configuration is formed by adjoining unplaced modules to the set of placed modules. One by one, the unplaced modules are selected and positioned in the partially formed placement configuration. Once a module is positioned, it will not be moved again. An example of constructive placement is the clustering algorithm: for each unplaced module a measure of the expected number of interconnections to the placed modules is computed and the one with the largest value is selected for placement.

Iterative placement algorithms, on the other hand, improve upon a placement configuration by applying small local changes. Typically a subset

of modules is selected and deterministically repositioned until the best configuration is found. A widely known algorithm is the force directed placement method, where the connections between modules are interpreted as springs that stretched out due to displacements between the modules. The placement configuration is then pulled together by successively reducing the forces of connections between modules using techniques such as a pair-wise exchange of modules.

Using whichever technique, once the modules are placed, the next step in the layout design process is to route the interconnections. In the next section, a brief overview of the routing process will be presented.

#### 1.4 Routing

Routing is the process of converting interconnections into wires within the designated routing regions according to constraints such as maximum wire lengths [KIN85]. The interconnections of module terminals, usually specified in the form of a net list, are made through one or more routing layers in the designated routing regions. Generally, two routing layers are used with vertical and horizontal traces on alternate layers. A physical wire changes direction by means of a via at the intersection of a horizontal trace and a vertical trace.

Many routing algorithms have been developed in the past three decades. The first recognized algorithm was developed by Lee in 1961 [LEE61]. The Lee algorithm is actually the shortest path algorithm by Moore [MOO59] applied to a grid structure representing the wiring space. Since Lee's original paper, a large number of extensions and variations have been published. These

algorithms are often referred to as grid expansion or maze-running algorithms due to their similarity to finding an entrance-to-exit path in a grid-structured maze.

Even though maze-running algorithms were created before the integrated circuits era and has been applied primarily to printed circuit board design, it is still used in many current VLSI layout design systems. This is due to the generality of the algorithm and the guarantee of finding a path if one exists. The main disadvantages of the Lee type maze-running algorithms lie in their large demand on memory and running time, and their inherent sequential nature of routing one net at a time. Such inherent negative features of the maze-running algorithms have given rise to other classes of routing algorithms. In the next chapter, a more detailed description of maze-running, line-search, and channel routing algorithms will be presented.

#### 1.5 Motivation

The size of the resulting layout has always been a major concern in VLSI design. Smaller layouts are less expensive and may exhibit better performance. An over-sized die has several adverse effects on both the cost and the performance of an integrated circuit:

1. A larger die with modules placed farther apart requires longer interconnecting wires. As gate delays are becoming shorter, especially in very high speed integrated (VHSI) circuits using such technologies as emitter coupled logic (ECL) and Gallium Arsenide (GaAs), signal delays due to excessively long interconnecting wires is becoming an increasingly significant factor.

- With a larger die size the number of circuits that can be fabricated on a wafer is reduced. Hence, the cost per die is increased.

- 3. As the number of functioning circuits per wafer decreases exponentially as the die size increases [GOT86], a larger die size implies a lower probability of a circuit functioning, a lower yield, and hence a higher cost.

It is, therefore, obvious that the larger the die size the poorer the performance and the higher the manufacturing cost.

In order to make efficient use of the available die area, modules of active devices and interconnecting wires compete with each other for space on the die surface. It has been observed that wiring can occupy more than half of the die area. Moreover, dead space containing no usable devices or wirings due to improper module placement and interconnection routing represents a major waste of precious die area. Therefore, in order to minimize the die size both the routing space and the dead space must be minimized.

Currently available CAD/CAE tools for VLSI layout design tend to use more die area than actually needed. In other words, they necessarily waste die space. Automatic layouts still cannot compete with manual layouts as far as the die size is concerned. This is because an experienced designer can understand the given design and find a more compact layout using his knowledge and intuitions. However, due to the extreme complexity of VLSI designs and a world shortage of skilled designers, in order to complete a design in a reasonable time and cost, CAD/CAE tools are indispensable despite their present inadequacies. In fact, it is widely recognized that the greatest impediment to the successful use of VLSI technology is the lack of adequate

CAD/CAE tools to support VLSI circuit design [LOS80].

In this thesis the VLSI routing problem, in particular, the channel routing problem, will be addressed. The main reason why routing remains such a difficult problem is its global nature: the way one interconnection is routed influences the potential solution for other interconnections. Any fragmentation of the routing task into smaller domains may affect this global aspect and hence the quality of the routing results [LUD83]. However, the problem of routing is simply too complex to be considered globally without subdividing it into smaller, more manageable, domains. As will be discussed in the next chapter on routing algorithms, the method of channel routing represents a simple yet effective approach to the VLSI routing problem.

#### 1.6 Thesis Objectives

The objectives of this research work are:

- 1. To identify areas that can be improved in existing detailed routing algorithms through a survey of published results.

- To improve the existing channel routing algorithms through the development of a detailed routing algorithm for regular channels in an attempt to obtain optimum or near optimum results for at least one class of channel routing problems.

- To improve the detailed routing algorithm for regular channels by extending it to allow doglegs and hence relaxing the restriction on one horizontal track per net.

#### 1.7 Thesis Structure

This thesis addresses the VLSI channel routing problem. The concept of channel routing, although introduced over a decade ago, is still the most popular routing strategy for LSI and VLSI layout designs. The next chapter describes on the major classes of routing algorithms, including maze-running, line-search, and channel routing algorithms, as well as other routing approaches, including hardware routers, expert routers, and the simulated annealing technique. It is then followed by Chapter III on the introduction of a non-dogleg detailed routing algorithm for regular channels. In Chapter IV, the extension of the non-dogleg algorithm to allow doglegs is described along with the implementation and the experimental results. Finally, conclusions for both the non-dogleg and the dogleg channel routing problems are drawn and recommendations for further research are given in the last chapter of this thesis.

# CHAPTER II VLSI ROUTING ALGORITHMS

Since the first routing algorithm was introduced by Lee in 1961 [LEE61], numerous routing algorithms have been developed. Many of those algorithms were very innovative and provided much understanding into the complex problem of routing. It is essential that those developments be understood before any fruitful research can be attempted. This chapter describes the three most important classes of routing algorithms that formed the basis of most computer-aided layout design systems today, namely, maze-running, line-search, and channel routing algorithms. In addition, other routing approaches, including hardware routers, expert routers and the simulated annealing technique are described.

## 2.1 <u>Maze-Running and Line-Search Routing Algorithms</u>

The maze-running and line-search algorithms are the most well known routing algorithms. The maze-running algorithms find a path between two points on a grid similar to finding an entrance-to-exit route in a grid-structured maze. The line-search algorithms, on the other hand, search for a path as a sequence of line segments. In the following two sections these two classes of algorithms will be described in detail.

#### 2.1.1 Maze-Running Routing Algorithms

Maze-running or grid-expansion algorithms are grid based algorithms that find a connecting path between two terminals of a net on the grid similar to finding an entrance-to-exit path in a grid-structured maze. Algorithms in this class assume the use of a uniform rectangular grid. The spacing between the grid points is such that for wires less than a certain width routing on the grid points will automatically provide the proper clearance between the wires. Although the use of such a grid eliminates the possibility of curved or diagonal traces typically seen in manual layouts, this loss of generality substantially simplifies the routing problem, thus allowing more complex problems to be tackled. This concept of grid based routing has in fact given rise to the entire class of maze-running algorithms, and the use of CAD/CAE systems in layout designs.

#### Lee Algorithm

The first maze-running algorithm that aimed at automated wire routing was developed by Lee in 1961 [LEE61] and is commonly called the Lee algorithm. It was originally developed for single layer routing on a planar rectangular grid. The objective is to find the shortest path, if such a path exists, on the grid connecting the two terminals of a net. Before a more precise definition of the algorithm, it would be best to begin with a simple example illustrating the algorithm.

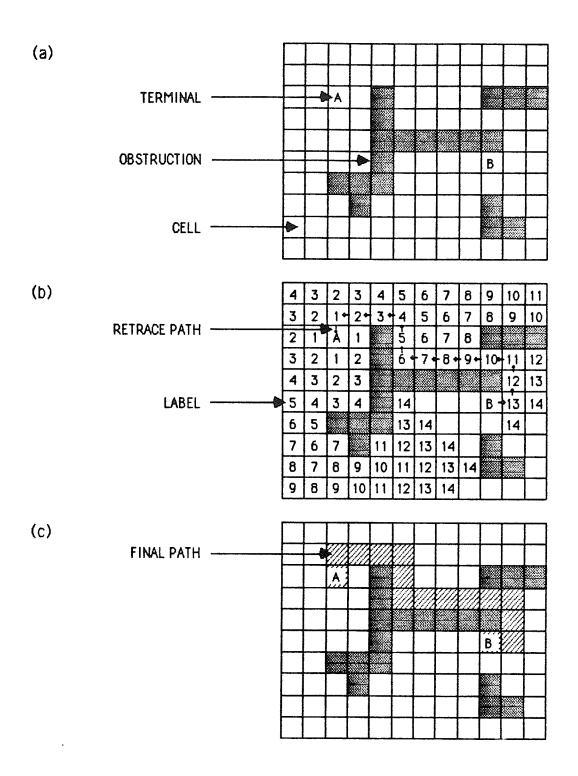

Assume a small routing region as shown in Fig. 1a. For a better illustration, the grid points are represented by rectangular cells. The numbers inside the cells are labels used in the algorithm, and the blackened

Fig. 1. Lee algorithm routing example. (a) Routing grid; (b) Cell expansion and retracing (note that B is labelled 14); (c) Final path between terminals A and B.

cells represent obstructions, such as routing voids or traces of routed nets. The cells labelled A and B are the two terminals of the net to be connected using the Lee algorithm. The goal is to find the shortest path between the two cells while avoiding the blackened obstruction cells.

The algorithm can be decomposed into two separate phases: the cell expansion phase and the retracing phase.

1. Cell Expansion (or wave propagation): The algorithm begins by selecting one of the two terminals as the source cell and the other terminal as the target cell. In theory, either terminal can be chosen as the source terminal. In practice, however, one terminal may be more desirable than the other, as will be seen later. Here, terminal A is selected as the source and terminal B as the target. With the source and target cells chosen, a label of 1 is entered into every empty cell immediately adjacent to the source cell. Since no diagonal traces are allowed, the adjacent cells are the north, west, south, and east cells. Next, a label of 2 is entered into every empty cell immediately adjacent to the cells labelled 1, and so on; increasing the label by one in every expansion step. This process continues until either (i) there are no empty cells adjacent to the labelled cells meaning that no path exists connecting the cells A and B on the grid and the algorithm terminates, or (ii) the target cell B is reached meaning that a path has been found and the algorithm proceeds to the next retracing phase. The key purpose of this cell expansion phase is in the labelling of the cells, where the numbers represent the Manhattan distance of the cells from the source cell. This process can also be viewed as a breadth-first-search in graph theory as the cells closer to the source cell are searched first.

2. Retracing: After the cell expansion phase, there exists at least one path connecting the source cell and the target cell among the expanded cells. However, the exact optimal path has not been determined. The main purpose of this retracing phase is to trace out the exact optimal path from the target cell back to the source cell. As shown in Fig. 1b the target cell B has been reached in the 14th expansion step. It follows that there must be a cell with a label of 13 adjacent to B. Similarly, for a cell with a label of 13 there must be a cell with a label of 12 adjacent to it, and so on. Therefore, by tracing the labelled cells in descending order from the target cell back to the source cell, the desired shortest path can be identified. In the retracing process, there are often more than one adjacent cell with the correct label. In theory, any one of those cells can be chosen and they will all yield paths having the shortest length. In practice, however, the cells not leading to a change in the path direction will normally be chosen to minimize the number of corners in the wire. For example, in Fig. 1b, the cell labelled 9 on the retracing path has two adjacent cells labelled 8. In such a case, the one to the left is chosen instead of the one above to avoid a change in the path direction. Once a path is selected, all the cells along the path are labelled as occupied and become obstructions for subsequent interconnections while the rest of the expanded cells are relabelled as empty and remain available for subsequent routing.

The result of these two steps are shown in Fig. 1c. The final optimal path is indicated by shaded cells in the diagram.

From the above example, it can be seen that the Lee algorithm is fairly simple. But the most important properties of the Lee algorithm are that: (i) it

guarantees to find a path if one exists, and (ii) it guarantees to find the optimal path if more than one path exist. As in the above example, the final path of length 14 is the shortest possible path connecting the cells A and B.

With the basic principles of the Lee algorithm illustrated in the above example, a more precise definition of the algorithm in pseudo-codes would help to clarify the details. First, a few definitions are required. Assume that the routing area is divided into a finite number, N, of subareas called cells labelled  $C_i$ . The cells representing obstructions such as routing voids or routed wires are labelled as occupied and are not available for routing. The remaining cells are labelled as free and can be used to form a path. Moreover, a cell  $C_i$  has associated with it a cost,  $f(C_i)$ , and a path p consisting of the starting cell S and a set of cells  $C_1$ ,  $C_2$ ,  $C_3$ , ...,  $C_n$  each adjacent to the previous cell forming an (n+1) cell path of

$$p = {S, C_1, C_2, C_3, ..., C_n}$$

has a path cost of, F(p), where

$$F(p) = \sum_{i=1}^{n} f(C_i).$$

In the original Lee path finding algorithm, the cost of a cell is the Manhattan distance between that cell and the source cell. However, path cost function can be generalized to any monotonic function or set of monotonic functions represented by a vector  $\mathbf{F} = [F_1, F_2, ..., F_n]$ . A path cost function is monotonic if for every path p and any of its subpath  $\mathbf{p_i}$ , the following inequality holds.

$$F(p_i) \le F(p)$$

With the above definitions in order, the Lee algorithm can be described more precisely in pseudo-code. Instead of showing the exact algorithm as presented by Lee, the algorithm is restated here to show just the essence of the algorithm; in particular, the cell expansion and retracing phases. The pseudo-codes used are similar to the Pascal language, and the syntax should be self-explanatory.

# [Lee (maze-running) Routing Algorithm]:

Lee( cell\_map );

cell\_map:

an ordered list of cells.

The list includes:

1) the location of obstruction cells;

2) the location of the source and target cells;

3) the definition of cell neighbourhood;

4) the path cost function.

Each individual cell is a structure which includes:

1) a cell identification field: id;

2) a cell label field: label;

The individual fields are referenced as cell. id and cell. label, respectively.

(Variable Definitions)

source:

the source cell;

target:

the target cell;

cell:

variable holding a cell;

path\_cell:

variable holding a cell in the retrace phase;

neighbour:

variable holding a neighbour cell;

label:

current label in the cell expansion phase;

found:

boolean variable used to terminate cell expansion;

```

begin

(initialization)

label := source.label := 0;

found := false;

[cell expansion]

while not found and number of empty cells in cell_map > 1 do

begin

for all empty cell in cell_map do

if cell.label = label then

for neighbour in the neighbourhood set of cell do

if neighbour.label = empty then

neighbour.label := label + 1;

else if neighbour.id = target.id then

(target cell is reached; terminate cell expansion)

found := true;

label := label + 1;

end:

[retrace]

if found then

begin

path_cell := target;

repeat

output path_cell.id;

for neighbour in the neighbourhood set of path_cell do

if neighbour.label = path_cell.label - 1 then

path_cell = neighbour;

until path_cell.id = source.id

end

else

(all cells have been examined and no path is found)

output "no path is found."

end.

```

From the above description of the algorithm it can be seen that the Lee algorithm requires at least  $N^2$  memory for an N×N routing region, and  $O(N^2)$  running time in the worst case, or  $O(L^2)$  for a path of length L in the cell expansion phase and O(L) in the retracing phase. Obviously, for a large routing region, the memory required to store the cell labels and the running time required to find a path through the grid are the two major drawbacks of the algorithm. In light of these storage and speed problems, a large number of variations and extensions to the original Lee algorithm have been developed [AKE67, GEY71, RUB74, HOE76, KOR82].

### Extensions of the Lee Algorithm

There are a large number of variations on the original Lee algorithm. Among the various extensions, several of the important ones are described in this section and they are organized into storage reduction techniques, speed up techniques, multi-terminal net extensions, and multi-layer extensions.

# **Storage Reduction Techniques**

The huge storage requirement of the Lee algorithm represents a very serious drawback, especially for large scale or dense layouts. For example, a double layer 1000×1000 grid would have two million cells. Wire lengths as long as 1000 could be expected in such a grid. Thus, during the cell expansions process, labels as large as 1000 would be used requiring at least 10 bits of storage per cell. If double-byte words are used, a total of over 3.8 mega-bytes must be allocated to store the grid. However, as can be seen from the example in Fig. 1, the minimum amount of information that must be

present includes only (i) a means of distinguishing between occupied cells and empty cells, and (ii) a means of distinguish between the predecessor cells from the successor cells in the retracing process. Based on this observation, a number of labelling scheme have been devised to encode the necessary information using fewer number of bits per label.

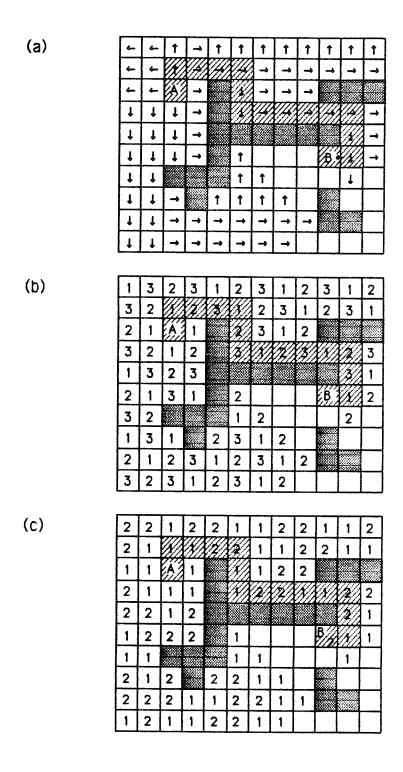

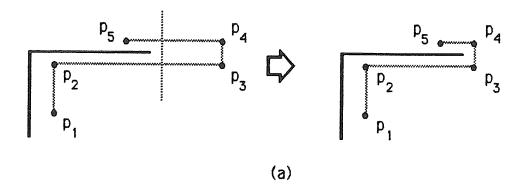

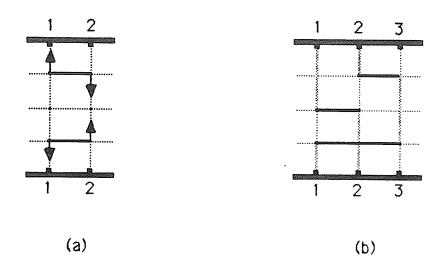

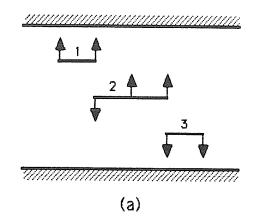

- 1. Direction Labelling Scheme: At each cell expansion step the adjacent cells are given direction labels of north, west, south, or east indicating the directions of expansion as shown in Fig. 2a. If a cell can be reached from more than one direction, one direction label is entered. Using the four direction labels, together with the empty cell and the occupied cell labels, there are a total of six distinct labels. Hence, three bits of storage is required per cell. This labelling scheme, however, has one drawback. Since only one of the cell expansion direction is entered, only one path can be found even if more than one exist. Thus the choice of selecting the path with fewer number of corners is sacrificed for the reduced storage.

- 2. 1-2-3 Labelling Scheme: Instead of storing the directions of expansion, a sequence of 1,2,3,1,2,3,... is used for labelling as shown in Fig. 2b. In the retracing phase, the reverse sequence is traced. This labelling scheme uses a total of five distinct labels, and thus still requires three bits of storage per cell. However, this technique allows multiple paths to be identified and the one with fewest corners to be selected.

- 3. 1-1-2-2 Labelling Scheme: This labelling scheme is similar to the 1-2-3 labelling scheme, except that a 1,1,2,2,1,1,2,2,... sequence is used as shown in Fig. 2c. Note that in the example the target cell B is reached with a 1 preceded by another 1. Therefore the retrace sequence

Fig. 2. Storage reduction techniques. (a) Direction labelling; (b) 1-2-3 labelling; (c) 1-1-2-2 labelling.

should be 1,1,2,2,1,1,... The biggest advantage of this labelling scheme is that only two labels are used in the sequence. Together with the occupied cell and the empty cell labels, a total of four distinct labels are required. Hence, only two bits of storage are required per cell instead of three as in the previous two schemes [AKE67].

All of the above labelling schemes are designed to reduced the amount of storage per cell. However, in practical routers, the selection of labelling schemes must be made according to the tradeoff between storage and efficiency [OHT86]. For example, although the 1-1-2-2 scheme requires only two bits per cell, the final label clearance process may be as involved as the cell expansion phase. Thus, additional bits are often used to simplify the processing.

## Speed-Up Techniques

Several speed up techniques are also possible. Most of such techniques are focused on the cell expansion phase. The objective is to reduce the number of cells that must be examined to find a connection path. However, in some speed up techniques such as double framing, the resulting path may not always be the optimum. The use of such techniques would thus involve a tradeoff between speed and optimality. The common approach is to find a solution quickly with a speed up technique, and if the resulting solution is unacceptable, the parameters are modified or a complete search is performed again. One point should be noted here is that, while the speed up techniques tend to reduce the average processing time, the worst case computational complexity remains unchanged.

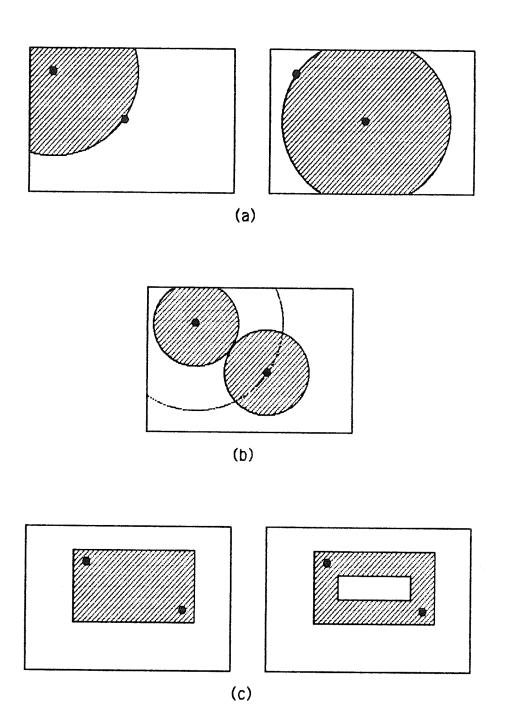

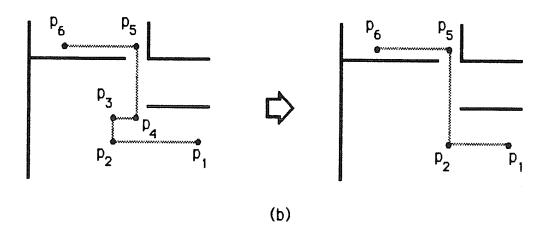

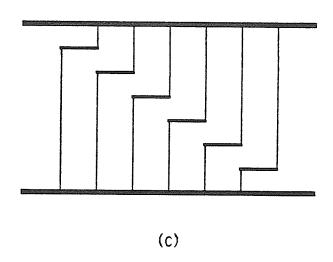

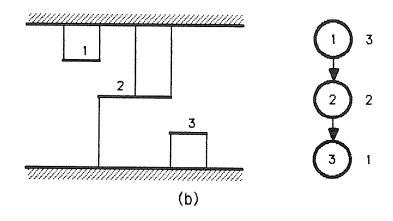

- 1. Starting Point Selection: For a given pair of terminals, it is more desirable to start the cell expansion process from the terminal closer to the boundary of the routing region since the number of cells that need to be examined are fewer (Fig. 3a).

- 2. Double Fanout: Cell expansion is performed from both terminals simultaneously until a point of contact is reached (Fig. 3b). This technique reduces the number of cells that need to be examined but requires a more complex scheme to keep track of the two simultaneous cell expansion processes.

- 3. An artificial rectangular frame is imposed around the Framina: terminal pair and no cell expansions are allowed outside this boundary (Fig. 3c). Typically, the frame is about 10-20% larger than the rectangle defined by the terminal pair and may be expanded or removed if a path cannot be found within this frame. The reason behind this technique is that, it has been observed that in most cases the shortest path between two cells is within the rectangle defined by the terminals. Therefore, by restricting the search area the probability of finding a path is still high while a considerable speed up is possible. A further extension to this framing technique is double framing, where a second, smaller frame is imposed inside the rectangle defined by the terminals to further reduce the search area. The use of this interior frame may prevent the algorithm from finding the shortest path. However, this technique is commonly used to quickly identify simple paths.

Fig. 3. Speed up techniques. (a) Starting point selection; (b) Double fanout; (c) Single and double framing.

#### <u>Multi-Terminal Net Extension</u>

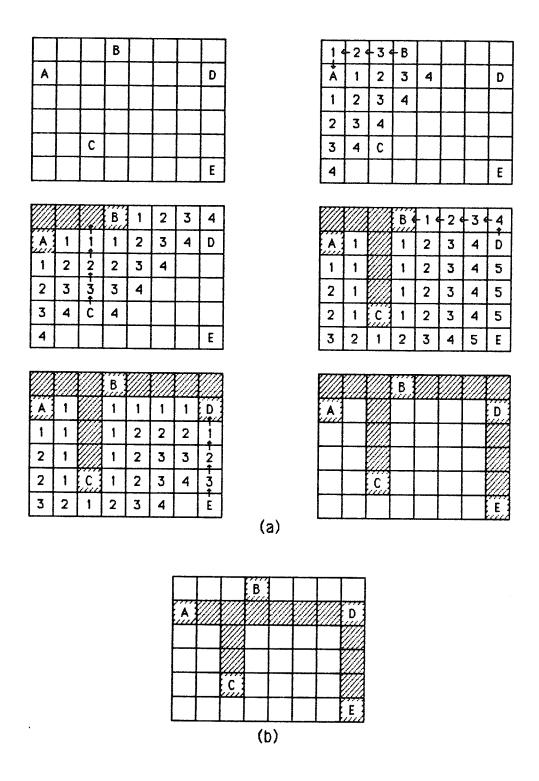

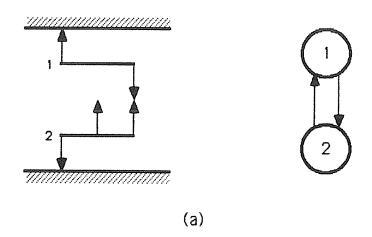

In the original Lee algorithm, only the connection of two terminal nets are considered. When a net with three or more terminals (multi-terminal net) is to be routed, a direct application of the algorithm is not possible. One solution to this problem is to begin by using one of the terminals as the source and the rest of the terminals as the targets, and find a path between the source and the first target reached. Once a path is found, all the cells in the two terminal path become source cells and all the other terminals remain as target cells, and the path finding process is repeated. Then all the cells in the resulting three terminal path become source cells and the other terminals remain as target cells, and so on, until all the terminals are connected. Figure 4a shows the routing of a 5-terminal net.

The interconnecting path obtained by this process is not always the optimum. In fact, this multi-terminal net routing problem is equivalent to the Minimum Steiner Tree problem in graph theory, which is known to be an NP-problem [GAR79]. The possibility of finding the optimal solution in polynomial time is unlikely. There is, however, one simple technique that is often able to improve the resulting path. The idea is to break the resulting multi-terminal path into two sub-paths. Then, one of the sub-paths can be used as the source and the other as the target. If the resulting path is better than the original path, the new path is kept and a better overall path is found. Applying this technique to the example in Fig. 4a, a shorter path is found as shown in Fig. 4b. This technique clearly requires longer running time, but it does often allow better paths to be found.

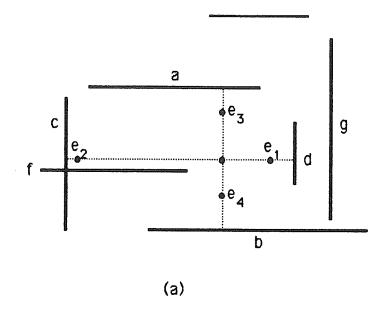

Fig. 4. Multi-terminal net routing example.

(a) Multi-terminal routing using terminal A as the first source cell;(b) A shorter path found by rerouting sub-paths.

### <u>Multi-Layer Extension</u>

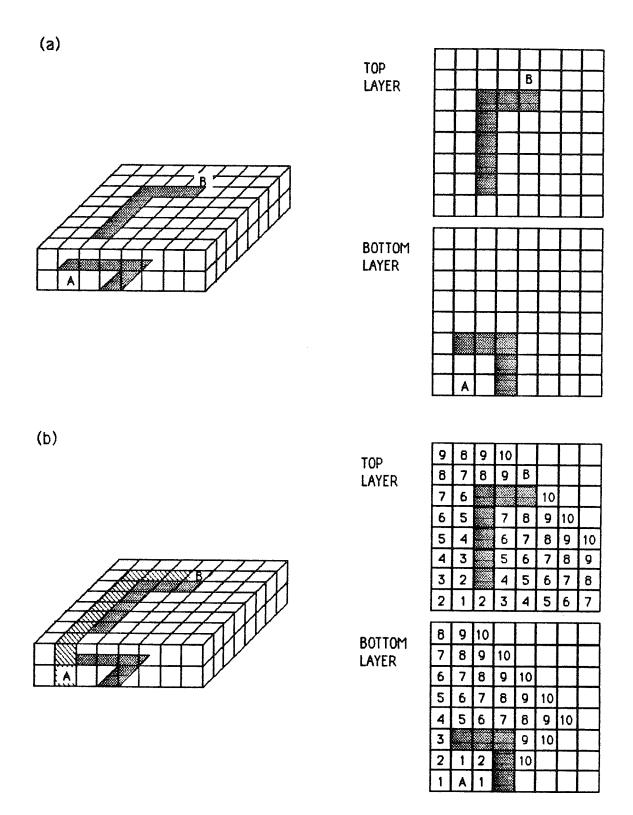

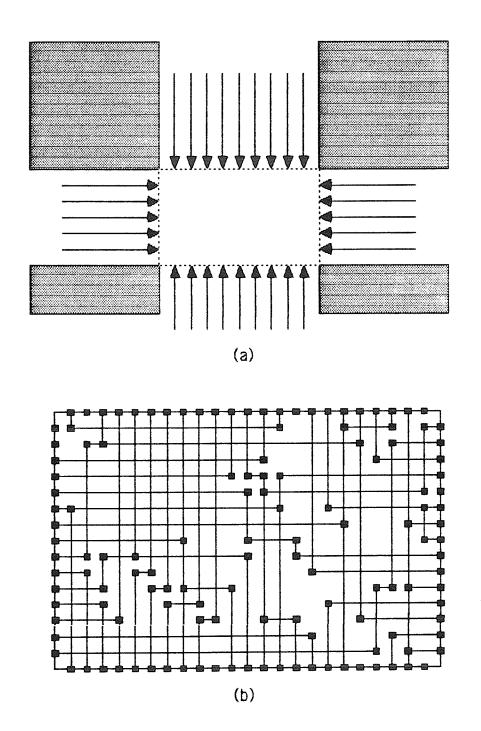

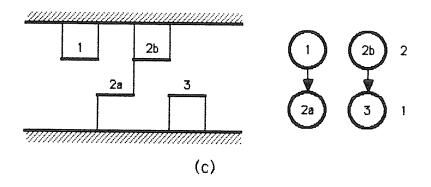

One of the most important variations to the original Lee algorithm is the extension to multi-layer regions with interconnecting vias. One way to model the three dimensional routing problem on a grid is to consider a three dimensional array of regular cubes as shown in Fig. 5a, where a double layer case is illustrated. Note that the grid points are now represented by cubic cells. As before, a pair of terminal cells are given, and the goal is to find the shortest path connecting the terminal pair.

The three dimensional Lee algorithm is very similar to the two dimensional case, except that the cells adjacent to a given cell now consist of not only the four planar cells in the north, west, south and east positions, but also the cells in the top and bottom positions. Using similar cell expansion and retracing processes as in the two dimensional case would lead to a path connecting the terminal pair with the minimum number of cells. It is assumed that an inter-layer connection through a via has the same cost as a unit length wire. The result of the example in Fig. 5a is shown in Fig. 5b.

## **Summary**

Maze-running algorithms are capable of finding the optimal path between two terminals with respect to any monotonic cost functions, provided that such a path exists. Numerous variations and extensions have been published to enhance the original maze-running algorithm developed by Lee. Some of the most important ones are the storage reduction techniques, the speed up techniques, the multi-terminal net extension, and the multi-layer extension. But, even with these enhancements maze-running algorithms still require

Fig. 5. Multi-layer extension. (a) Double layer routing problem; (b) Routing result.

substantial amount of storage and running time. To address these drawbacks, the class of line-search algorithm have thus been developed. In the next section, the line-search routing algorithms will be described.

# 2.1.2 <u>Line-Search Routing Algorithms</u>

The class of line-search routing algorithms was first proposed by Hightower [HIG69] to reduce the storage requirement and to speed up the running time of the maze-running algorithms. Basically, paths are found by constructing sequences of connected line segments starting from the terminal points until they intersect. There are three major differences between the line-search algorithms and the maze-running algorithms.

- 1. The line-search algorithms also proceed to find a path by running on a grid. But, unlike the maze-running algorithms in which a unit of memory is allocated for each grid point, the routing space is considered as a continuous plane and paths are represented by a set of line segments. In this sense, the line-search algorithms can be viewed as proceeding on an virtual grid.

- The line-search algorithms process and store line segments rather than cell maps. Thus, in most cases the amount of storage required, and the running time is substantially reduced.

- 3. The line-search algorithms, although usually able to find a path, cannot guarantee that a path be found even if one exists. Furthermore, the optimality of the resulting path cannot be guaranteed. However, the small storage requirement and the fast running time still make this class of algorithms very attractive.

### <u>Hightower Algorithm</u>

The most representative and best known line-search routing algorithm is due to Hightower [HIG69]. In this section, the Hightower algorithm will be described.

First a few definitions are required before the algorithm cannot be explained.

- 1. A <u>cover</u> of a point p is a line segment  $\alpha$  such that a perpendicular to a passes through p.

- 2. A <u>horizontal (vertical) cover</u> of p is a cover in the horizontal (vertical) direction such that no other covers of p exist between it and p.

- 3. A <u>horizontal (vertical) escape line</u> is a horizontal (vertical) line segment through p bounded by the vertical (horizontal) covers of p.

- 4. An <u>escape point</u> e is a point on the horizontal (vertical) escape line of p which is not covered by both horizontal (vertical) cover of p, or any other horizontal (vertical) line segments between p and the cover.

- 5. The <u>object point</u> is the escape point currently being processed.

- 6. The <u>target point</u> is the point to be reached from the object point.

- A <u>unit</u> is the minimum spacing between wires. It defines the grid spacing.

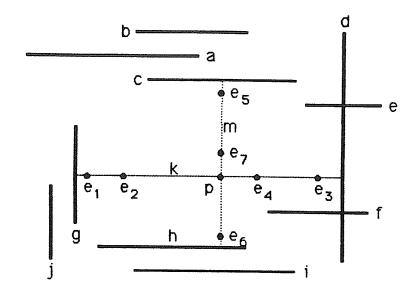

An illustration of the above definitions is given in Fig. 6.

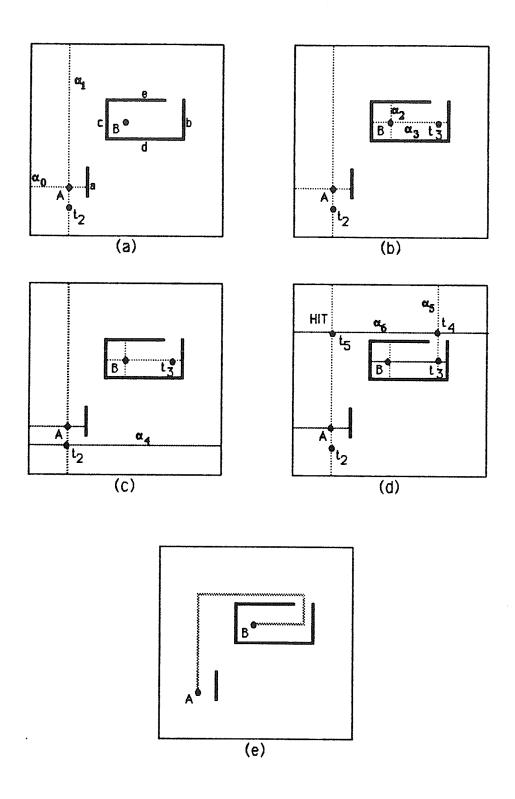

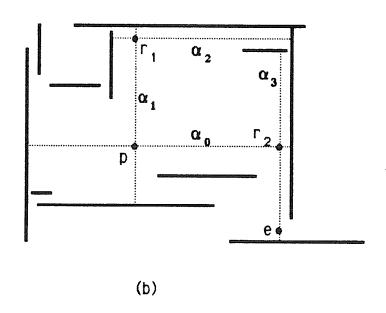

With the terms defined, consider now the example in Fig. 7. It is required to connect the terminal points A and B in the given routing region with blockage wires a, b, c, d and e. First the escape lines  $\alpha_0$  and  $\alpha_1$  are constructed through the object point A (Fig. 7a). Notice that there are no escape points along the horizontal escape line  $\alpha_0$  since the horizontal covers of A are the top and bottom boundaries. Along  $\alpha_1$ , on the other hand, the point

- 1. Covers of point p: b, c, d, h, i, g.

- 2. Horizontal covers: c, h.

- 3. Verical covers: g, d.

- 4. Horizontal escape line of p: k.

- 5. Vertical escape line of p: m

- 6. Horizontal escape points:  $e_5$  and  $e_6$ , but not  $e_7$ .

- 7. Vertical escape points:  $e_1$ ,  $e_2$  and  $e_4$ , but not  $e_3$ .

Fig. 6. An illustration of definitions used in the Hightower algorithm.

Fig. 7. Hightower algorithm routing example.

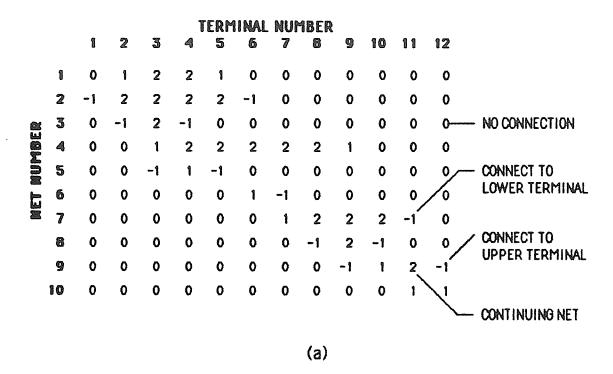

(a-d) Escape processes; (e) Final route.