# Power Quality Conditioning Technology for Power Grids with Modern Lighting Loads

by

Radwa Mohamed Sayed Abdalaal

A thesis submitted to the Faculty of Graduate Studies in partial fulfilment of the requirements of the degree of

DOCTOR OF PHILOSOPHY

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg

Copyright © 2020 by Radwa Abdalaal

# **Examining Committee**

Prof. Carl Ngai Man Ho, Dept. of Electrical and Computer Engineering, University of Manitoba

Prof. Udaya Annakkage, Dept. of Electrical and Computer Engineering, University of Manitoba

Prof. Qiuyan Yuan, Dept. of Civil Engineering, University of Manitoba

Prof. Ka-Hong Loo, Dept. of Electronic and Information Engineering, Hong Kong Polytechnic University

#### **Abstract**

Poor power quality network, including long and short voltage variations, is directly reflected into visual light flickering in light emitting diode (LED) lighting networks. On the other hand, a large scale of LED lighting network injects high harmonic contents that are generated by the internal driver of LEDs. Accordingly, this will distort the quality of the grid leading to high voltage and current total harmonics distortion.

This thesis proposes a power electronics apparatus to mitigate major power quality problems in LED lighting networks and improve the overall quality of distribution networks. An active power filter has been proposed as a comprehensive solution to improve grid current and light intensity flickers in a large-scale LED lighting network. The first part of the research study is conducted to gain a better understanding of the characterization of commercial dimmable LED lamps as nonlinear loads. The second part of the research study proposes a single-phase transformerless unified power quality conditioner (TL-UPQC) topology with its controls. The topology provides a stable output voltage for a flicker free lighting network. An active power filter injects harmonic and reactive currents to provide unity power factor. A dynamic voltage restorer quickly supports the load voltage for any voltage dip, swell or flickering in the network. Stability of the designed controllers is analyzed by a small-signal modeling technique. In addition, the proposed topology has been utilized as a central dimmer system for LED lamps while maintaining high voltage and current quality.

The TL-UPQC features have been extended to improve the grid voltage profile by designing an ac voltage control loop to achieve reactive power compensation into the input grid. Moreover, the thesis presents a novel approach for a supervisory remote management system to regulate a secondary control system that is based on the available capacity of distributed units connected to

the same point of common coupling. The TL-UPQC system topology and its controller methodology have been verified experimentally with a 500VA / 120V prototype. Modularized distributed TL-UPQC systems have been evaluated by implementing a controller hardware-in-the-loop test. All described strategies' experimental results show good agreements with the theoretical concept.

## **Use of Copyrighted Material**

The following publications have been used in this thesis. As a first author, I would like to acknowledge the use of this material,

- © 2017 IEEE. Reprinted with permission from, R. M. Abdalaal and C. N. M. Ho, "Transformerless single-phase UPQ for large scale LED lighting networks," in *Proc. IECON Ann. Conf. IEEE Ind. Electron. Soc.*, 2017, pp. 1629-1634.

- © 2019 IEEE. Reprinted with permission from, R. M. Abdalaal, C. N. M. Ho, C. K. Leung and H. S. Chung, "A Remotely Central Dimming System for a Large-Scale LED Lighting Network Providing High Quality Voltage and Current," *IEEE Trans. Ind. Appl.* vol. 55, no. 5, pp. 5455-5465, Sept.-Oct. 2019.

- © 2020 IEEE. Reprinted with permission from, R. Abdalaal and C. Ho, "Characterization of commercial LED lamps for power quality studies," *IEEE Can. J. Elect. Computer Eng.*, 2020, early access.

- © 2020 IEEE. Reprinted with permission from, R. Abdalaal and C. Ho, "A supervisory remote management system for parallel operation of modularized D-STATCOM," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, 2020.

## Acknowledgments

Foremost, I would like to express my deepest gratitude and sincere appreciation to my supervisor Prof. Carl Ngai Man Ho for his invaluable guidance, motivation and endless support. It will always be an honor to be his student. I am indebted to thank Dr. Ho for allowing me to grow as a research scientist and an engineer. Giving the opportunity to join Dr. Ho's lab, Renewable Energy Interface and Grid Automation (RIGA), helped me to develop expertise on hardware design and implementation, which I am grateful for. Dr. Ho has also extended his encouragement and support for my IEEE volunteering work. He has been a tremendous advisor for the IEEE Industry Application Society Student Branch Chapter, assisting the group in every step.

I am very much thankful for my advising committee Prof. Udaya Annakkage and Prof. Qiuyan Yuan, for their feedback and suggestions regarding my thesis. Their invaluable insights helped me to develop a broader perspective to my work. I would like also to thank Prof. Carson Leung and Prof. Henry Chung for providing me technical comments on the conducted research.

My heartfelt thanks go to my research group mates, RIGA lab members, who become my dear friends. I would like to thank Dr. King Man Siu, Mr. Mandip Pokharel and Mr. Isuru Jayawardana for sharing their experience and providing me with insightful feedback on my research work. My deepest thanks to Ms. Zhuang Zhang, Mr. Yang Zhou, Mr. Dong Li, Mr. Hafis Umar-Lawal, Mr. Yanming Xu and Mr. Avishek Ghosh for all the fruitful discussions and enjoyable time we had in the lab. I would like also to appreciate the support I received from the faculty staff, Ms. Amy Dario and Ms. Traci Gledhill. My sincere thanks to the technical support, Mr. Erwin Dirks and Mr. Shrimal Koruwage for their prompt assistance regarding any technical problems. I wish to acknowledge the contribution of the undergraduate students in this research work, Mr. Mark Van Egmond, Mr. Justin Roznik, Mr. Syed Habib Ur Rehman and Mr. Nibrasul I. Ohin.

I would also wish to express my gratitude to Prof. Yasser Higazi for his invaluable support and encouragement throughout my graduate studies.

I thank my family and friends whom I am blessed to have. The person with the greatest indirect contribution to this achievement and my life is my father. I thank him for always encouraging and supporting me to pursue my goals. I thank my mother for her unconditional love. Special thanks goes to my loving husband Mohamed Talayie for his patience and support during my PhD study.

# Dedication

"To my loving parents, Mr. Mohamed Sayed Abdalaal and Ms. Maha Mustafa"

# **Table of Contents**

| Exami                                                                             | inee Co | ommittees                                                          | ii   |

|-----------------------------------------------------------------------------------|---------|--------------------------------------------------------------------|------|

| Abstra                                                                            | act     |                                                                    | iii  |

| Ackno                                                                             | wledg   | ments                                                              | v    |

| Dedica                                                                            | ation   |                                                                    | vii  |

| Table                                                                             | of Con  | tents                                                              | viii |

| List of                                                                           | f Table | s                                                                  | xii  |

| List of                                                                           | f Figur | es                                                                 | xiii |

| Chapte                                                                            | er 1    | Introduction                                                       | xx   |

| 1.1                                                                               | Backg   | round                                                              | 1    |

| 1.2                                                                               | Overv   | iew of Power Quality Definition and Standards                      | 2    |

|                                                                                   | 1.2.1   | Power Quality Steady-State Issues                                  | 4    |

|                                                                                   | 1.2.2   | PQ Disturbances Issues                                             | 8    |

| 1.3                                                                               | Motiv   | ation and Research Objectives                                      | 9    |

| 1.4                                                                               | Resea   | rch Contributions                                                  | 175  |

| 1.5                                                                               | Thesis  | Layout                                                             | 12   |

| Chapter 2 Literature Review of Power Quality Mitigation in a Distribution Network |         | 15                                                                 |      |

| 2.1                                                                               | Introd  | uction                                                             | 15   |

| 2.2                                                                               | UPQC    | C - State of Art                                                   | 15   |

|                                                                                   | 2.2.1   | Classification of UPQC Topologies                                  | 16   |

|                                                                                   | 2.2.2   | Transformerless UPQC topology                                      | 23   |

|                                                                                   | 2.2.3   | Series APF Compensation Control Strategy                           | 23   |

|                                                                                   | 2.2.4   | Shunt APF Compensation Control Strategy                            | 25   |

| 2.3                                                                               | Grid V  | Voltage Regulation Techniques                                      | 27   |

| 2.4                                                                               | Parall  | el Operation of Modularized Converters                             | 30   |

| 2.5                                                                               | Chapt   | er conclusion                                                      | 34   |

| Chapte                                                                            | er 3    | Characterization of Commercial LED Lamps for Power Quality Studies | 35   |

| 3.1                                                                               | Introd  | uction                                                             | 35   |

| 3.2                                                                               | LED I   | Lamps Technology                                                   | 36   |

|                                                                                   | 3.2.1   | LED Semiconductor material                                         | 37   |

|        | 3.2.2   | LED Drivers                                                                      | 37 |

|--------|---------|----------------------------------------------------------------------------------|----|

|        | 3.2.3   | LED International Regulations                                                    | 41 |

| 3.3    | LED I   | amps Power Quality Problems                                                      | 42 |

| 3.4    | Experi  | mental Setup of LED Characterization                                             | 44 |

| 3.5    | Experi  | mental Results and Analysis                                                      | 47 |

|        | 3.5.1   | Harmonic Analysis                                                                | 48 |

|        | 3.5.2   | Static Relationship between Light Intensity, LED Array Voltage and Input Voltage |    |

|        | 3.5.3   | Dimming with amplitude variation technique                                       | 51 |

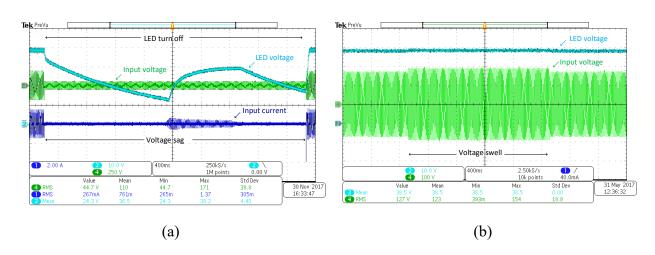

|        | 3.5.4   | Flickering and Sensitivity to Voltage Fluctuations                               | 53 |

|        | 3.5.5   | Voltage Sag and Swell                                                            | 59 |

| 3.6    | Chapte  | er Conclusion                                                                    | 61 |

| Chapte | er 4    | Transformerless Unified Power Quality Conditioner                                | 63 |

| 4.1    | Introd  | uction                                                                           | 63 |

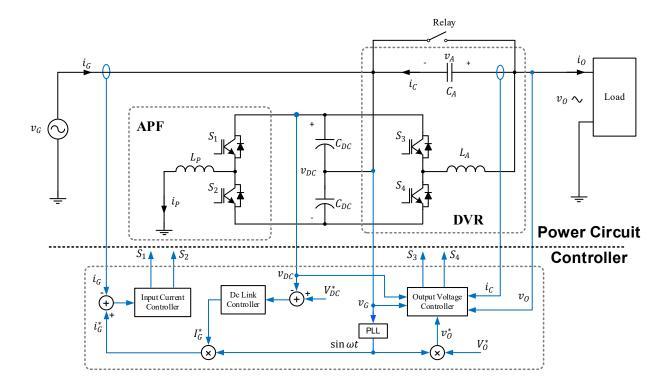

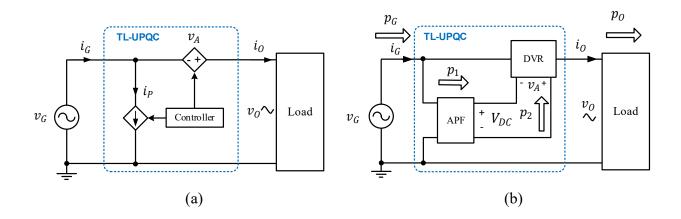

| 4.2    | Propos  | sed TL-UPQC Topology                                                             | 64 |

|        | 4.2.1   | Principle of operation                                                           | 64 |

|        | 4.2.2   | Series DVR Compensation Approach                                                 | 68 |

| 4.3    | Contro  | oller Design and Implementation                                                  | 69 |

|        | 4.3.1   | Control topology of APF                                                          | 69 |

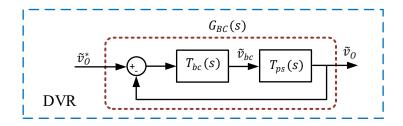

|        | 4.3.2   | Control Methodology of DVR                                                       | 71 |

| 4.4    | Systen  | n modeling and Characterization                                                  | 76 |

|        | 4.4.1   | State space model of APF                                                         | 76 |

|        | 4.4.2   | State space model of DVR                                                         | 80 |

| 4.5    | TL-UI   | PQC Sizing                                                                       | 82 |

| 4.6    | Experi  | mental Verifications                                                             | 85 |

|        | 4.6.1   | Verifications of Mathematical Model                                              | 86 |

|        | 4.6.2   | Results of Reactive Power Compensation and Current Harmonics Elimination         | 88 |

|        | 4.6.3   | Results of Voltage Variations and Flickers Elimination                           | 89 |

| 4.7    | Chapte  | er Conclusion                                                                    | 92 |

| Chapte | er 5    | A Remotely Central Dimming System                                                | 93 |

| 5.1    | Introd  | uction                                                                           | 93 |

| 5.2    | State o | of Art of Dimming Technology                                                     | 95 |

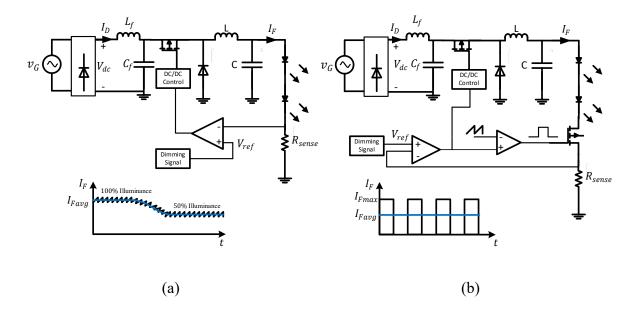

|        | 5.2.1   | LED Driver Dimming Techniques.                                                   | 95 |

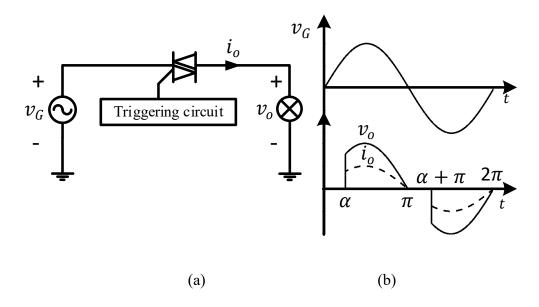

|                      | 5.2.2  | TRIAC-Based Dimmers                                                  | 97  |

|----------------------|--------|----------------------------------------------------------------------|-----|

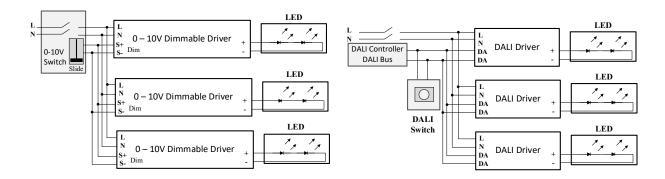

|                      | 5.2.3  | Protocols of Dimming Systems                                         | 99  |

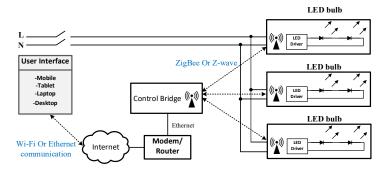

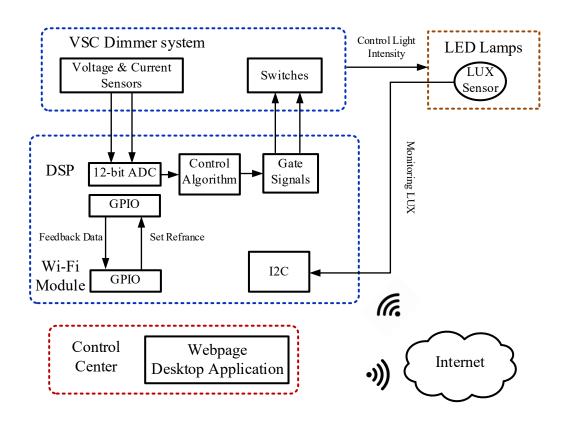

| 5.3                  | Propos | sed Remote Control Dimming System                                    | 101 |

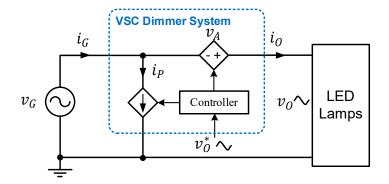

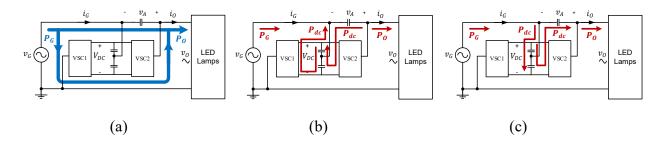

|                      | 5.3.1  | Principle of Operation                                               | 103 |

|                      | 5.3.2  | Remote System and Devices                                            | 105 |

| 5.4                  | Syster | n Modelling and Characterization                                     | 107 |

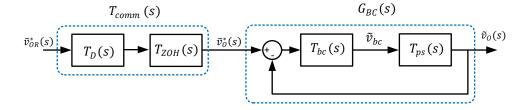

|                      | 5.4.1  | Stability of Control system                                          | 107 |

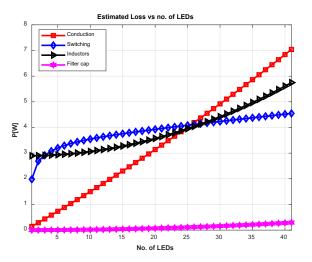

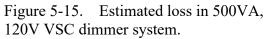

|                      | 5.4.2  | System Loss Estimations                                              | 108 |

| 5.5                  | Exper  | imental Verifications                                                | 110 |

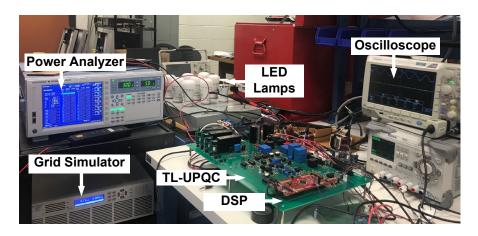

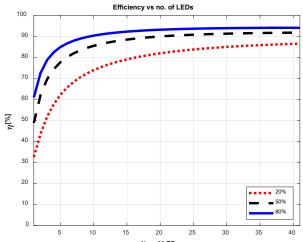

|                      | 5.5.1  | Implementation of Testbed                                            | 110 |

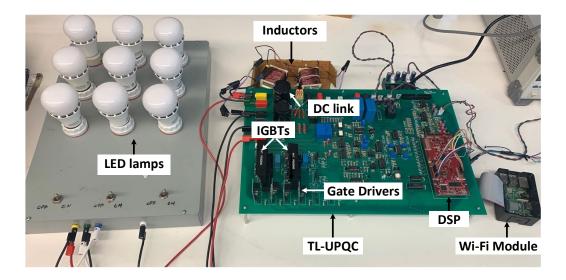

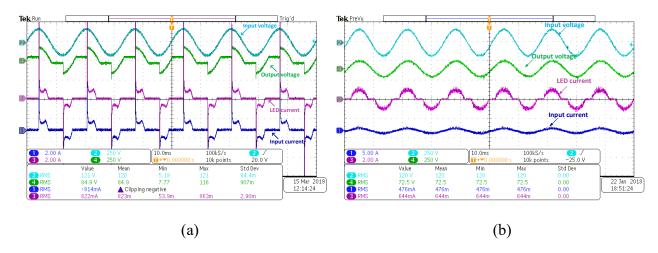

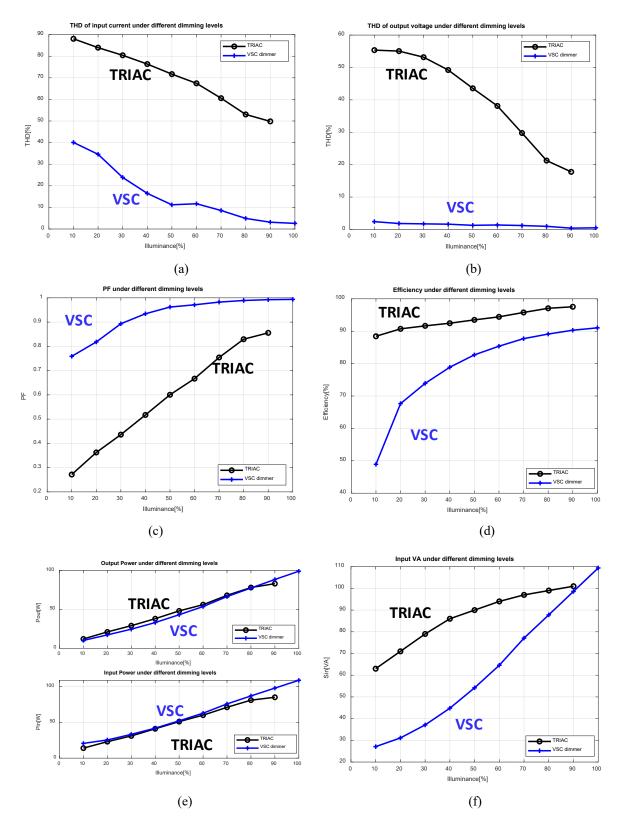

|                      | 5.5.2  | Evaluation of Dimming Performance                                    | 110 |

|                      | 5.5.3  | Static Power Quality Evaluations                                     | 111 |

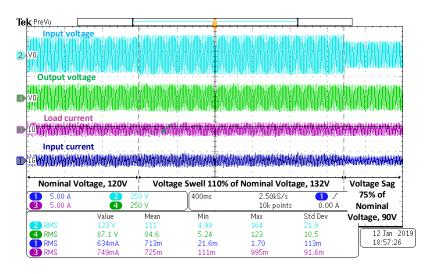

|                      | 5.5.4  | Voltage Sag and voltage swell                                        | 113 |

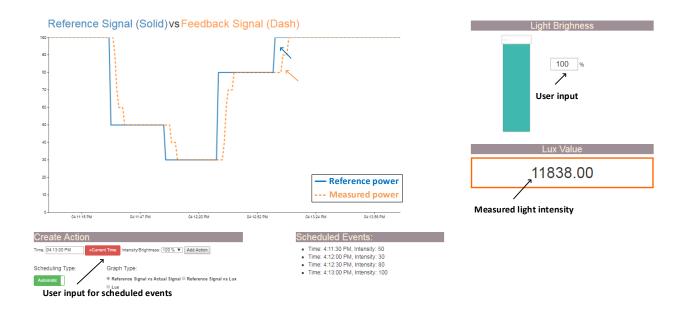

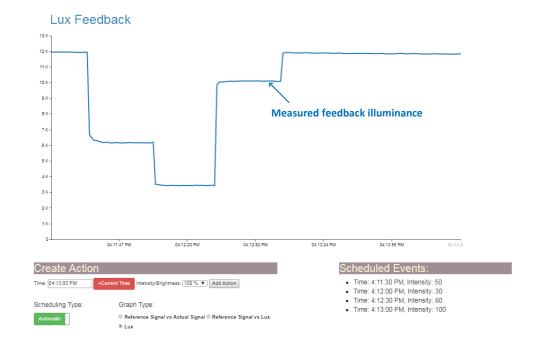

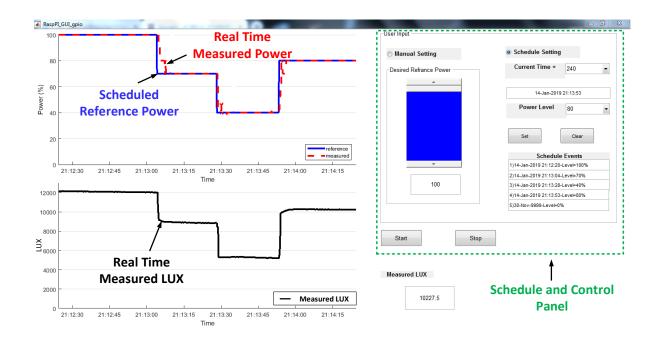

|                      | 5.5.5  | Interactive GUI and Network Latency                                  | 114 |

| 5.6                  | Chapt  | er Conclusion                                                        | 117 |

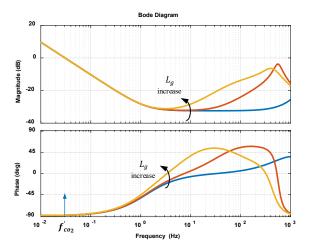

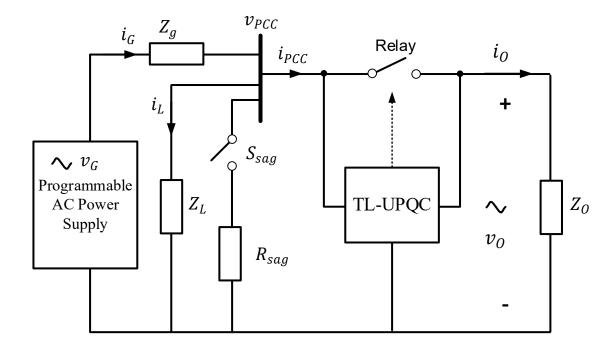

| Chapter 6 6.1 Introd |        | Enhanced Control Methodology for Input Grid Voltage Regulation       | 118 |

| 6.1                  | Introd | uction                                                               | 118 |

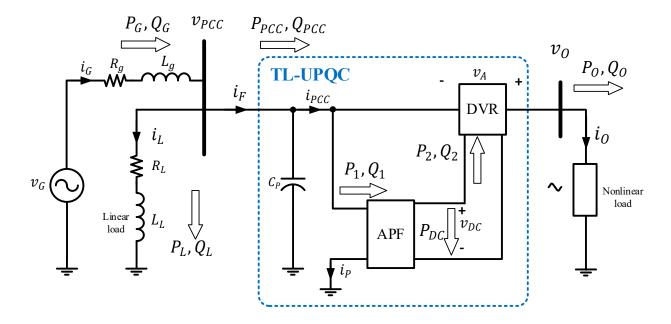

| 6.2                  | Syster | n Description and Operation                                          | 119 |

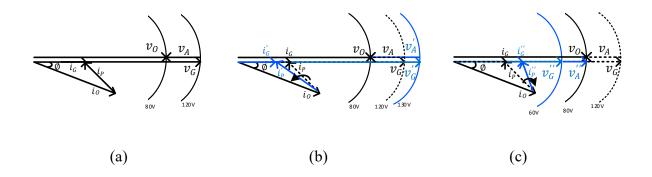

|                      | 6.2.1  | Power Flow Analysis                                                  | 122 |

|                      | 6.2.2  | Enhanced Controller Strategy                                         | 124 |

| 6.3                  | System | n Modeling                                                           | 126 |

|                      | 6.3.1  | Dc voltage loop                                                      | 128 |

|                      | 6.3.2  | Ac voltage loop                                                      | 129 |

|                      | 6.3.3  | System stability and controller design                               | 130 |

| 6.4                  | Exper  | imental Verifications                                                | 134 |

|                      | 6.4.1  | Controller implementation                                            | 136 |

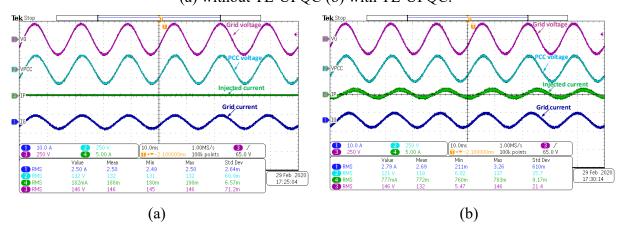

|                      | 6.4.2  | Nonlinear load at the load bus                                       | 138 |

|                      | 6.4.3  | Linear load at bus B                                                 | 139 |

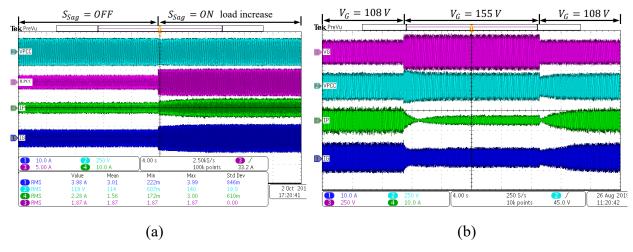

|                      | 6.4.4  | Transient                                                            | 139 |

| 6.5                  | Chapte | er Conclusion                                                        | 142 |

| Chapt                |        | A Supervisory Remote Management System for Modularized distributed T |     |

|                      | •      | tems                                                                 |     |

| /.I                  | introd | uction                                                               | 143 |

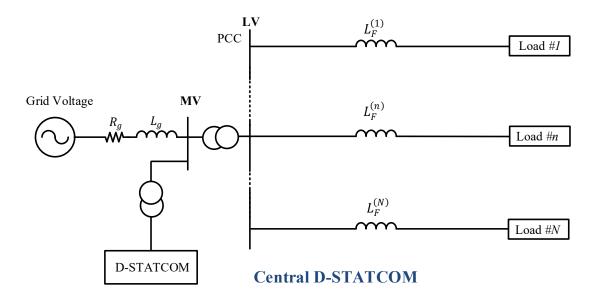

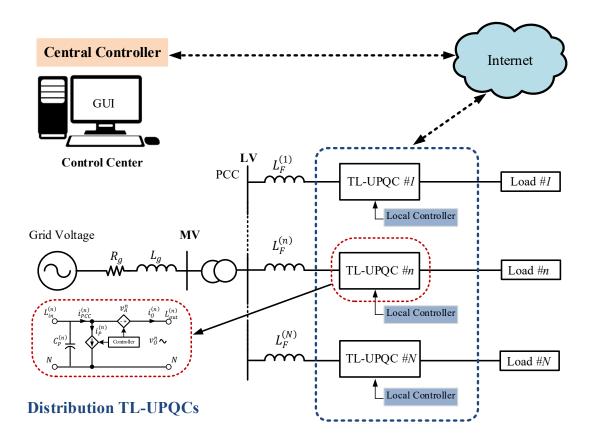

| 7.2       | Paralle | el-Operated TL-UPQCs                         | 145 |

|-----------|---------|----------------------------------------------|-----|

|           | 7.2.1   | Distributed System Operation                 | 147 |

|           | 7.2.2   | Control Scheme Structure                     | 151 |

|           | 7.2.3   | Control Scheme Coordination                  | 155 |

| 7.3       | System  | n implementation                             | 164 |

| 7.4       | Experi  | mental Verification                          | 166 |

|           | 7.4.1   | Validation of one TL-UPQC module             | 166 |

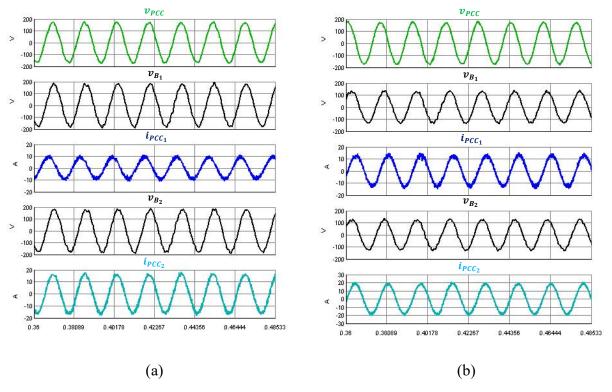

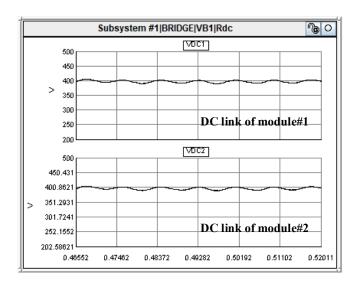

|           | 7.4.2   | Validation of parallel operation of TL-UPQCs | 168 |

| 7.5       | Chapte  | er Conclusion                                | 172 |

| Chapter 8 |         | Conclusion and Future Work                   | 173 |

| 8.1       | Conclu  | usion and major contributions                | 173 |

| 8.2       | Future  | Work                                         | 178 |

| Ref       | erences |                                              | 188 |

# **List of Tables**

|      | Table 1-I POWER QUALITY STANDARDS                                             | 3  |

|------|-------------------------------------------------------------------------------|----|

|      | TABLE 3-I COMPARISON BETWEEN THE EFFICACY OF VARIOUS TYPES OF LIGHTING SOURCE | ES |

| [16] | ]3                                                                            | 36 |

|      | TABLE 3-II POWER SUPPLY REQUIREMENTS IN ENERGY STAR PROGRAM [98]              | 12 |

|      | TABLE 3-III BASIC PARAMETERS MEASURED FOR LED LAMPS UNDER TEST                | 18 |

|      | TABLE 3-IV POWER QUALITY PARAMETERS WITH VARYING VOLTAGE AMPLITUDE            | 53 |

|      | TABLE 3-V PERCENT FLICKER FOR 2% STEP CHANGE IN MODULATION INDEX              | 57 |

|      | TABLE 3-VI PERCENT FLICKER UNDER DIFFERENT DIMMING LEVELS                     | 59 |

|      | TABLE 4-I SYSTEM PARAMETERS                                                   | 35 |

|      | TABLE 4-II MEASURED POWER ANALYSIS PARAMETERS WITH CONNECTION TO A NONLINEAR  |    |

| Lo   | AD                                                                            | 39 |

|      | TABLE 5-I COMMUNICATION PARAMETERS                                            | 17 |

|      | TABLE 6-I ENHANCED TL-UPQC SYSTEM PARAMETERS                                  | 36 |

|      | TABLE 6-II TL-UPQC CONTROLLER DESIGN                                          | 36 |

|      | TABLE 6-III POWER ANALYSIS MEASUREMENTS WITHOUT AND WITH UPQC SYSTEM 13       | 38 |

|      | TABLE 7-I COMMUNICATION DELAY EFFECT                                          | 52 |

|      | TABLE 7-II MEASURED POWER ANALYSIS PARAMETERS FOR VARIOUS TYPES OF LOADS 16   | 58 |

|      | TABLE 7-III SYSTEM SPECIFICATIONS                                             | 59 |

|      | TABLE 8-I TL-UPOC SYSTEM FEATURES                                             | 75 |

# **List of Figures**

| Figure 1-1.       | Voltage fluctuations of 161 kV substation supplying an electric arc furnace load |

|-------------------|----------------------------------------------------------------------------------|

| [3]               | 2                                                                                |

| Figure 1-2.       | Power quality problems classification [4] 4                                      |

| Figure 2-1.       | General block diagram of UPQC topology (a) VSC (b) CSC                           |

| Figure 2-2.       | Classification of UPQC [20]                                                      |

| Figure 2-3.       | (a) 1P2W FB UPQC topology (b) 1PP2W HB UPQC topology (c) 1P2W three-             |

| leg UPQC topolo   | pgy                                                                              |

| Figure 2-4.       | (a) 3P3W UPQC topology (b) 3P4W UPQC topology                                    |

| Figure 2-5.       | Left UPQC configuration. 21                                                      |

| Figure 2-6.       | (a) DG unit integration with UPQC (b) Battery integration with UPQC 22           |

| Figure 2-7.       | UPQC configuration with (a) interline (b) multi-converter                        |

| Figure 2-8.       | Phasor diagrams of DVR compensation methodologies (a) UPQC-P (b) UPQC-           |

| Q (c) UPQC-S      |                                                                                  |

| Figure 2-9.       | (a) Instantaneous reactive power control technique (b) Synchronous reference     |

| frame control tec | Phnique                                                                          |

| Figure 2-10       | Voltage control mode of a D-STATCOM in the d-q frame [57], [58] 29               |

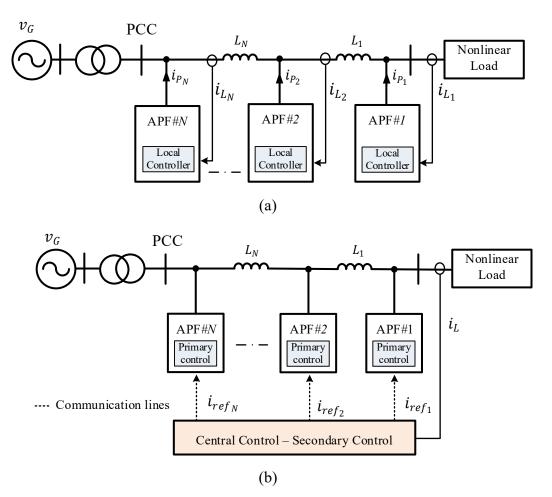

| Figure 2-11.      | (a) Decentralized control scheme (b) centralized control scheme                  |

| Figure 2-12.      | (a) Master/slave control scheme (b) distributed control scheme                   |

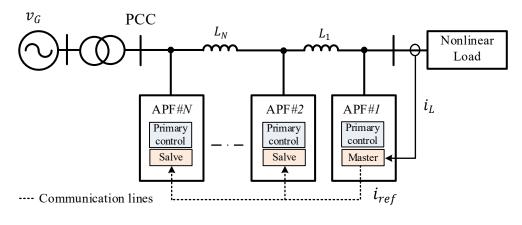

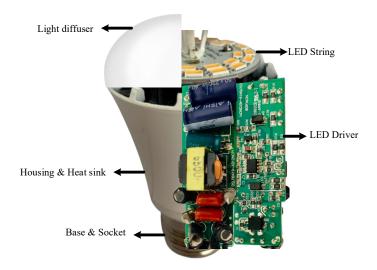

|      | Figure 3-1.     | Sectional view diagram of an LED lamp                                         | 37  |

|------|-----------------|-------------------------------------------------------------------------------|-----|

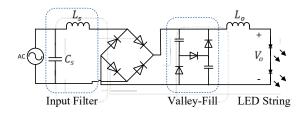

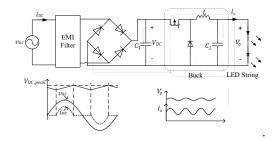

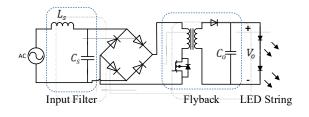

|      | Figure 3-2.     | Passive LED driver based on valley-fill circuit [92].                         | 40  |

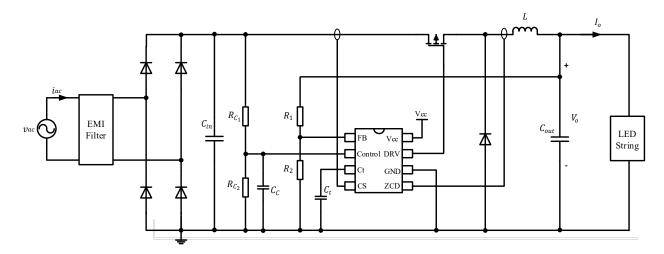

|      | Figure 3-3.     | Single-stage LED driver based on buck converter                               | 40  |

|      | Figure 3-4.     | Single-stage LED driver based on flyback converter                            | 40  |

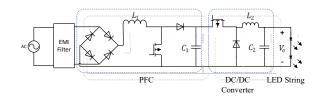

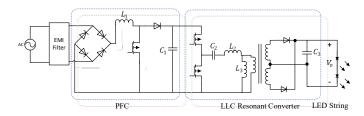

|      | Figure 3-5.     | Two-stage LED driver.                                                         | 40  |

|      | Figure 3-6.     | Conventional two-stage LED driver for high power applications                 | 40  |

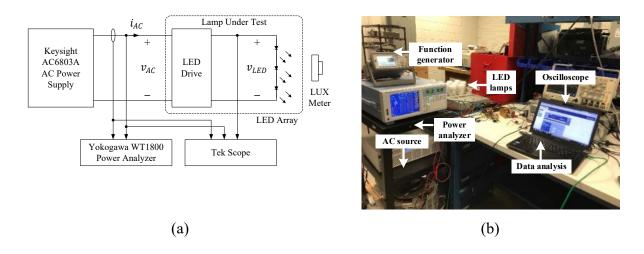

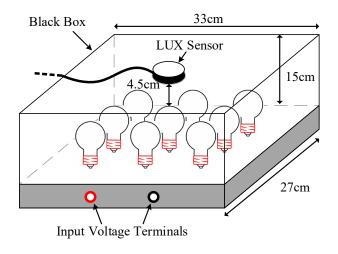

|      | Figure 3-7.     | Experimental setup (a) block diagram (b) laboratory setup.                    | 45  |

|      | Figure 3-8.     | Black box dimension.                                                          | 45  |

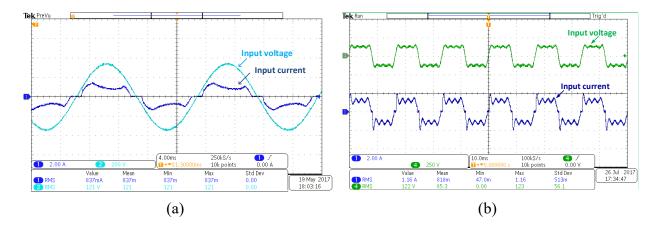

|      | Figure 3-9.     | Input voltage and input current drawn by LEDs (a) sinusoidal input voltage (  | (b) |

| dist | torted input vo | ltage                                                                         | 49  |

|      | Figure 3-10.    | Harmonic spectrum of the current drawn by the LEDs                            | 50  |

|      | Figure 3-11.    | Input voltage vs (a) LED voltage and (b) light intensity                      | 51  |

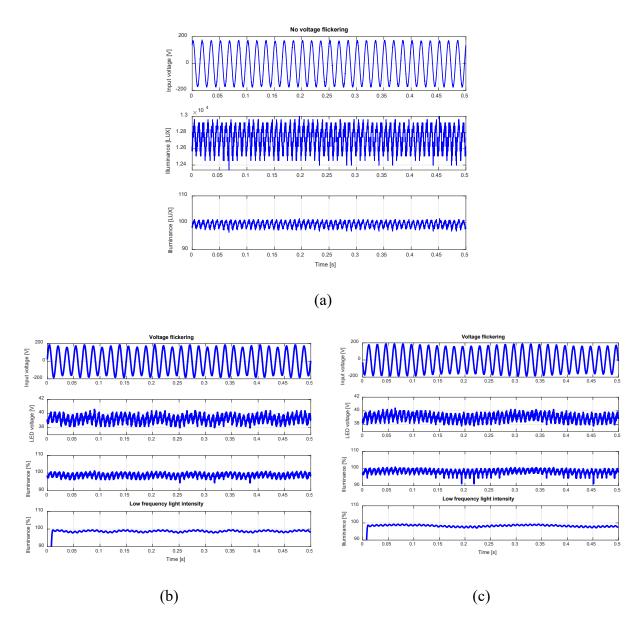

|      | Figure 3-12.    | Applied voltage flickering to LED lamps                                       | 55  |

|      | Figure 3-13.    | LED voltage and light intensity with (a) no flickering input voltage (b) 15 l | Hz  |

| vol  | tage flickering | g (c) 4 Hz voltage flickering.                                                | 56  |

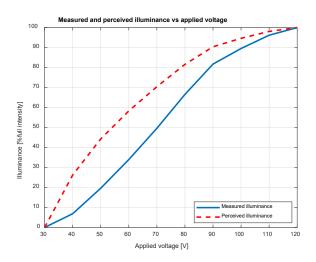

|      | Figure 3-14.    | Measured and perceived light intensity under different voltage levels         | 58  |

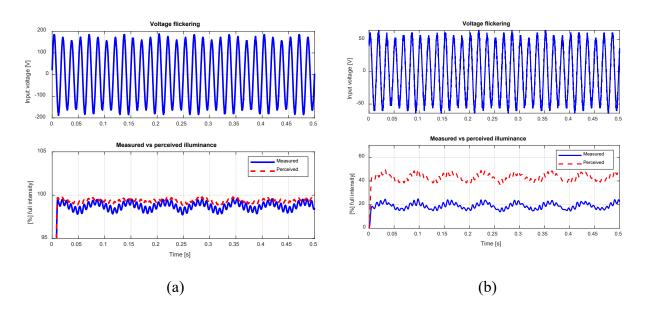

|      | Figure 3-15.    | Measured and perceived illuminance with voltage flickering (a) 100% lig       | ght |

| inte | ensity (b) 16%  | light intensity                                                               | 58  |

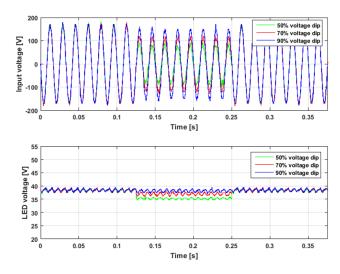

|      | Figure 3-16.    | Voltage across the LED for different applied voltage sag levels               | 60  |

|      | Figure 3-17.    | LED voltage at (a) 23% voltage sag (b) 110% voltage swell                     | 60  |

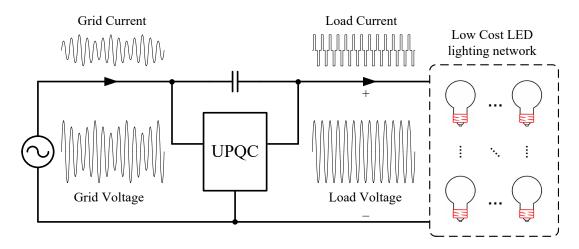

| Figure 4-1.      | The conceptual idea of a TL-UPQC to solve PQ issues of a LED lighting           |

|------------------|---------------------------------------------------------------------------------|

| network          |                                                                                 |

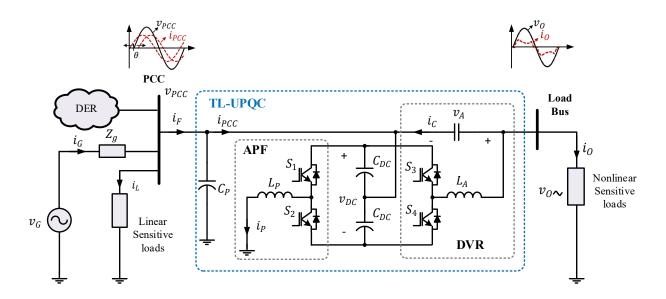

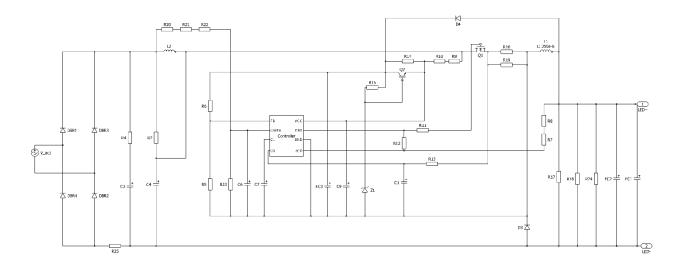

| Figure 4-2.      | The proposed single-phase TL-UPQC                                               |

| Figure 4-3.      | (a) Steady-state circuit model of the proposed TL-UPQC (b) a block diagram of   |

| power flow in th | e TL-UPQC system 66                                                             |

| Figure 4-4.      | Phasor diagrams of (a) normal operation (b) voltage swell (v) voltage sag 68    |

| Figure 4-5.      | Half-bridge inverter configuration of APF                                       |

| Figure 4-6.      | Control block diagram of the APF                                                |

| Figure 4-7.      | Half-bridge inverter configuration of DVR                                       |

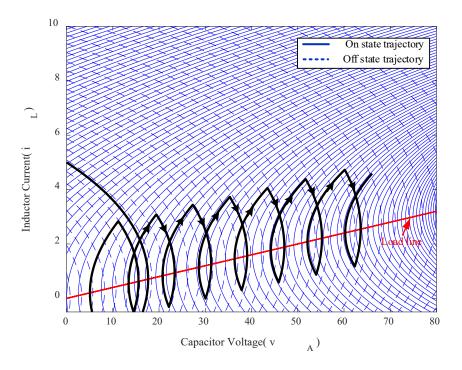

| Figure 4-8.      | Switching trajectories of DVR                                                   |

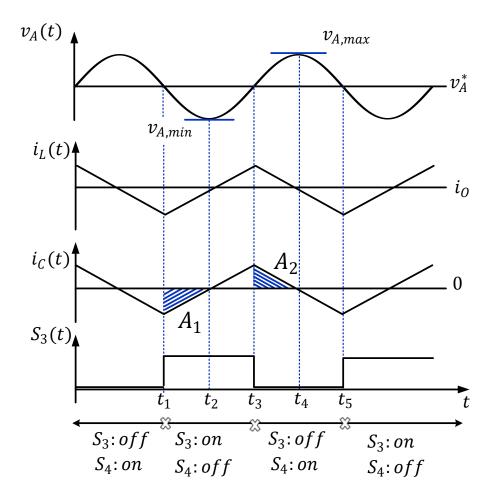

| Figure 4-9.      | Typical waveforms of the DVR [115]74                                            |

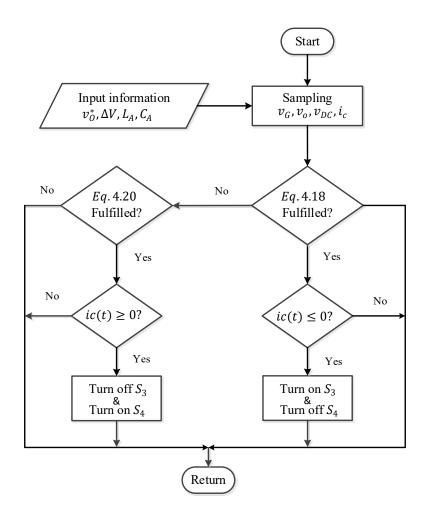

| Figure 4-10      | Flow chart of boundary control law                                              |

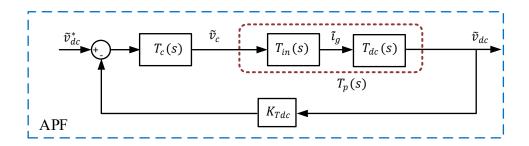

| Figure 4-11      | . Small-signal control block diagram of the shunt APF converter                 |

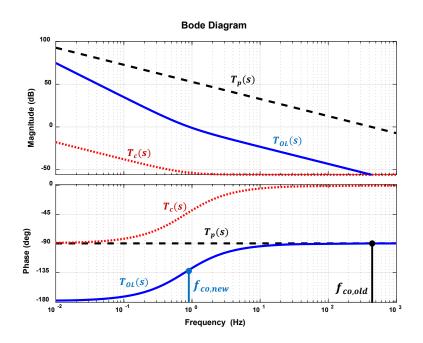

| Figure 4-12      | . Frequency response of power stage $(Tp)$ , controller $(Tc)$ and Overall open |

| loop system (TO  | L)80                                                                            |

| Figure 4-13      | Small-signal control block diagram of the DVR converter                         |

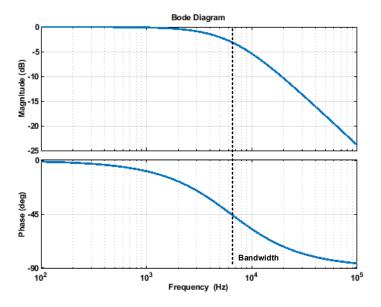

| Figure 4-14      | Frequency plot of boundary control                                              |

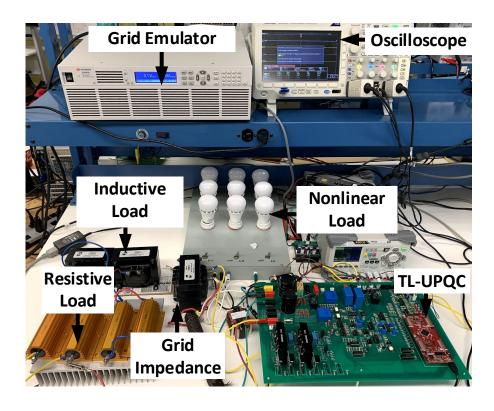

| Figure 4-15      | Experimental setup                                                              |

| Figure 4-16      | . Connection diagram for frequency response analyzer Bode 100 87                |

| Figure 4-17      | Frequency response of mathematical model, simulation and experiment 88          |

| Figure 4-18.      | APF experimental results with (a) linear (b) nonlinear load                     |

|-------------------|---------------------------------------------------------------------------------|

| Figure 4-19.      | DVR results for voltage flickering of 6Hz (a) 100 ms/div (b) 20 ms/div 90       |

| Figure 4-20.      | DVR results for (a) over voltage 135V (b) under voltage 90V91                   |

| Figure 4-21.      | Voltage sag waveforms in time scale of (a) line cycle, and (b) switching cycle. |

|                   | 91                                                                              |

| Figure 4-22.      | Voltage waveforms for input voltage swell                                       |

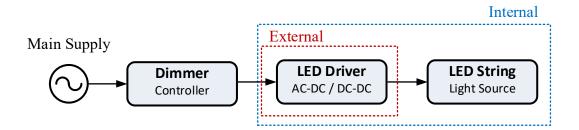

| Figure 5-1.       | An LED dimming system. 93                                                       |

| Figure 5-2.       | Proposed remote control VSC dimmer system                                       |

| Figure 5-3.       | Dimming techniques (a) AM (b) PWM                                               |

| Figure 5-4.       | Standard TRIAC-dimmer lighting system                                           |

| Figure 5-5.       | 0-10V dimmer system                                                             |

| Figure 5-6.       | DALI dimmer system. 100                                                         |

| Figure 5-7.       | Wireless dimmer system                                                          |

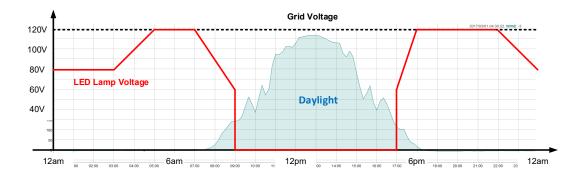

| Figure 5-8.       | Example of dimming profile for street lighting system                           |

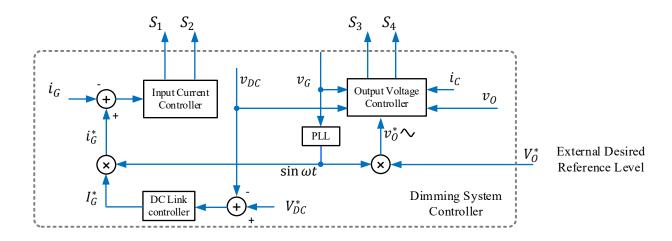

| Figure 5-9.       | Modified TL-UPQC control strategy for the addition of dimming function. 103     |

| Figure 5-10.      | Equivalent circuit of VSC dimmer system                                         |

| Figure 5-11.      | Phasor diagrams of VSC dimmer system under a dimming level (a) steady-          |

| state (b) voltage | swell (c) voltage sag. 105                                                      |

| Figure 5-12.      | Power flow under a dimming level (a) steady-state (b) voltage swell (c) voltage |

| sao               | 105                                                                             |

| Figure 5-13      | 3. System architecture of communication and interface                          |

|------------------|--------------------------------------------------------------------------------|

| Figure 5-14      | 4. Small-signal model the VSC dimmer system control scheme                     |

| Figure 5-15      | 5. Estimated loss in 500VA, 120V VSC dimmer system                             |

| Figure 5-16      | 5. Estimated Efficiency of the VSC dimmer system under various dimming levels, |

| 20%, 50% and 8   | 30% of rated illuminance                                                       |

| Figure 5-17      | 7. Testbed setup                                                               |

| Figure 5-1       | 8. Waveforms at 50% illuminance with (a) TRIAC-based dimmer (b) VSC            |

| dimmer system.   |                                                                                |

| Figure 5-19      | Power quality measurements comparison (a) THD of input current (b) THD of      |

| lamp voltage (c) | PF (d) efficiency (e) output/input power (f) input VA                          |

| Figure 5-20      | ). 70% dimming level under voltage sag and voltage swell                       |

| Figure 5-21      | 1. Webpage GUI for dimming lighting systems                                    |

| Figure 5-22      | 2. Webpage Light intensity feedback signal                                     |

| Figure 5-23      | 3. Desktop application for dimming lighting systems                            |

| Figure 6-1.      | TL-UPQC topology for voltage regulation in LV Distribution Network 119         |

| Figure 6-2.      | Phasor diagrams of (a) PFC mode (b) capacitive mode (c) inductive mode. 121    |

| Figure 6-3.      | A block diagram of power flow in a TL-UPQC system                              |

| Figure 6-4.      | Control block diagram of the enhanced control methodology                      |

| Figure 6-5.      | Small-signal block diagram of the dc voltage loop                              |

| Figure 6-6       | Small-signal block diagram of the ac voltage loop.                             |

| Figure 6-7.      | Frequency response of the dc voltage loop without a compensator               |

|------------------|-------------------------------------------------------------------------------|

| Figure 6-8.      | Frequency response of the dc voltage loop including a compensator 133         |

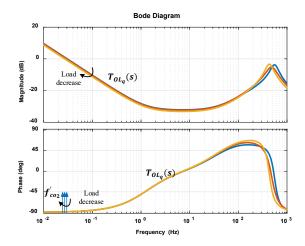

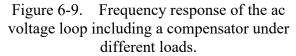

| Figure 6-9.      | Frequency response of the ac voltage loop including a compensator 133         |

| Figure 6-10.     | Experimental test block diagram                                               |

| Figure 6-11.     | Laboratory setup                                                              |

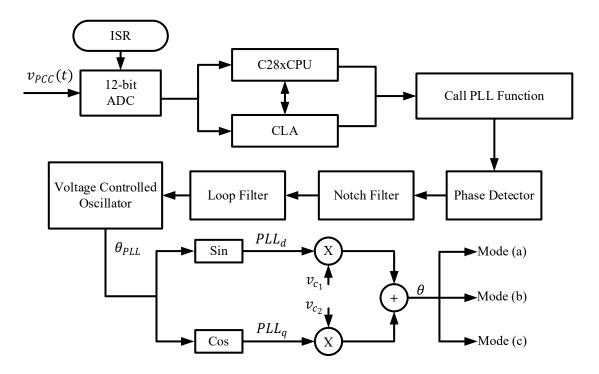

| Figure 6-12.     | Block diagram of PLL implantation in DSP                                      |

| Figure 6-13.     | System waveforms for nonlinear loads at the load bus (a) without TL-UPQC      |

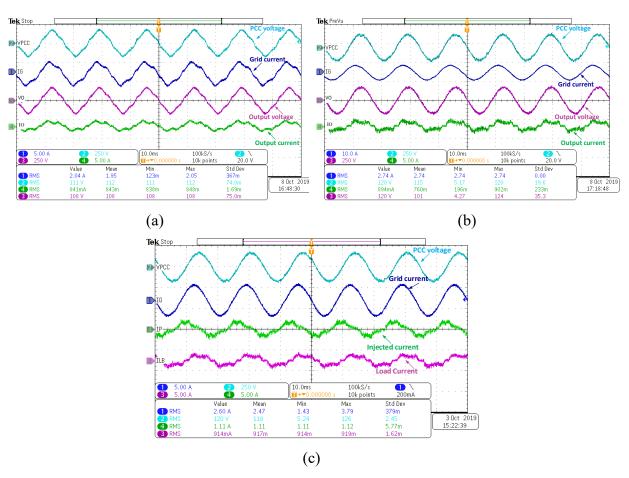

| (b) with TL-UPQ  | C                                                                             |

| Figure 6-14.     | System waveforms during an under voltage for linear loads at the load bus     |

| (a) without TL-U | PQC (b) with TL-UPQC                                                          |

| Figure 6-15.     | System waveforms during an over voltage for linear loads at bus B (a) without |

| TL-UPQC (b) with | th TL-UPQC141                                                                 |

| Figure 6-16.     | Waveforms with TL-UPQC system ( $Ssag = ON$ ) (a) a sudden load change at     |

| PCC bus (b) with | rapid voltage fluctuation                                                     |

| Figure 7-1.      | Conventional central D-STATCOM architecture                                   |

| Figure 7-2.      | Proposed modularized distributed TL-UPQC systems architecture 144             |

| Figure 7-3.      | Topology and structure of an individual TL-UPQC system                        |

| Figure 7-4.      | Control scheme of parallel operation of distributed TL-UPQC systems 152       |

| Figure 7-5.      | Small-signal control block diagram of CC and one LC                           |

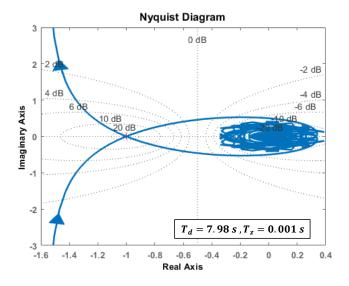

| Figure 7-6. Frequency response of the dc voltage loop gain (TOLd) and the ac voltage loop  | op  |

|--------------------------------------------------------------------------------------------|-----|

| gain ( <i>TOLq</i> )15                                                                     | 59  |

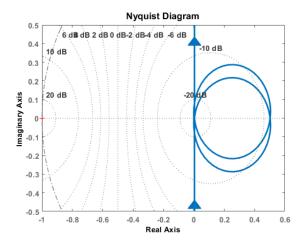

| Figure 7-7. Nyquist diagram of the ac voltage loop gain without communication effective.   | eci |

| TOLq(s)15                                                                                  | 59  |

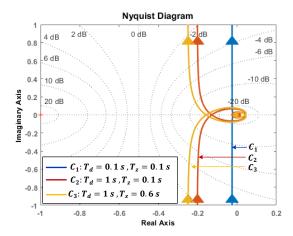

| Figure 7-8. Nyquist plot of the ac voltage loop gain under various communication dela      | ıys |

| TOLq'(s)15                                                                                 | 59  |

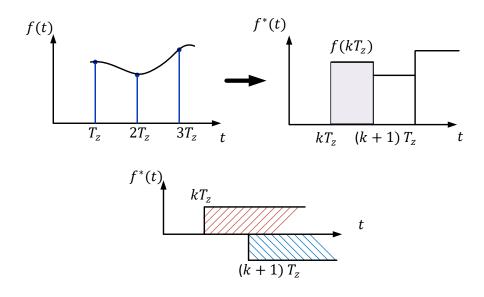

| Figure 7-9. Impulse sampling representation of ZOH                                         | 61  |

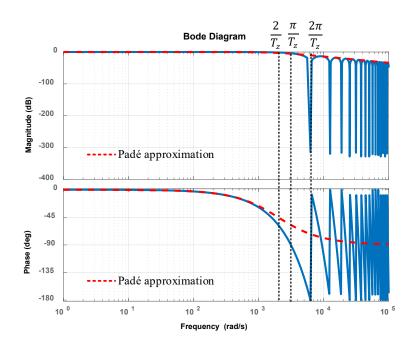

| Figure 7-10. Frequency response of ZOH                                                     | 61  |

| Figure 7-11. Marginally stable Nyquist plot of the ac voltage loop                         | 63  |

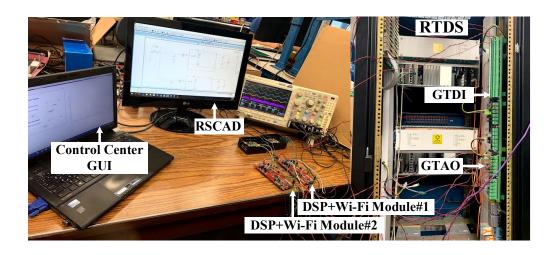

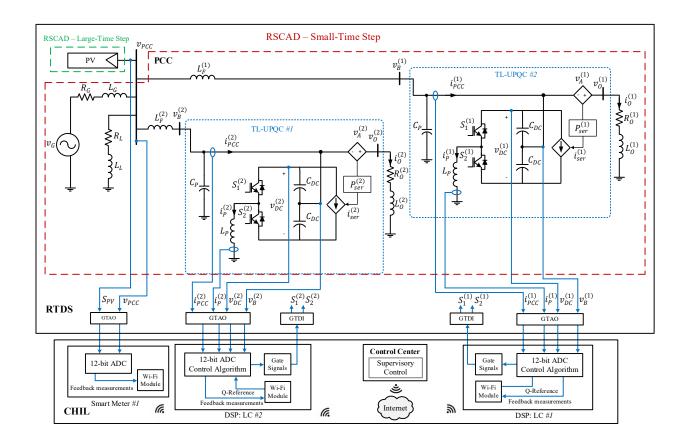

| Figure 7-12. Controller hardware-in-the-loop (CHIL) testbed                                | 65  |

| Figure 7-13. System implementation using CHIL with RTDS                                    | 65  |

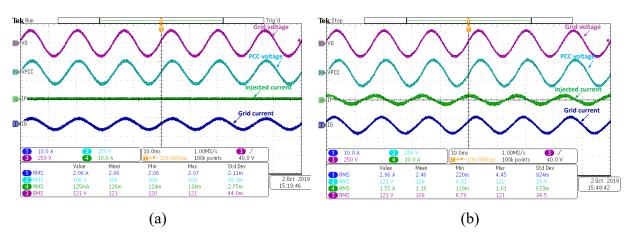

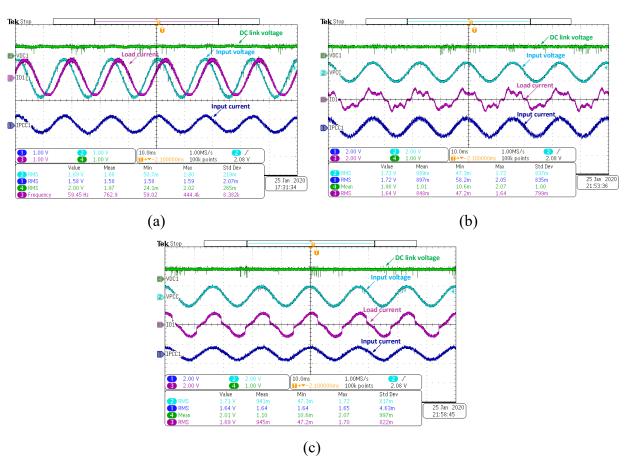

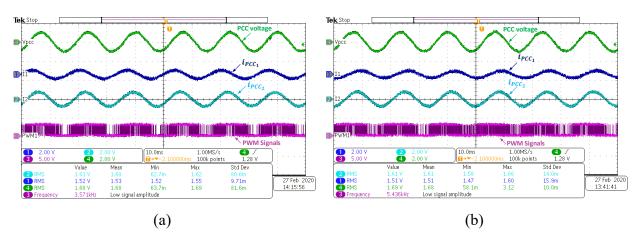

| Figure 7-14. PFC mode (experimental results with (a) linear (b) nonlinear load – LED lam   | ıps |

| (c) nonlinear load – rectifier bridge circuit.                                             | 67  |

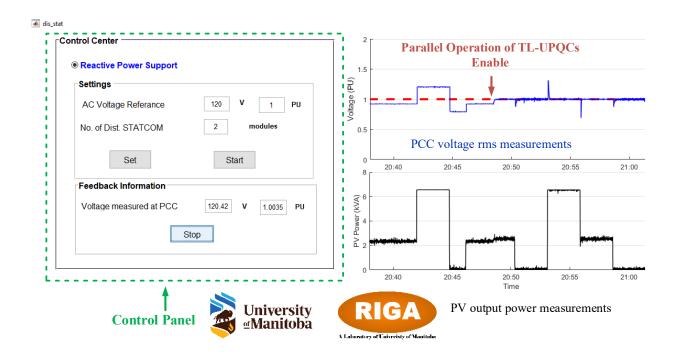

| Figure 7-15. GUI - control center panel. 17                                                | 70  |

| Figure 7-16. Steady-state waveforms for (a) capacitive mode (b) inductive mode 17          | 70  |

| Figure 7-17. Steady-state waveforms captured in RTDS for (a) capacitive mode (b) inductive | ive |

| mode17                                                                                     | 71  |

| Figure 7-18. Dc link measurements as captured in RTDS                                      | 71  |

#### **List of Abbreviations**

1P2W Single-phase two-wire 3P3W Three-phase three wire 3P4W Three-phase four wire

ADC Analogue to digital converter

AlGa Aluminum Gallium arsenide

AM Amplitude modulation

APF Active power filter

BCSSS Boundary control with second order switching surface

CC Central controller

CFL Compact fluorescent lamps

CHIL Controller hardware-in-the-loop

CLA Control low accelerator

CM Common-mode

CSC Current source converter

CSI Current source inverters

DALI Digital addressable lighting interface

DER Distributed energy resources

DG Distributed generation

DSP Digital signal processer

D-STATCOM Distribution static synchronous compensator

DVR Dynamic voltage restorer

E-Caps Electrolytic capacitors

EMI Electromagnetic interference

ePWM Enhanced pulse width modulation FACTS Flexible ac transmission systems

FB Full-bridge

FPGA Field-programmable gate array

GaN Gallium Nitride GaP Gallium phosphide

GPIO General-purpose input/output

GTAO Giga-transceiver analogue output

GTDI Giga-transceiver digital input

GUI Graphical user interface

HB Half-bridge

HBVSI Half-bridge voltage source inverter

HID high-intensity discharge

HPF High pass filter

HPS High pressure sodium

HPS Hypertext transfer protocol

IGBT Insulated-gate bipolar transistors

InGaN Indium Gallium Nitride

IP Internet protocol

ISR Interrupt service routine

LC Local controller

LED Light emitting diode

LPF low pass filter LV Low voltage

MMC Multi-modular converter

MV Medium voltage

OLED Organic light emitting diode PCC Point of common coupling

PF Power factor

PFC Power factor correction

PLL Phase locked loop

PQ Power quality

PV Photovoltaic

PWM Pulse width modulation rms Root-mean-square

RTDS Real time digital simulator

SCR Short circuit ratio

Si Silicon

SiC Silicon Carbide

SPI Serial peripheral interface SRF Synchronous reference frame

SSH Secure shell SSL Solid-state lighting

STATCOM Static synchronous compensator

THD Total harmonic distortion

TL-UPQC Transformerless unified power quality conditioner

UART Asynchronous receiver/transmitter

UPFC Unified power flow conditioner

UPQC Unified power quality conditioner

UPQC-DG Distributed generation unified power quality conditioner

UPQC-L Left unified power quality conditioner UPQC-R Right unified power quality conditioner

UPS Uninterruptible power supply VSC Voltage source converter VSI Voltage source inverters

WBG Wide bandgap

# Chapter 1 Introduction

#### 1.1 Background

Increasing advances in smart grid technologies aim for a more efficient and reliable network. Following the widespread use of solid-state controls for power conditioning, power quality (PQ) has become a significant issue. Currently, the practice of achieving high PQ standards is very challenging due to the extensive employment of power electronics-based appliances. Poor PQ will ultimately influence various sectors including industrial processes, essential services, residential applications, commercial investments, etc. Equipment may malfunction or be damaged during a voltage sag or a voltage swell. Besides, loads based on advanced electronic devices are very sensitive to PQ variations, which directly affect many customers. Therefore, both the utility and consumers require high demand for improved PQ parameters.

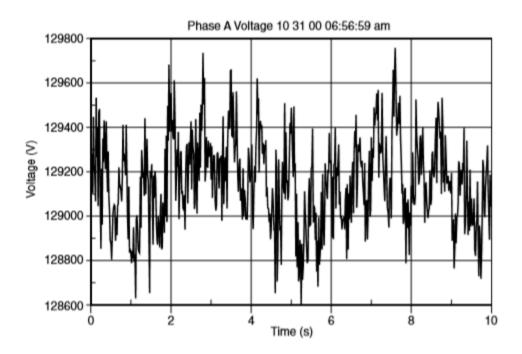

Manitoba Hydro has set certain standards to deliver a reliable and a high quality power service to every customer whose lines are connected to their network [1]. However, the company has been striving to achieve a flicker free network after receiving 57 reports of blinking LED street lights across the province [2]. In addition to the concerns that light flicker could trigger seizure for people with certain medical condition. Light flickering is frequently recounted in cities with large steel industry, since electric arc furnaces represent a major source of voltage fluctuations happening in

the network as indicated in Figure 1-1 [3].

In this chapter, PQ definitions and terms that are used in the conducted research are presented. Causes and effects of PQ issues are discussed. A quick overview of PQ standards and measurements are given. The motivation of the conducted research is highlighted followed by research objectives, author contributions and the organization of this thesis.

Figure 1-1. Voltage fluctuations of 230 kV substation supplying an electric arc furnace load [3].

## 1.2 Overview of Power Quality Definition and Standards

According to [3], PQ is mainly a consumer driven issue and can be defined from the user point of view as "any power problem revealed in voltage, current, or frequency deviations, that results in failure or malfunction of customer equipment". It can also be defined as "the characteristics of power supply that enable the equipment to work properly".

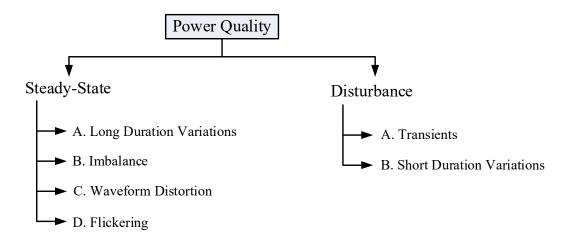

PQ issues are related to both voltage quality and current quality. There are international standards that have been formalized to define the guidelines of the power quality characteristics that customers should expect from their local electric utility. IEC and IEEE are the main organizations for PQ standards and requirements in the international community. Table 1-I gives most commonly standards of recommended practices for voltage and current characteristics. In general, PQ issues are classified into two main groups [4]; steady-state and disturbances as illustrated in Figure 1-2. The steady-state category is specified for continuous and periodic characteristics (voltage regulations, i.e. long duration voltage variations, unbalance, harmonics and flickering). On the contrary, disturbance appears randomly and occurs for a short time (transients, short duration voltage variations and interruptions). PQ causes and their consequences are summarized in the following subsection [3].

TABLE 1-I POWER QUALITY STANDARDS

| Standard       | Specification                                                                             |

|----------------|-------------------------------------------------------------------------------------------|

| IEEE 1159      | Provides power quality definitions, terms description and general guidelines              |

| EN 50160       | Specifies voltage characteristics provided by the supplier in public distribution systems |

| IEEE Std 1547  | Provides technical requirements and specifications regarding distributed resources.       |

| IEC 61000-3-2  | Specifies harmonic currents injection limitation into the public grid                     |

| IEEE 519       | Gives recommended practices of voltage and current harmonics in electric power systems    |

| IEC 61000-3-3  | Sets limitation of voltage fluctuations and flickering reverted on the public grid        |

| IEC 61000-4-15 | Identifies design specifications for flickering measuring techniques and devices          |

| IEEE PAR1789   | Addresses human biological effects due to visible and invisible light flicker             |

Figure 1-2. Power quality problems classification [4].

### 1.2.1 Power Quality Steady-State Issues

#### A. Long Duration Voltage Variations

As stated by IEEE Standard 1159 [6], long duration root-mean-square (rms) voltage variations are deviations in voltage that last for longer than 1 min. These variations are either over voltages or under voltages. Typical values for an over voltage are between 1.1 to 1.2 pu, while an under voltage is a decrease in the rms voltage, typically ranges between 0.8 to 0.9 pu. The supply voltage characteristic according to EN 50160 [7] should be within  $\pm 10\%$  of its nominal value for 95% of the week. Protection circuit breakers should be designed to trip when the system voltage exceeds these limits. IEEE Std 1547 [8] sets the maximum acceptable voltage deviation caused by a distributed generation (DG) unit to be  $\pm 5\%$  at PCC.

Causes: load changes and utility faults. Over voltages are caused by switching off heavy loads or connection of a large capacitor bank. On the other hand, switching on large loads, and overloaded networks are the cause of under voltages.

Consequences: reduced lifetime of equipment, system shutdown and loss of data.

#### B. Imbalance

Imbalance, also called unbalance, is a PQ problem related to both voltage and current in a three-phase system. It is defined in ANSI C84.1 [9] as "the maximum deviation from the average of the three-phase voltages or currents, divided by the average of the three-phase voltages or currents, expressed in percent". The imbalance is calculated in IEEE Standard 1159 as follows,

$$\%Imbalance = \frac{V_{neg}}{V_{pos}} \times 100 \% \tag{1.1}$$

where,  $V_{neg}$  is the magnitude of the negative sequence components and  $V_{pos}$  is the positive sequence component.

In general, a voltage/current unbalance in a three-phase system is a phenomenon in which the three voltage/current magnitudes or the phase-angle differences between them are not equal. The maximum voltage unbalance recommended by ANSI C84.1 under no load conditions is 3%. The limit specified by EN 50160 should not exceed 2% for normal system and 3% for systems with single-phase loads.

Causes: unequal single-phase loading in a three-phase system. Faults results in broken fuses of one phase of a three-phase capacitor bank.

Consequences: negative sequence induced into the system, which is harmful to three-phase loads. Heating and failure of loads.

#### C. Waveform Distortion

A waveform distortion is a deviation from the ideal sinusoidal waveform. This deviation is characterized by the spectral content of the waveform, which contains dc offset, harmonics, interharmonics, notching and noise [1]. Voltage and current harmonics are the primary concern of the PQ of the network. Harmonic components are sinusoidal components with frequencies that are equal to integer multiples of the fundamental frequency (usually 50 or 60 Hz). Fourier series can represent a distorted periodic waveform by an infinite number of sinusoidal waves, which contain the fundamental frequency and the harmonics components. Nonlinear loads create harmonic currents. The interaction of harmonic currents with the system impedance will cause harmonic voltage distortion. The term total harmonic distortion (THD) is used to measure the distortion factor of a waveform with respect to its fundamental component. The THD of current  $THD_i$  and voltage  $THD_v$  are calculated using the following expressions respectively,

$$THD_{i} = \frac{\sqrt{\sum_{h=2}^{\infty} I_{h}^{2}}}{I_{1}}$$

(1.2)

$$THD_{v} = \frac{\sqrt{\sum_{h=2}^{\infty} V_{h}^{2}}}{V_{1}}$$

(1.3)

where, h is harmonic order,  $I_h$  and  $V_h$  are rms value of the harmonic component order n of current and voltage respectively, while  $I_1$  and  $V_1$  are rms value of the fundamental component of current and voltage respectively.

IEC 61000-3-2 [10] and IEEE 519 [11] standards are widely adopted recommendations practice for harmonic control in electric power systems. IEEE 61000-3-2 provides limitation of harmonic current emissions that are being injected into the public grid. This standard is applicable

for equipment connected to the low voltage (LV) distribution network with a 16 A per phase. For each individual harmonic current component, a certain percentage of the fundamental current limit is set. IEEE 519 provides guidelines for voltage as well as current harmonic emissions. For bus voltage below 1 kV, the maximum THD in voltage distortion is 8%, while it is 5% for bus voltage between 1 kV and 69 kV. The current THD considering harmonic components up to the 50<sup>th</sup> order excluding interharmonics is limited to 5%.

It is noteworthy that lower THD in power systems will result in higher power factor (PF) and higher efficiency. The term power factor is the ratio of the total power input in watts to the total apparent power in VA. PF is calculated using the following expression [12],

$$PF = \frac{1}{\sqrt{1 + THD_i^2}} \cos(\theta_v - \theta_i) \tag{1.4}$$

Where,  $\theta_v - \theta_i$ : is the phase difference between voltage and current.

For linear loads, the PF will be equal to  $\cos(\theta_v - \theta_i)$ . This is not the full definition of power factor and is called displacement power factor. The displacement power factor is only true if both voltage and current waveforms are sinusoidal. Therefore, PF is calculated in terms of distortion factor and displacement power factor.

Causes: nonlinear loads such as arc furnace, arc welder, all power electronics equipment, switched mode power supply, adjustable speed drives, and LED lamps.

Consequences: overheating in cables and equipment, high core and copper losses in motors and transformers, lower efficiency, and electromagnetic interference (EMI) with communication systems.

#### D. Flickering

Flickering is a voltage fluctuation with regular variation. It is defined as "a series of random or continuous voltage changes" [3]. Voltage magnitude changes and the frequency by which the change take place are used to characterize the flickering phenomenon [4]. The term flicker is derived from the impact of voltage changes on the variation of the light intensity of lamps in a way that will be perceived by the human eye. Flickering at certain frequencies have direct human health risks that have been addressed by IEEE PAR1789 [13]. IEC 61000-3-3 [14] specifies limitation of voltage fluctuations in LV distribution network, while IEC 61000-4-15 [15] sets the international standard to design apparatus (flickermeter) for flickering measurements. The flickermeter gives two measurements, short-term flicker severity ( $P_{st}$ ) for a period of 10 min and long-term flicker severity ( $P_{lt}$ ) that takes an evaluation time of 12 consecutive short-term flicker severity index. According to IEC 6100-3-3 the flicker perception level of the  $P_{st}$  index and the  $P_{lt}$  should not exceed 1 and 0.65 respectively, in order to comply with the user's preferences for a comfortable environment.

Causes: arc furnace, arc welder and frequent start/stop of heavy loads.

Consequences: Visual perception of flickering for various lighting sources.

## 1.2.2 PQ Disturbances Issues

#### A. Transients

Transient is a fast change in voltage or current. Transients can be measured by the peak magnitude, the rate of rise or the change of a waveform from one operating point to the next operating point. Transients are classified into impulsive and oscillatory transient. Impulsive

transient is a unidirectional sudden change in the steady-state condition of voltage/current. In contrast, oscillatory transient is a bidirectional sudden change in the steady-state condition of voltage/current [1], [4].

Causes: Switching of capacitive or inductive loads, lighting surge and utility fault clearing.

Consequences: Loss of data and possible damage.

#### B. Short Duration Voltage Variations

Short duration voltage variations are changes in voltage magnitude that last less than 1 min as defined in IEEE 1159 standard. These variations are temporary, and it can be either an increase (voltage swell), or a decrease (voltage sag) in voltage magnitude or a total loss of voltage supply (interruption). According to EN50160 standard, a voltage dip (sag) is a sudden decrease in rms voltage between 0.1 to 0.9 pu for durations from 0.5 cycle to 1 min. Whereas, a voltage swell is a sudden increase in rms voltage between 1.1 to 1.8 pu for duration from 0.5 cycle to 1 min. An interruption occurs when the supply voltage decreases to lower than 0.1 pu of the nominal voltage.

Causes: A fault in the power system, utility failure, component failure, starting of heavy loads and large motors.

Consequences: Circuit breaker tripping, loss of data, equipment damage, short lifetime and malfunction.

# 1.3 Motivation and Research Objectives

Consequent to recent developments in the technology of solid-state lighting (SSL) and hence light emitting diode (LED) lamps, high luminous intensity LEDs are now taking a significant share

of the lighting sources market. It is well known that the main advantages of utilizing LED lamps are long lifetime and low energy consumption compared to conventional lighting technologies, such as incandescent lamps and florescent lamps [16], [17]. However, some low-cost LED lamps inject harmonic currents into the grid, which affect the power system network especially in a large-scale lighting system such as a street lighting network and a parking building lighting network [18]. In addition, LED lamps are sensitive to power system disturbances like voltage sags and voltage flickering. Even though a voltage sag lasts for few milliseconds it may cause the lamp to flicker or even get damaged in some cases. This is particularly important for lighting networks, which are located near electric arc furnaces [19], since light intensity changes rapidly in response to voltage flickers.

The work done in this thesis is intended to develop a comprehensive solution for most power quality problems related to modern lighting loads. The ultimate goal is to remove flickering on LED lighting networks, which is a major concern to many users, and to enhance the overall electric power quality at distribution levels. Specific objectives followed in this research can be listed as follows,

- Review PQ standards and existing active power filter (APF) topologies to fulfill these standards in LV distribution networks.

- Review LED lamp technology including LED drivers, LED PQ standards and LED dimming techniques.

- Characterize and analyze different aspects of the behavior of commercial LED lamps to comprehend the main causes of PQ issues linked to LEDs utilization. This characterization is essential before developing a solution that limits LEDs influences on

system PQ parameters.

- Employ APF as a promising solution for PQ problems related to LED lighting networks.

The system is intended to,

- a) Mitigate voltage flickering, by maintaining the voltage across the LEDs at a constant amplitude.

- b) Achieve a high dynamic response to be able to compensate for voltage sags and swells which are interpreted by the LEDs as a dimming request causing light flickering.

- c) Improve the PF and reduce the THD of the input current by eliminating harmonic components injected by LEDs.

- d) Allow amplitude voltage control to achieve light dimming and endorse energy saving.

- e) Provide input grid voltage support and improve the overall stability of the grid.

- Design and implement a transformerless unified power quality conditioner (TL-UPQC)

to mitigate current and voltage quality problems as discussed in the previous point.

- Validate the proposed topology through conducting various experimental tests while emulating PQ problems happening in the network.

- Develop a remote management central dimming technique for LED lamps applying the same power electronic apparatus.

- Maximize functions of the TL-UPQC system and extend its feature to deliver reactive power compensation for input grid voltage regulation.

- Provide stability analysis and design guidelines for the TL-UPQC system control methodology to achieve a desired performance including control system bandwidth and phase margin design.

- Formulate a suitable secondary control strategy that manages parallel operation of modularized TL-UPQC converters to improve grid voltage stability. The control methodology should cope with the new developments and structure of smart grid applications.

This thesis proposes a single-phase transformerless active power filter topology to achieve the goal of PQ improving for LED lighting networks. The apparatus serves as a power quality conditioner that is connected between the ac supply and LEDs. The proposed TL-UPQC mitigates most of voltage and current problems. It solves flickering phenomenon happening in the network. The system's control methodology attains stability and fast dynamic response for short disturbance. It should be emphasized that there is currently no developed solution for this problem in the literature or the market. A hardware prototype has been built to verify the theoretical findings with the experimental results. Steady-state and dynamic analysis have been performed.

## 1.4 Thesis Layout

This thesis is comprised of 8 chapters. The contents of the remainder of this thesis are briefly described as follows,

In chapter 2, since a unified power quality conditioner (UPQC) system has been adopted as the solution to solve PQ issues in LED lighting networks, this chapter focuses on reviewing UPQC topologies and control strategies. Grid voltage regulation techniques that have been proposed in the literature are also presented. In addition, parallel operation of modular converters is reviewed and discussed.

In chapter 3, a broad analysis of the main PQ issues related to the use of LEDs is presented. An overview of LED lamps technology is given including the structure, LED drivers and international regulations of LED lighting industry. PQ problems related to LEDs are discussed with proposed solutions in the literature. Then, the methodology followed in this research to evaluate the performance and the behavior of LEDs, laboratory setup description and experimental results are presented in detail.

In chapter 4, a comprehensive power quality conditioner, which is the TL-UPQC system is introduced. The topology's principle of operation and implementation are described. Stability of the designed controllers is analyzed by small-signal modeling technique and verified experimentally with a gain-phase analyzer. The chapter also presents a derived set of generalized equations to size the UPQC system. A description of the laboratory prototype along with experimental results to validate the operation of the TL-UPQC as a power quality conditioner is presented.

In chapter 5, the functions of the topology presented in Chapter 4 are extended to include a dimming function to LED lamps. The chapter reviews existing dimming techniques in the literature and the market to highlight the advantages of the proposed dimming technique. The implementation of the remote management system and data acquisition are explained. Small-signal characteristics and the influence of communication delay on system stability are analyzed. Experimental results and power analysis comparison between utilizing the TRIAC-based dimmer and the proposed TL-UPQC dimmer system for dimming function are conducted and discussed.

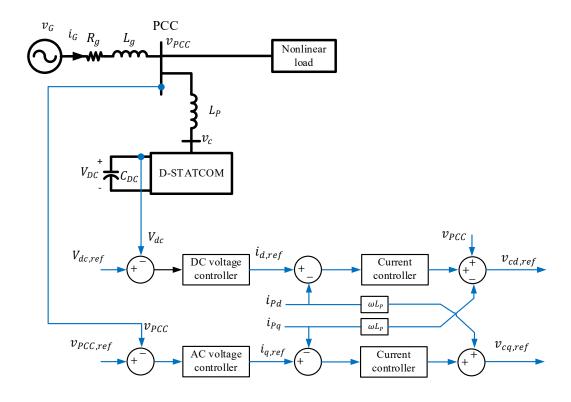

In chapter 6, the TL-UPQC will perform as a distribution static synchronous compensator (D-STATCOM) to provide reactive power support to the input grid, in addition to the features that have been presented in Chapter 4 and Chapter 5. The enhanced control strategy is developed in accordance to the controller design criteria. Three different modes of operation are analyzed according to the power flow analysis between the TL-UPQC system and the grid. System modeling for each control loop is studied. The laboratory prototype is applied to validate the proposed enhanced feature.

In chapter 7, parallel operation of distributed TL-UPQCs connected to low voltage distribution networks is proposed. The operation is intended to improve the grid voltage profile while considering the connected modules rated capacity. An advanced control technique that allows monitoring, wireless communication and coordination between the connected modules is presented. The proposed control methodology is evaluated by controller hardware-in-the-loop approach, where the power stage is simulated in a real time digital simulation, while the control algorithm is developed in a digital signal processor. Experimental results including random behavior of a photovoltaic system are presented.

In Chapter 8, the main points of this thesis are concluded. Future work recommended to further continue this research study is discussed.

# Chapter 2 Literature Review of Power Quality Mitigation in Distribution Networks

#### 2.1 Introduction

Nowadays, power electronic based devices signify a potential solution to maintain high PQ in modern power systems. While, flexible ac transmission systems (FACTS) are used to enhance the PQ in the ac transmission line networks, APFs mitigate harmonics and voltage disturbances in distribution networks. The principle of operation of an APF is to inject an equal and an opposite voltage/current to compensate the actual disturbance. There are three types of APFs: shunt, series and a combination of both. Shunt APF injects current into the grid to compensate for load current harmonics and reactive power consumption. On the other hand, series APF injects voltage to mitigate voltage disturbances propagating in the network, such as flickering, voltage swells and voltage sags. A UPQC is a combination of series and shunt active filters. Therefore, it is a cost effective and a comprehensive solution to suppress PQ issues that are related to both voltage and current disturbances. Therefore, the UPQC topology has been selected as the solution to compensate for voltage/current related problems existing in an LED lighting network.

## 2.2 UPQC - State of Art

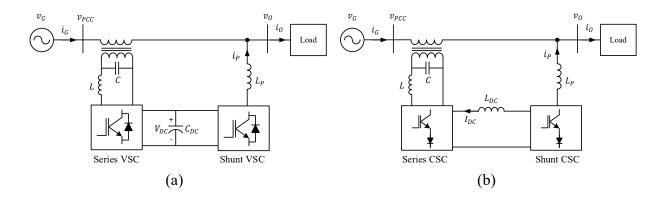

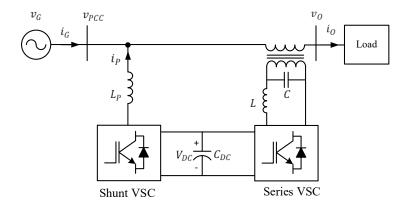

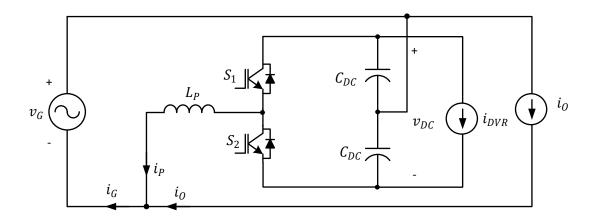

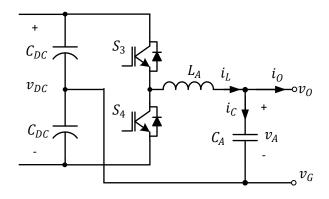

A literature review on UPQC topologies to improve the PQ of the network has been reported in [20]. A general block diagram of a UPQC topology is shown in Figure 2-1. It consists of two

inverters, a shunt inductor  $L_P$  and an LC filter. The shunt inductor connects the shunt inverter to the system and injects current to the network. The LC filter is a low pass filter (LPF) that cancels high frequency switching ripples in the inverter output voltage. The two inverters share a common dc link. A series transformer is required to step down the voltage or the current of the series inverter.

Figure 2-1. General block diagram of UPQC topology (a) VSC (b) CSC.

# 2.2.1 Classification of UPQC Topologies

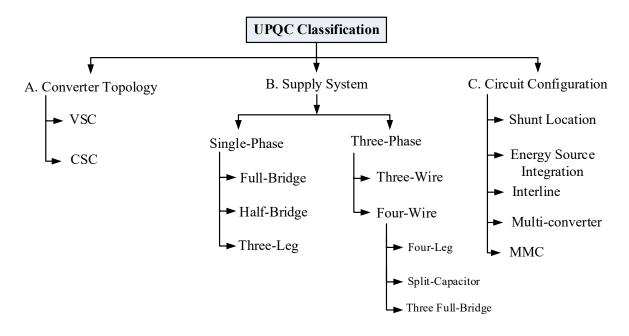

Figure 2-2 shows classification of UPQC topologies according to a) converter topology; voltage source converter (VSC) or current source converter (CSC) b) supply system; single-phase or three-phase system c) UPQC configuration that takes various converters configuration including shunt location, energy storage integration, interline, multi-converter and multi-modular converter (MMC) topologies [20].

Figure 2-2. Classification of UPQC [20].

#### A. Converter Topology

The most adopted converter topology is the VSC topology, which is shown in Figure 2-1 (a) [21], [22]. It consists of two voltage source inverters (VSIs) with a common energy storage capacitor  $C_{dc}$  as its dc link. The VSC is a cost-effective topology and offers the ability of multilevel operation for high voltage application. Nevertheless, the electrolytic capacitor limits the lifetime of the converter. Figure 2-1 (b) depicts the second topology, which is based on a CSC topology [23], [24]. In this topology, two current source inverters (CSI) share a common reactor  $L_{dc}$ . The CSC topology has an inherent protection capability against short circuits. However, it requires series connection of blocking diodes, which leads to high on-state losses. Moreover, high dc link losses are associated with the use of a bulky inductor.

A comparison study between VSC and CSC shunt active power filters has been investigated in [25]. It was concluded that both voltage and current source shunt active filters are effective for

filtering harmonics. The  $THD_I$  of the input current was less than 5% for both topologies. The major contribution of losses in the CSC topology was the dc link reactor. Whereas, the main source of losses in the VSC topology, was found to be the ac filter. The efficiency of the VSC topology was found to be higher than the efficiency of the CSC topology at nominal operating point. In addition, the CSC topology requires a separate clamp circuit for overvoltage protection, which adds complexity to the main circuit.

#### B. Supply System

UPQC systems are classified according to the input supply. The input source can be a single-phase or three-phase supply. Voltage and current unbalance compensation are additional PQ problems to be mitigated in a three-phase system. Other voltage and current related PQ problems are similar for both single and three-phase systems.

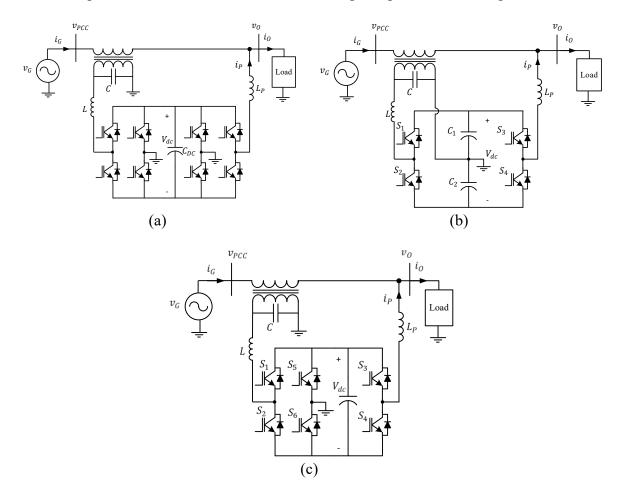

A conventional single-phase two-wire (1P2W) UPQC system topology comprises of two full-bridge (FB) converters as shown in Figure 2-3 (a) [26], [27]. It consists of eight switching devices, which increases the number of gate drivers as well as the conduction losses compared to other topologies. Though, as an advantage, a smaller filter size can be used if a unipolar switching technique is employed. A UPQC topology that is based on two half-bridge (HB) converters is shown in Figure 2-3 (b). The configuration requires less number of switching devices. It consists of two legs, one leg each for shunt and series inverters. This configuration has fewer semiconductor device counts. Nevertheless, it requires higher dc link voltage and higher breakdown voltage for semiconductors. Three-leg single-phase UPQC topology has been proposed in the literature [29]. It consists of six switches as shown in Figure 2-3 (c). Two HB converters are used; one leg (switches  $S_1 \& S_2$ ) is for the series inverter and one leg (switches  $S_3 \& S_4$ ) is for the shunt inverter,

while the third leg (switches  $S_5 \& S_6$ ) is common between the two inverters. This configuration offers a compromise between the number of switching components, dc voltage and filters size.

Figure 2-3. (a) 1P2W FB UPQC topology (b) 1PP2W HB UPQC topology (c) 1P2W three-leg UPQC topology.

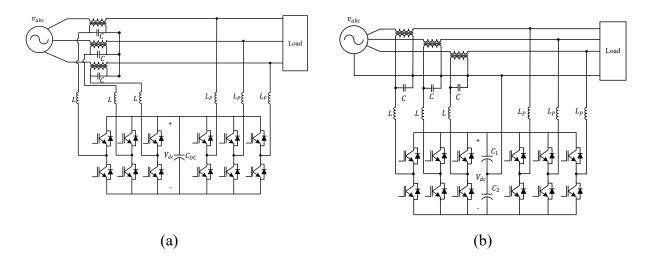

For a three-phase system, UPQC topology can be either three-phase three wire (3P3W) topology [30] as shown in Figure 2-4 (a), or three-phase four wire (3P4W) topology [31], [32] as shown in Figure 2-4 (b). 3P3W UPQC system is employed with industrial loads e.g. frequency converters, arc furnace, and arc welding machines, whereas 3P4W UPQC system is utilized with unbalanced three-phase loads or assortment of single-phase loads. Various three-phase topologies have been proposed [20], e.g. four-leg [31] and two-split capacitor [32] as in Figure 2-4 (b). A

single-phase to three-phase UPQC system has been proposed in [33]. This topology can be applied in rural or remote areas when only single-phase distribution system is accessible for economic reasons.

Figure 2-4. (a) 3P3W UPQC topology (b) 3P4W UPQC topology.

#### C. Circuit Configuration

A UPQC system can be classified according to the location of the shunt converter with respect to the series converter. Right UPQC (UPQC-R) configuration is when the shunt converter is placed to the right of the series converter as shown in Figure 2-1. Left UPQC (UPQC-L) configuration is when the shunt converter is placed to the left of the series converter as shown in Figure 2-5. The UPQC-R configuration is more popular, as the shunt converter will guarantee a sinusoidal input current going through the transformer under different loading conditions. When harmonic currents go through a transformer, its ohmic losses and eddy current losses will increase [34] leading to temperature rise in the transformer.

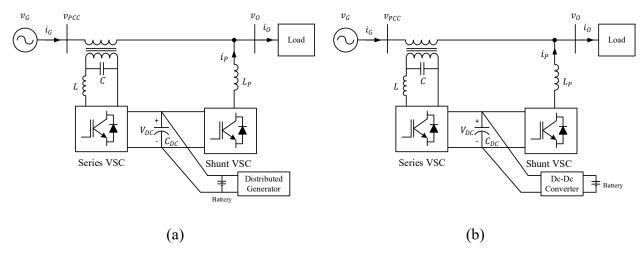

Due to the reduction of fossil fuels energy sources, replacing conventional power generators with clean energy resources is now encouraged. Consequently, DG units based on renewable

energy sources are becoming widely utilized. Many researches propose the integration of DG with UPQC system (UPQC-DG) [35]-[37]. Energy source integration will allow the UPQC system to compensate for a power outage as well. The DG unit is connected to the dc link as an energy source through a suitable converter as illustrated in Figure 2-6 (a). The advantage of a UPQC-DG system over a conventional UPQC system is the capability to inject active power at the event of a voltage interruption. Loads connected to the point of common coupling (PCC) will continue to receive power from the DG unit. Moreover, the UPQC-DG system will be able to inject active power to the grid. A photovoltaic (PV) system integrated with a UPQC system has been proposed in [36], [37]. The PV UPQC-DG system is able to transfer power in both interconnected mode and islanded mode.

A battery can replace the DG unit in a UPQC system as shown in Figure 2-6 (b). In [38], [39], a combined super capacitor energy storage system and battery storage system has been proposed to compose an additional energy source to the UPQC system. The combined system is connected to the dc link through s bidirectional dc/dc converter. In this case, the topology will maintain the dc voltage constant and supply sensitive loads under power supply interruptions forming an uninterruptible power supply (UPS).

Figure 2-5. Left UPQC configuration.

Figure 2-6. (a) DG unit integration with UPQC (b) Battery integration with UPQC.

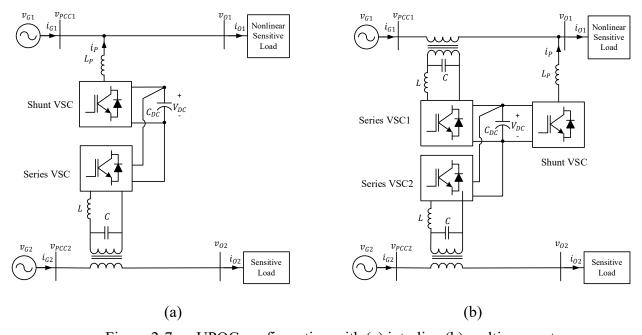

Figure 2-7. UPQC configuration with (a) interline (b) multi-converter.

The term interline has been introduced in the literature for both unified power flow conditioner (UPFC) and UPQC systems to control the power flow in two different transmission lines or distribution feeders as shown in Figure 2-7 (a) [40], [41]. The authors in [42], [43] has proposed a multi-converter UPQC topology as depicted in Figure 2-7 (b). The multi-converter topology extends the interline topology by connecting a third converter to improve the overall performance

of the UPQC system. For medium to high voltage levels, MCC UPQC system has been proposed [44], [45]. Adopting the MMC technology will reduce the voltage stress across the switching devices and enhance the quality of the output voltage waveform.

#### 2.2.2 Transformerless UPQC topology

A conventional UPQC topology requires a series isolated transformer. Nevertheless, transformers are bulky, and add more cost and losses to the system. A transformerless FB UPQC topology for single-phase applications is presented in [46]. The authors highlighted the importance of considering the circulating current problem in the converter design. A transformerless three-leg UPQC has been proposed in [47]. Despite the fact that the topology has less switching and conduction losses compared to a FB UPQC topology, the shared leg introduce mutual coupling between the two converters. The authors in [29] has proposed a specific modulation control technique to deal with the coupling issue introduced by the shared leg. The topology introduces constrains in practical applications due to the presence of leakage current.

## 2.2.3 Series APF Compensation Control Strategy

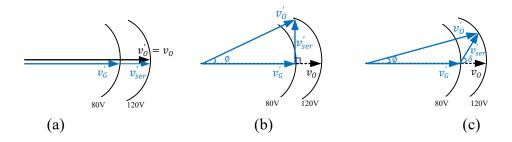

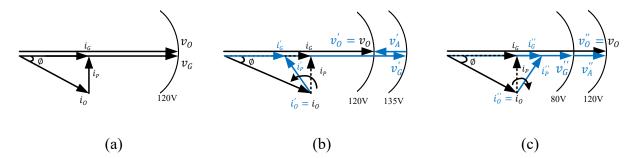

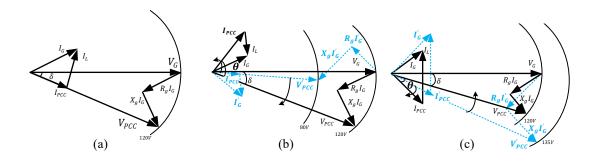

As mentioned earlier in this chapter, the series APF compensates for voltage related problems and acts as a dynamic voltage restorer (DVR). One of the major power quality voltage related problem is voltage sag/swell. Three main voltage sag/swell compensation techniques have been reported in the existing literature. Figure 2-8 shows the phasor diagrams of these techniques.

Figure 2-8. Phasor diagrams of DVR compensation methodologies (a) UPQC-P (b) UPQC-Q (c) UPQC-S

Active power control (UPQC-P) technique is the most common approach to compensate voltage disturbances [26]. This technique's concept is to inject/absorb a voltage  $v_{ser}$  in phase/out of phase with the main supply voltage through the series converter to mitigate a voltage sag/swell. The shunt converter under steady-state operation supplies the active power demand of the series converter. During a voltage sag (transient condition), the dc link supplies the series converter with the active power demand. The shunt inverter draws an equivalent active power to charge up the dc link voltage.

Reactive power control (UPQC-Q) technique has been employed in [30] to compensate for a voltage sag. The technique is based on injecting the series voltage  $v_{ser}$  that is in phase quadrature with the source current in UPQC-R or with the load current in UPQC-L. As the shunt APF maintain unity power factor, the energy injected by the DVR is minimum. A phase angle is created between the supply voltage and the delivered voltage in order to inject a quadrature voltage. Therefore, a larger injection voltage magnitude is needed than in a UPQC-P technique for an equal compensation of voltage sag.

Active reactive power control technique, donated by (UPQC-S), is a technique where the series converter delivers complex power. The authors in [48] has proposed minimum volt-ampere loading (UPQC-VA<sub>min</sub>) technique during a voltage sag. The principle of operation for this

technique is to inject the series voltage  $v_{ser}$  in an optimal angle with respect to the source current.

In order to enhance the operation of the series APF under all condition, the authors in [49] has presented maximum VA loading approach. Similar to UPQC-VA<sub>min</sub>, the injected voltage is controlled at an appropriate angle based on operational requirements. The series APF shares reactive power delivery with the shunt APF under steady-state and transient conditions. Consequently, the series converter loading will be maximized on the contrary to UPQC-VA<sub>min</sub> technique. This technique will reduce the loading on the shunt APF as well as its VA rating. However, it employs several control loops, which adds complexity to the system controller.

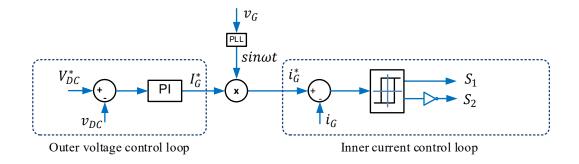

# 2.2.4 Shunt APF Compensation Control Strategy

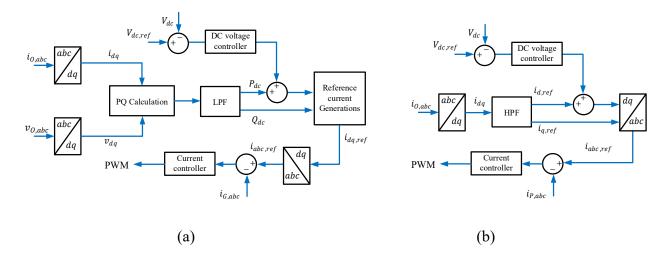

The shunt APF is mainly used for current harmonics mitigation caused by nonlinear lads connected to the PCC. The APF controller detects the harmonic contents in the load current and generates a reference current to oppose them. Once, the generated current is injected into the grid, the load harmonics current is suppressed, and the source current will contain only the fundamental component of the load current. The shunt APF is also used to deliver reactive power required by the load in order to achieve a voltage in phase source current with a unity power factor. There are various techniques that have been reported in the literature to generate the reference currents [50].

The instantaneous reactive power theory has been widely adopted in the literature. It is based on a mathematical calculation for the instantaneous active power (P) and reactive power (Q). The calculations are done in the time domain, where the load voltages and load currents are transformed to the d-q frame, from which the instantaneous load P and Q are calculated as follows,

$$P = v_d i_d + v_q i_q \tag{2.1}$$

$$Q = v_q i_d - v_d i_q \tag{2.2}$$

where,  $v_{dq}$  and  $i_{dq}$  are the d-q components of the load voltages and currents respectively.

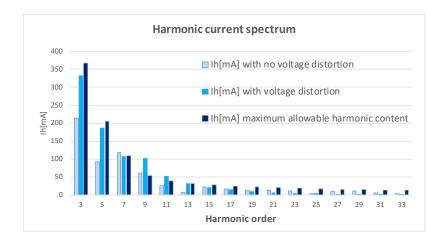

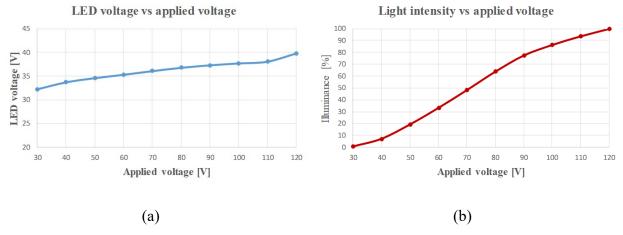

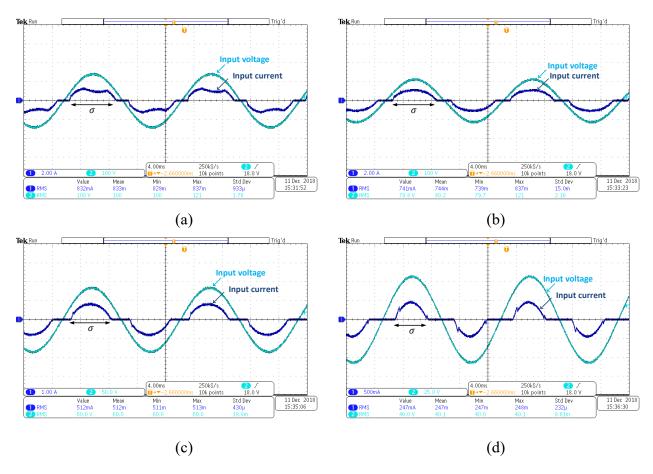

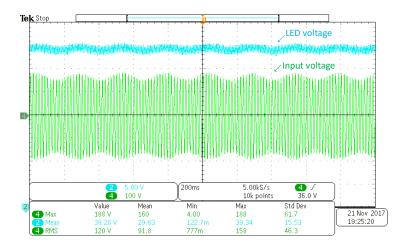

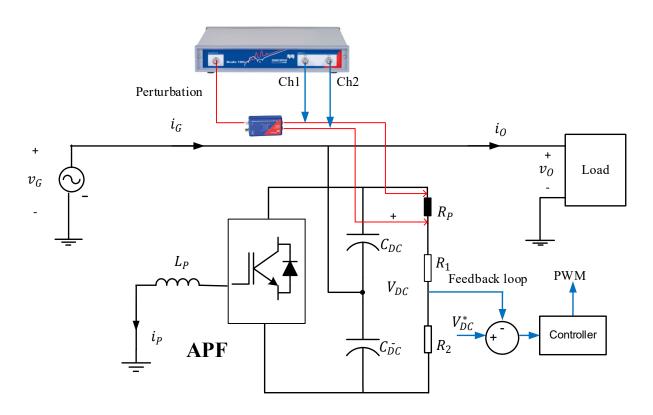

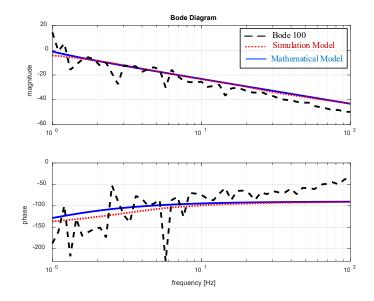

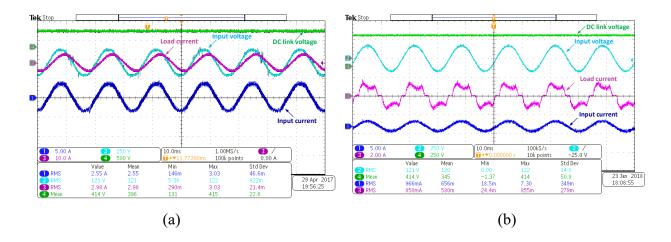

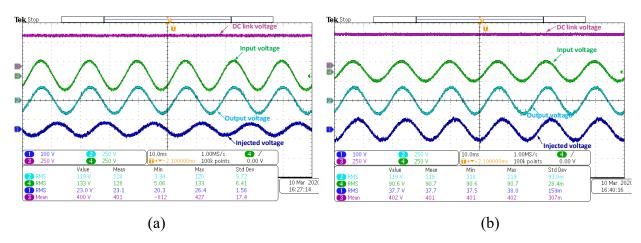

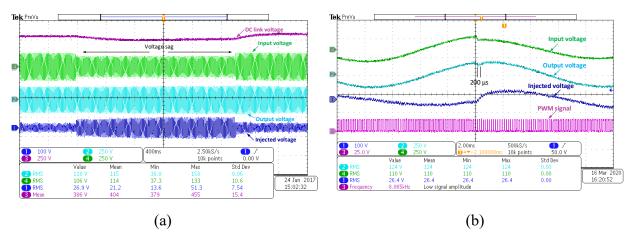

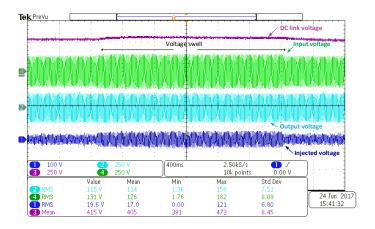

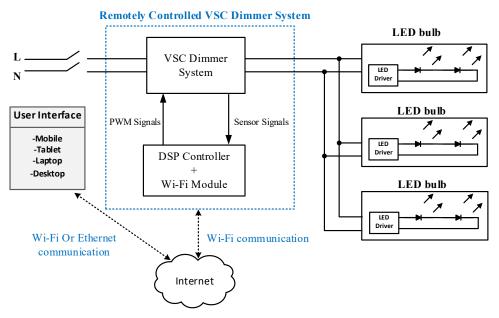

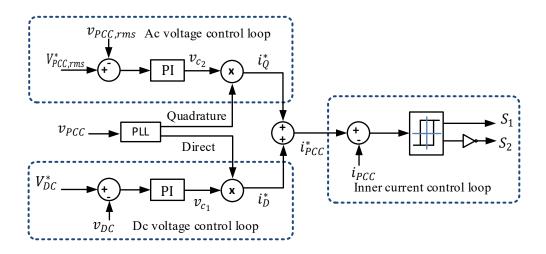

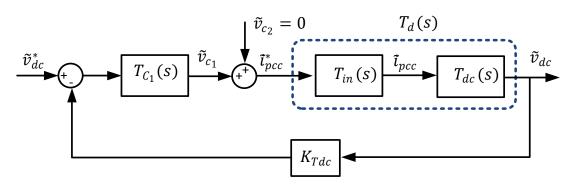

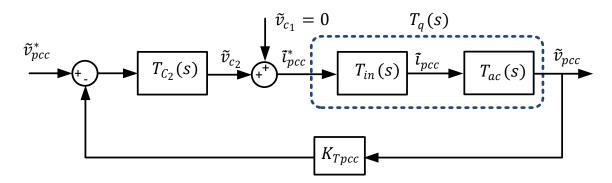

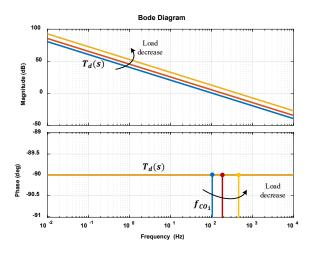

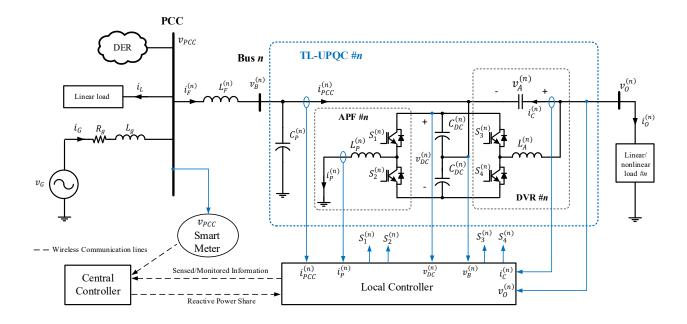

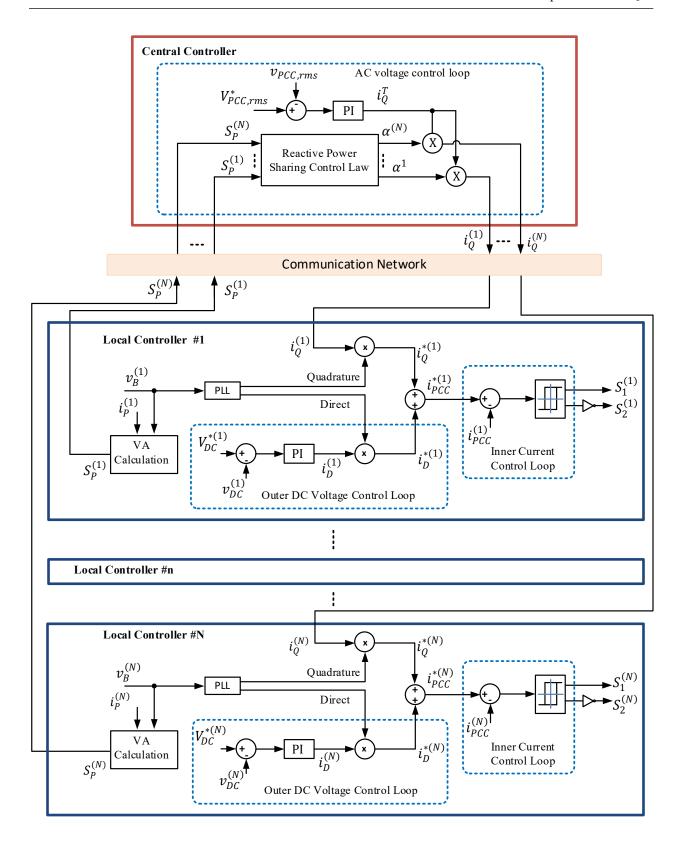

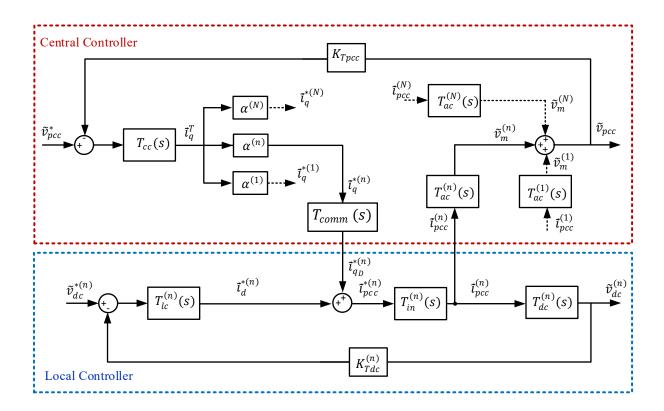

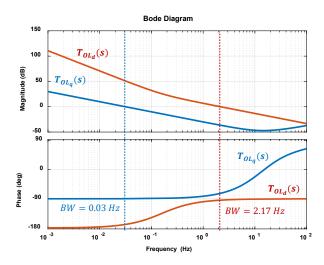

p and q components are fed into a LPF to decompose the power into dc component an ac component. The dc components represent the power required by the connected load. In order to have a unity power factor, the dc component of the reactive power is set to zero while the dc power is added to the losses required by the converter to maintain the dc link voltage. Accordingly, the source reference currents are generated as shown in Figure 2-9 (a).