# CARRIER COMMUNICATION ON BUS-BARS AND CABLES

by

Peter T. Ashton

A Thesis

presented to the University of Manitoba

in partial fulfillment of the

requirements for the degree of

Master of Science

Winnipeg, Manitoba, 1989

© Peter T. Ashton, 1989

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

18BN 0-315-51632-1

# CARRIER COMMUNICATION ON BUS-BARS AND CABLES

ΒY

### PETER T. ASHTON

A thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements of the degree of

### MASTER OF SCIENCE

### © 1989

Permission has been granted to the LIBRARY OF THE UNIVER-SITY OF MANITOBA to lend or sell copies of this thesis, to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

I hereby declare that I am the sole author of this thesis. I authorize the University of Manitoba to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Peter T. Ashton

I further authorize the University of Manitoba to reproduce this thesis by photocopying or by other means, in whole or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Peter T. Ashton

The University of Manitoba requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

#### ABSTRACT

The purpose of this thesis is to develop a device which selective relays employing zone instantaneous protection (ZSIP) to communicate over 600V busses and cables. What makes this application different from other carrier current systems is that the required signal must be sent at the exact moment that the electrical noise on the bus is at its worst. To facilitate development of this device, measurements are taken to determine the nature of electrical noise present on 600V busses under different conditions. Using this information, a microprocessor based carrier current system is developed and two prototype units are constructed. Testing of these prototypes reveals that the system is very fast and good noise rejection has characteristics. Due to the success of these prototypes, I foresee little difficulty extending the ZSIP system to incorporate the carrier current concept.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to Professor G. Swift for his valuable guidance throughout the development of this thesis. I would also like to thank Federal Pioneer Ltd. for suggesting this topic and providing the financial support which made it possible. Finally, the many helpful comments and suggestions provided by the department's electrical technologists are greatly appreciated, as they are what transformed this thesis from only an idea into a working system.

# TABLE OF CONTENTS

| ABST | RACT | •••••                                                                                                                                                                                                                           | iv                                           |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| ACKN | OWLE | DGEMENTS                                                                                                                                                                                                                        | ٧                                            |

| Chap | ter  | F                                                                                                                                                                                                                               | age                                          |

| I.   |      | INTRODUCTION                                                                                                                                                                                                                    | 1                                            |

|      | 1.2  | Purpose Background 1. Fundamentals of Relaying 2. The ZSIP System Problem Scope                                                                                                                                                 | 1<br>1<br>1<br>4<br>4<br>5                   |

| II.  | 2.2  | ELECTRICAL NOISE MEASUREMENTS  Required Measurements Measurement Equipment Results of Measurements 1. Normal Conditions 2. Fault Conditions                                                                                     | 6<br>7<br>15<br>15<br>28                     |

| III. | 3.2  | HARDWARE/SOFTWARE DESIGN  Design Philosophies  Possible Blocking Signal Schemes  1. FSK System  2. Multi-frequency System  3. Blocking Signal Conclusion  Hardware  1. Carrier Current Receiver  2. Carrier Current Transmitter | 40<br>40<br>41<br>41<br>45<br>48<br>50<br>54 |

|      | 3 4  | Software Design                                                                                                                                                                                                                 | 57                                           |

| IV. | TESTING                                                               | 64  |

|-----|-----------------------------------------------------------------------|-----|

|     | 4.1 Quantitative Data 4.2 Use of Pseudo-bus 4.3 Tests using AC Wiring | 66  |

|     |                                                                       |     |

| ٧.  | CONCLUSIONS AND RECOMMENDATIONS                                       | 78  |

|     |                                                                       |     |

| REF | ERENCES                                                               | 80  |

|     |                                                                       |     |

| App | pendix                                                                |     |

| Α.  | Measurement Software Source Code                                      | 81  |

| В.  | DFT Software Listing                                                  | 92  |

| C.  | Carrier Current Software Source Code                                  | 97  |

| D.  | PIA Port Map                                                          | 104 |

| E.  | Microprocessor Board Information                                      | 106 |

| F.  | Data Sheets for Selected Devices                                      | 110 |

# LIST OF FIGURES

| Figure |                                                     |    |

|--------|-----------------------------------------------------|----|

| 1.1    | Time Coordinated Protection                         | 2  |

| 1.2    | Schematic of Coupling Circuit                       | 9  |

| 1.3    | Amplitude Bode Plot of Coupling Circuit             | 9  |

| 2.1    | Time Domain Recording on 208V Bus @ 15:20           | 17 |

| 2.2    | Fourier Spectrum of Waveform in Figure 2.1          | 18 |

| 2.3    | Time Domain Recording on 600V Bus @ 03:00           | 20 |

| 2.4    | Fourier Spectrum of Waveform in Figure 2.3          | 21 |

| 2.5    | Time Domain Recording on 600V Bus @ 11:00           | 24 |

| 2.6    | Fourier Spectrum of Waveform in Figure 2.5          | 25 |

| 2.7    | Time Domain Recording on "Quiet" 600V Bus @ 15:10 . | 26 |

| 2.8    | Fourier Spectrum of Waveform in Figure 2.7          | 27 |

| 2.9    | Staged Fault Equipment                              | 29 |

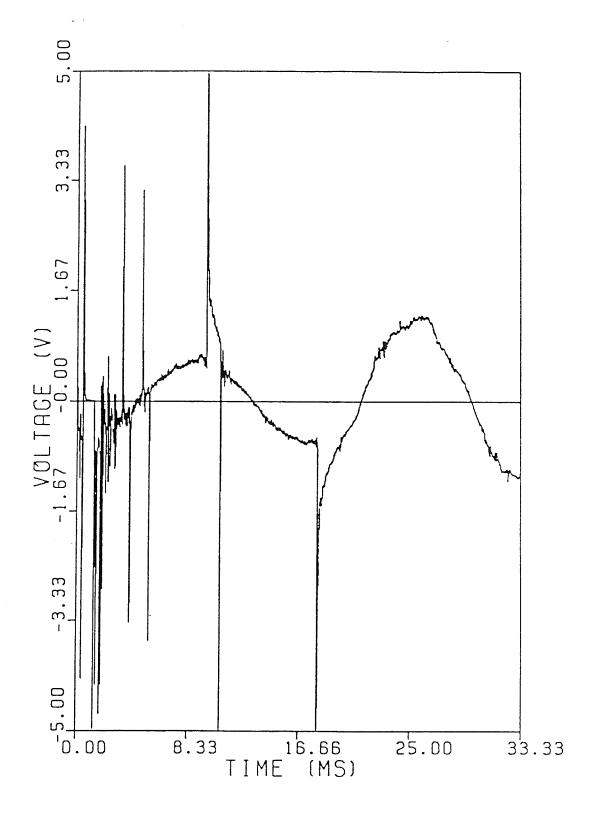

| 2.10   | Fault Recording - Sampling on Phase 'A'             | 30 |

| 2.11   | Fourier Spectrum of Waveform in Figure 2.10         | 31 |

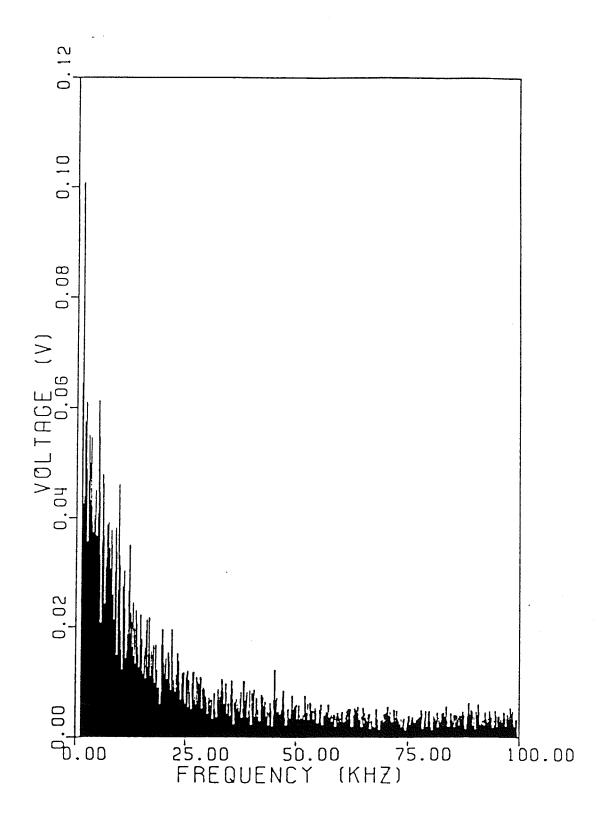

| 2.12   | Fault Recording - Sampling on Phase 'C'             | 32 |

| 2.13   | Fourier Spectrum of Waveform in Figure 2.11         | 33 |

| 2.14   | Fault Recording - Phase 'A' to Ground               | 35 |

| 2. 15  | Fourier Spectrum of Waveform in Figure 2.14         | 36 |

| 2. 16  | Fault Recording - Worst Case Noise                  | 37 |

| 2.17   | Fourier Spectrum of Waveform in Figure 2.16         | 38 |

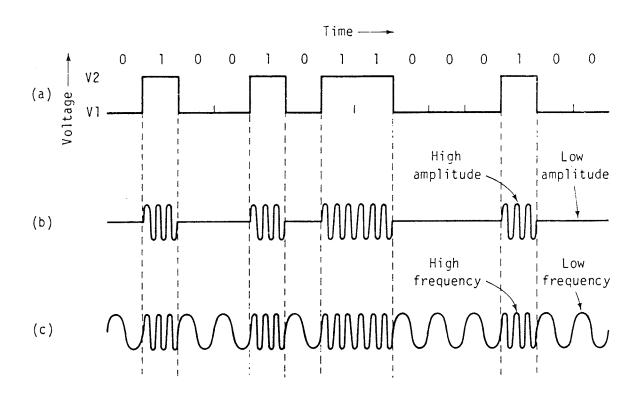

| 3.1 | Modulation Schemes                                                          | 42 |

|-----|-----------------------------------------------------------------------------|----|

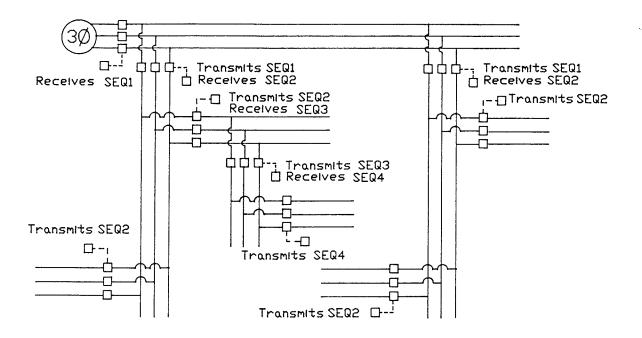

| 3.2 | Application of FSK to the ZSIP System                                       | 43 |

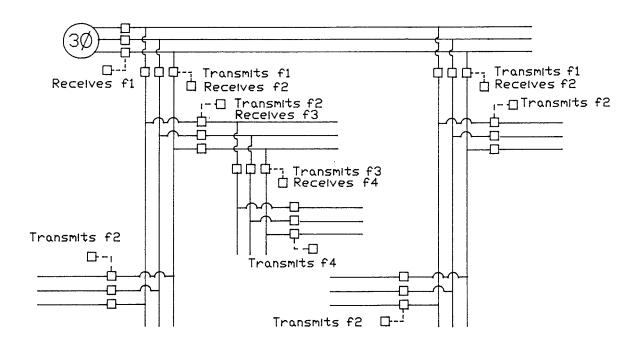

| 3.3 | Application of Tones to the ZSIP System                                     | 46 |

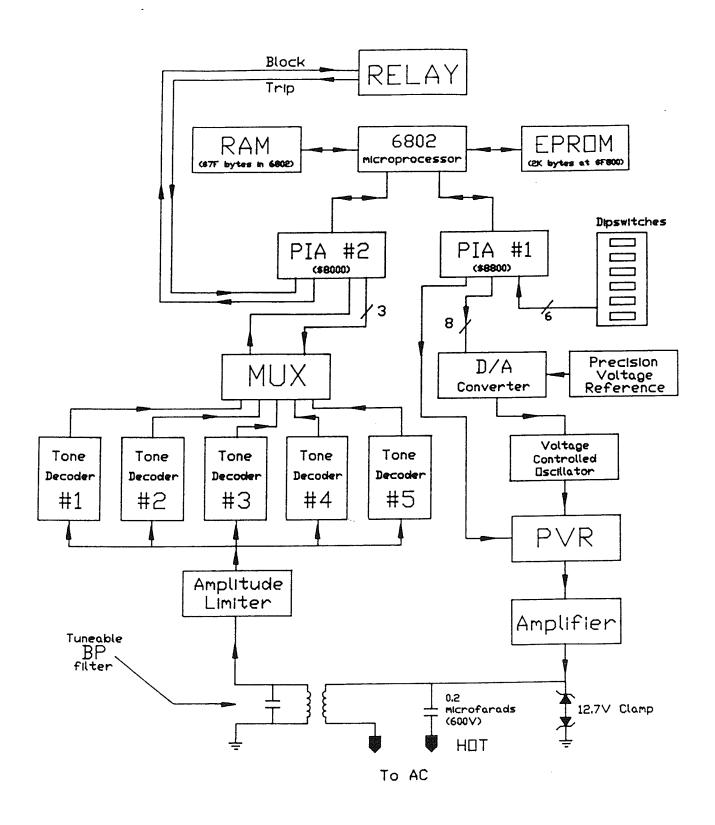

| 3.4 | Block Diagram of Hardware                                                   | 51 |

| 3.5 | Simplified Hardware Schematic                                               | 52 |

| 3.6 | Transmit/Receive Timing Diagram                                             | 58 |

| 3.7 | Receiver Sampling Scheme                                                    | 59 |

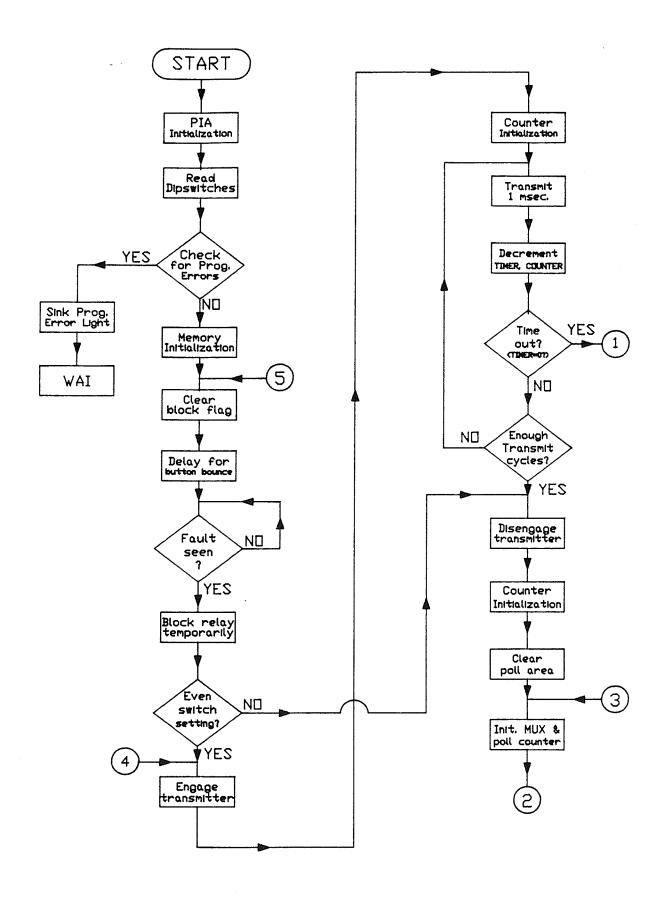

| 3.8 | Flowchart of Carrier Current Software                                       | 61 |

| 4.1 | Photograph of Actual Transmit/Receive Timing                                | 65 |

| 4.2 | Photograph of Tone Decoder Lock-in Response                                 | 65 |

| 4.3 | Tone Decoder Response with Small Amount of Noise .                          | 69 |

| 4.4 | Tone Decoder Response with Large Amount of Noise .                          | 69 |

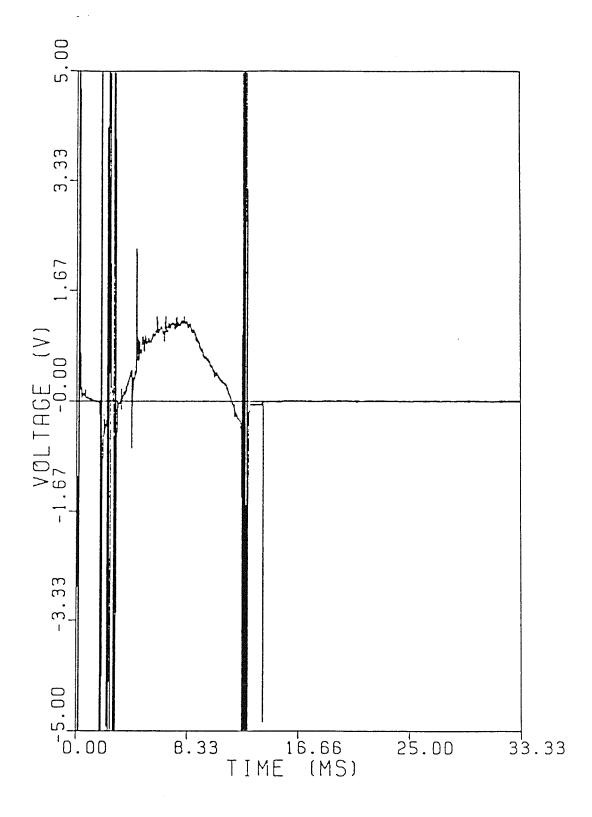

| 4.5 | Recording of Maximum Allowable Noise when using "2 of Last 4" Voting Scheme | 71 |

| 4.6 | Fourier Spectrum of Waveform in Figure 4.5                                  | 72 |

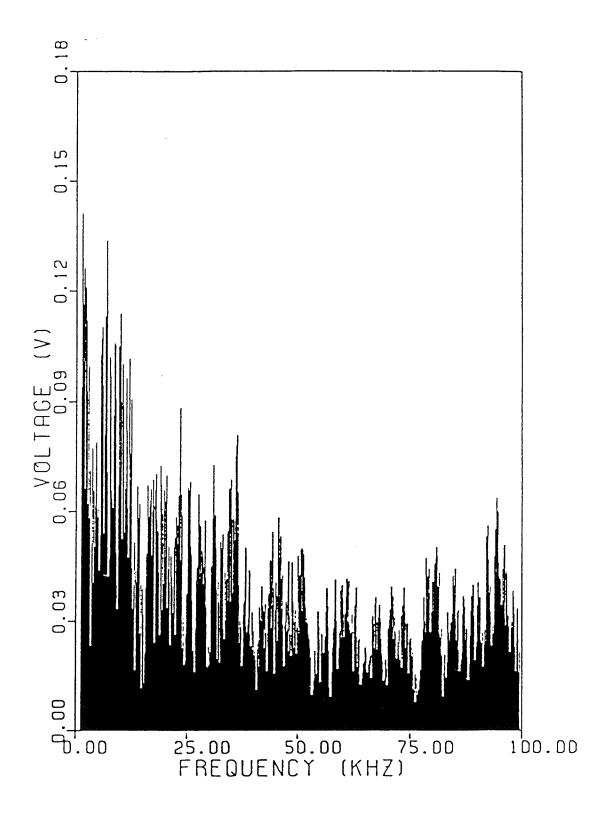

| 4.7 | Recording of Maximum Allowable Noise when using "3 of Last 4" Voting Scheme | 73 |

| 4.8 | Fourier Spectrum of Waveform in Figure 4.7                                  | 74 |

# Chapter I

#### INTRODUCTION

#### 1.1 Purpose

The purpose of this research is to develop a device which will interface with Federal Pioneer's ZSIP<sup>1</sup> system of ground fault relays and allow them to communicate over 600V busses or cables. This device would be a useful enhancement to the ZSIP system and would make the product more attractive in a competitive marketplace.

### 1.2 Background

To fully understand the need for this research and how the carrier current unit would function, it is necessary to first know some of the fundamentals of protective relaying and some details of the ZSIP system itself.

## 1.2.1 Fundamentals of Relaying

Inside a typical factory, institution, or sub-station, power is distributed via a system of 600V busses and cables. The distribution network has a hierarchical structure with a primary distribution bus feeding several secondary busses,

<sup>&</sup>lt;sup>1</sup>"Zone Selective Instantaneous Protection", a Federal Pioneer Limited registered trademark.

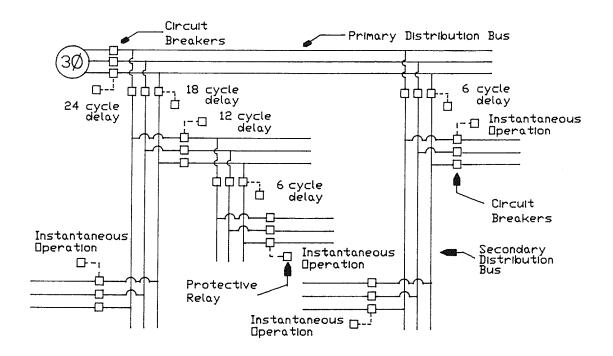

which in turn feed other busses, and so on. Figure 1.1 shows a simplified version of a distribution network. Near the junction of two busses there are circuit breakers (one for each phase) which are capable of interrupting the current being fed into the smaller bus. Connected to these breakers is a protective relay which senses the current on the bus through current transformers and causes the breakers to open if this current exceeds a preset threshold.

Figure 1.1: Time Coordinated Protection.

The relays and breakers described above are used to provide protection against faults, i.e. short circuits, which sometimes appear. These faults can burn and damage the busses because of the huge currents they draw. In addition, they are also dangerous because they can spread to other busses as the arc follows the path of the drifting ions. To remove a fault, the current feeding it must be interrupted by opening the breakers and then allowing the ions to dissipate.

Since it is desirable to cut the power to as few busses as possible, methods have been devised to make sure the breakers immediately upstream of the fault are the ones that are opened. The most common way of doing this is by time coordinating the upstream and downstream relays. Normally, the furthest downstream relay is in an instantaneous mode where it will open its breakers as soon as a fault is detected. Although the next upstream relay also "sees" the fault, it is in a timed mode in which it will wait for a preselected period of time (say, 6 cycles) after a fault is sensed before it will open its breakers. If the fault is located downstream of the furthest downstream relay, then the upstream relay will not operate since the fault will already be removed by the time the timed mode has elapsed. This system of protection can be extended to any number of distribution levels simply by adding successively longer delays to the upstream relays.

The problem with TCP (Time Coordinated Protection) is that for a fault occurring on the primary distribution bus

(near the ac source), there is a very long delay (say, 24 cycles) before the timed mode finally ends and the breakers are opened. During this time, considerable damage can be done to the bus-bars, and the arc may spread to other busses as well.

# 1.2.2 The ZSIP System

ZSIP avoids the problems associated with TCP by providing upstream and downstream relays with a method of communicating. Twisted wire pairs are run between each upstream/downstream relay pair, thereby providing the downstream relay with the ability to tell the upstream relay whether or not it sees a fault. Time delays are not necessary in this scheme so each relay is by default in instantaneous mode. When a relay sees a fault, it first sends a "block" signal to the relay just upstream from it. Then, if it has not received a block signal itself, operates its breakers.

Using this system, a fault on the primary distribution bus is removed almost instantly since there are no other relays to see the fault and block the relay. This results in far less bus-bar damage while maintaining the ability to cut off only the minimum number of busses.

## 1.3 Problem

Although the ZSIP system provides better protection than TCP, it is also more expensive. Since the upstream/downstream relay pairs can be far apart (say 300m), the cost of running wire and conduit is not inconsequential. The question is then "Why not use the bus-bars themselves as the communication media?". This type of communication is not new; carrier current devices have been around for years. However, what makes this application novel is that one is trying to send a signal while an arcing fault exists on the bus. In other words, the signal is being sent at the exact moment that the noise on the bus is at its worst.

#### 1.4 Scope

To begin to solve the problem described above, it is necessary to have a feel for the kind of electrical noise found on a 600V distribution system. Only once the nature of the noise has been characterized can the design of the unit's hardware and software begin. In this thesis, Chapter II describes the types of measurements needed, how they were made, and what they revealed. Chapter III is devoted to the design of the hardware and software and describes why this design was chosen. A chapter explaining the testing conducted on the carrier current units comes next, and is followed by the final chapter containing conclusions and recommendations.

## Chapter II

#### ELECTRICAL NOISE MEASUREMENTS

### 2.1 Required Measurements

Knowing the nature of the electrical noise present on a 600V distribution system is crucial to the design of the carrier current ZSIP system. There are really two distinct measurements which need to be made:

- 1) measurements under normal conditions (i.e. no fault present) to make sure steady state noise is not misinterpreted as a blocking signal.

- 2) measurements <u>just</u> after a fault occurs to make sure that arc induced noise is not interfering with the transmission of the blocking signal.

The first of the two measurements above is extremely simple to make. By clipping a spectrum analyzer onto the bus (through a HP filter) and scanning over a frequency range from 10 - 100 kHz, a good picture of the noise environment develops. On the other hand, measurement 2) is much more difficult to make as it requires that a few ac cycles of data

be "captured" immediately after the fault occurs. A calculating storage oscilloscope can do this, but its calculating function is usually limited to an FFT (Fast Fourier Transform) of only 512 points of data. To "see" frequencies up to 100kHz, the Nyquist criterion requires that the data be sampled at greater than 200kHz. If 5 ac cycles of data are wanted, then more than 16,667 samples need to be taken. A calculating oscilloscope is certainly not sufficient for this task. The next section describes the actual method used to accumulate the data for both types of measurements.

### 2.2 Measurement Equipment

The measurement system used in this thesis consists of a 12MHz IBM-PC AT computer, a custom made data acquisition board, a passive coupling circuit, and some machine code programs.

The data acquisition board used is the QUAD A/D1, made by MicroMarine Technology. It consists of four Harris 12µs, 12 bit analog to digital (A/D) converters, four sample and hold devices, a 16 channel MUX circuit, and the required hardware to interface it to the PC. The 12µs conversion time gives each one of the converters the ability to sample at 83.3kHz. However, by using 3 of these A/D converters at once, a sampling rate of 250kHz is theoretically possible. The 4th A/D channel is reserved for voltage sensing to initiate the sampling in the staged fault measurements.

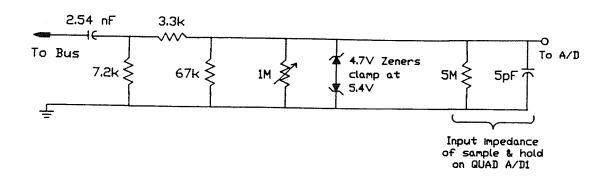

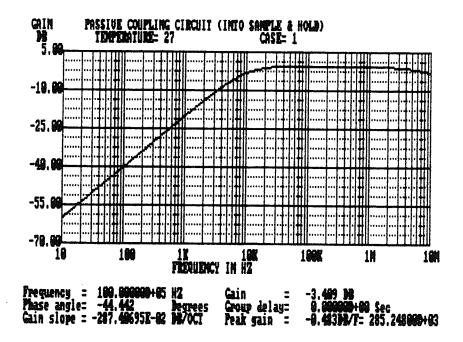

The Quad A/D1 is connected to the 600V bus through a passive coupling circuit to protect its sensitive electronics from the high voltage. This coupling circuit is essentially just an RC network which forms a HP filter. High power zener diodes are used to clamp the output voltage at 5.2V so that high frequency noise spikes do not exceed the maximum input voltage of the sample and hold circuits. Figure 1.2 shows a schematic of the coupling circuit while an amplitude Bode plot is given in Fig. 1.3. It can be readily seen that this circuit provides a great deal of attenuation at 60Hz ( >40dB ) while providing almost no attenuation at frequencies upwards of 10kHz.

Due to the extreme speed required by this sampling task, the software to run the A/D equipment must be written in machine code. There are, in total, three versions of this software, each of which performs a slightly different task.

SAMPLE.EXE captures 6630 samples (can be varied) at 198.9kHz immediately after being run, and saves this data to the default disk drive using a filename supplied by the user.

TIME\_SAM.EXE is used for automated data acquisition. When run, this program takes one set of data immediately (6630 samples at 198.9kHz) and saves it to disk using the user supplied name with a numerical suffix added.

Figure 1.2: Schematic of Coupling Circuit.

Figure 1.3: Amplitude Bode Plot of Coupling Circuit.

Once done, the program enters a wait mode where it continually polls the hardware timer until it determines that one hour has elapsed. At this time, another set of data is taken, the numerical suffix is updated, appended to the filename, and the file is saved. This procedure is repeated endlessly until stopped by the user.

CHK4FLT.EXE is used in the staged fault measurements. Here, the 4th A/D channel is used to sense the voltage on one phase through a voltage divider. Once any voltage exceeding a preset threshold is detected it means that both breakers have been closed and sampling can be initiated. This program takes 6630 samples at 198.9kHz and saves the data to disk using the name supplied by the user.

Since these three programs are so similar, only the listing for TIME\_SAM.EXE is shown in Appendix A.

The final stage in the measurement process is the analysis of the data using Fourier transforms. Since this is a very time-consuming job, especially when the number of samples is large, the University's Amdahl mainframe is best suited to this task. There are many algorithms available which perform discrete Fourier transforms, each of which has advantages and disadvantages:

# (1) Classical Discrete Fourier Transform (DFT) Method

This method is directly derived from the continuous Fourier transform equations [1].

The DFT ,

$$X(k) = A(k) + jB(k)$$

where, for N samples

$$A(k) = \frac{\left[\sum_{n=0}^{N-1} X(n)\cos(Qnk) + Y(n)\sin(Qnk)\right]}{N}$$

$$B(k) = \frac{\left[\sum_{n=0}^{N-1} Y(n)\cos(Qnk) - X(n)\sin(Qnk)\right]}{N}$$

where:

$$Q = \frac{2 \pi}{N}$$

$$X(n) = \text{real part of discrete signal}$$

$$Y(n) = \text{imaginary part of discrete signal}$$

$$k \text{ takes on values from 0 to N-1}$$

Note: Physical signals have no imaginary part so the above simplify to:

$$A(k) = \frac{\left[\sum_{n=0}^{N-1} X(n)\cos(Qnk)\right]}{N}$$

$$B(k) = \frac{\left[\sum_{n=0}^{N-1} -X(n)\sin(Qnk)\right]}{N}$$

Fourier coefficients are given by:

$$C(k) = \left| A(k) + jB(k) \right|$$

This yields a two sided spectrum with terms for both positive and negative frequency. However, for this application, negative frequency is essentially the same thing as positive frequency. So, to simplify things, only the positive frequencies are shown. The Fourier coefficients have amplitudes that are the sums of their positive and negative components [2].

The fundamental drawback to the classical DFT is that it is so computationally intensive. For N samples, this algorithm requires  $\frac{1}{2}N^2$  major operations (for example, a multiplication).

### (2) Cooley Tukey FFT Algorithm

This is the method applied by many commercial FFT programs. It works by uncoupling row and column calculations, thus converting a single difficult problem into multiple easy ones [2]. This results in considerably less computation time than the classical DFT algorithm. For N samples there are only  $\frac{1}{2}Nlog_2N = \frac{1}{2}N\frac{log_{10}N}{log_{10}2}$  (assuming a radix of 2) major operations required.

The problem with the FFT is that the allowable number of samples is intimately related to the radix of the FFT algorithm.

so, assuming a radix of 2,  $N = 2^{M}$

Since it is desirable to sample as fast as possible with the QUAD A/D1 AND take an integer number of ac cycles, this restriction on the number of samples is a problem.

#### (3) Goertzel's 2nd Order DFT Algorithm

Goertzel's algorithm [1] is a happy medium between the FFT and the classical DFT. This method requires only half as many real multiplications as the classical method  $(\frac{1}{4}N^2)$ , and uses 2N trigonometric operations instead of  $2N^2$ . However, this algorithm still retains the advantage of the classical method

because it allows any even number of samples to be used.

A comparison of the previous three methods for a 4 096 point transform yields the following:

Table 2.1

| Algorithm      | Time (s) |

|----------------|----------|

| Classical DFT  | 67.29    |

| Cooley - Tukey | 0.76     |

| Goertzel's     | 12.42    |

The preceding table justifies the claim that Goertzel's algorithm is considerably faster than the classical method. Although this computational advantage is somewhat significant for 4 096 points of data, it takes on an even greater importance when the number of points exceeds 10 000. For this reason, and the fact that varying numbers of samples are wanted, Goertzel's method was chosen for analysis of all the sampled data. A listing of the FORTRAN program used is provided in the Appendix B.

The numerical data taken during normal and fault conditions is uploaded to the Amdahl via a 1200 baud telephone modem using Kermit<sup>2</sup>. This data is then processed and plotted on the Amdahl's high speed laser printers.

<sup>&</sup>lt;sup>2</sup>Kermit is a telecommunications package which facilitates file transfers between 7 bit and 8 bit computer systems.

## 2.3 Results of Measurements

The next two sections describe the methodology of the electrical noise measurements and present some selected results. These results are explained and their impact on the carrier current ZSIP system is discussed.

## 2.3.1 Normal Conditions

Electrical noise measurements under normal conditions were conducted at Federal Pioneer's Rockman Ave. transformer plant in Winnipeg between May 11th and 18th, 1988. Measurements were made on three different electrical supplies at many different times throughout the day. These supplies were a 208V, 3-phase supply driving a variety of loads, a 600V supply near some seam welding machines, and finally, a 600V supply on a quiet side of the plant.

To make the above measurements, the sampling equipment was connected to one phase of the supply through the passive coupling circuit which was previously described. Since the sampling software automated the measurement process, the equipment could be left unattended for 24 hours at a time. This resulted in measurements being taken for a wide variety of load conditions through the day and night. This procedure was followed for the first two supplies but, due to time constraints, only three measurements could be made on the third supply.

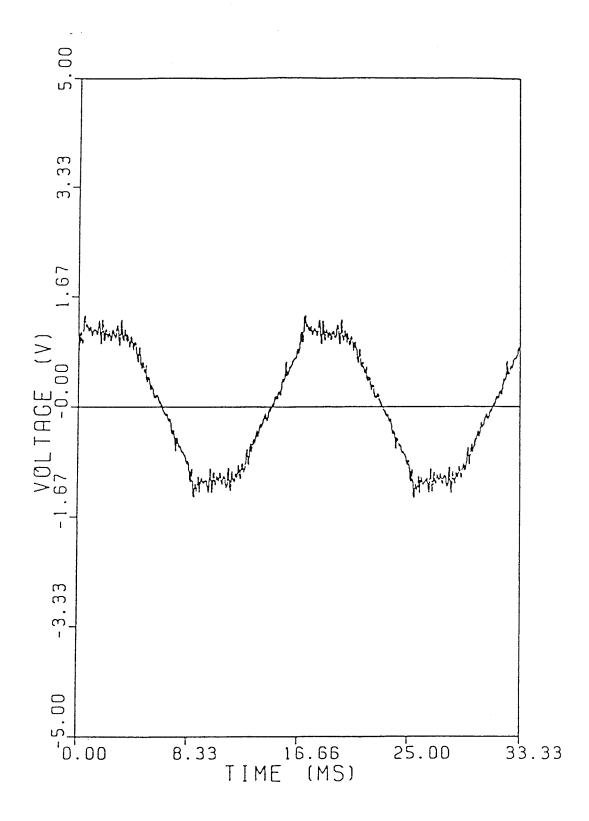

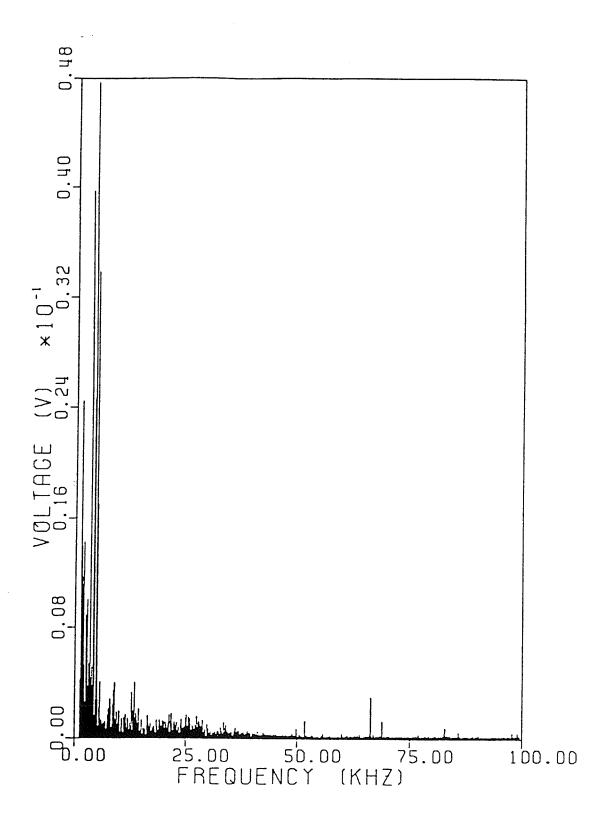

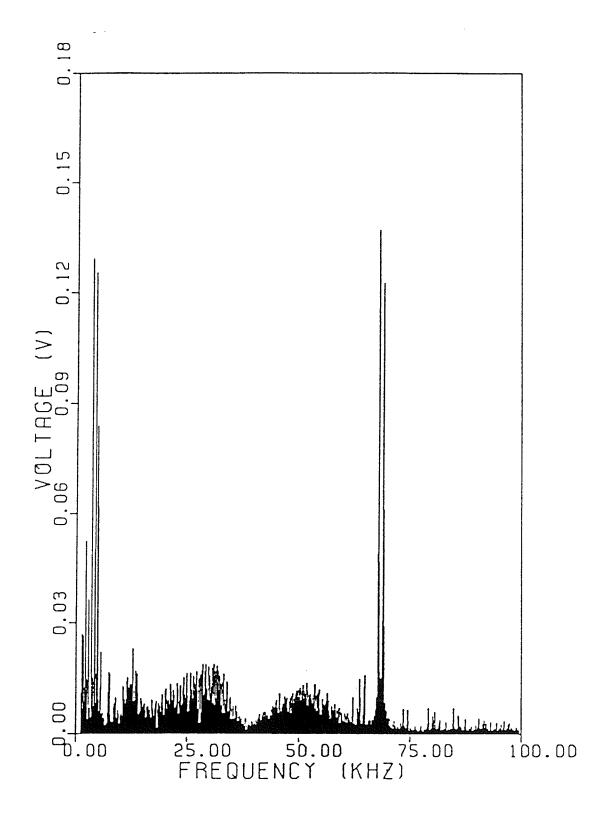

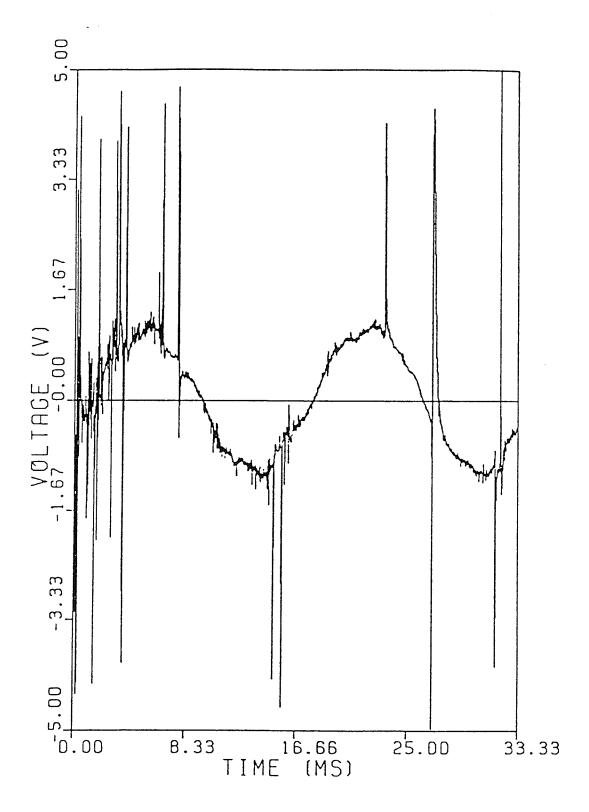

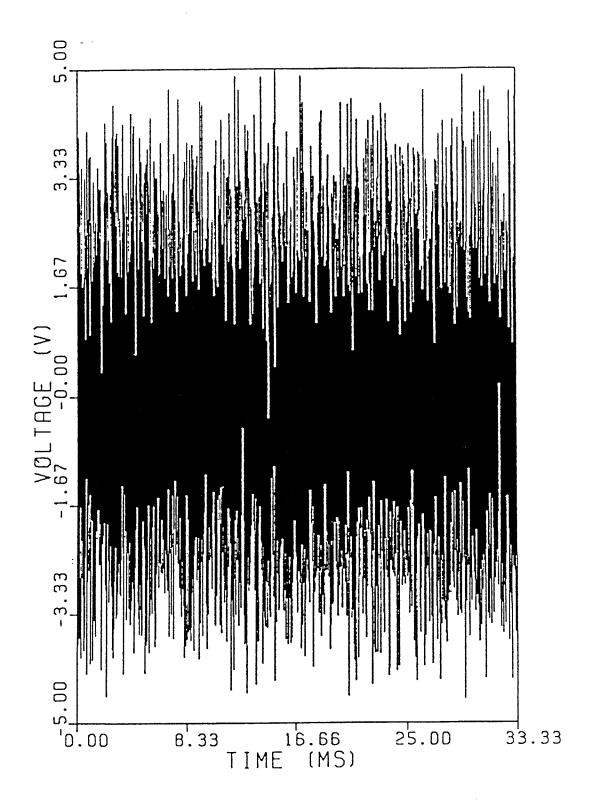

Figure 2.1 shows a typical voltage waveform found on the 208V bus. This particular signal was recorded at 3:20 p.m. and certainly appears to suffer from a great deal of noise and distortion. However, this figure is, in some ways, deceptive. Since this waveform is viewed by the sampling hardware through a high-pass filter, the high frequency noise component appears very large in comparison with the 60Hz fundamental. If viewed on an oscilloscope which was directly coupled to the bus, there would not be 45 dB of attenuation at 60Hz as there is here, and therefore, the waveform would look more sinusoidal. Figure 2.2 shows the discrete spectrum obtained by performing a Fourier transform on the signal in Fig. 2.1. As can be clearly seen, there is some noise present at low frequencies (<4 kHz) but practically none up in the PLC (Power Line Carrier) frequency range (60kHz to 100kHz). Other measurements at different times reveal very similar results.

One observation worth noting with all of the spectra presented is the small frequency gap near zero Hz. This is created intentionally since these coefficients are large and tend to make everything else look comparatively tiny. Since these low frequencies are of no interest here anyway, they are set to zero before the plots are generated.

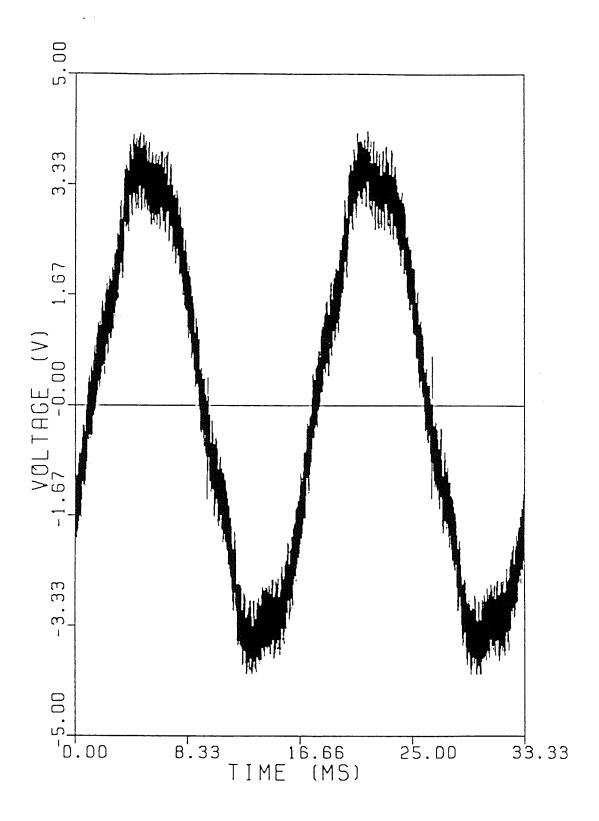

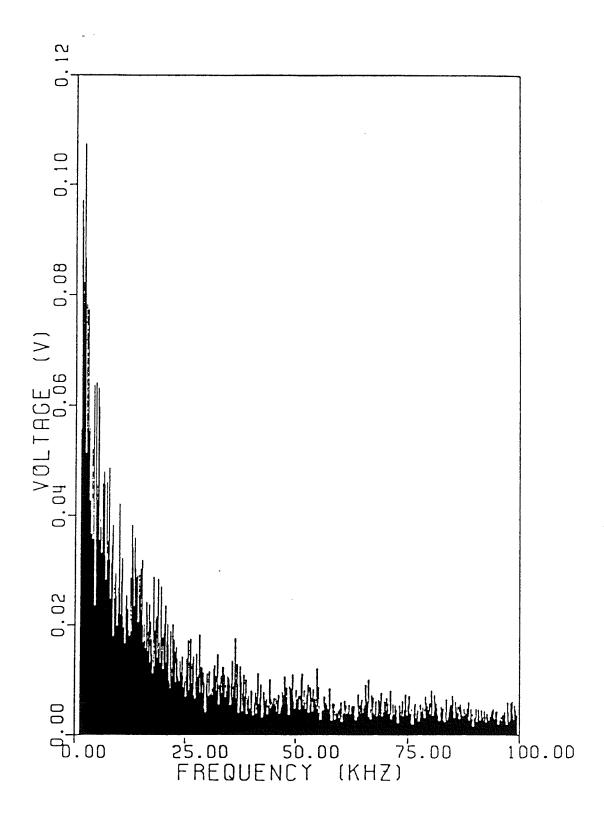

Figure 2.3 is a plot of the waveform found on the "noisy" 600V bus at 3:00 a.m. Observing this signal, it is quite obvious that this bus is subjected to more noise than is the 208V bus. When Fourier transforms are performed, there is

Figure 2.1: Time Domain Recording on 208V Bus @ 15:20.

Figure 2.2: Fourier Spectrum of Waveform in Figure 2.1.

a very interesting result (see Fig. 2.4). Here, there is moderate noise below about 5kHz. However, upwards of 5kHz, the noise is almost insignificant with the exception of two huge noise spikes which appear to be centered at about 70kHz. On a later visit to FPL, we were able to determine with the aid of an oscilloscope that these signals were actually present at 130kHz rather than 70kHz. The 99.45kHz Nyquist frequency allowed these signals to be aliased since there was no anti-aliasing filter included in the coupling circuit. This oversight was later corrected, before the fault measurements were taken.

The source of these two "mystery signals" has never been identified. Since the frequency spacing between them is almost exactly 1kHz, it seems unlikely that they would result from some natural phenomenon. Below are several possible causes and a judgment on their likelihood:

- Some resonant condition on FPL's busses not likely since the signals are present on busses on opposite sides of the plant.

- 2) Some travelling wave phenomenon no, since the wavelength is too long. The frequency of travelling waves is determined only by the length of the bus.

Figure 2.3: Time Domain Recording on 600V Bus @ 03:00.

Figure 2.4: Fourier Spectrum of Waveform in Figure 2.3.

- 3) An air induced signal might be possible.

Apparently, some navigational beacons use extremely low frequencies like this, although it is unlikely that the transmitted power would be high enough to induce a voltage of 0.26V in FPL's busses.

- 4) Some carrier signal injected by Manitoba Hydro Maybe, Hydro telecontrol confirms that a PLC channel from Dorsey to Brandon is operated in the 130kHz to 140kHz range. However, they claim that line traps prevent this signal from getting back into the distribution. In addition, this signal would have to pass through a large step-down transformer to get into FPL's plant. This would almost certainly attenuate the signal to a level far below 0.26V.

- 5) Some carrier current signal from one of FPL's industrial neighbors impossible since there are only residential customers on FPL's feed.

- 6) A signal originating from inside FPL itself most likely cause. Although FPL does have an energy management system, it uses lower frequencies (~ 3kHz I think). The 1kHz frequency spacing suggests that the signals are due to some form of FSK communication. However, the exact source remains a mystery.

Since these "mystery signals" are far above the frequency range under investigation (60 - 100kHz), they are not of any real concern.

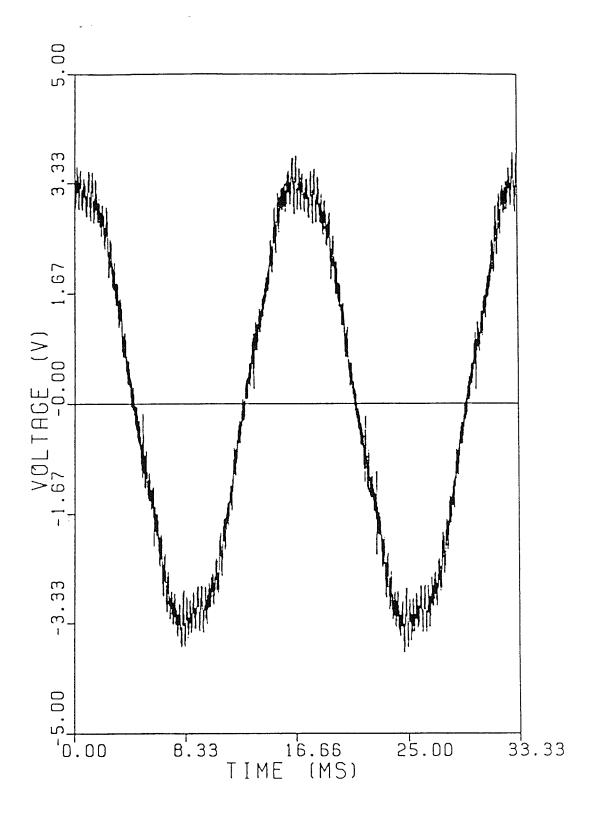

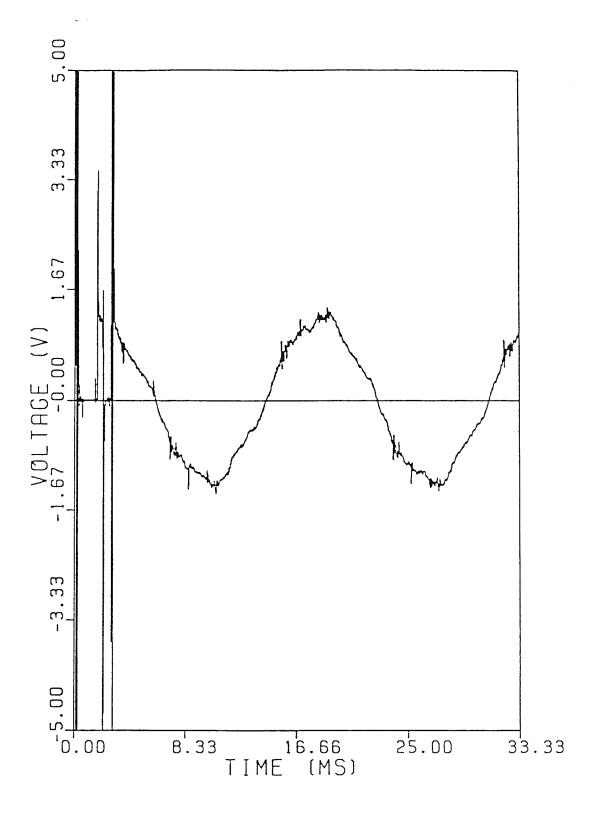

Proceeding to the next time domain measurement (Fig. 2.5), it appears that there is even more noise present on the 600V bus at 11:00 a.m. than at 3:00 a.m. This is expected since there is more equipment operating at this time. Figure 2.6 shows the corresponding Fourier spectrum for this waveform. Here again, the two "mystery signals" are present, although with smaller amplitudes. This is possibly due to capacitive loads on-line at this time which short some of the energy to ground. Also present is a large noise component below 5kHz and some seemingly random noise between about 10kHz and 60kHz. However, the PLC frequency range, which is of the most interest, seems basically noise free.

The next measurement (Fig. 2.7) was made on the other, quieter, 600V bus at 3:10 p.m. Notice that the low frequency noise component is somewhat smaller than on the other 600V bus. In addition, there is no appreciable noise component found in the mid-frequency band. The two mystery signals are present although with reduced amplitudes. Most importantly, the PLC frequency range is essentially free of noise which means that a carrier current system should not be adversely affected by steady state noise.

Figure 2.5: Time Domain Recording on 600V Bus @ 11:00.

Figure 2.6: Fourier Spectrum of Waveform in Figure 2.5.

Figure 2.7: Time Domain Recording on "Quiet" 600V Bus @ 15:10.

Figure 2.8: Fourier Spectrum of Waveform in Figure 2.7.

## 2.3.2 Fault Conditions

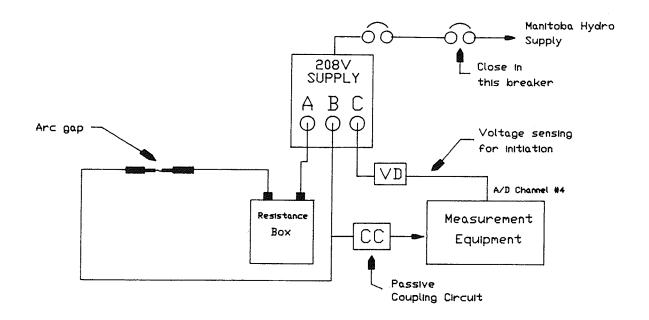

Electrical noise measurements under fault conditions were conducted in the University of Manitoba's machines lab between August 15th and 19th, 1988. Figure 2.9 is a simplified diagram which shows how the staged faults were conducted. Essentially, phases 'A' and 'B' of a 208V supply are shorted together through an arc gap, using four 7.5kW resistance boxes in parallel to limit the current. By properly controlling the current, a large amount of noise can be generated from the arcing fault while making sure that the circuit breaker does not operate. In the arc gap, a thin piece of nickel wire is used to connect phases 'A' and 'B'. When the breaker is closed, this wire evaporates almost instantly and provides the ions necessary to establish an arcing fault.

The measurement software (CHK4FLT.EXE) continuously polls A/D channel 4, looking for any significant deviation from zero volts on phase 'C'. If this occurs, it indicates to the program that the breaker has been closed and so sampling should be started. In Fig. 2.9, sampling is shown on phase 'A' only. Although this was true for most tests, some measured the noise on phase 'C', the unfaulted phase.

Figure 2.9: Staged Fault Equipment.

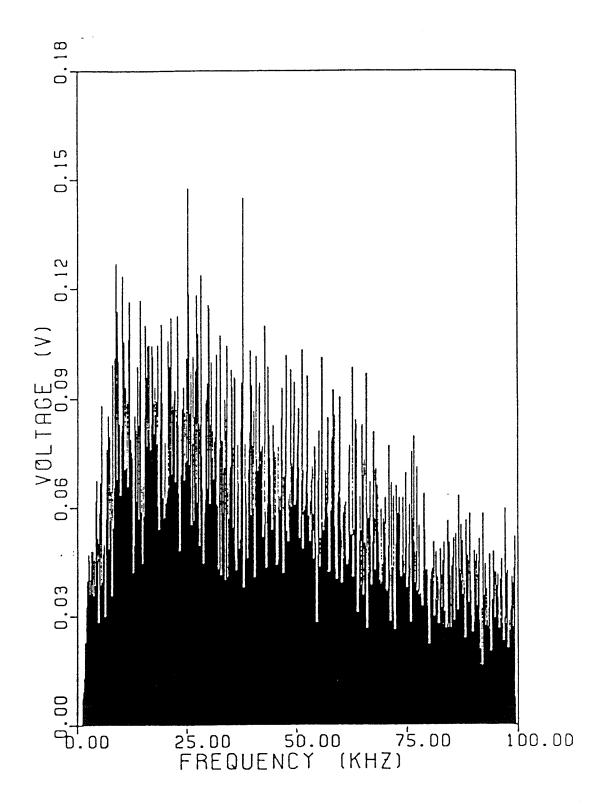

In Fig. 2.10, two cycles of data are shown immediately after an arcing fault is initiated on phases 'A' and 'B'. Here, the noise is worst immediately following the fault initiation as the nickel wire vaporizes and the arc becomes established. As time passes, the arc seems to quench itself and the waveform essentially returns to normal after about three ac cycles. Figure 2.11 shows the Fourier spectrum for this waveform. The electrical noise is very high at low frequencies ( < 5kHz) but seems to decrease exponentially with frequency. In the PLC frequency range, the noise seems to be stable at about 5mV; far less than the 40mV needed to lock in a tone decoder.

Figure 2.10: Fault Recording - Sampling on Phase 'A'.

Figure 2.11: Fourier Spectrum of Waveform in Figure 2.10.

Figure 2.12: Fault Recording - Sampling on Phase 'C'.

Figure 2.13: Fourier Spectrum of Waveform in Figure 2.11.

The next fault recording (Fig. 2.12) is for a situation very similar to the one above except that the sampling is performed on phase 'C' instead of phase 'A'. Since phase 'C' is unfaulted, almost all the noise found here will have been coupled in from phases 'A' and 'B'. The time domain recording shows a waveform which is extremely distorted during the first few milliseconds of the fault's existence. The distortion disappears very quickly and the waveform returns to normal. Fourier transforms reveal that there is somewhat less noise here than in the previous example, although the noise in the PLC range is still about 5 to 10mV.

Figure 2.14 shows the waveform recorded when phase 'A' is shorted to ground rather than to phase 'B'. The time domain plot reveals nothing out of the ordinary; the noise is severe at first but dies to nothing as the arc quenches itself. The frequency domain plot in Fig. 2.15 reveals a noise spectrum very similar to the ones found for phase to phase faults. Again, the noise in the PLC range is negligible.

The next recording (see Fig. 2.16) shows the "worst case" noise for the staged fault measurements. Here, the resistance boxes are short circuited to see the results when the fault current is as high as possible. The electrical noise is quite severe at first as the wire evaporates, and even worse later when the circuit breaker operates. Figure 2.17 shows the noise spectrum for this measurement and, as expected, it is a real mess. As usual, the low frequency noise

Figure 2.14: Fault Recording - Phase 'A' to Ground.

Figure 2.15: Fourier Spectrum of Waveform in Figure 2.14.

Figure 2.16: Fault Recording - Worst Case Noise.

Figure 2.17: Fourier Spectrum of Waveform in Figure 2.16.

is the worst, but, in this case, there is also a lot of noise spread throughout the rest of the spectrum. Even up in the PLC range, the voltage varies from 10 to 65mV. It would be very difficult to make a carrier current system operate reliably under these conditions. Luckily, it turns out that most of the noise shown here is due to the operation of the breaker and not from the electrical arc itself. Since the blocking signals used in the ZSIP system are meant (by definition) to be sent before the breakers operate anyway, this condition does not pose any real problem for the carrier ZSIP system.

In concluding this chapter, it should be noted that a number of electrical noise measurements were taken to get an idea of the kinds of noise expected under normal and fault conditions. These measurements encompassed a variety of load conditions and fault scenarios which are a good representation of conditions found in the real world. None revealed enough noise in the PLC frequency range to jeopardize the operation of a carrier current system utilizing frequencies between 60 and 100kHz. Using the knowledge gained in this chapter, the design of the carrier ZSIP unit's hardware and software can now be started.

#### Chapter III

### HARDWARE/SOFTWARE DESIGN

## 3.1 <u>Design Philosophies</u>

In designing the hardware and software for the carrier ZSIP system there are a few design philosophies to keep in mind:

- 1) Each unit should be universal. Ideally, there should be a "generic box" which can be taken off the shelf and installed at any point in the distribution system. This means that every unit must contain hardware for both transmitting and receiving of signals. In addition, there must be some simple method for the user to configure the unit to operate on a particular distribution level.

- 2) The system must be both reliable and secure. In protection, reliability means that a device WILL operate when it is supposed to. Security means it WON'T operate when it isn't supposed to. One hundred percent reliability and security is impossible to achieve, but, it is reasonable to expect that a

blocking signal will be received in less than 1 ac cycle and, that noise on the bus won't cause a false operation.

3) The system must be inexpensive. After all, if the cost of the carrier system is greater than the cost of running wire and conduit, then there is no reason to develop the carrier system in the first place.

# 3.2 Possible Blocking Signal Schemes

In the following sections, two possible schemes for transmitting blocking signals are discussed. The relative advantages and disadvantages of each are detailed and, from this, a conclusion is reached.

## 3.2.1 FSK System

Frequency shift keying (FSK) is widely used for low speed communications in devices such as 300 baud telephone modems. FSK works by transmitting one frequency to represent a digital zero, and another frequency to represent digital one (see Fig. 3.1). In an application such as a carrier current system, these two frequencies would be quite high so that they would be subject to as little low frequency electrical noise as possible [3,4]. A frequency spacing of up to 10% of the center frequency is typical.

Figure 3.2 shows how FSK could be applied to the ZSIP system. Communication between adjacent levels of distribution is accomplished by transmitting a particular sequence of bits. For example, the relay on the primary distribution bus receives signals from the two relays on the secondary distribution busses using SEQ1. The relays on the secondary busses receive signals from their corresponding downstream relays using SEQ2. Using this scheme, exactly n-1 unique sequences are required for n levels of distribution.

Figure 3.1: Modulation Schemes.

(a) Two level signal. (b) Amplitude modulation.

(c) Frequency modulation (FSK).

Source: Structured Computer Organization, Andrew S. Tannenbaum Prentice Hall Inc., 1984.

Figure 3.2: Application of FSK to the ZSIP System.

An FSK based carrier current system has two main advantages. First, because the transmissions are digital, it makes the system very flexible. To add new levels of distribution to the system, or to change some of the sequences, all that is required is a change in the software. The other advantage is the system's cost. Since the hardware is simple and readily available, each unit should be inexpensive to produce.

Unfortunately, the disadvantages of FSK in this application far outweigh its benefits:

- 1) Referring to Fig. 3.2 again, consider the situation for a fault occurring on the furthest downstream bus. The relay here is required to block its corresponding upstream relay using SEQ4. This relay is meanwhile trying to block its upstream relay using SEQ3, and so on up the distribution. It can be clearly seen that there is going to be a problem here. When more than one unit tries to transmit at once, interference results since each unit is trying to use the same two frequencies.

- 2) The way to get around problem (1) is to introduce delays. The furthest downstream unit gets the first chance to transmit, and, therefore, needs no delay. The upstream units do have delays which increase in duration as you move upstream (notice how this is starting to look like TCP again!). Using this technique eliminates the interference problem but causes another problem. Since the delays described above must be very small to maintain the advantages of the ZSIP system, the transmission must be very fast. To keep the total delay time below one ac cycle for five levels of distribution, a transmission speed of exceeding 2400 baud is required. In July and August of 1988, FSK prototypes using the EXAR 2207/2211 and National Semiconductor LM1893 were

tested using the University's electrical wiring as the transmission medium. It was found that the fastest reliable FSK transmission achievable was only about 600 baud. This is far too slow for the ZSIP system.

3) The final problem with FSK is its vulnerability to random noise. If one is sending a sequence consisting of 8 bits of data, and even one bit is corrupted by noise, then the entire transmission is garbage. To make an FSK system reliable and secure, a lot of redundancy and error checking would have to be incorporated into the transmission scheme.

#### 3.2.2 Multi-frequency System

Presently, systems using amplitude modulated tones make up the majority of carrier current remote control systems [5]. In these devices, a high frequency signal is injected into the ac supply to indicate to a remote unit that a particular action is to be carried out. Different tones are used to select which of several actions is to be performed. In some devices, these tones occupy a relatively low frequency band, between say 3kHz and 10kHz. However, to avoid interference from low frequency noise associated with arcing faults, higher frequencies need to be chosen for this application (60 - 100kHz for example).

Figure 3.3 shows how tones could be applied to the carrier ZSIP system. The technique is similar to FSK except that adjacent relays now communicate by using a particular tone. Tone  $f_4$  uses the lowest frequency,  $f_3$  the second lowest, and so on. For a relay to be blocked, it must both "hear" the required tone, and "see" a fault on the bus. This prevents relays from other distribution branches from blocking relays accidentally. In this system, there are n-1 tones required for n levels of distribution.

Figure 3.3: Application of Tones to the ZSIP System.

The advantages of a multi-frequency PLC system are numerous:

- 1) The system is very reliable since intermittent noise won't affect the receiver. Some type of voting system incorporated into the software would make the system resistant to random noise while maintaining a good deal of sensitivity [6].

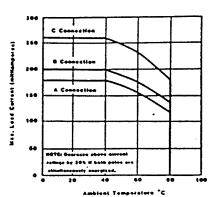

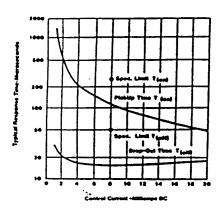

- 2) The system is very fast since all the transmitters can operate at once, hence, there are no delays required. Manufacturer's data states that a tone decoder will typically lock onto a signal with frequency  $f_0$  in 10 cycles of  $f_0$ . i.e. for  $f_0 = 80 \text{kHz}$ , t = 0.125 ms.

- 3) The cost to manufacture each unit is small since the hardware is cheap and readily available.

The only real drawback to this type of system is that it is not quite as flexible as FSK since it is the hardware, not software, that determines the number and frequency of the tones.

## 3.2.3 Blocking Signal Conclusion

Overall, it seems that a multi-frequency system is more suitable for this application than is an FSK system. FSK would be better suited to a use where only one transmitter is used at once, and where transmission speed is not a major concern. For example, FSK would be ideal for remotely interrogating devices, such as wattmeters, over the power lines.

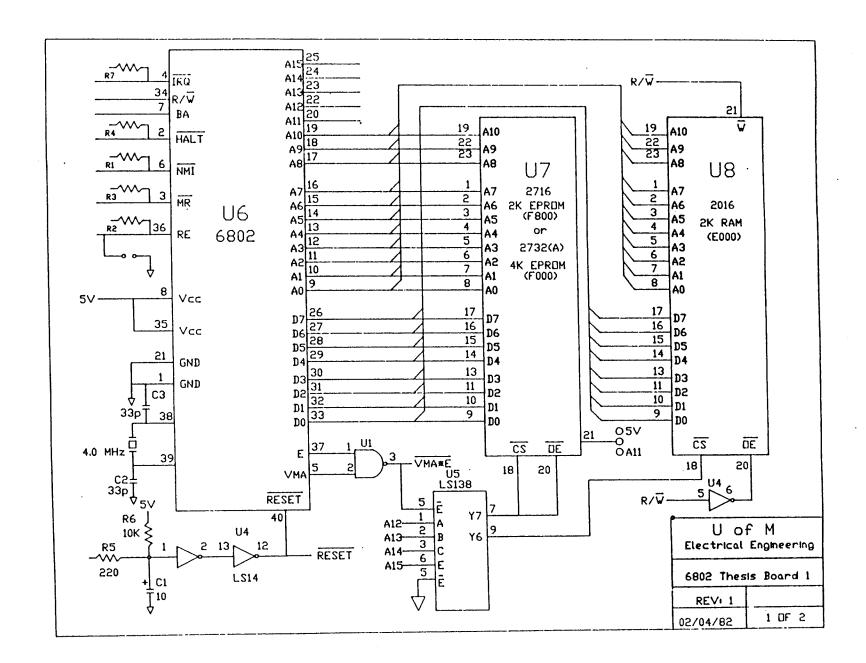

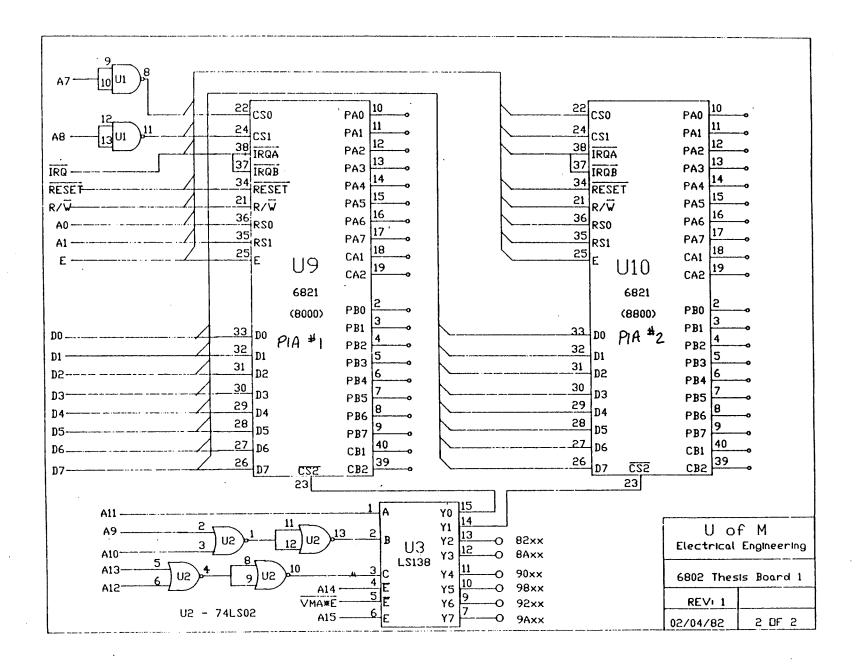

#### 3.3 <u>Hardware Design</u>

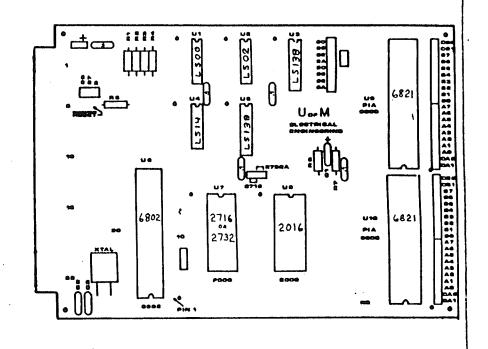

Since the protective relays used in the ZSIP system are microprocessor based, it only makes sense that the carrier current unit should be microprocessor based as well. This way, a common processor could be used to run both the relay and the carrier system, thus reducing the total cost of incorporating the carrier current concept into the ZSIP system. The microprocessor around which the prototype units were built was the Motorola 6802. This processor is basically an enhanced version of Motorola's popular 6800 with 128 bytes of internal RAM provided. The clock rate of 1MHz provides more than enough processor speed for this application. The 6802 is mounted on a PCB along with a Signetics 8732 4K EPROM, 2 Motorola 6821 PIAs for I/O control, and a socket for an additional 2K of RAM.

The remaining hardware is comprised of the carrier current transmitter and receiver. This part of the hardware is controlled by the microprocessor through the two PIAs described above. In the receiver, hardware is provided for the

reception of five different tones. As mentioned before, five tones will allow for up to six levels of distribution. Since three or four is the typical number of levels used in most installations, there should be no problem with this limitation.

The frequencies of the tones used are 95, 87, 79, 71, and 63kHz. A great deal of compromise was required when choosing these frequencies. First, since the measurements that were previously described extended only up to 100kHz, this is the maximum frequency that is known to be "safe". On the other hand, the frequencies should not be too low or there will be insufficient coupling of the signal between the distribution system's busses. One other consideration deals with the wavelength of the PLC compared to the length of the bus. To prevent standing waves,  $\lambda$  should be at least 10 times as long as the bus [5].

i.e. for a bus length of 300m,

$$10\times(300\text{m}) \le \lambda$$

$$3000\text{m} \le \frac{3\times10^8}{f} \qquad f \le 100\text{kHz}$$

This criterion further justifies the statement that the frequency range should not exceed 100kHz.

The frequency spacing of 8kHz is chosen basically arbitrarily to yield the frequency band listed above. However, trouble could arise if this spacing was made too small, since there is some frequency deviation in both the transmitter and receiver.

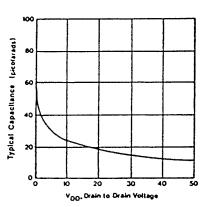

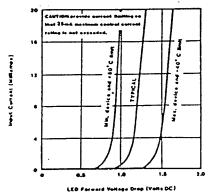

## 3.3.1 Carrier Current Receiver

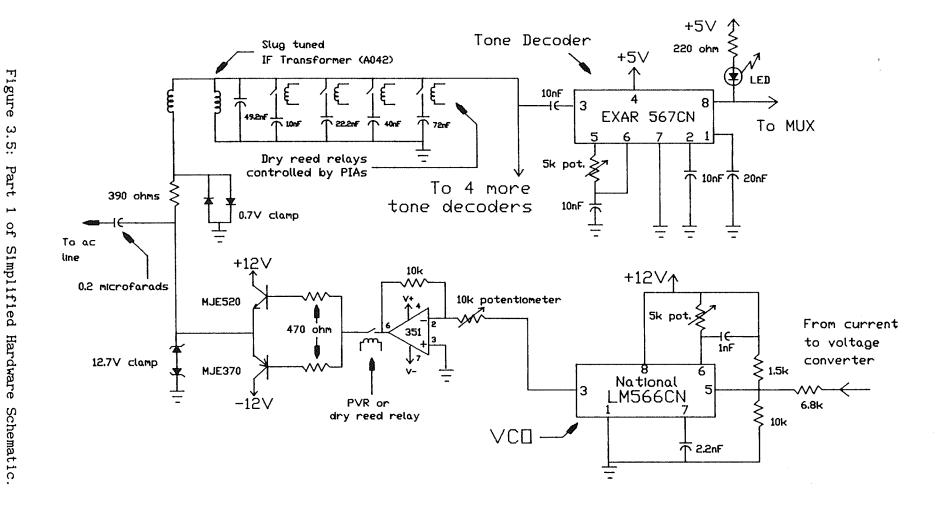

A block diagram of the system's hardware is given in Fig. 3.4 and a schematic in Fig. 3.5. For a signal to be received by the carrier current hardware, it must first pass through a very sharp band-pass filter. This filter is formed using an A042 IF transformer in parallel with some capacitance [7]. This capacitance is chosen by the microprocessor, depending on the frequency of the signal trying to be detected. Dry reed relays are used to switch in the appropriate capacitance to achieve the desired center frequency. It should be noted that the user informs the microprocessor of the tones to be used by setting dip switches on the circuit board. These switches are read immediately after the PIAs are initialized and the settings are stored in RAM for future reference.

Next, the received signal passes through an amplitude limiter. This device is basically just two silicon diodes which clip any voltage above 0.7V. This attenuation is necessary because the capture bandwidth of the tone decoders increases as a function of the input voltage. By limiting the amplitude of the input signal, we are assured that the bandwidth will not rise above a known value.

The tone decoders used (EXAR 567s) were chosen on the basis of their cost, speed, and sensitivity to small signals. In this application, these devices have a lock-in time of less than 0.15ms. and, can detect as little as 40mV of signal

Figure 3.4: Block Diagram of Hardware.

modulated with a great deal of Gaussian noise. The tone decoder center frequency can be very accurately controlled by adjusting a small ten turn potentiometer. Since the BW is so small, exact tuning is important for the unit to perform properly.

Although all five tone decoders are "listening" for a particular tone all the time, the output of only one of them makes it to the PIA. This is accomplished through the use of an 8 to 1 line multiplexer (MUX). This device receives three SELECT lines from the PIA which tell it which tone decoder output to route to the microprocessor. As an added advantage, the MUX has a pin with an inverted output which converts the active low outputs from the TDs to active high signals before being feeding them to the PIA. Note that the MUX's function could have been implemented in software rather than hardware. However, the cost of the MUX is small and, the software is both faster and simpler when the MUX is used. For this reason, the MUX is an integral part of the hardware design.

#### 3.3.2 <u>Carrier Current Transmitter</u>

Control of the transmission hardware is accomplished through PIA #1. To select a particular tone, the PIA simply sends eight bits to the input of the digital to analog (D/A) converter. These eight bits are inversely proportional to the frequency desired with 11111111 being the lowest possible frequency and 00000000 being the highest possible frequency.

The correct binary numbers to yield the tones mentioned in the previous sections were determined experimentally and are now written into the software (see next section). The D/A converter translates the received bits into an analog signal which is passed onto the current to voltage converter.

Since it is important to make the D/A very stable, a special voltage reference is used. The MC1403 precision voltage reference provides a positive reference voltage of exactly +2.500V to the D/A converter. This + $V_{ref}$  is then inverted by a 741 op-amp to provide bipolar references of  $t_{ref}$  to the current to voltage converter (CVC).

The CVC is basically just an inverting op-amp with an adjustable offset voltage. Its purpose is to convert the D/A converter's output current to an analog voltage suitable for input to the voltage controlled oscillator (VCO) without loading the D/A's circuits. The offset voltage is adjusted with a small potentiometer and serves to vary the bias voltage to the VCO's input.

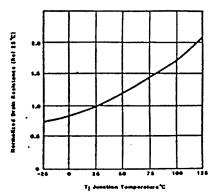

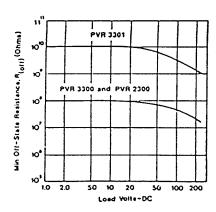

The high frequency tones to be transmitted are produced by the VCO. In the prototype units, National LM566s are used, although other suitable products are available from other manufacturers. The LM566 accepts an analog input voltage and produces a square or triangular wave output with a frequency proportional to this input. For this application, the square wave output is chosen because it results in a higher RMS voltage for equivalent supply voltages.

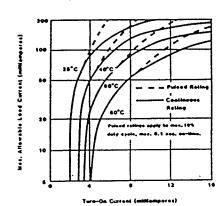

Following the VCO is a photovoltaic relay (PVR). This device acts like a very fast dry reed relay in that it can switch both positive and negative voltages with reasonably large amplitudes. Internally, the PVR uses a dielectrically isolated LED to energize a bidirectional MOSFET (BOSFET) switch. Since there are no moving parts, this device has an almost unlimited life span. The PVR is necessary due to the nature of the transmission scheme (see section on software). Since the transmitted signal appears huge at the tone decoder input (due to its proximity), the tone decoder is essentially blind to all small signals on the line as long as the transmitted signal is present. For this reason, the microprocessor must be able to halt the transmission from time to time so that the tone decoder gets a chance to operate. The PVR provides this capability. The problem with PVRs is that they are relatively new and, hence, fairly expensive. While waiting for the PVRs to arrive, dry reed relays were employed in their place and relatively good performance was still obtained. Thus, as an economy measure, dry reed relays could be substituted here at the expense of some performance.

The final transmitter stage is the push-pull amplifier which uses two large power transistors to amplify the input signal and drive the ac line through a  $0.2\mu F$  capacitor. These transistors each handle about 6W and tend to get very hot when used for an extended period of time. However, since in actual operation the length of a transmission is short (say 10ms.)

this is not a major concern. As a safety precaution, a 12.7V clamp circuit is employed at the output of the amplifier to clip any high frequency noise spikes that may make their way into the transmitter from the ac line.

## 3.4 Software Design

Software to run the carrier current hardware is written in machine code (for speed) and stored in the 4K EPROM on the microprocessor board. This software takes care of two problems that exist with the previously described hardware.

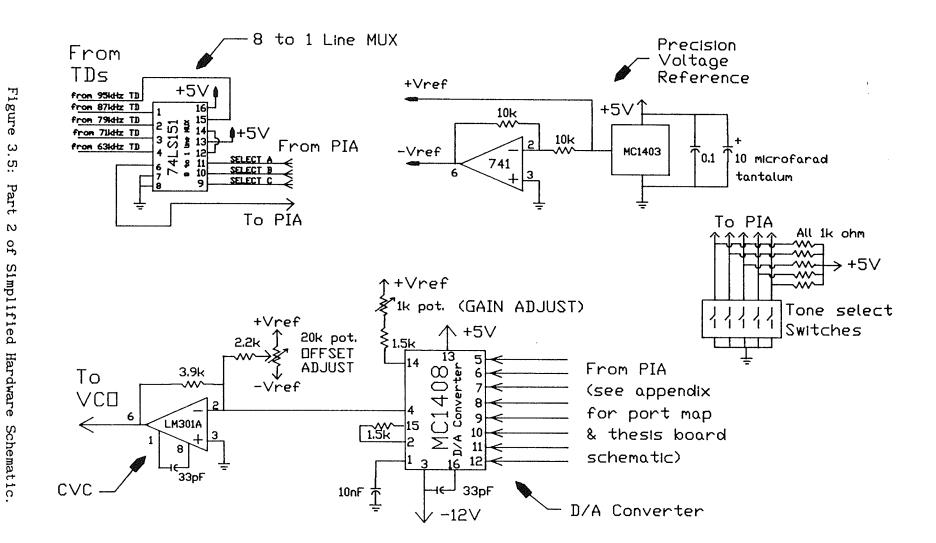

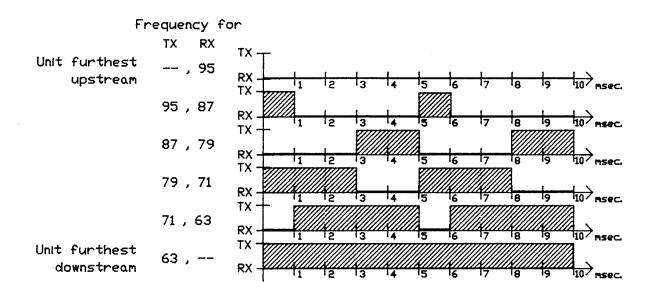

to their proximity to the carrier transmitter, the tone decoders are essentially blind to all small signals on the ac line while the transmitter is operating. To get around this problem, there must be some elaborate method of alternately transmitting and receiving in such a way as to guarantee a sufficient transmit/receive overlap between adjacent relays. Figure 3.6 shows this technique graphically. Since each unit may "see" a fault at a slightly different time, adjacent units must share an overlap time of at least 0.5ms. no matter when the individual transmit/receive cycles begin. In Fig. 3.6, the origin indicates the moment that the fault is detected by the relay. It can be clearly seen that no matter how the graphs are shifted, there is guaranteed to be an overlap of at least 0.5ms. within the 10ms. window. Practically speaking, the difference between the times that individual relays sense the

Figure 3.6: Transmit/Receive Timing Diagram.

fault is small and so the actual TX/RX timing would look very similar to that shown in Fig. 3.6. Here, the overlap between adjacent units has been intentionally maximized for optimum performance.

The second problem taken care of by the software is the susceptibility to spurious noise. Since this noise is of a random nature, the best way to distinguish it from a real signal is to only recognize signals with a duty cycle greater than some threshold value. This is accomplished in the  $\mu P$  based system by polling the MUX output every 0.2ms. (the tone decoder lock-in/ring time) and blocking the relay only if at least two of the last four samples indicate that the required

tone is present. Figure 3.7 details the sampling and voting that occurs within a 2.2ms. window.

Figure 3.7: Receiver Sampling Scheme.

The above voting scheme is only one of many possible schemes. In the section on testing, some results using this method under extremely noisy conditions are presented, along with the results using a slightly modified algorithm.

Figure 3.8 is a flowchart which shows the salient features of the software. Additionally, a complete listing of the program is given in Appendix C. Some noteworthy information not found in the flowchart follows:

- 1) Dip switches are read immediately after PIA initialization and, if no errors are found, their settings are stored in RAM for future reference. This means that the only way to make the unit recognize a change in dip switch settings is to turn the unit off, then back on. If an error is found in the dip switch information, the programming error light is turned on and program execution halts. Either of the following constitutes a programming error:

- (i) more than one switch set (ON)

- (ii) a switch with number greater than 6 set.

- 2) Each dip switch represents a particular pair of transmit and receive tones. The low numbered switches correspond to the high frequencies while the high numbered switches correspond to lower frequencies. When configuring two units for communication, it is essential that the downstream relay use the higher numbered switch. In addition, if units are to communicate, they must use consecutively numbered dip switches (e.g. 1 and 2, or 4 and 5, etc.). This implies that the furthest downstream relay in the distribution system must use the highest numbered dip switch. The second most downstream relay must use the second highest dip switch, and so on.

Figure 3.8: Flowchart of Carrier Current Software - Part 1.

Figure 3.8: Flowchart of Carrier Current Software - Part 2.

- 3) A red button on each unit serves to provide a TRIP signal to the unit for testing purposes. Since for a transmission to occur both units must "see" a fault, a connector is furnished at the back of each unit. When the wires from each unit are connected, the result is that when either test button is pressed, both units "see" a fault at the same time.

- 4) In the software, a default communication window of 10ms. is used. Each relay will be temporarily blocked at the start of this interval and will remain blocked until the 10ms. expires. In this time, the unit will have tried to detect the required blocking signal being sent from the downstream relay. If this signal was detected, then the relay will remain blocked until the fault disappears (or, in these test prototypes, for approximately three seconds). If a block signal was not detected in the 10ms. window, then the relay will be unblocked and allowed to go into its timed mode. If the 10ms. window is not satisfactory, it can be changed by altering the value of the variable TIMER and reassembling the code.

#### Chapter IV

#### **TESTING**

### 4.1 Quantitative Data

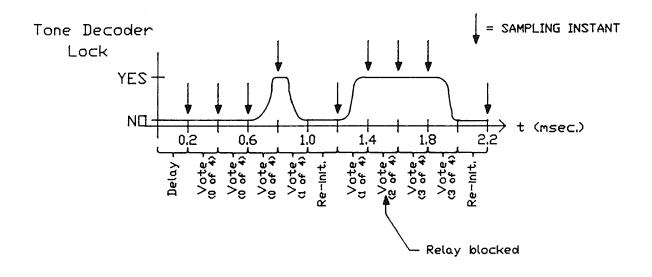

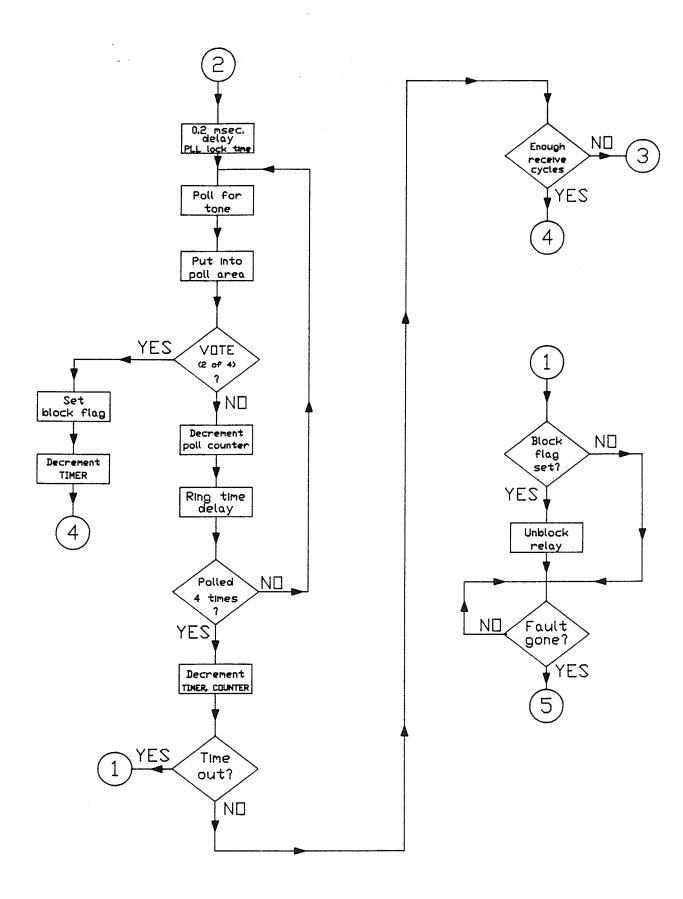

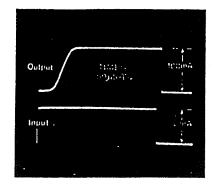

To determine if the carrier current hardware performing as it should, several tests need to be performed. The first test is to find out if the actual transmit/receive scheme is the same as the planned scheme, shown in Fig. 3.6. Here, an analog capture scope is used to view the carrier output using a time scale of 1 ms/div. By using multiple triggers, a picture can be built up showing the unit's output for each possible dip switch setting (see Fig. 4.1). The leftmost side of this picture corresponds to the instant when the unit's test button is pressed. Notice that Fig. 4.1 is nearly identical to the desired output shown in Fig. 3.6. The only discrepancy is that in the actual output there is some overlap of the transmit cycles. For example, the 3rd and 4th traces have a transmit overlap of about 0.1ms. imperfection is caused by the slow operation of the dry reed relay which is used to engage and disengage the transmitter. In the software, this relay is opened about 0.2ms. before the beginning of the receive cycle, although it seems to take about 0.3ms. to actually cease transmitting. Utilizing a PVR to engage the transmitter would eliminate this delay, since

Figure 4.1: Photo of Actual Transmit/Receive Timing.

Figure 4.2: Photo of Tone Decoder Lock-in Response.

it operates about twice as fast as a dry reed relay.

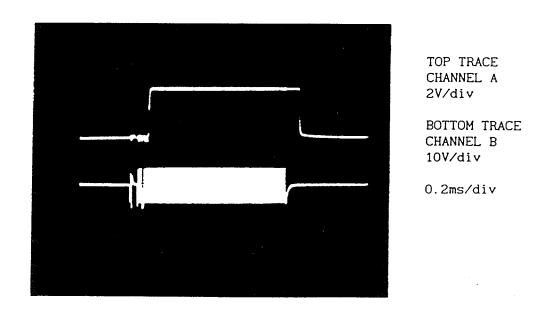

Figure 4.2 shows the scope trace resulting from a test to measure the actual tone decoder lock-in time. The bottom trace is a 95kHz input signal to one of the unit's five tone decoders. The top trace is the signal emerging from the inverting output of the MUX. Notice that the tone decoder has both a finite lock-in time and a finite ring time. It appears that the time to achieve a lock is about 0.125 - 0.15 ms. Most of this delay is due to the tone decoder's phase locked loop (PLL), although some is due to the propagation delay in the MUX. The tone decoder ring time seems to be only about 0.1ms in duration. Finally, note the distortion at the beginning of the transmit cycle. The exact cause of this is unknown, although it is suspected that the dry reed relay is at least part of the problem.

### 4.2 <u>Use of Pseudo Bus</u>

One requirement of the carrier current system is that a signal from it should be able to couple into neighboring phases of the distribution system through the small parallel capacitance. This is necessary so that a blocking signal can skirt around a fault on one phase of the distribution system. In a typical installation, the bus-bars might measure 3" wide, have 6" spacing, and run parallel for 1500'. Therefore, a good guess for this parallel capacitance is:

$C = \frac{\varepsilon A}{d} \quad \text{where: A = area}$   $= 3(in) \times 0.0254(m/in) \times 1500(ft)$   $\times 0.3048(m/ft) = 34.8 \text{ m}^2$   $d = \text{spacing} = 6(in) \times 0.0254(m/in) = 0.1524 \text{ m}$   $\varepsilon = \text{permittivity} \simeq \varepsilon_0 = \text{permittivity of free space}$   $= 8.85 \times 10^{-12} \text{ F/m}$   $\Rightarrow C = 2.02 \times 10^{-9} \text{ F} = 2.02 \text{ nF}$

Since the third phase is twice as far away (12"), the capacitance will be roughly half of this, or 1nF.

To test the carrier system's ability to couple between phases of a distribution system, a piece of pseudo-bus is constructed. This pseudo-bus was made from three, 2m pieces of 1.5" copper bus-bar with a tiny spacing between the phases equal to the thickness of a piece of black electrical tape. A capacitance meter shows that this bus has a capacitance of 2.2nF between the center phase and either outer phase, and about 1.5nF between the two outside phases. This is very similar the the capacitances expected from the long three phase distribution bus described above. The two carrier current prototypes are found to communicate flawlessly between the phases of this pseudo-bus. To determine the minimum phase-to-phase capacitance for the system to work, pseudo-bus is shortened to 1m and the three phases are spaced with packing foam to decrease the capacitance. Using this configuration, the capacitance from the inside conductor to one of the two outside conductors was about 250pF. Capacitance

between the outside conductors was about 150pF. Even with this tiny capacitance, the carrier system works perfectly at all but the very lowest tone. For this reason, there should be no difficulty coupling a blocking signal into nearby phases in an actual distribution system.

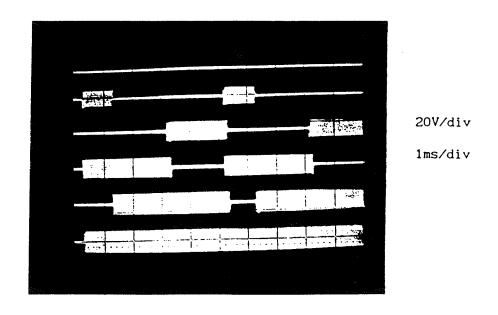

the carrier system's susceptibility electrical noise, a Wavetek pseudo-random noise generator is used. This device has a 100kHz bandwidth and, therefore, produces noise very similar to that which can be expected during an arcing ground fault. In this test, an attempt was made to transmit between the two outermost phases of the pseudo-bus. The noise generator is coupled, through a resistance box, into the same phase as the carrier current The series resistance serves to provide many discrete amplitude levels so that the noise susceptibility can be evaluated over a wide range of conditions. It soon becomes clear that the receiver has no trouble picking out the desired signals even when there is a tremendous amount of noise present. Figures 4.3 and 4.4 are taken with an analog storage scope for different levels of injected noise. In each of these figures, the top trace is the noise present on the receiving bus-bar and the bottom trace is the output from the receiver MUX. Figure 4.4 is particularly impressive because the blocking tone is indistinguishable from the rest of the noise on the bus. Although the duration of the 'ON' signal from the MUX output is shorter than in Fig. 4.3, it is still more than

TOP TRACE CHANNEL A 0.5V/div

BOTTOM TRACE CHANNEL B 2V/div

1ms/div

Figure 4.3: TD Response with Small Amount of Added Noise.

TOP TRACE CHANNEL A 0.5V/div

BOTTOM TRACE CHANNEL B 2V/div

1ms/div

Figure 4.4: TD Response with Large Amount of Added Noise.

long enough to cause the relay to block.

Next, tests need to be performed to determine the absolute maximum amount of noise that the system can tolerate.

There are actually two noise limits to be determined:

- 1) The noise limit for reliable operation.

- 2) The noise limit for security.

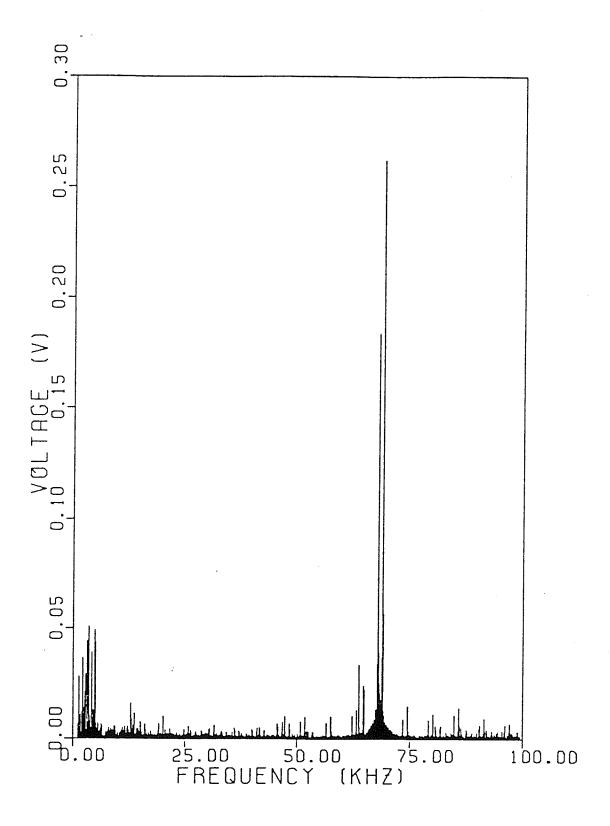

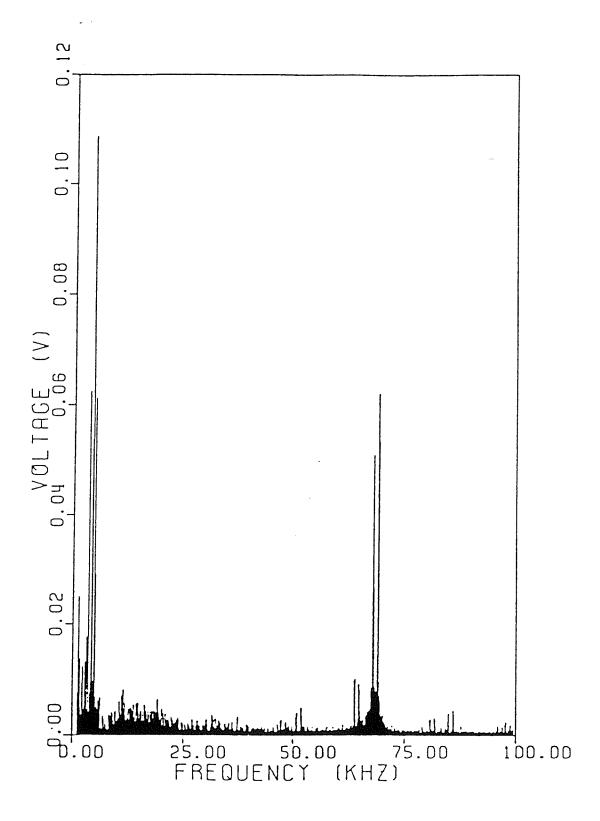

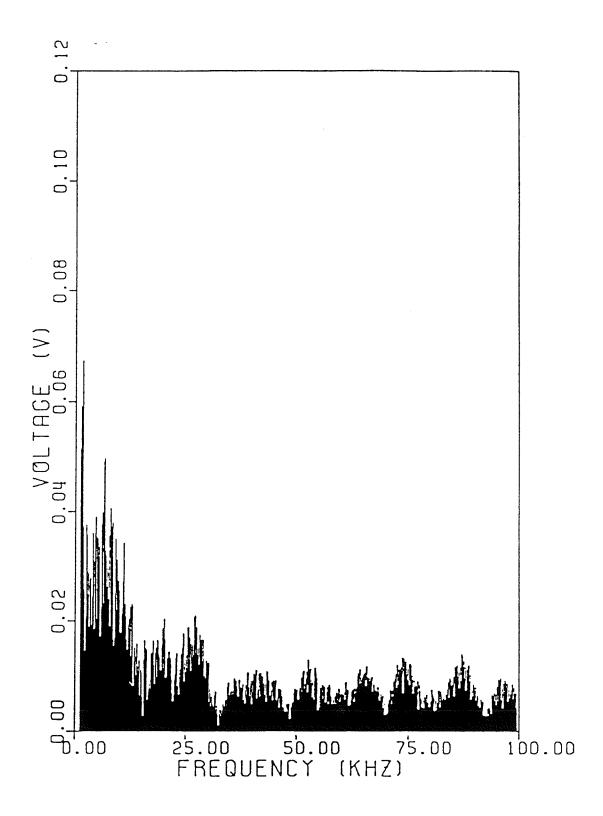

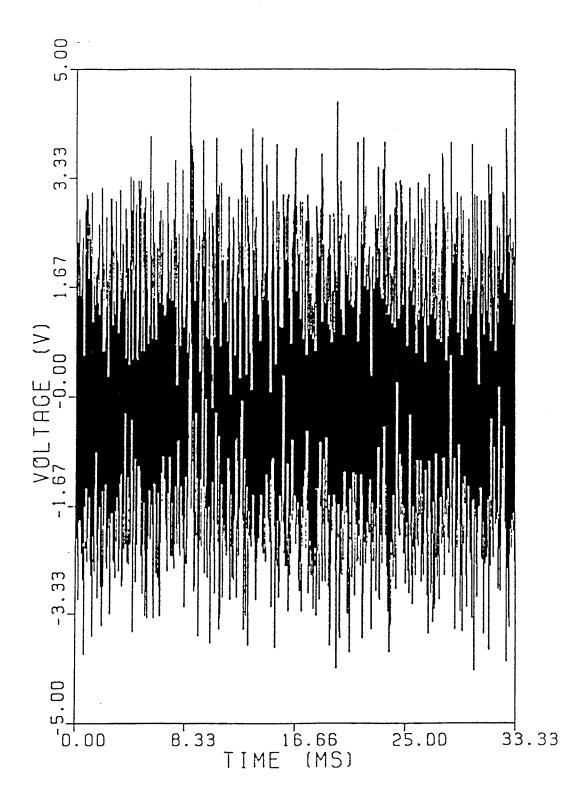

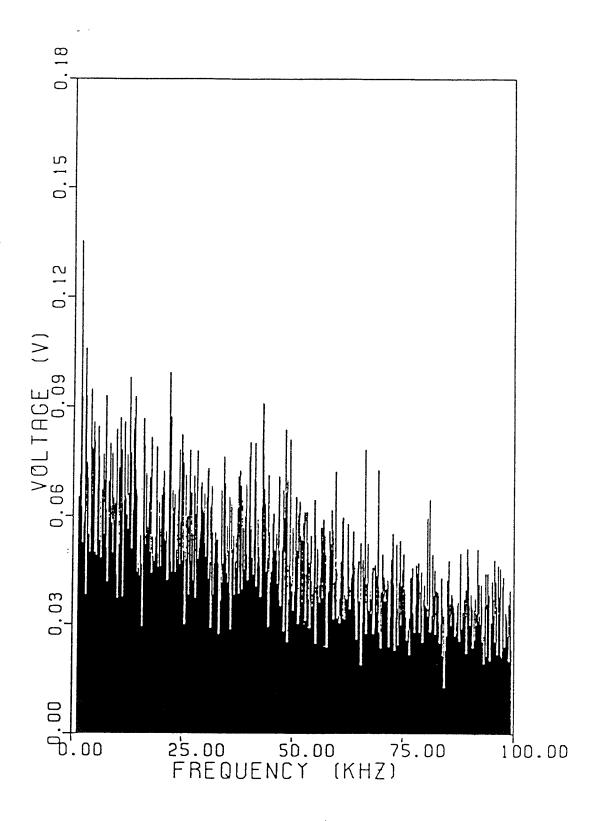

However, as it turns out, the system becomes insecure before it becomes unreliable, so, the latter of these two provides the overall noise limit. To compare the amount of noise present here with the amount present during faults, the QUAD A/D1 is used again. To be consistent with the earlier fault measurements, the samples are taken with the same measurement equipment, including the HP filter. Figure 4.5 is a time domain plot which shows the experimentally determined maximum allowable noise when using the "2 of last 4" voting scheme. The Fourier spectrum of this noise is presented in Fig. 4.6. Notice that the noise seems to be distributed quite evenly across the entire frequency spectrum. In the PLC range, the noise varies from about 20 to 85mV, with an average of about 55mV.

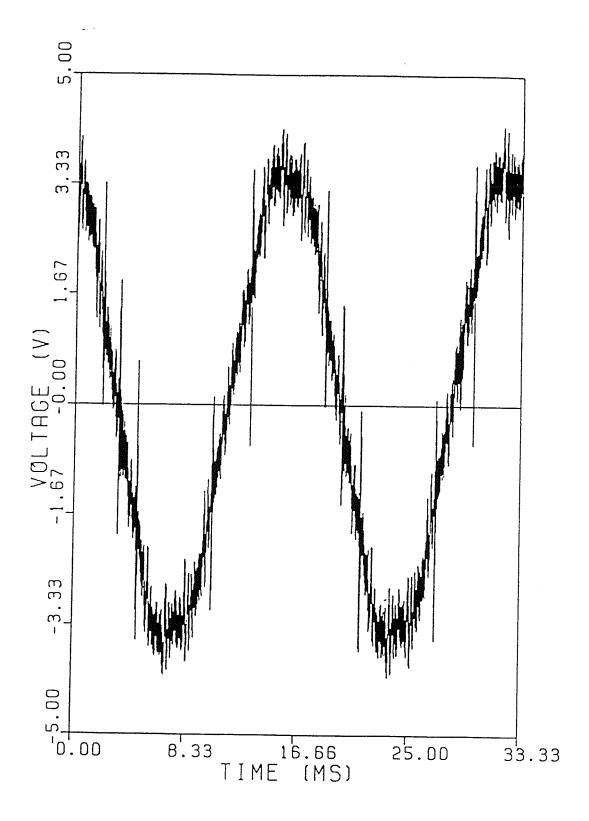

To try to improve the carrier system's security, the voting system is changed to "3 of last 4" scheme. Using this algorithm, a much higher noise limit is found (see Fig. 4.7 and 4.8). The frequency spectrum indicates that the PLC noise

Figure 4.5: Recording of Maximum Allowable Noise when using "2 of Last 4" Voting Scheme.

Figure 4.6: Fourier Spectrum of Waveform in Figure 4.5.

Figure 4.7: Recording of Maximum Allowable Noise when using "3 of Last 4" Voting Scheme.

Figure 4.8: Fourier Spectrum of Waveform in Figure 4.7.

ranges from roughly 25 to 80mV, with a mean of about 65mV. This is about <u>seven times</u> as much noise as was found in the 208V fault tests. Even when the fault test data is extrapolated to 600V, the noise immunity is still acceptable. Keep in mind though, these results are only for two possible voting schemes. Given time, many other even better algorithms could probably be found , and the noise limit could be extended still higher.

To make sure that the carrier current system can operate while low impedance, ground connected loads are present, another test using the pseudo-bus was set-up. Here, transmit lead was coupled onto phase 'A' and the receive lead was placed on phase 'C' along with a resistance box, one side of which was connected to ground. Even when the resistance to ground was reduced to zero ohms, a blocking signal was still easily received on phase 'C'. However, when the resistance box was moved to phase 'A' (same phase as transmitter), no transmission was possible until the series resistance was raised to  $6.8\Omega$ . Shorting phase 'B' (the middle conductor) to ground did not affect the operation in any way. These results suggest that if very low impedance loads are found in an installation, the output impedance and power the transmitter circuit may need to be increased.

### 4.3 Tests Using AC Wiring

Transmitting a carrier current signal over conventional 120V wiring is a useful test because it experiences some of the same noise that can be expected on a 600V supply. However, results from this type of test are not conclusive because of the differences between ac wiring and 600V busses and cables. Some of these differences are:

- AC wiring provides less phase-to-phase coupling because the wiring paths are short and do not necessarily run parallel to each other.

- 2) The signals emitted by the carrier current transmitter eventually return to the unit through ground. Since the neutral wire in conventional wiring is always connected to ground at some point, each and every device connected to the ac line will short some of the RF energy to ground. This effect causes a tremendous attenuation of carrier current signals. In a factory where a 600V supply is used, the loads are usually connected between phases and rarely have a ground connection.

- 3) Many devices such as computers and stereos actually have RF filters in their power supply circuits. These filters usually consist of a capacitor between the

hot and neutral wires, and sometimes include an inductor in series with the hot wire, on the device side of the capacitor [5]. Although these devices keep RF energy out, they also attenuate high frequency signals on the line by shorting them to ground. Industrial installations generally have fewer devices which use this sort of power line conditioning, and, hence, experience less attenuation of high frequency signals.

Power line tests conducted over long distances pose somewhat of a problem since no relays are available for testing. Therefore, the only way to force both units to "see" an imaginary fault at the same time is to connect their test buttons together with a wire. Since the trip signal created by the button is only 5V, there is a limit to how long this wire can be. In the tests conducted, successful transmission of all but the lowest tone was possible between two different labs in the Engineering building. These labs were physically about 30m apart and utilized different phases of the ac supply. The fact that only the lowest tone failed to operate properly is indicative of insufficient coupling capacitance, rather than attenuation or noise.

Overall, the test results indicate that the carrier current system works quite well, although some minor changes in the hardware and/or software may be required in the future.

### Chapter V

#### CONCLUSIONS & RECOMMENDATIONS

The ZSIP system provides the best available protection against ground faults occurring on 600V distribution systems. To make the ZSIP system a more saleable commodity, a system to allow the relays to communicate over 600V busses and cables has been developed. The following are conclusions reached in this thesis research with accompanying recommendations where appropriate:

- 1) Electrical noise measurements have been taken during steady state and fault conditions. Using Goertzel's 2nd order algorithm to analyze the data reveals that the noise present in the PLC frequency range is reasonably small, and therefore, there are no foreseeable interference problems.

- 2) The relative benefits of FSK and multi-frequency systems were weighed. It was decided that a multi-frequency system is better suited to this application due to its inherent speed and reliability.

- 3) Two prototype carrier current units have been constructed and tested. These units are microprocessor based and use five tones to provide communication between six levels of distribution.

Testing these units revealed the following:

- (i) A blocking signal from either unit can easily be transmitted between different phases of the distribution system through the tiny parallel capacitance (as small as 150pF) to be received by the other unit. This ability allows the blocking signal to skirt around a fault on one phase of the supply.

- (ii) Each unit's noise rejection is acceptable, but could be improved by exploring other blocking signal verification schemes (i.e. voting).

- (iii) If very low impedance ground connected loads are expected (  $<6.8\Omega$  ), the carrier current transmitter's output impedance and power may need to be increased.

- 4) Due to the success of the prototype units, I foresee little difficulty extending the ZSIP system to incorporate the carrier current concept.

#### REFERENCES

- [1] Burrus, C.S., and Parks, T.W., <u>DFT/FFT</u> and <u>Convolution</u>

<u>Algorithms: Theory and Implementation</u>, Wiley Interscience

Publications, 1985

- [2] Ramirez, R. W., <u>The FFT, Fundamentals and Concepts</u>, Prentice Hall Inc., 1985

- [3] Ciarcia, S., <u>Build a Power-line Carrier Current Modem</u>, Byte Magazine, August 1983

- [4] Summary of an IEEE Guide to Power Line Carrier Applications, IEEE Transactions on Power Apparatus and Systems, Vol. PAS-99, No. 6, Nov./Dec. 1980

- [5] Cunnningham, J.E., and Horn, D.T., <u>Handbook of Remote Control and Automation Techniques</u>, TAB Books Inc., 1984

- [6] Ciarcia, S., <u>Tune in and Turn on: A Computerized AC Remote Control System</u>, Byte Magazine, April/May 1978

- [7] <u>National Semiconductor, 1984 Linear Supplement</u>, National Semiconductor Corp., 1984

- [8] Jung, W.G., <u>IC Op-amp Cookbook</u>, 2nd Edition, Howard W. Sams & Co. Inc., 1980

- [9] Sedra, A., and Smith, K., <u>Microelectronic Circuits</u>, CBS College Publishing, 1982

- [10] Piety, R.A., <u>Intrabuilding Data Transmission Using Power-line Wiring</u>, Hewlett Packard Journal, May 1987

- [11] EXAR Telecommunications Databook, EXAR Corp., 1985

## Appendix A

## MEASUREMENT SOFTWARE

Page 1-1

```

T I M E \_ S A M - 3 A/D PORTS USED AT ONCE 12 MHz - 80286 Version

0000

0064[

segment para stack 'stack'

db 100 dup(0)

stack

0000

1

0064

stack

ends

0000

segment para public 'data' db 36 dup(0)

0024[

data

0000

fcb

]

0024

0025

0026

0027

dta

db 0

00

namnuml

db

0

01

0026 01

0027 00

0028 42 65 67 69 6E 6E 69

Ck speed is set at maximum.'

6E 67 20 73 61 6D 70

6C 69 6E 67 2E 2E 2E

6D 61 6B 65 20 73 75

72 65 20 63 6C 6F 63

6B 20 73 70 65 65 64

20 69 73 20 73 65 74

20 61 74 20 6D 61 78

69 6D 75 6D 2E

0065 57 61 69 74 69 6E 67

2E 2E 2E 2E

006F 50 72 6F 67 72 61 6D

20 68 61 6C 74 65 64

20 62 79 20 72 65 71

75 65 73 74 2E

0089 46 49 4C 45 20 45 52

52 4F 52 21

0094 57 72 69 74 69 6E 67

20 64 61 74 61 20 66

6F 72 20 73 61 6D 70

6C 65 20 73 65 74 20

namnum2

db

1

00

fcharn

db

Beginning sampling...make sure clo

spmsg

maximum.'

wtmsg

db 'Waiting...'

abmsq

db 'Program halted by request.'

errmsg

db 'FILE ERROR!'

52

57

20

6F

6C

23

flmsg

db 'Writing data for sample set #'

00

00B1

db 0

ssnuml

00B2

00

19E6[

0000

db 0

dw 6630 dup(0)

ssnum2

00B3

storage

]

48 24

28 64

08 04

20 10

01 00

00 00

347F

3483

3487

12 56

32 16

02 01

db 48h, 24h, 12h, 5

db 28h, 64h, 32h, 1

db 8h, 4h, 2h, 1h

db 20h, 10h, 5h, 2h

db 1h, 0h, 0h, 0h

db 0h, 0h, 0h, 0h

lookupl

56h

16h

05

348B

02

lookup2

348F

00

3493

```

```

Microsoft (R) Macro Assembler Version 4.00

2/27/89 12:22:56

Page

1 - 2

0004[

3497

decimal db 4 dup(0)

٦

349B

00

db 0

temph

349C

0.0

templ

db 0

349D

19E6

dw 6630

dw 2210

numsamp

349F

08A2

numloop

34A1

data

ends

0000

code

segment para public 'code'

próc far

0000

main

Std. preamble except retain DS as PTR to PSP

assume cs:code

0000

1E

push ds

B8 0000

1000

mov ax,0

0004

50

push ax

B8 ---- R

mov ax,data

mov es,ax

assume es:data

0005

8000

8E C0

Move FCB parameter from PSP to DS

000A

mov si,5ch

mov di,offset fcb

;string's source

;string's dest.

;string's length

;fwd. transfer

;move the string

ΒE

005C

0000 R

BF

000D

0010

B9 000C

mov cx,12

0013

FC

cld

0014

F3/ A4

rep movsb

Establish data segment addressability

0016 8E D8

mov ds,ax

assume ds:data

Routine to clear the display

mov cx,25

mov al,0ah

call dispchar

loop jback

mov fcharn,61

B9 0019

0018

;set counter;LF character

BO OA

E8 0250 R

001B

;output char.;continue...;# of char. in

001D

jback:

0020

E2 FB

C6 06 0027 R 3D

mov bx,offset spmsg; point to data ;print msg mov al,0ah call dispchar jmp sample; # of char. in ;upcoming msg point to data ;print msg ;print msg ;line feed ;

0022

0027

BB 0028 R

E8 0237 R

B0 0A

002A

002D

E8 0250 R

EB 2D 90

002F

Read the T.O.D. clock

0035

B4 00

mov ah,0

int lah

mov bx,dx

;clear AH

;read T.O.D.

;save LSW

clock:

0037

CD 1A

0039

8B DA

```

```

Microsoft (R) Macro Assembler Version 4.00

2/27/89 12:22:56

Page

1-3 -

int lah

cmp bx,dx

je wait

mov ah,1

int l6h

003B

CD 1A

3B DA

74 FA

wait:

;read T.O.D.

003D

; same as before?

003F

;if yes, go back

;set lowest bit

;read keyboard

0041

B4 01

frstpt:

CD 16

74 12

0043

0045

;if no key has;been pressed,;jump ahead;clear AH

jz fine2

mov ah,0

int 16h

cmp al,3

0047

B4 00

;get key

;is it Ctrl-C?

;no, jump ahead

;abort otherwise

;is it ESC?

;no, jump ahead

;abort otherwise

CD 16

3C 03

75 03

0049

004B

004D

jne finel

E9 0218 R

3C 1B

004F

jmp abort

0052

finel:

cmp al,27

jne fine2

0054

75 03

E9 0218 R

0056

jmp abort

B4 00

CD 1A

0059

fine2:

mov ah,0

005B

int lah

;read T.O.D. clock

005D

cmp dx,bx

jne frstpt

;time to sample? ;no keep looking

75 EO

005F