# RESEARCH ON STABILITY ISSUES OF A GRID-CONNECTED PV INVERTER IN POWER HARDWARE IN THE LOOP (PHIL) ARCHITECTURE

by

Mandip Pokharel

A Thesis submitted to the Faculty of Graduate Studies of

The University of Manitoba

in partial fulfillment of the requirements of the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg, Canada

Copyright © 2020 by Mandip Pokharel

## **Abstract**

This thesis presents an in-detail stability analysis of a Power Hardware in the Loop (PHIL) network formed through an Ideal Transformer Method (ITM) interface. The evergrowing demand of PHIL testing necessitates a thorough research in the area. The ITM interface devices are crucial in determining the accurate and stable PHIL. Therefore, this thesis considers the parameters of these individual devices to develop analytical equations with which the stability can be determined quantitatively. This helps in choosing the interface devices as well as the system parameters before forming the PHIL setup. The PHIL testing is something that requires an experimental result to validate its operation besides the theoretical and mathematical formulations. The work in this thesis follows the methodology of mathematical analysis followed by experimental results.

The PHIL setup used in this thesis for its analysis considers a simple resistor divider network to formulate its hypothesis and finally extends the study to evaluate a Grid Connected PV Inverter (GCPI) in a PHIL architecture. The delay present in the PHIL network as a result of non-ideal interface devices creates a major discrepancy between the results in the actual system with the PHIL system. In order to eliminate the effect of this delay, this thesis considers an application of a Smith Predictor (SP) compensator. This SP compensator consists of a model of the interface and the estimation of the delay in the PHIL network of choice. This thesis

works towards developing the model of the interface device in the ITM interface. To validate the model, an experimental gain and phase measurements are made and compared with the gain and phase of the model. This ensures that an accurate model of the interface is obtained to model the SP compensator. Also, the round-trip delay of the PHIL network under study is estimated through various combinations of I/O devices. Once the SP compensator model is developed, it is implemented in Real Time Digital Simulator (RTDS) to verify the stability predictions made from the theory. The SP employed PHIL network with resistor divider and a GCPI is used as an actual hardware for the experimental validations.

Besides the stability analysis of a PHIL network, this thesis also presents a fundamental work that could benefit the dynamic response of a switched-mode amplifier. The switched-mode amplifier with a conventional linear controller would have a bandwidth limited by the converter parameters. This thesis explores the area of non-linear control by implementing a Second Order Switching Surface (SSS) based Boundary Controller (BC) to a Full Bridge (FB) Voltage Source Inverter (VSI) operating with unipolar switching. The experiments are performed in a 550 VA, VSI prototype which showed a transient response in the range or 150-320 µs. This can easily be extended to push the dynamic response of such setup with use of advanced digital control card complemented by a higher switching semiconductor device.

## **Use of Copyrighted Material**

I would like to confirm the approval from all the authors and hereby acknowledge the use of following publications during the preparation of this thesis. Only the contents of the publications where I am the first author are included in this thesis.

#### **Publications in IEEE Journal**

- M. Pokharel, and C. N. M. Ho, "Development of Interface Model and Design of Compensator to Overcome Delay Response in a PHIL Setup for Evaluating a Grid-Connected Power Electronic DUT," IEEE Transactions on Power Electronics (Submitted).

- ©2020 IEEE. Reprinted, with permission, from M. Pokharel, and C. N. M. Ho,

"Stability Analysis of Power Hardware in the Loop (PHIL) Architecture with Solar Inverter," IEEE Transactions on Industrial Electronics (Early Access), 2020.

- ©2019 IEEE. Reprinted, with permission, from M. Pokharel, N. Hildebrandt, C. N. M. Ho and Y. He, "A Fast-Dynamic Unipolar Switching Control Scheme for Single-Phase Inverters in DC Microgrids," IEEE Transactions on Power Electronics, vol. 34, no. 1, pp. 916-927, Jan. 2019.

©2019 IEEE. Reprinted, with permission, from M. Pokharel, A. Ghosh and C. N. M.

Ho, "Small-Signal Modelling and Design Validation of PV-Controllers With INC-MPPT Using CHIL," IEEE Transactions on Energy Conversion, vol. 34, no. 1, pp. 361-371, March 2019.

#### **Publications in IEEE Conference**

- ©2020 IEEE. Reprinted, with permission, from M. Pokharel, and C. N. M. Ho, "Modelling and Experimental Evaluation of Ideal Transformer Algorithm Interface for Power Hardware in the Loop Architecture," 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, pp. 1404-1410, March 2020.

- ©2017 IEEE. Reprinted, with permission, from M. Pokharel and C. N. M. Ho, "Stability study of power hardware in the loop (PHIL)simulations with a real solar inverter," IECON 2017 43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, 2017, pp. 2701-2706, October 2017.

Regarding the copyright policy of IEEE, following is endorsed;

"In reference to IEEE copyrighted material, which is used with permission in this thesis, the IEEE does not endorse any of University of Manitoba's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to <a href="http://www.ieee.org/publications\_standards/">http://www.ieee.org/publications\_standards/</a> publications/rights/rights link.html to learn how to obtain a License from RightsLink. If

applicable, University Microfilms and/or ProQuest Library, or the Archives of Canada may supply single copies of the dissertation."

## Acknowledgements

I am highly indebted to my advisor Dr. Ngai Man (Carl) Ho for his constant guidance, encouragement and motivation throughout my PhD study. I am grateful to Dr. Ho for always being available to discuss research works as well as for reviewing my research papers and providing with critical comments. I feel honored to be the part of such a glorious learning environment.

I would also like to recognize the invaluable advice provided time to time by my internal committee members Dr. Athula Rajapakse and Dr. Hartmut Hollaender to help shape this thesis. Special thanks go to my external examiner for taking the time to read this thesis and providing with valuable suggestions to help improve the quality of the work.

The work in this thesis would not have been possible without the resources and equipment in the RIGA lab. I would also like to pay a special regard to my lab mates Avishek Ghosh, Dong Li, Hafis Umar-Lawal, Isuru Jayawardana, Dr. King Man Siu, Dr. Radwa Abdalaal, Yang Zhou, Yanming Xu, Dr. Yuanbin He and Zhuang Zhang for making this learning experience fruitful and memorable. I appreciate the help of technical support staffs Mr. Erwin Dirks and Mr. Shrimal Koruwage for arranging various equipment and making them readily available.

I express my deepest gratitude to my parents Guna Raj Pokharel and Kishori Pokharel for continuously believing in me. Finally, I wish to shower a special thanks to my wife Rabina Koirala for being patient with me and giving me the emotional support and encouragement throughout this academic pursuit.

# **Dedication**

To my dear parents, my beloved wife and my supportive sister!

# **Table of Contents**

| Abs  | tracti                                             |  |  |

|------|----------------------------------------------------|--|--|

| Use  | of Copyrighted Materialiii                         |  |  |

| Ack  | Acknowledgements vi                                |  |  |

| Ded  | licationviii                                       |  |  |

| Tab  | le of Contentsix                                   |  |  |

| List | of Tablesxiv                                       |  |  |

| List | List of Figuresxv                                  |  |  |

| Nor  | Nomenclaturexx                                     |  |  |

| Cha  | pter 1 Introduction 1                              |  |  |

|      | 1.1. Background                                    |  |  |

|      | 1.2. Motivation2                                   |  |  |

|      | 1.3. Statement of the Problem                      |  |  |

|      | 1.4. Thesis Statement5                             |  |  |

|      | 1.5. Thesis Objectives and Research Contributions  |  |  |

|      | 1.6. Thesis Organization                           |  |  |

| Cha  | pter 2 Literature Review on Components of a PHIL10 |  |  |

|      | 2.1. A Brief History                               |  |  |

|      | 2.2. Real Time Simulators                          |  |  |

|     | 2.3. Interface Algorithms                                                  | 13 |

|-----|----------------------------------------------------------------------------|----|

|     | 2.4. Power Amplifier                                                       | 15 |

|     | 2.5. Time Delay                                                            | 16 |

|     | 2.6. Delay Compensation Techniques                                         | 18 |

|     | 2.7. A Grid Connected PV Source                                            | 21 |

|     | 2.8. PHIL Case Studies                                                     | 23 |

|     | 2.9. Summary of Chapter 2                                                  | 24 |

| Cha | pter 3 Small-Signal Model of a Physical PV-Controller with CHIL Validation | 25 |

|     | 3.1. Introduction                                                          | 26 |

|     | 3.2. System Description                                                    | 28 |

|     | 3.3. System Architecture                                                   | 29 |

|     | 3.3.1 Topology of Power Conversion Stage                                   | 29 |

|     | 3.3.2 Control Strategy                                                     | 30 |

|     | 3.4. Mathematical Modelling                                                | 31 |

|     | 3.4.1 Linearized Model of a PV source                                      | 31 |

|     | 3.4.2 Modelling a Converter                                                | 33 |

|     | 3.4.3 Modelling a MPPT Controller                                          | 36 |

|     | 3.4.4 Modelling a Voltage Controller                                       | 37 |

|     | 3.5. Model Validation and Controller Design                                | 39 |

|     | 3.5.1 Power Stage Model Validation                                         | 39 |

|     | 3.5.2 Controller Design                                                    | 42 |

|     | 3.5.3 Controller Performance Evaluation                                    | 44 |

|     | 3.6. System Implementation and Experimental Results                        | 46 |

|     | 3.7. Summary of Chapter 3                                                  | 51 |

| Cha | pter 4 Stability of a PHIL System: A Quantitative Analysis                 | 53 |

| 4.1. Introduction                                                             | 54   |

|-------------------------------------------------------------------------------|------|

| 4.2. System Modelling and Analysis                                            | 55   |

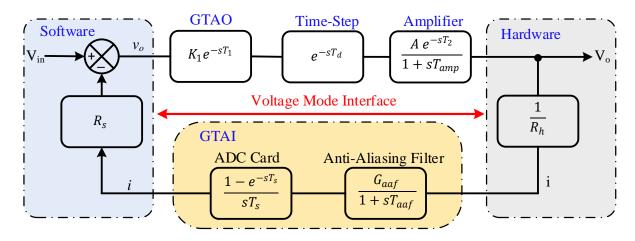

| 4.2.1 PHIL Architecture                                                       | 55   |

| 4.2.2 Interface Modelling                                                     | 56   |

| 4.2.3 Approximate Delay Model                                                 | 58   |

| 4.3. Development of Stability Equations                                       | 62   |

| 4.3.1 Necessary but Not Sufficient Condition                                  | 63   |

| 4.3.2 Formulation of Stability Criteria                                       | 64   |

| 4.3.3 Investigating Stability                                                 | 65   |

| 4.4. Verifying the Stability                                                  | 69   |

| 4.4.1 A Resistor Divider Network                                              | 69   |

| 4.4.2 A Grid Connected PV Inverter                                            | 71   |

| 4.5. Experimental Evaluation with PHIL                                        | 72   |

| 4.5.1 A Resistor Divider Network                                              | 73   |

| 4.5.2 PHIL with a Grid Connected PV Inverter                                  | 78   |

| 4.5.2.1 Steady-State Operations                                               | 80   |

| 4.5.2.2 Transient Operations                                                  | 82   |

| 4.5.2.3 Accuracy Estimation                                                   | 83   |

| 4.6. Discussion on Future Applications                                        | 84   |

| 4.7. Summary of Chapter 4                                                     | 85   |

| Chapter 5 ITM Interface Characterization and Compensator Design for a Delay I | Free |

| PHIL Response                                                                 | 86   |

| 5.1. Introduction                                                             | 87   |

| 5.2. Mathematical Model of ITM Interface                                      | 88   |

| 5.2.1 Model of an Analogue Input Card                                         | 89   |

|   | 5.2.2 Model of an Analogue Output Card                                  | 93  |

|---|-------------------------------------------------------------------------|-----|

|   | 5.2.3 Model of a Linear Amplifier                                       | 93  |

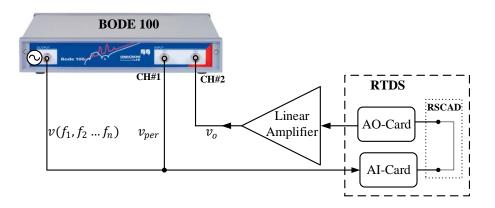

|   | 5.3. System Implementation                                              | 94  |

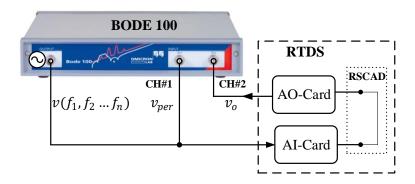

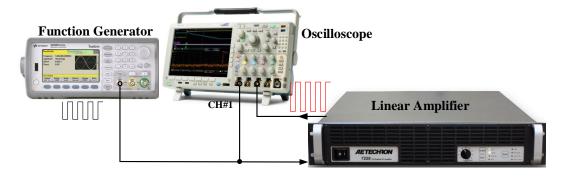

|   | 5.3.1 AO-AI Card Frequency Response Measurement Setup                   | 94  |

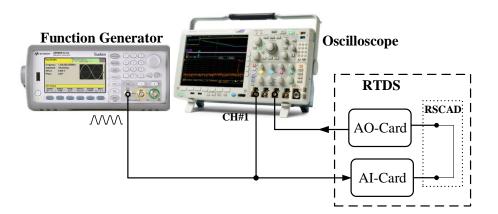

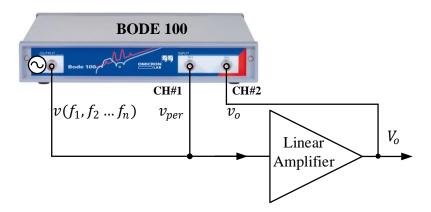

|   | 5.3.2 Linear Amplifier Frequency Response Measurement Setup             | 96  |

|   | 5.3.3 AO-AI-Linear Amplifier Frequency Response Measurement Setup       | 97  |

|   | 5.4. Experimental Results and Model Validation                          | 98  |

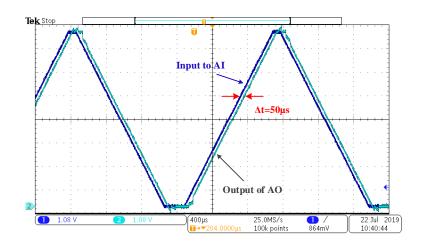

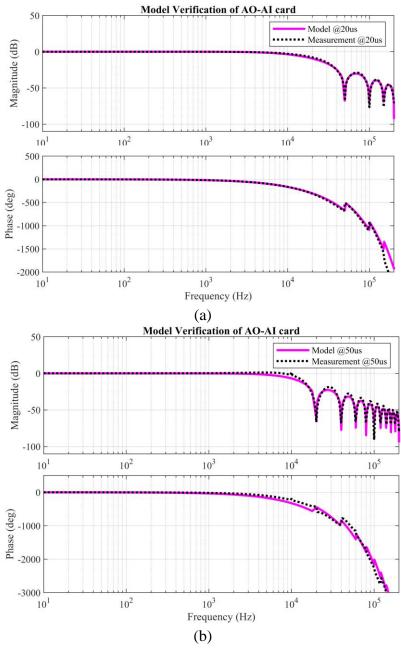

|   | 5.4.1 AO-AI Card Model Validation                                       | 98  |

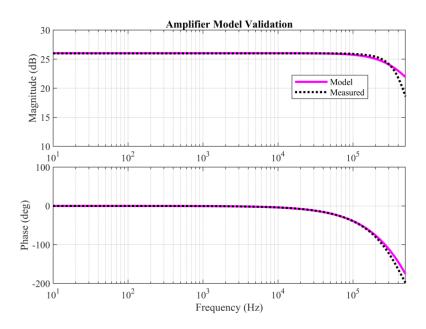

|   | 5.4.2 Linear Amplifier Model Validation                                 | 101 |

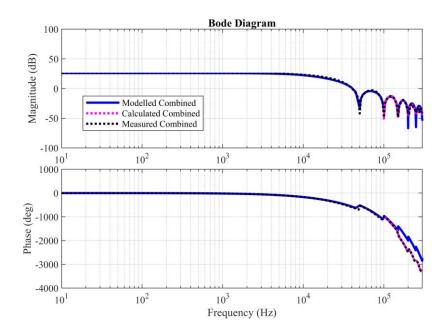

|   | 5.4.3 Linear Amplifier with AO-AI Model Validation                      | 103 |

|   | 5.5. Stability of a PHIL with an ITM Interface                          | 104 |

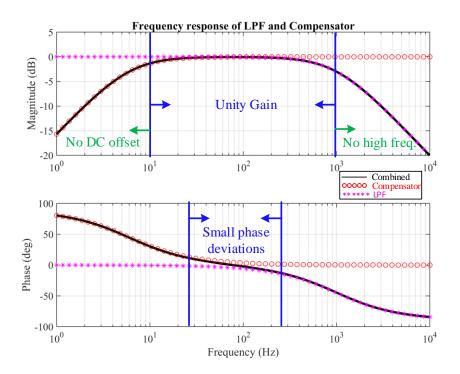

|   | 5.6. Delay Compensation of a PHIL System                                | 105 |

|   | 5.7. Experimental Verification of a Compensator Employed PHIL           | 110 |

|   | 5.7.1 A Case Study of Resistor Divider Network in PHIL                  | 110 |

|   | 5.7.2 A Case Study of Evaluating a PV Inverter in PHIL                  | 113 |

|   | 5.8. Summary of Chapter 5                                               | 117 |

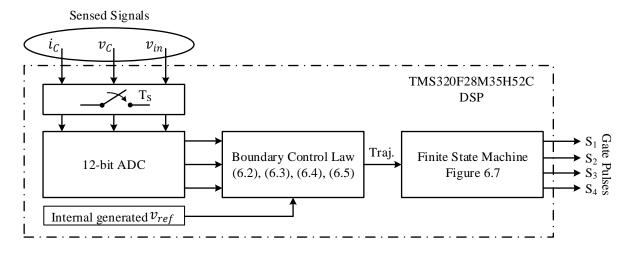

| C | Chapter 6 A Fast Dynamic Switched-Mode Amplifier with 3-Level Switching | 119 |

|   | 6.1. Introduction                                                       | 120 |

|   | 6.2. Principle of Operation                                             | 123 |

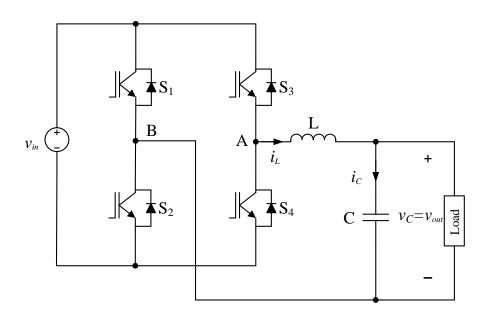

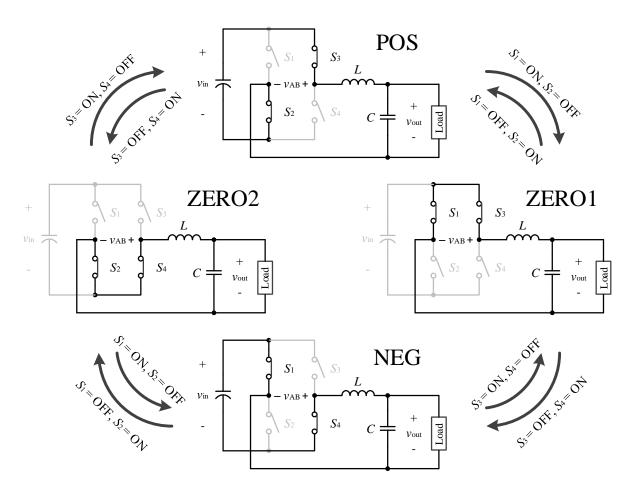

|   | 6.2.1 Switching Pattern of a USS                                        | 124 |

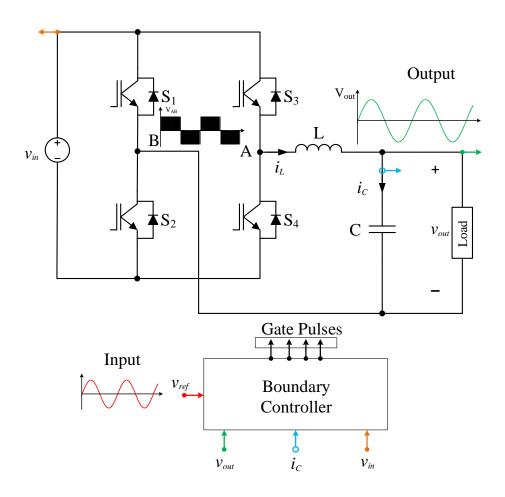

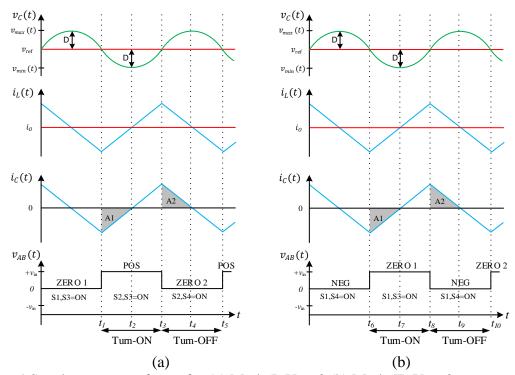

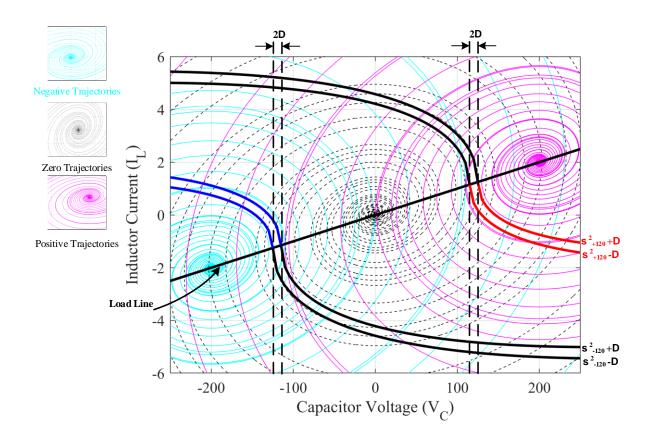

|   | 6.2.2 BC Law for Output Voltage Control with USS                        | 126 |

|   | 6.3. Steady-State Characteristics                                       | 131 |

|   | 6.3.1 Duty Ratio                                                        | 132 |

|   | 6.3.2 Inductor Current Ripple                                           | 132 |

|   | 6.3.3 Capacitor Voltage Ripple                                          | 133 |

|   | 6.3.4 Switching Frequency                                               | 134 |

| 6.4. Controller Design and Implementation                        | 135 |

|------------------------------------------------------------------|-----|

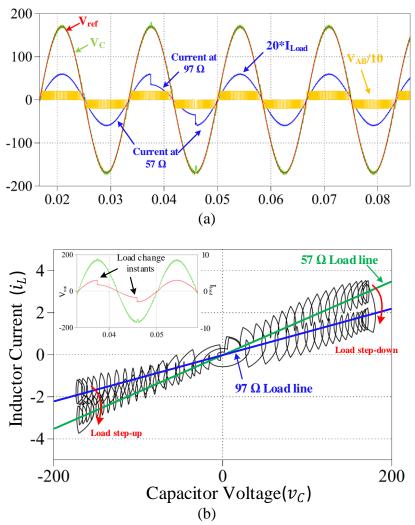

| 6.5. Simulation and Experimental Results                         | 138 |

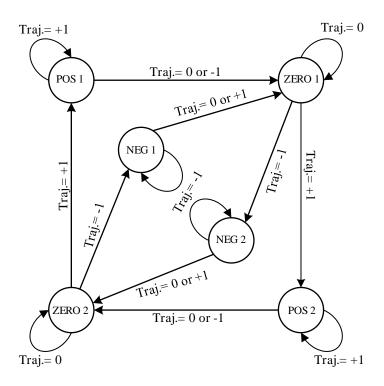

| 6.5.1 Simulation Results with Boundary Controller                | 138 |

| 6.5.2 Simulation Results with Conventional Controllers           | 142 |

| 6.5.2.1 Directly Implemented PI Controller                       | 142 |

| 6.5.2.2 PI Controller with Reference Frame Transformation        | 142 |

| 6.5.2.3 PR Controller                                            | 143 |

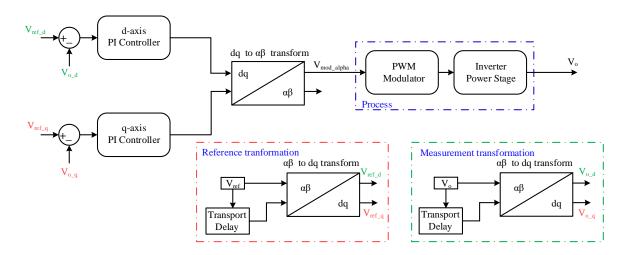

| 6.5.3 Experimental Results                                       | 144 |

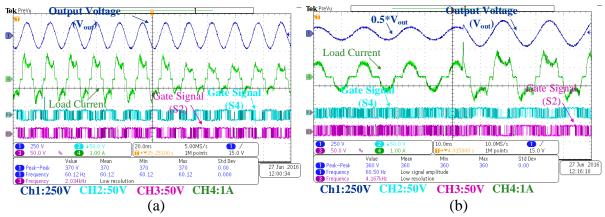

| 6.5.3.1 Steady State Operation with BC                           | 145 |

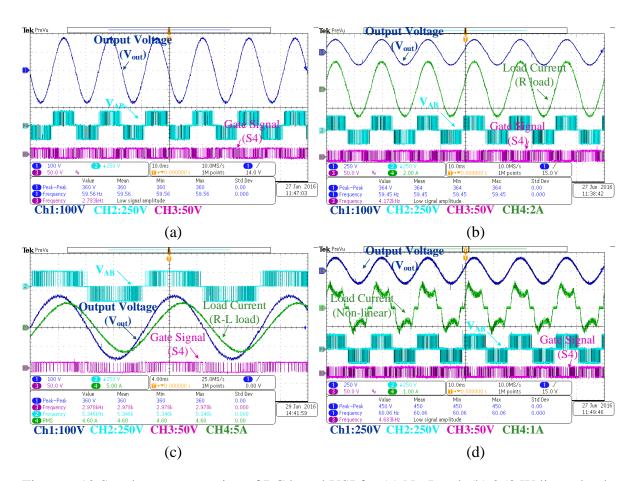

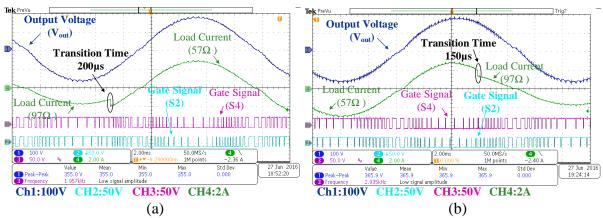

| 6.5.3.2 Performance of BC During Load Transients                 | 147 |

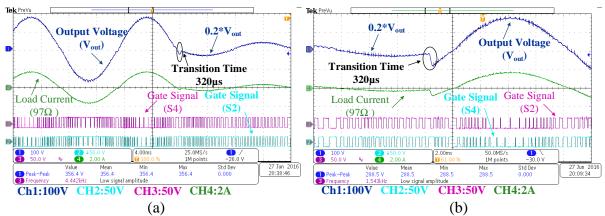

| 6.5.3.3 Performance of BC During Reference Transients            | 148 |

| 6.5.3.4 Performance of BC During Transients with Non-linear Load | 149 |

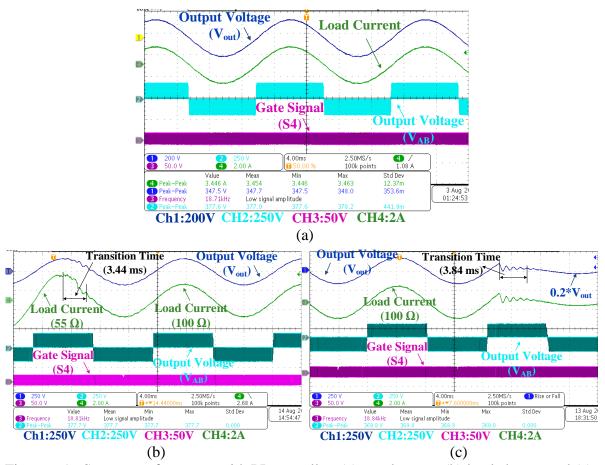

| 6.5.3.5 Performance with a Conventional PI Controller            | 150 |

| 6.5.3.6 Performance Evaluation of BC based FB VSI                | 151 |

| 6.6. Discussions                                                 | 152 |

| 6.6.1 Comparison with Linear Amplifier                           | 153 |

| 6.6.2 Limitations                                                | 155 |

| 6.7. Summary of Chapter 6                                        | 156 |

| Chapter 7 Conclusion and Possibility of Future Extensions        | 157 |

| 7.1. Conclusion and Major Contribution                           | 157 |

| 7.2. Possible Future Extensions                                  | 160 |

| References                                                       | 163 |

| Appendix A                                                       | 182 |

| Appendix B                                                       | 185 |

# **List of Tables**

| Table 3.1 Parameter of BP-365 PV module at Standard Test Conditions (STC)      | 40         |

|--------------------------------------------------------------------------------|------------|

| Table 3.2 Equivalent SD model data for BP-365.                                 | 40         |

| Table 3.3 System specifications                                                | 41         |

| Table 4.1 Interface parameters                                                 | 60         |

| Table 4.2 ISE comparisons for varying value of $R_C$ .                         | 61         |

| Table 4.3 Stability criteria with RH table.                                    | 64         |

| Table 4.4 System specifications                                                | 79         |

| Table 4.5 Error measurements.                                                  | 84         |

| Table 5.1 AO-AI card model parameter.                                          | 101        |

| Table 5.2 Amplifier parameter                                                  | 102        |

| Table 6.1 System parameter for the state-plane plot                            | 131        |

| Table 6.2 System performance with various controllers.                         | 144        |

| Table 6.3 Specification of the VSI prototype.                                  | 145        |

| Table 6.4 Table of measurements.                                               | 152        |

| Table 6.5 Simulation parameters for measuring step response of switched-mode a | ımplifier. |

|                                                                                | 153        |

# **List of Figures**

| Figure 1.1 A PHIL test setup for a grid-connected PV inverter                               |

|---------------------------------------------------------------------------------------------|

| Figure 2.1 A comparison of various simulation platforms                                     |

| Figure 2.2 ITM interface (a) Voltage mode (b) Current mode                                  |

| Figure 2.3 Control of a plant with delay.                                                   |

| Figure 2.4 Control of a plant with delay (a) SP employed block (b) equivalent block [40] 20 |

| Figure 3.1 A typical two-stage grid connected PV inverter scheme                            |

| Figure 3.2 Architecture of a DC power conversion stage                                      |

| Figure 3.3 Linear model of a PV source                                                      |

| Figure 3.4 Schematic of a power conversion stage                                            |

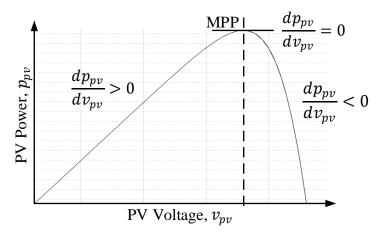

| Figure 3.5 Graphical representation of an INC algorithm                                     |

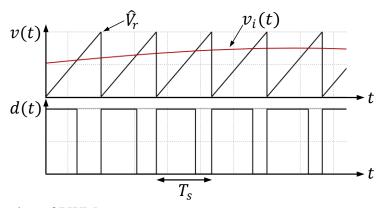

| Figure 3.6 Generation of PWM                                                                |

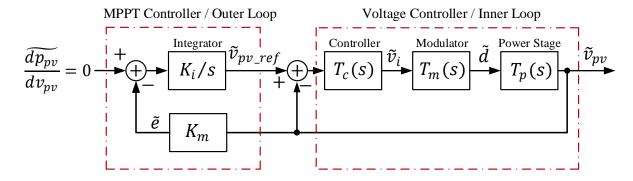

| Figure 3.7 A comprehensive small-signal model of PV source with its controller              |

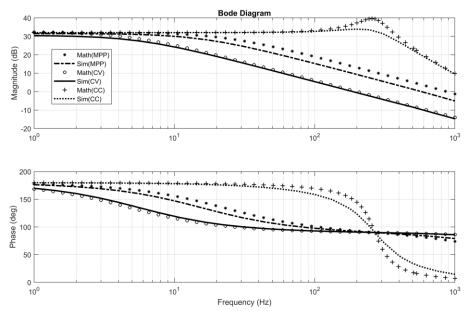

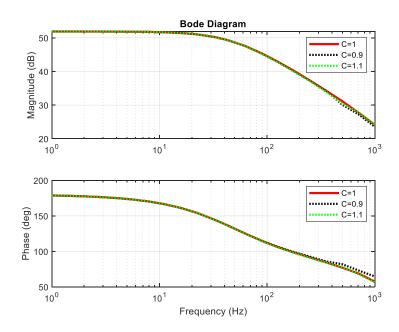

| Figure 3.8 Power stage frequency responses at various operating points in I-V curve 41      |

| Figure 3.9 Frequency response of power stage due input capacitance variations               |

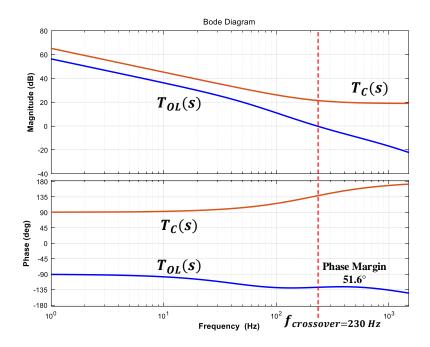

| Figure 3.10 Frequency response of inner loop $T_{OL}(s)$ and controller $T_C(s)$            |

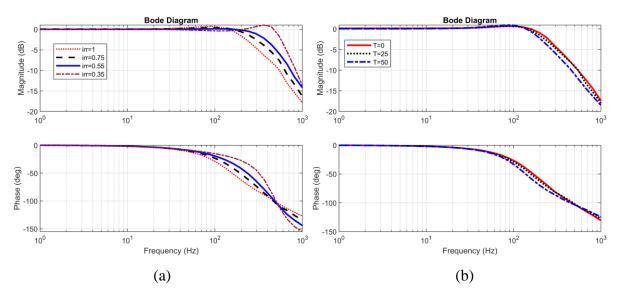

| Figure 3.11 Frequency response of inner loop with varying (a) Irradiance at Temp=25 °C and  |

| (b) Temperature at Irradiance=1 Sun. 44                                                     |

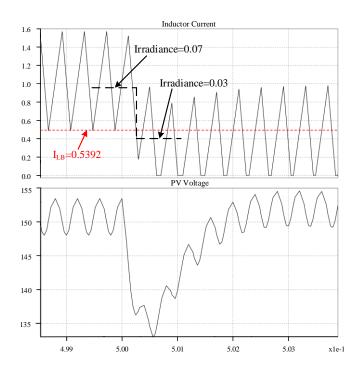

| Figure 3.12 Dynamic transition in irradiance for switching from CCM to DCM45                                          |

|-----------------------------------------------------------------------------------------------------------------------|

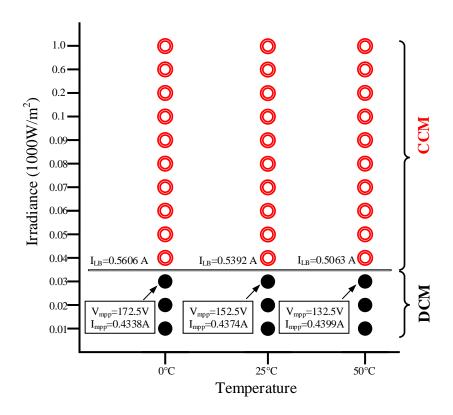

| Figure 3.13 Loci of operating points with variation in temperature and irradiance                                     |

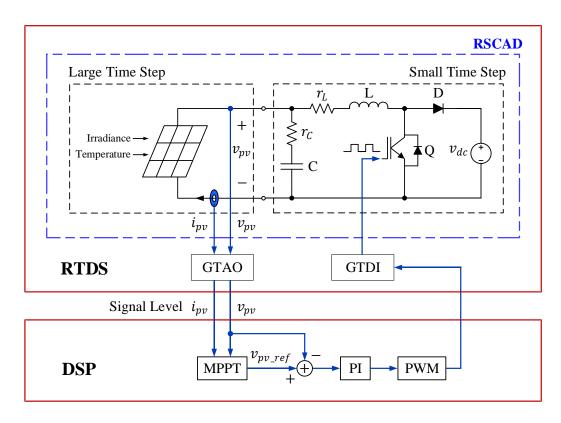

| Figure 3.14 System implementation setup for CHIL testing of controller                                                |

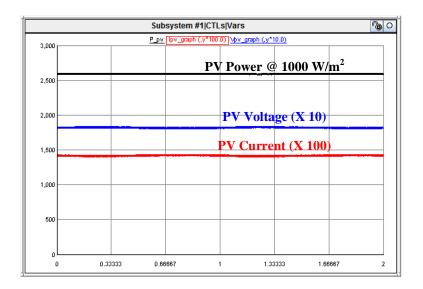

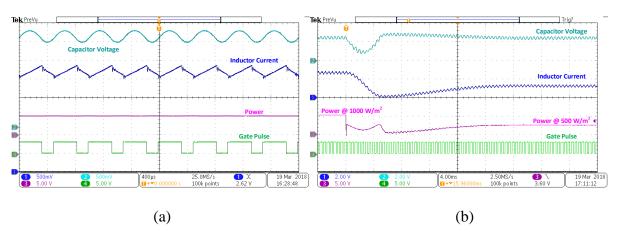

| Figure 3.15 Steady-state response captured in RSCAD-runtime at irradiance $1000 \text{ W/m}^2 \dots 480 \text{ m}^2$  |

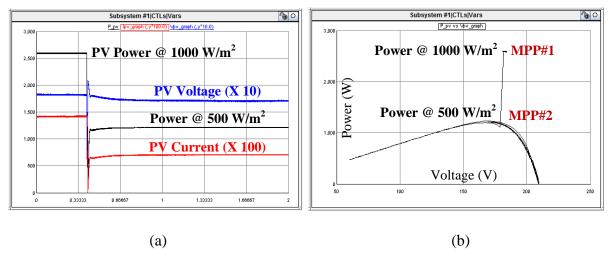

| Figure 3.16 (a) Transient response of the system for irradiance change from $1000 \text{ W/m}^2$ to $500 \text{ m}^2$ |

| W/m <sup>2</sup> (b) Change of operating point in P-V curve due to transient                                          |

| Figure 3.17 Experimental results (a) Steady-state and (b) Transient, Ch. 1 (5 V corresponds to                        |

| 26.6 A), Ch. 2 (5 V corresponds to 368.33 V), Ch. 3 (5 V corresponds to 2.597 kW) 49                                  |

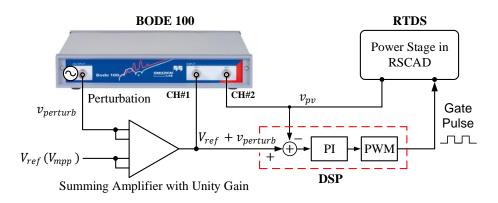

| Figure 3.18 Connection scheme of Bode100 for frequency response evaluation 50                                         |

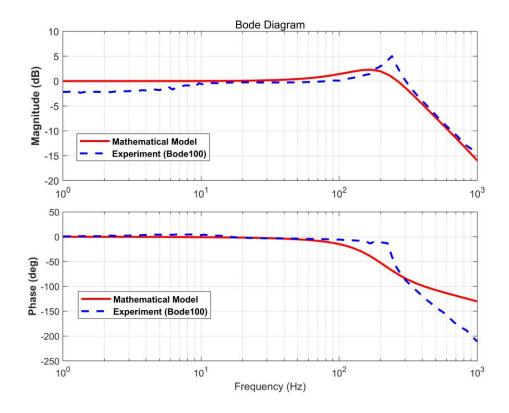

| Figure 3.19 Comparison of closed loop frequency response of voltage controller from                                   |

| mathematical model, simulation and experiment                                                                         |

| Figure 4.1 Resistor divider network in PHIL with ITM interface                                                        |

| Figure 4.2 Control block representation of a resistor divider network in PHIL 57                                      |

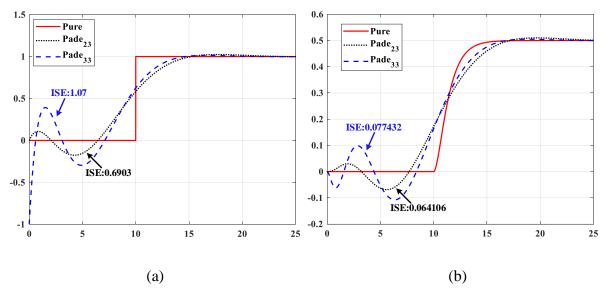

| Figure 4.3 Step response of PD for (a) Pure delay & (b) Second order TF with Pure delay 59                            |

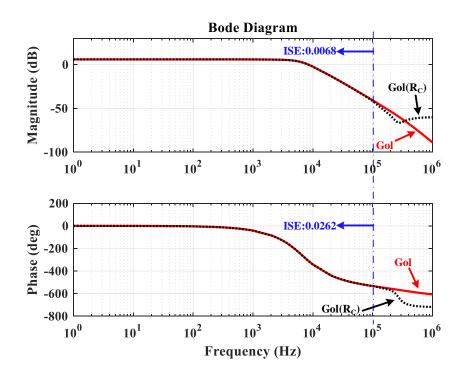

| Figure 4.4 Accuracy evaluation of interface with current source resistor                                              |

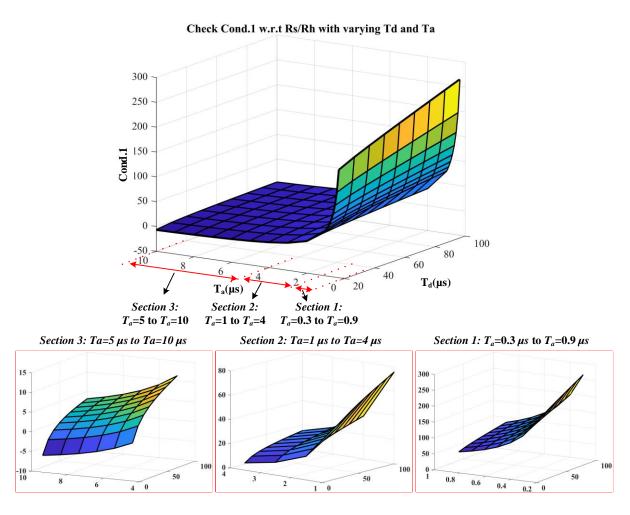

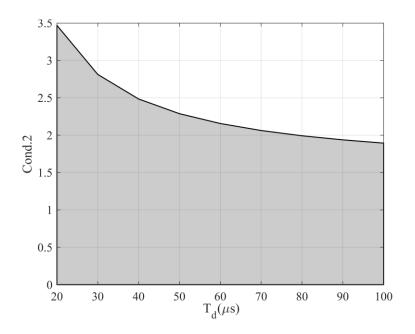

| Figure 4.5 Graphical representation of $Cond.1$ for varying $T_d$ and $T_a$                                           |

| Figure 4.6 Area under the plot showing region satisfying <i>Cond.</i> 2                                               |

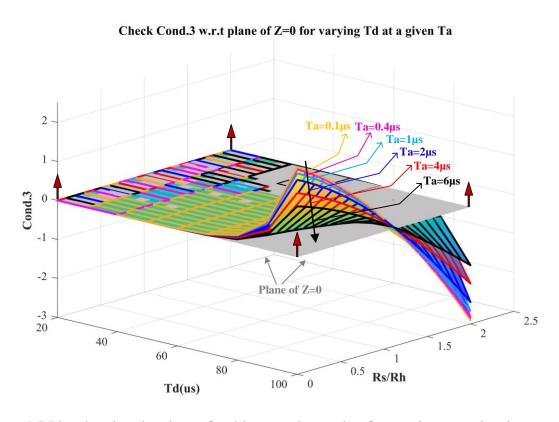

| Figure 4.7 Plot showing the plane of stable operating region for varying $T_d$ and resistance ratio.                  |

|                                                                                                                       |

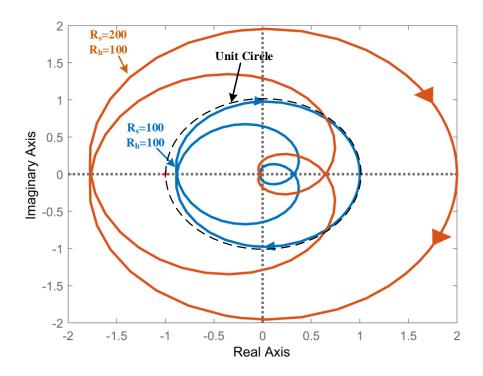

| Figure 4.8 Nyquist stability test for a system of resistor divider                                                    |

| Figure 4.9 Output impedance measurement of a micro inverter (a) testing setup (b) inverter                            |

| connection scheme. 71                                                                                                 |

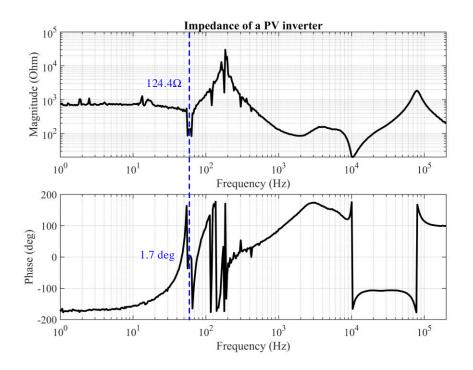

| Figure 4.10 Experimental determination of output impedance of an inverter                                             |

| Figure 4.11 PHIL Implementation with resistor divider network                           | 73        |

|-----------------------------------------------------------------------------------------|-----------|

| Figure 4.12 Compensator design to eliminate the delay due to filter.                    | 74        |

| Figure 4.13 Resistor divider measurement ( $R_s/R_h=1$ ) at (a) hardware node (b) softw | are node. |

|                                                                                         | 75        |

| Figure 4.14 Comparison of results with and without employing the compensator            | 76        |

| Figure 4.15 Measurements for varying $R_s/R_h$ .                                        | 77        |

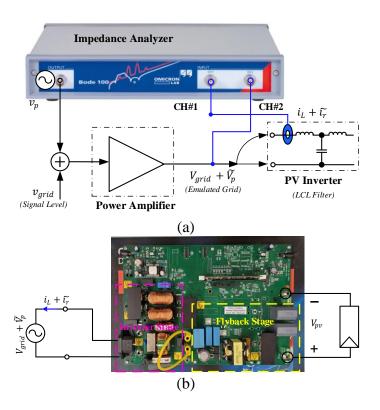

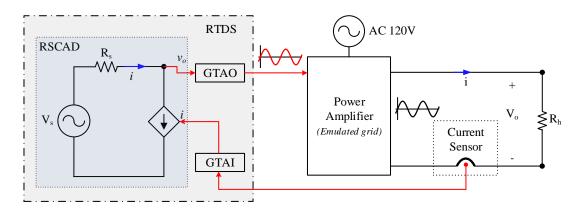

| Figure 4.16 PHIL arrangement for evaluating a grid connected PV inverter                | 78        |

| Figure 4.17 PHIL test bed for PV inverter evaluation.                                   | 80        |

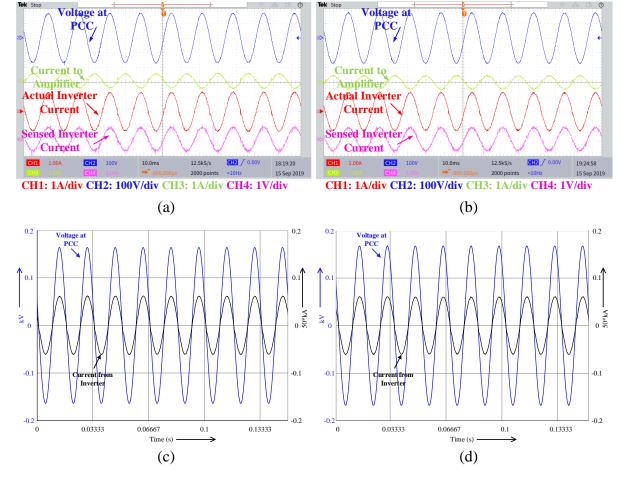

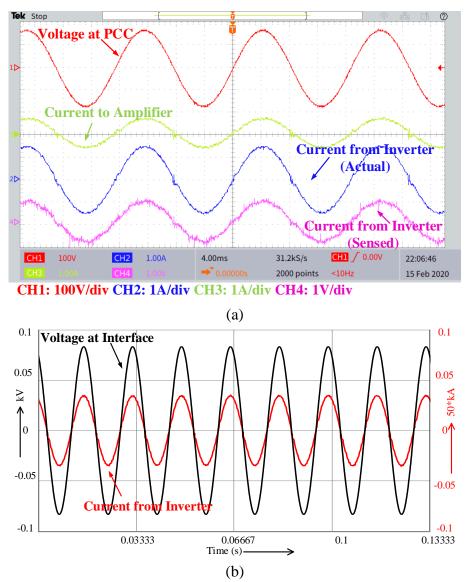

| Figure 4.18 Steady-state results of PV inverter with (a) SG-hardware measurements       | (b) WG-   |

| hardware measurements (c) SG-software measurements and (d) WG-software measurements     | irements. |

|                                                                                         | 81        |

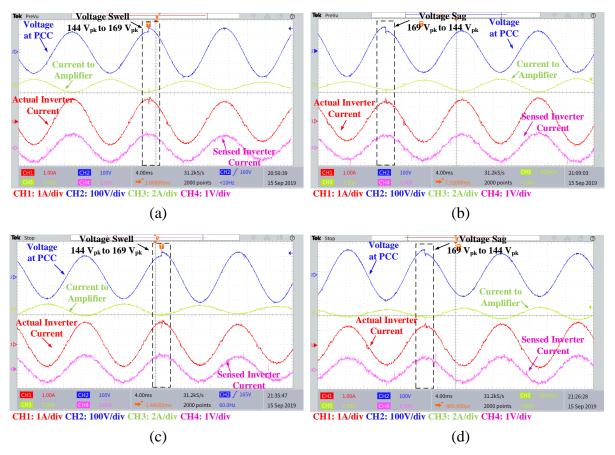

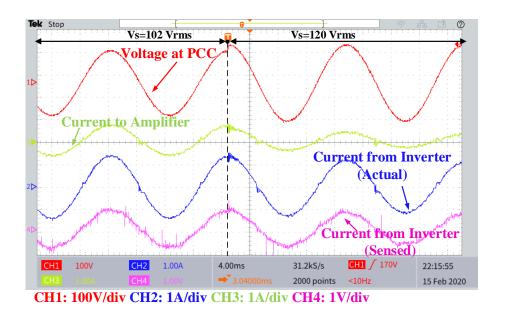

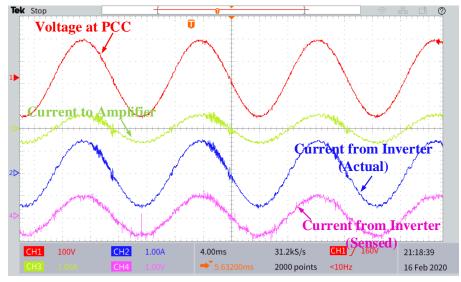

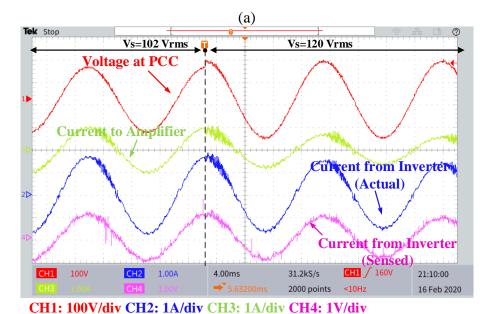

| Figure 4.19 Transient performance of PV inverter with PHIL under (a) SG-voltage         | swell (b) |

| SG-voltage sag (c) WG-voltage swell (d) WG-voltage sag                                  | 83        |

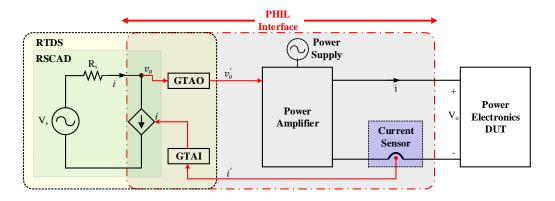

| Figure 5.1 An ITM configuration for evaluating a PE DUT.                                | 89        |

| Figure 5.2 Functional block of an AI card.                                              | 89        |

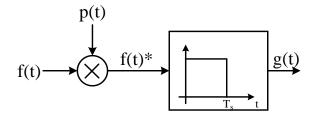

| Figure 5.3 Mathematical representation of a ZOH.                                        | 91        |

| Figure 5.4 Hardware setup for frequency response extraction of AO-AI card               | 95        |

| Figure 5.5 Hardware Setup for delay estimation of AO-AI card                            | 95        |

| Figure 5.6 Hardware setup for frequency response extraction of linear amplifier         | 96        |

| Figure 5.7 Hardware Setup for delay estimation of linear amplifier.                     | 97        |

| Figure 5.8 Hardware setup for frequency response extraction of linear amplifier-AO      | -AI card. |

|                                                                                         | 98        |

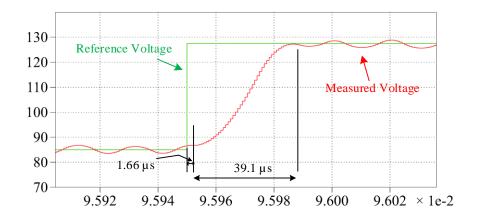

| Figure 5.9 Delay measurement from AI to AO for a time step of 50 us                     | 99        |

| Figure 5.10 AO-AI frequency response for a time step of (a) 20 $\mu$ s (b) 50 $\mu$ s                  | 100      |

|--------------------------------------------------------------------------------------------------------|----------|

| Figure 5.11 Delay measurement of a Linear amplifier.                                                   | 102      |

| Figure 5.12 Frequency response of a linear amplifier for developed model and exper                     | iment.   |

|                                                                                                        | 103      |

| Figure 5.13 Frequency responses of modelled, calculated and measured AO-AI-an                          | nplifier |

| combination                                                                                            | 104      |

| Figure 5.14 PHIL arrangement of a resistor divider network.                                            | 106      |

| Figure 5.15 Control block representation of a PHIL resistor divider network                            | 106      |

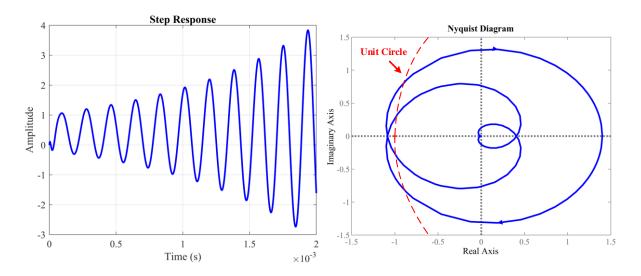

| Figure 5.16 A response of an uncompensated PHIL network.                                               | 107      |

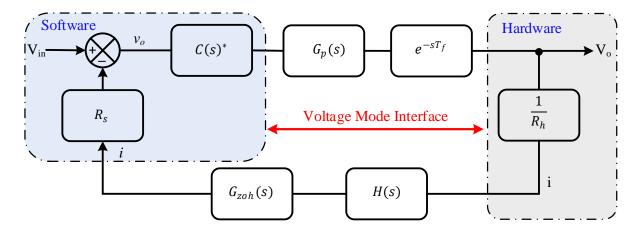

| Figure 5.17 Architecture of a compensated PHIL network.                                                | 108      |

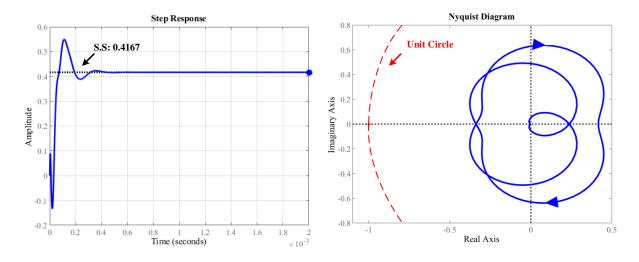

| Figure 5.18 Response of a PHIL network with compensator.                                               | 109      |

| Figure 5.19 Uncompensated PHIL result for varying resistances ratio.                                   | 111      |

| Figure 5.20 Compensated PHIL result (a) for $R_s/R_h=1.4$ (b) for increasing $R_s/R_h=1.4$             | 112      |

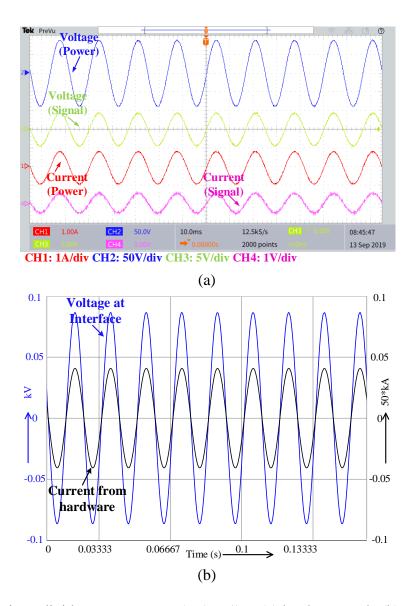

| Figure 5.21 Experimental setup for PV inverter evaluation in PHIL.                                     | 113      |

| Figure 5.22 PV inverter steady-state results with SG (a) measurement at actual inverted                | er PCC   |

| (b) measurement at software node.                                                                      | 114      |

| Figure 5.23 PV inverter during voltage swell with SG                                                   | 115      |

| Figure 5.24 PV inverter with WG (a) steady-state (b) transient.                                        | 116      |

| Figure 6.1 A typical full-bridge VSI                                                                   | 121      |

| Figure 6.2 Unipolar switching scheme pattern with uniform switching                                    | 125      |

| Figure 6.3 Architecture of a BC employed VSI.                                                          | 127      |

| Figure 6.4 Steady state waveforms for (a) Mode I: V <sub>ref</sub> >0 (b) Mode II: V <sub>ref</sub> <0 | 128      |

| Figure 6.5 State-Plane representation of inherent trajectories along with switching surface.                             |

|--------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                          |

| Figure 6.6 Controller operational sequence.                                                                              |

| Figure 6.7 Finite State Machine for trajectory movements [111]                                                           |

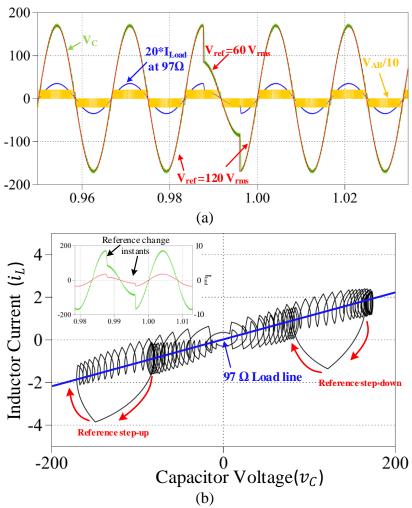

| Figure 6.8 Simulation showing performance during load transients (a) time-domain plot (b)                                |

| state-plane plot                                                                                                         |

| Figure 6.9 Simulation showing performance during reference transients (a) time-domain plot                               |

| (b) state-plane plot                                                                                                     |

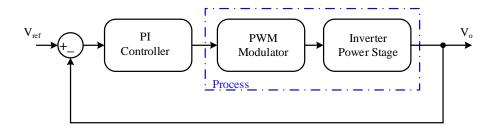

| Figure 6.10 Output voltage control with a directly implemented PI                                                        |

| Figure 6.11 Output voltage control with a reference frame transform PI                                                   |

| Figure 6.12 Steady-state operation of BC based VSI for (a) No-Load, (b) 250 W linear load,                               |

| (c) 550 VA inductive load, and (d) 100 W non-linear load                                                                 |

| Figure 6.13 System performance during load transients: (a) $97\Omega$ to $57\Omega$ , and (b) $57\Omega$ to $97\Omega$ . |

|                                                                                                                          |

| Figure 6.14 System performance during reference transients: (a) 120 $V_{rms}$ to 24 $V_{rms}$ , and (b)                  |

| 24 V <sub>rms</sub> to 120 V <sub>rms</sub>                                                                              |

| Figure 6.15 System performance with non-linear load: (a) load transient, and (b) reference                               |

| transient. 150                                                                                                           |

| Figure 6.16 System performance with PI controller: (a) steady state, (b) load change and (c)                             |

| reference change. 151                                                                                                    |

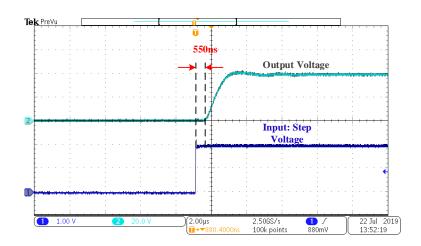

| Figure 6.17 Step response of a switched-mode amplifier                                                                   |

# Nomenclature

## List of Symbols

| $i_{pv}$                   | Photovoltaic current                                       |

|----------------------------|------------------------------------------------------------|

| $v_{pv}$                   | Photovoltaic voltage                                       |

| $I_{mpp}$                  | Current at maximum power point of a photovoltaic source    |

| $V_{mpp}$                  | Voltage at maximum power point of a photovoltaic source    |

| $R_{mpp}$                  | Resistance at maximum power point of a photovoltaic source |

| $I_o$                      | Saturation current of a photovoltaic source                |

| $V_t$                      | Thermal voltage of a photovoltaic array                    |

| $N_{\scriptscriptstyle S}$ | Number of cells in series of a photovoltaic array          |

| $R_{\mathcal{S}}$          | Equivalent series resistance in a single diode model       |

| $R_p$                      | Equivalent parallel resistance in a single diode model     |

| а                          | Diode ideality constant                                    |

| L                          | Inductance of a converter                                  |

| С                          | Capacitance of a converter                                 |

| R                          | Load resistance of a converter                             |

| $r_L$                      | Parasitic resistance of an inductor                        |

| $r_C$                      | Parasitic resistance of a capacitor                        |

$v_{dc}$  DC link voltage representing the DC bus

$v_C$  Voltage across a capacitor

$i_L$  Current through an inductor

$i_{LB}$  Boundary current between CCM and DCM mode

$f_{sw}$  Switching frequency of a converter

Duty cycle of a converter

$V_s$  Input voltage at the software end

$R_s$  Resistance at the software end

$R_h$  Resistance at the hardware end

$R_C$  Resistance in parallel to a current source

$K_1$  Software gain

$K_2$ , A Amplifier gain

T<sub>2</sub> Amplifier input output delay

$T_a, T_{amp}$  Amplifier bandwidth

$T_f, T_{aaf}$  Anti-aliasing filter cut-off

$T_s$ ,  $T_d$  Time step delay

$T_{lpf}$  Low pass filter cut-off of an analogue input card

$T_{comp}$  Time constant of a compensator

$G_{aaf}$  Gain of an anti-aliasing filter

$v_{ref}$  Reference voltage to a controller

D Hysteresis voltage band

#### **List of Abbreviations**

PHIL Power Hardware in the Loop

PE Power Electronic

PV Photovoltaic

FC Fuel Cell

DUT Device Under Test

CHIL Controller Hardware in the Loop

PCS Power Conversion Stage

RTS Real Time Simulator

AI Analogue Input

AO Analogue Output

GCPI Grid Connected Photovoltaic Inverter

RTDS Real Time Digital Simulator

INC Incremental Conductance

MPPT Maximum Power Point Tracking

ITM Ideal Transformer Method

SP Smith Predictor

VSI Voltage Source Inverter

HIL Hardware in the Loop

ABS Automatic Braking System

TCS Traction Control System

V2G Vehicle to Grid

DSP Digital Signal Processors

IA Interface Algorithms

PCD Partial Circuit Duplication

DIM Damping Impedance Method

DAC Digital to Analogue Converter

ADC Analogue to Digital Converter

PA Power Amplifier

TF Transfer Function

PD Padé Approximations

PCC Point of Common Coupling

GPA Gain Phase Analyzer

MPP Maximum Power Point

PI Proportional Integral

SD Single Diode

CCM Continuous Conduction Mode

PWM Pulse Width Modulator

CC Constant Current

CV Constant Voltage

DCM Discontinuous Conduction Mode

GTAO Giga-Transceiver Analogue Output

GTDI Giga-Transceiver Digital Input

ISR Interrupt Service Routine

AQ Action Qualifier

RH Routh-Hurwitz

SE Simulation Environment

ISE Integral Square Error

LHS Left Hand Side

SCR Short Circuit Ratio

WG Weak Grid

SG Strong Grid

PLL Phase Locked Loop

GTAI Giga-Transceiver Analogue Input

AAF Antialiasing Filter

ZOH Zero Order Hold

FB Full Bridge

BC Boundary Controller

SSS Second order Switching Surface

BSS Bipolar Switching Scheme

USS Unipolar Switching Scheme

FSM Finite State Machine

PR Proportional Resonant

THD Total Harmonic Distortion

FPGA Field Programmable Gate Arrays

## **Chapter 1**

## Introduction

## 1.1. Background

The technology of Power Hardware in the Loop (PHIL) is gaining interest in the recent years in industries as well as in academic research settings. The PHIL arrangement offers a variety of advantages in terms of flexibility, space requirement and time. This semi-physical simulation setup can emulate an actual-like environment to evaluate real power apparatuses. This type of testing platform provides a great degree of freedom while evaluating Power Electronic (PE) converters with renewable energy sources, such as solar or wind energy. One of the applications is, testing a Photovoltaic (PV) inverter connected to the grid under changing environmental conditions and performing various other grid interaction studies. This is just one application and PHIL platforms have been widely adopted to evaluate systems with real energy sources and energy storage elements to study the interactions between them [1], [2].

In industries, PHIL-based burn-in systems are used to evaluate the efficiency and stability of a power converter instead of using a real resistive load to dissipate the power supplied by the converter. Typically, these burn-in tests last for a couple of minutes to even several years. The PHIL-based approach can minimize the energy wasted in these tests by

power cycling the energy to air-conditioning systems needed to cool the testing setup. In order to enhance power process efficiency and enable full manual control of element characteristics, full power electronics PHIL platforms have been proposed. These platforms are common to use a PE based emulators instead of real energy sources and storage elements. One example is a Fuel Cell (FC) energy source. This requires a PE converter and a controller to emulate the electrical behaviors of the FC to have reactions with the connecting system [3], [4]. This benefits in significantly reducing the size of testing platform as well as providing a relatively safe testing environment. For the PHIL applications described above, it is a common practice to usually evaluate a single element, e.g. FC, single Device-Under-Test (DUT), or electronic ballasts, in the power loop.

#### 1.2. Motivation

PHIL may be described as a system consisting of a real-time software model interacting with a physical device through an interface for exchange of power between them. With this feature, PHIL stands out among real-time simulations for running a wide variety of tests ranging from evaluating power converters, performing various grid interaction studies, integration of renewables in microgrid to various source emulation applications. Unlike the existing real-time simulation where the entire system with controllers and power-networks are simulated in real-time, PHIL is an extension to these real-time simulations and existing Controller-Hardware-in-the-Loop (CHIL) simulations.

The increasing trend towards renewable based energy sources demand more system level investigations. The impact of integrating these sources at different power coupling point becomes important for system engineer to ensure stability as well as to aid in system planning.

Microgrids that integrate renewable energy sources are new approach for overcoming high operating costs for delivering power to remote communities and providing improved energy efficiency of electrical networks in modern buildings [5], [6]. However, most of research in this topic is at the computer simulation level or individually testing of a power apparatus in microgrid. These studies entail a wide technology gap between the reported research results and the realities of practical performance [7]-[9]. In order to achieve results more accurate to the practical system, it has been proposed to use a PHIL platform to evaluate microgrids with actual power flowing into the electrical networks and devices [10]-[16].

It is therefore not wrong to foresee the applications of PHIL in testing and evaluating renewable sourced devices growing. Also, when it comes to renewable based sources, it is imperative to use PE converters as the Power Conversion Stage (PCS) before the power can be delivered to the grid or in any other usable form. This is another high-potential application area of PHIL where a non-linear PE converter is involved. The use of these real PE hardware in testing is due to the complexities in accurately modelling all the non-linear dynamics of PE devices. The PHIL testing would particularly flourish in such environments as there is no more reliance on computer models rather an actual PE hardware.

#### 1.3. Statement of the Problem

The PHIL forms an attractive way for testing various linear devices as well as non-linear PE converters in laboratory scale and yet get a result that resembles an actual like scenario. This approach, however promising, suffers from various stability problems arising due to the interface between the hardware and software environment required to create a PHIL. The PHIL architecture comprises of a power apparatus (source or load) as a part of the system interfaced

with a Real Time Simulator (RTS) accompanying remainder of the sub-system. The intermediary medium to create the interaction between these two sub-systems are vital in achieving an actual like response.

The interface medium in PHIL basically consists of devices like, amplifier, Analogue Input (AI) card, Analogue Output (AO) card and sensor. This interface, therefore, naturally consists of an unavoidable delay from the fiber cables, input /output (I/O) cards, sensors, conditioning circuits, filters and amplifiers. While, ideally, it is desirable to have an infinite bandwidth interface with no delays but practically this cannot be achieved as the conversion time within the I/O cards, computation time required by the RTS and the response of the amplifier contributes to this delay and bandwidth restrictions. With this, it is therefore required that a comprehensive analysis of the stability of a PHIL system be performed. Also, from the standpoint of system performance, these interface devices in PHIL play a significant role in quantifying the stability as well as the accuracy. Moreover, the stability problems of PHIL have been intriguing to many researchers and the challenge remains to completely demystify the stability issues. The solution to this would demand a trade-off between robustness and accuracy.

To unravel the problem; the first major concern is the time delay of the loop and its effect on stability and the second challenge is to obtain an actual-like results with acceptable errors. As to consider the issue independently, the improvement areas are;

Changing the amplifier platform from linear to PE based (also termed as switched-mode amplifier). This allows performing PHIL test for high power applications as the size and cost of PE amplifiers reduces significantly with increasing power level compared to linear amplifiers. However, the limitation of PE based power amplifier in terms of achieving a fast-dynamic response for PHIL application should first be addressed.

- The I/O cards require a considerable amount of time to perform analogue to digital conversion and digital to analogue conversion. The solution to this is more restricted towards the RTS manufacturer rather than on the user end.

- To deal with the stability problems in algorithm level. This requires the need for detailed investigation of the interface and accordingly design compensators that can eliminate the instability due to delays as well as improve accuracies.

#### 1.4. Thesis Statement

While the application of PHIL for evaluating power electronic DUTs is gaining popularity, the stability concerns associated with the delay in the interface is lacking a thorough investigation. The studies currently present cannot provide answers to all the factors affecting instability and therefore requires an in-depth study. The effect of delay in the closed loop response of PHIL can be eliminated by integrating a Smith Predictor compensator with the PHIL loop which consequently aids in stability as well.

## 1.5. Thesis Objectives and Research Contributions

The objective of this thesis is to investigate the stability issues in PHIL and develop a mathematical and analytical framework along with future recommendations for interface amplifier. Since PHIL is an application-oriented architecture, all the theoretical formulations and analysis in this thesis are verified experimentally. A Grid-Connected PV Inverter (GCPI)

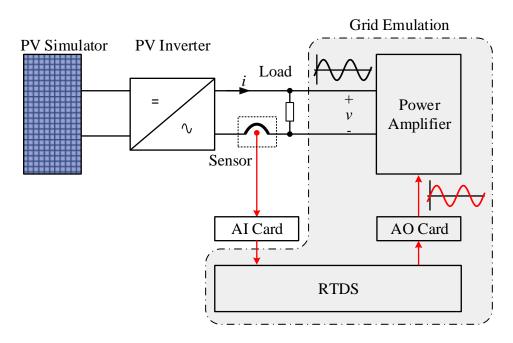

is chosen as the non-linear power electronic DUT to demonstrate the operation of a stable PHIL. The arrangement of GCPI in a PHIL is shown in Figure 1.1. The outcomes from this work can directly benefit any industrial / academic research or test application in the field of PHIL.

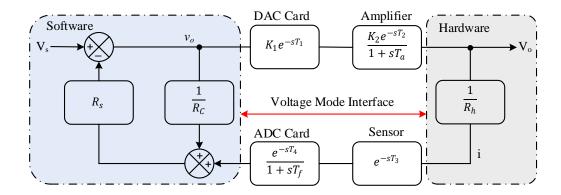

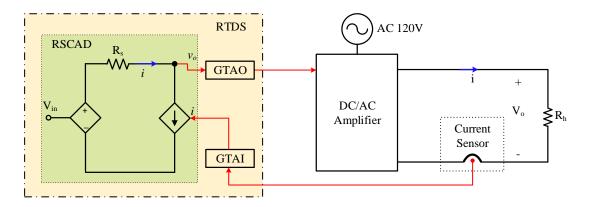

Figure 1.1 A PHIL test setup for a grid-connected PV inverter.

To explicitly detail the research objective, each component in Figure 1.1 needs to be studied individually to understand the research questions and the analysis follows accordingly. The main contribution and research objectives of this work is divided into following themes;

To familiarize with the RTS device (Real Time Digital Simulator (RTDS)) and its interface: - a CHIL approach is used to study the performance of a PV module with its corresponding controllers. This includes the development of small-signal model of PV module and Incremental Conductance (INC) based Maximum Power Point Tracking

- (MPPT) algorithm. The developed mathematical model is verified with experimental results obtained from RTDS by the means of frequency response plots. The contribution of this work includes the comprehensive model development and experimental verification with CHIL approach.

- Stability evaluation of PHIL loop: This study includes the development of a set of mathematical inequalities that defines the boundary of stability in a PHIL, considering the existing model of interface. The contribution in this work is quantifying the stability criteria in terms of interface device parameters, DUT and delay time.

- O PHIL interface device characterization and interface model development: The characterization includes development of each interface device model and experimentally verifying it using frequency response approach. The potential research contribution in this work is the experimental validation of developed model which has not been reported in existing literatures.

- Designing a compensator to overcome delay response in a PHIL: this work includes

designing a compensation block which eliminates the effect of time delay in the closed

response to achieve a robust PHIL operation. The contribution from this work is the

application of Smith Predictor compensator in a PHIL setup.

- O Design, implementation and demonstration of an interface switched-mode amplifier: The interface amplifier which is a critical component of a PHIL architecture needs to be designed to have a fast-dynamic response, especially for a switched-mode amplifier which is an obvious choice for applications requiring high power testing. This work includes the application of boundary controller to design and experimentally verify a fast-dynamic switched-mode power amplifier even while operating at low switching

frequency. This work could contribute in establishing a benchmark for future PE amplifier for PHIL applications.

#### 1.6. Thesis Organization

The content of this thesis comprises of material published/under-review in IEEE conferences and journals organized to form majority of the chapters within this thesis. In total, this thesis contains seven chapters structured in following ways;

Chapter 1 introduced various applications of PHIL in industries as well as in academic research environment along with the motivation behind this work. The problems with PHIL setup are also discussed in great lengths along with research objectives to address few of these problems.

Chapter 2 reviews the integral components comprising the PHIL architecture. This includes, interface algorithms, amplifiers, delay models, delay compensation methods and a brief section of existing studies in PHIL. Also, existing literatures on a PV source connected to the grid is summarized in the same chapter.

Chapter 3 presents the development of a linear model of PV along with its related controller. The CHIL approach is applied to verify the developed model. The details on small-signal modelling and experimental validations are also discussed in this chapter.

Chapter 4 works to develop a mathematical framework to describe the stability of a PHIL loop. The evaluation of a PV inverter in a stable PHIL loop is also demonstrated in this chapter with adequate experimental results.

Chapter 5 presents the characterization of the Ideal Transformer Method (ITM) interface in a PHIL and develops the individual model of interface devices. The experimental validation

of the model also forms the part of Chapter 5. Additionally, Chapter 5 discusses the design methodology of a Smith Predictor (SP) compensator followed by the application of SP compensator in PHIL along with the experimental results which also makes the content of this chapter.

Chapter 6 includes the design and implementation of a single-phase Voltage Source Inverter (VSI) with a second order switching surface-based controller. This VSI forms the basis of a switched-mode amplifier in a PHIL. This chapter shows the experimental validations of the VSI-based switched amplifier at various operating conditions.

Chapter 7 concludes this thesis by discussing briefly the research objectives achieved and presenting the possibility of extending this research work.

Finally, the references followed during the course of this research is listed with numbers representing the cross-referencing location pointing the corresponding text in this thesis.

## Chapter 2

## Literature Review on Components of a PHIL

### 2.1. A Brief History

The history of Hardware-in-the-Loop (HIL) simulations dates back to as early as 1930s, where it was used in the aircraft industry for flight simulators [17]. Over the years, with the growing computational power of the microprocessors the real-time simulations opened its way. With this, the application of HIL simulations progressed rapidly. The major application included testing missile guiding system by NASA [18]. Later, the automobile industry adopted the HIL simulations to design Automatic Braking System (ABS) and Traction Control System (TCS) to name a few [17]. The electric power and robotic sector also could not remain untouched by it [18]. A brief description of various applications and extensions of HIL in electric power research areas and industries are discussed in [19]. This include, CHIL for designing and testing a control hardware (including the controller) without the need to operate an actual power stage hardware (simulated in real-time), PHIL for testing the part of real hardware along with its controller in actual simulated environment, and other variants being PHIL with thermal HIL for designing an air conditioning system for buildings.

Recently with the increasing penetration of renewable sources in the grid, the PCS with non-linear PE converter poses a new challenge for this integration. This requires a thorough analysis of the renewable hardware in an actual-like setting to be able to test the engineering elements as well as to foresee the risks involved during implementations. This has been one of the major areas where PHIL applications have been mainly applied, typically, in micro-grids with distributed generations. Besides, the upward trend in electric vehicle market also demands a detailed investigation in the technologies like Vehicle to Grid (V2G) where the energy stored in the batteries are utilized by the grid in smoothing the load profile during peak periods [20]. The evaluation of V2G technology with PHIL is also an active research area [21]-[23]. From this, it can only be predicted the evolution of HIL in every aspect starting from engineering design to ensuring the system operation in a projected manner.

Given the flexibility and demand of PHIL testing in industry and academia, it is important to understand the existing state-of-the-art in the field. The subsequent sections present a brief overview of the key elements that forms a PHIL study platform.

#### 2.2. Real Time Simulators

Real-time simulations have been in use for many years now. Down the time, many different types of RTS have been developed. One of the pioneers in the field of simulator development include RTDS Technologies Inc, who started their commercial RTS in 1991 with Digital Signal Processors (DSP). Following this, by 1996 other companies like Électricité de France, SIEMENS and OPAL-RT developed their simulators too [24]. Currently, the number of RTS are growing, notable mentions being; RTDS, OPAL-RT, dSPACE, Typhoon and RTBOX. These RTS are grouped under variety of functionality, hardware architecture,

modelling and solution algorithm to name a few. The detailed comparison of various RTS including the characteristics of hardware and software is presented in [24]. Further, Lauss et al. [25] presents the potential applications of currently existing digital RTS for PHIL studies. It is important to quantify the time-step whenever real-time simulation is discussed. It has been suggested that "50µs" would provide a good enough resolution to study the transients of a 50/60 Hz power system network [24], [25]. However, when it comes to studying high frequency PEs devices the time step must be lowered considerably [24], [25]. Also, multi-rate simulation is a feasible alternative to represent interfacing of PE devices with 50/60 Hz power system network. With the development of such high computational capability RTS, the simulation studies have been revolutionized. The conventional non-real-time simulation are easily replaceable to perform real-time simulation studies and can also be extended to perform CHIL and PHIL simulations.

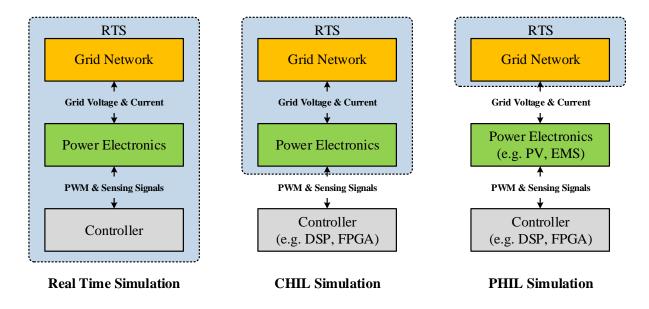

Figure 2.1 A comparison of various simulation platforms.

The functional difference between three simulation platforms for the case of PE converter exchanging power with the grid is shown in Figure 2.1. As mentioned in Faruque et al. [24], CHIL simulation consists of a physical controller generating switching signals for controlling PE converter simulated inside the RTS. The entire system including the controller is run in RTS for a real-time simulation of the similar system. Moreover, if a part of power exchange point is decoupled between RTS and physical hardware (Grid and PE Converter in Figure 2.1.) to have a virtual exchange of power, such type of simulation technique has been termed as PHIL by the literatures [24]-[27]. To achieve virtual power exchange between RTS and physical system, design of proper interface is imperative.

### 2.3. Interface Algorithms

The interface in PHIL is the one that differentiates it from its actual counterpart. Therefore, the arrangement of devices in interface for exchange of power affects the performance of the PHIL-based system. Based on applications and performance requirements, interface devices can be arranged to create a PHIL. These arrangements of devices to form interface is termed what is called an Interface Algorithms (IA). There are several IA proposed in the literatures based on their performance parameters like, implementation ease, stability margin and accuracy [26], [28], [29].

It is well reported that IA like Ideal Transformer Method (ITM) offers advantages in ease of implementation and accuracy but often suffers from stability problems [26], [29]. Another IA called Partial Circuit Duplication (PCD) that requires a linking impedance duplicated in software and hardware has an improved stability than ITM but at the expense of lower accuracy [25], [26], [29], [30]. Besides, this inclusion of hardware impedance is not desirable for high

power applications. The IA which offers considerable balance between accuracy and stability is Damping Impedance Method (DIM) but the implementation complexities with DIM is relatively higher [25]. DIM is created as a result of combining the advantages of both ITM and PCD. Other notable mentions of IA include time variant first order approximation and transmission line model [26]. These IAs due to their higher limitations in implementations are not widely used for PHIL applications.

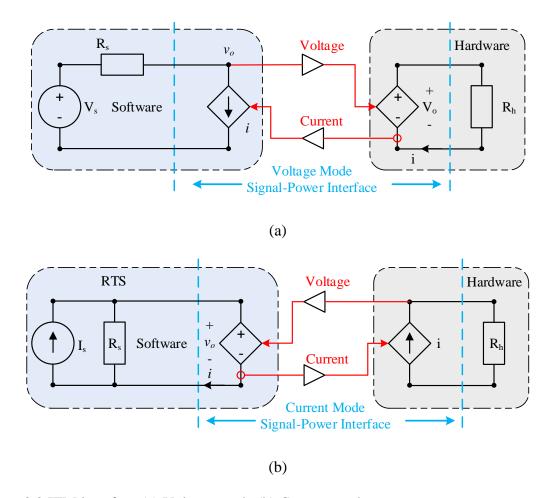

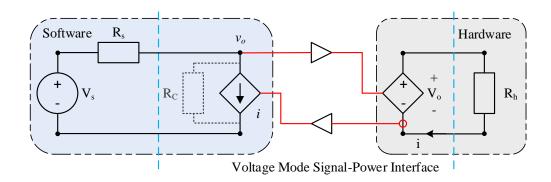

Figure 2.2 ITM interface (a) Voltage mode (b) Current mode.

The IAs, in general, are classified into two types; voltage and current, based on the type of signal interfaced [25], [30]. Figure 2.2 shows such arrangements of an ITM interface with

voltage mode and current mode signal exchanges. In voltage mode interface, Figure 2.2 (a), voltage from RTS is sent out through output Digital to Analogue Converter (DAC) card in signal level which is then amplified using voltage amplifier before its connected to DUT. The current drawn by DUT is sensed and fed back to RTS through its input Analogue to Digital Converter (ADC) card. With similar arrangement, by sending out the current and feeding back the voltage in the interface, current mode interface shown in Figure 2.2 (b) can be configured. Due to the advantages of ITM, it has become a common method to conduct PHIL studies. Similarly, this research work considers ITM interface for evaluating the stability of PHIL.

## 2.4. Power Amplifier

Power Amplifier (PA) is one of the crucial devices in the interface of a PHIL architecture. For a real system represented by PHIL, interface devices are mandatory but ideally are expected to have a unity gain with infinite bandwidth. Same applies for PA whose performance characteristics are based on factors like bandwidth, rise time, power level, slew rate and operating regions. Given these parameter dependencies, it is practically not possible to achieve unity gain and infinite bandwidth PA. A comprehensive analysis on the application of three types of PA, viz., switched-mode, generator type and linear amplifier used for PHIL simulations is presented in [31]. Each of these types of PA have their own advantages and applications in a PHIL interface and therefore there is no one clear winner. As described in Lauss et al. [25], Ren et al. [31] and Lehfuss et al. [32], switched-mode PA are flexible in terms of their use as a voltage or current amplifier and are easy to design and implement even for megawatts power range. However, switched-mode PA suffers from a drawback of low bandwidth and slower response time compared to linear amplifiers [25], [31]. Linear amplifiers

are ideal for low power applications, but their size, weight, and cost go up considerably for high power applications [25]. Similarly, generator type amplifier is ideal for system requiring three-phase balanced supplies such as testing a microgrid [13], [25], [31].

## 2.5. Time Delay

The time delay in PHIL is the result of interface devices cascaded to form the power exchange medium. Additionally, the time-step required to solve a simulation by digital RTS also contributes to this time delay. Ideally, it is desirable to have a system without any delays. Moreover, with the digital RTS running at a certain time-step, even if the interface is designed to have no delays the unavoidable time-step delay is inherently present within. This calls for characterizing the delays in each interface devices before incorporating it in any studies related to PHIL simulation. It also becomes essential to be able to represent the delays with their corresponding mathematical expression to enable better understanding of its effect on system performance.

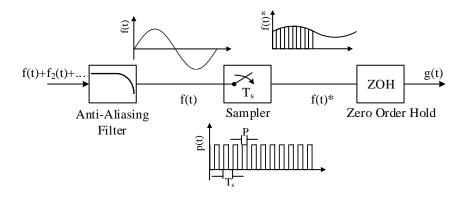

A time dependent function f(t) with a time delay  $T_d$  when exposed to a unit step input can be represented as  $f(t-T_d)$ . Taking Laplace transform, it can be expressed in frequency domain by  $s=j\omega$  where  $\omega$  represents the angular frequency.

$$f(t - T_d) \xrightarrow{\mathcal{L}} F(s) \cdot e^{-sT_d}$$

(2.1)

The exponential function in (2.1) if plotted in frequency domain using bode plot would represent a constant magnitude with infinitely growing phase. This infinite phase lag in time delay results in non-rational Transfer Function (TF) and mathematically be seen as a system with infinite dimension state vector which makes it difficult to control and analyze [33]. In order to avoid such situation, it is a general practice to rationalize the exponential TF of time

delay using Taylor, and Padé approximations (PD) [34], [35]. The comparison of Taylor series with PD for delay is presented in [35]. It is seen that Taylor series has a larger error compared to PD when approximating a pure time delay. Also, Hanta and Prochazka [35] proposes that accuracy of PD increases if the order of numerator is made less than the denominator. The comparison between different degrees of PD have been further presented in [34]. It is seen that, rational approximation of delay using Padé has the highest accuracy when the order of numerator is one less than the denominator.

Rational approximation of time delay using PD results in a polynomial equation in numerator and denominator. If  $R_{m,n}(sT_d)$  is the rational approximation of  $e^{-sT_d}$  of order (m,n) where m and n are positive integers then PD can be expressed by (2.2) [34];

$$e^{-sT_d} \xrightarrow{Pade} R_{m,n}(sT_d) = \frac{P_m(sT_d)}{Q_n(sT_d)}$$

(2.2)

Where,

$$P_m(T_d) = \sum_{k=0}^{m} \frac{(m+n-k)! \, m!}{(m+n)! \, k! \, (m-k)!} (-sT_d)^k$$

and,

$$Q_n(T_d) = \sum_{k=0}^{n} \frac{(m+n-k)! \, n!}{(m+n)! \, k! \, (n-k)!} (-sT_d)^k$$

With (2.2), delay can be represented by rational function which is more comfortable to handle than the exponential function. However, this approximation remains valid only for a certain frequency range. This is because the phase lag from a rational function is bounded unlike the infinite phase of pure delay and the error in phase increases beyond the frequency band [33].

## 2.6. Delay Compensation Techniques

The delay in the interface directly affects the performance of the PHIL. Studies have suggested that the stability margin reduces with the increasing delay of the PHIL interface [36], [37]. Similarly, it is also obvious that the accuracy of the PHIL is greatly reduced with the delays [37]. Therefore, it is apparent that the effect of these delays be eliminated or compensated if an accurate and a stable PHIL is desired. One of the feasible solutions to eliminate the effect of delay in PHIL is to compensate for this delay in the result. A compensation method that takes care of the phase delay introduced by the time delay is proposed in [36]. This compensation method used high pass filter to provide the additional phase. Another method to compensate for the effect of time delay is to add a phase advance to the fundamental and harmonic component obtained after Fourier analysis of original signal in RTS [28]. The original signal is then recreated from the phase advanced signal and amplified to take care of time delay in the PHIL loop. However, this method suffers from a lot of limitation like number of harmonics order, time to solve the Fourier by RTS, and power angle of DUT and software node. Another work by Marks, Kong and Birt [37] considers the entire PHIL loop like a classical control block and introduces a pole-zero compensator that deals with any inaccuracies within certain frequency range. This also improves the stability of a PHIL loop; specially for DIM interface.

Time delay compensation has been popular in process control systems where the time delay originates from the sluggish nature of plant. This delay in system to respond to any control actions has led system to run towards instability. This has been a trivial problem for researchers for decades and numerous solutions to overcome the effect of time delay have been proposed. One among many solutions was proposed by Smith [38] which eliminates the delay

effect in the closed loop response by inserting a feedback loop in the original system termed as Smith Predictor (SP) [39], [40]. Another advantage of SP is that it can be incorporated with the system with existing controllers [41], [42]. This makes SP an ideal application for PHIL to eliminate delay in its closed loop response and incorporating compensators as in [37] to improve the stability. However, such application of SP in PHIL has not been reported in the literature so far and therefore makes the study of this research work.

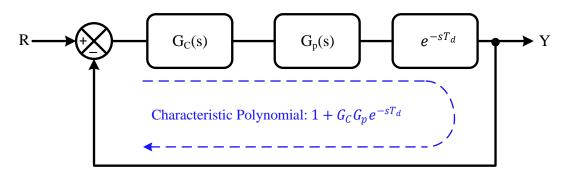

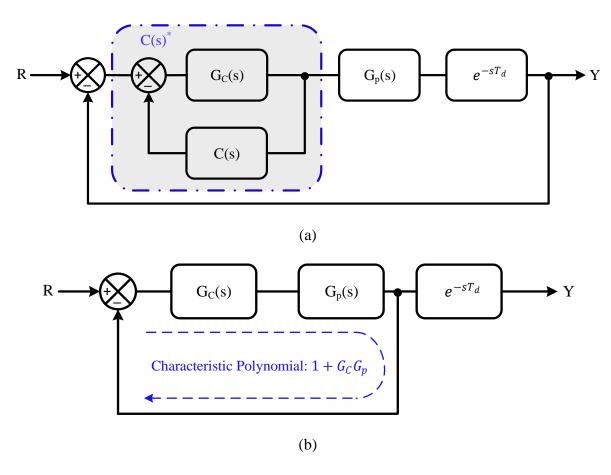

Figure 2.3 Control of a plant with delay.

A standard block representing a delay inherited plant  $G_p$  controlled by a controller  $G_C$  is shown in Figure 2.3. The closed loop response of such delayed plant with a standard controller would contain the delay term with infinitely growing phase. This makes the system difficult to achieve the set design criteria and controller design becomes extremely difficult. However, if the delay term in the forward path is pushed after the feedback node, the closed loop response of the resulting system would no longer contain the delay term. To achieve this objective, a SP based compensator can be designed.

Following up with the control block in Figure 2.3, the SP employed block with compensator C(s) and the expected equivalent block is presented in Figure 2.4. The input to

output closed loop TF from Figure 2.4 (a) and Figure 2.4 (b) can be derived and equated to obtain the compensator TF C(s).

From Figure 2.4 (a),

$$\frac{Y(s)}{R(s)} = \frac{G_p(s)C(s)^* e^{-sT} d}{1 + G_p(s)C(s)^* e^{-sT} d}$$

(2.3)

Where,  $C(s)^*$  is the combined controller and compensator TF. Similarly, from Figure 2.4 (b), the equivalent closed loop response that is expected by employing a SP can be obtained and is given by (2.4).

$$\frac{Y(s)}{R(s)} = \frac{G_p(s)G_c(s)}{1 + G_p(s)G_c(s)} e^{-sT_d}$$

(2.4)

Figure 2.4 Control of a plant with delay (a) SP employed block (b) equivalent block [40].

Equating the closed loop TF of (2.3) and (2.4), the TF of  $C(s)^*$  can be obtained;

$$C(s)^* = \frac{G_c(s)}{1 + G_c(s)G_p(s)(1 - e^{-sT}d)}$$

(2.5)

Also, referring to block in Figure 2.4 (a),  $C(s)^*$  can be derived;

$$C(s)^* = \frac{G_c(s)}{1 + G_c(s)C(s)}$$

(2.6)

The expression for SP compensator shown as C(s) in Figure 2.4 (a) can be obtained by comparing (2.5) and (2.6);

$$C(s) = G_n(s)(1 - e^{-sT_d})$$

(2.7)

Equation (2.7) gives the model of compensator to be employed in the forward path along with existing controller to achieve a delay free response. Moreover, an important observation from (2.7) is that it requires the model of plant and delay. When such compensator is realized for a system consisting of delays like the PHIL, it becomes critical that each device in the PHIL loop is modelled accurately.

#### 2.7. A Grid Connected PV Source

The use of PV source as a backup supply for supporting the main power units as well as in emergency facilities has been popular over the years [43]. In addition, PV systems being renewable source are preferred in standalone and grid-connected configurations. Each PV application demands different implementation schemes. Grid connected PV systems require either a centralized inverter or multiple inverters for power transfer. This can be achieved through single or two stages. Each of these schemes have their own pros and cons [44]. The single stage topology in which a centralized inverter is responsible for MPPT, grid current control and voltage amplification is simple and cost effective but has potential drawbacks [45].

The reduced tracking efficiency during partial shading due to centralized MPPT, losses due to module mismatch, and derating result in low power output. There are other schemes where a string of PV modules interfaced with a string inverter has higher tracking efficiency as compared with the centralized inverter configuration due to localized MPPT in individual strings. Few other single stage topologies require the PV voltage to be higher or equal to the peak of grid voltage and hence offer lesser flexibility [44]. Considering the limitations of single stage topologies, dual stage PV energy conversion techniques were introduced to obtain better flexibility in terms of mass production and higher efficiency in the energy conversion process [46]. In these topologies, each PV module or string is connected with a DC-DC converter stage that is interfaced with a DC link of a common inverter stage. While each DC-DC converter is responsible for MPPT, the DC-AC inverter takes care of the grid current and DC bus voltage control [47]. A better control is achieved on individual PV strings by implementation of distributed level energy converters, which sometimes are also referred as DC power optimizers. This approach overcomes the shortcomings of the central inverters in terms of energy harvesting efficiency, reliability as well as flexibility in operation and future enlargements.

Integrating PV power to AC or DC grid requires a converter in between. The advantages of these converters are MPPT and power factor correction to name a few. However, the interaction of these converters with the grid raises a concern for stability issues. The PHIL study with the PV inverter to estimate the grid impedance is presented in [48]. This estimation technique allows to study the effect of connecting the converter to an emulated grid with time varying grid impedance, especially in a PHIL setup. Similar other studies have been carried out with PV source to evaluate the performance in PHIL. A PV emulation including the electric

thermal model with PHIL is presented in [49], while [50] uses PHIL to evaluate PV micro-inverter. A case study for testing a 500 kW PV inverter connected to a PV source using PHIL is presented in [51]. A DC loop PHIL is used to emulate the PV characteristic and an AC loop PHIL is used to emulate the connection of inverter to a distribution grid to study the reactive power control of an inverter as well as its effect on the distribution grid. There are no limitations in the type of system evaluation with PHIL, but PV application remains a popular choice to carry out such investigations.

#### 2.8. PHIL Case Studies

The majority of PHIL studies in literatures have focused towards improving the stability and accuracy of the PHIL loop. Work proposed in Ren, Steurer and Baldwin [26], and Ren, Steurer and Baldwin [52] serves as a basic framework for choosing IA based on accuracy and stability for various applications. Similarly, the interfacing issues of RTS along with inclusion of compensation for improving the accuracy of ITM is discussed in [30] and [36]. Another work focuses on accuracy improvement through online-parametric estimation using wide-band system identification technique for a DIM interface [53].

The application of PHIL studies is broad yet relatively new and the existing works are analyzed case-based rather than generic. The range of PHIL application varies from source emulation like solar and wind farm [49], [54], [55], switch-mode amplifier [32], [56], grid connected systems evaluation [57], [58] to cases where it requires grid impedance measurement [48].

## 2.9. Summary of Chapter 2

This chapter presented a general overview of the crucial components comprising the PHIL architecture. The chapter started with a short historical background behind the development of RTS and finally ended with the mentions of some notable case studies relating to PHIL. In between, the rational representation of delay model along with the SP compensator development is described with some mathematical formulations.

## **Chapter 3**

# Small-Signal Model of a Physical PV-Controller

## with CHIL Validation

This chapter is the result of original work published under M. Pokharel, A. Ghosh and C. N. M. Ho, "Small-Signal Modelling and Design Validation of PV-Controllers With INC-MPPT Using CHIL," IEEE Transactions on Energy Conversion, vol. 34, no. 1, pp. 361-371, March 2019.

The purpose of this work is to analyze the PV source to be able to apply it as a renewable source for PHIL testing. Also, to understand and get familiar with RTS device and its interface, PV model in RTDS is configured with a PCS with an actual controller connected using a CHIL approach. With CHIL, the MPPT controller implemented in DSP control-card can directly be used to track the maximum power from the PV panel. The CHIL approach enables to practically validate the PV model and its associated controller for power conversion which may aid in control design process. The details about this work is discussed in sections following.

#### 3.1. Introduction

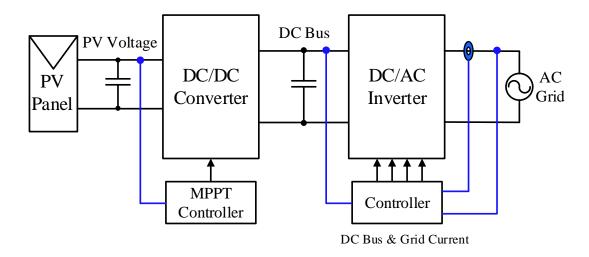

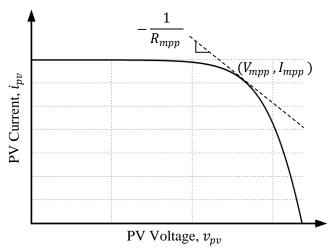

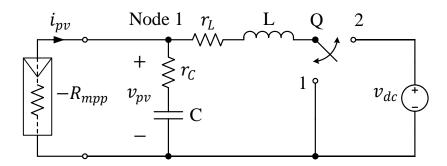

The maximum energy that can be harvested from a PV system at any instant depends on the effectiveness and response time of the MPPT algorithm used and related controllers. To facilitate proper controller design, a precise mathematical model of the system is required. Besides the controller, it is also important to know the architecture in which the PV source is connected to extract its power. It is common to have PV systems connected to the grid through inverters to transfer power to the grid. But as the number of PV source starts to grow, concerns for reliability and efficiency becomes critical. As a result, a lot of researches have reported various structures with single and two stages of power processing for connecting PV source to the grid [44]- [47]. One of such prominent schemes for extracting power from PV source is a two-staged GCPI which consists of a DC-DC converter responsible for MPPT and a DC-AC inverter for feeding power to the grid. A typical layout for power extraction with such scheme is shown in Figure 3.1.

Figure 3.1 A typical two-stage grid connected PV inverter scheme.

One of many variants of schematic in Figure 3.1 is its application as a DC power optimizer where the DC PCS (PV panel and DC-DC converter) is paralleled with multiple such stages followed by a single central inverter [44], [47], [59]. The DC-DC converter in the DC PCS is particularly responsible for MPPT which may be achieved with topologies like boost converter, buck-boost converter, SEPIC converter or various boost derived converters [60]-[62]. There are no such limitations in the topology itself and are also application dependent, but the choice of boost-based converter is supported by the fact that such converters provide a stable DC output voltage along with input voltage step-up function for PV [62]. The limitations are rather with the controller or the control algorithm as the same topology may exhibit improved power conversion and MPPT efficiency with the use of more advanced algorithms [63], [64].

For a GCPI shown in Figure 3.1, the performance of each PCS as well as their controllers is important in determining the overall performance of such system. Therefore, it is essential that each of these components are evaluated to decide the architecture and algorithm that can guarantee an efficient system. With the increasing penetration of PV energy into the grid, the effect of adding these switching converters at the Point of Common Coupling (PCC) also becomes an important grid integration study. Besides, the performance of inverter during various grid transients is another prospect that needs to be covered to understand the operation challenges of connecting such switching converters to the grid. Further, to simplify the study, the system in Figure 3.1 can be broken down into two parts; first the DC PCS which consists of a PV panel, a DC-DC converter and a MPPT controller, and second the AC PCS which consists of an inverter connected to the grid with its controller which controls the power delivered to the grid by controlling the grid current and at the same time maintaining the DC

bus voltage to the desired set point. The DC and AC PCS can be analyzed individually to understand their performance parameters. The sections in this chapter would focus on analyzing the DC PCS while the AC PCS is covered in the section of upcoming chapters, Chapter 4 and Chapter 5.

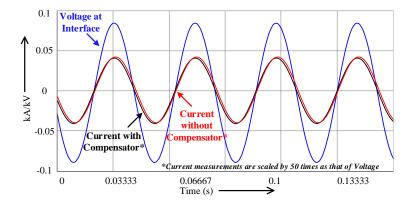

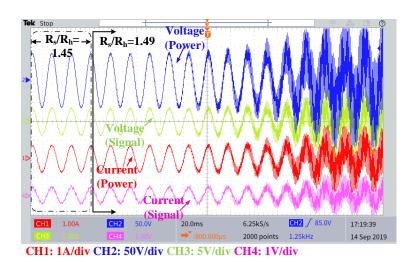

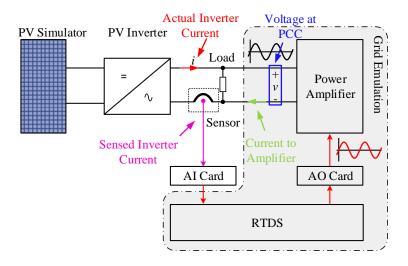

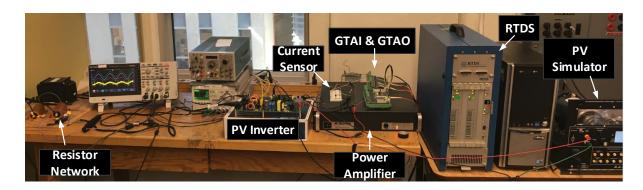

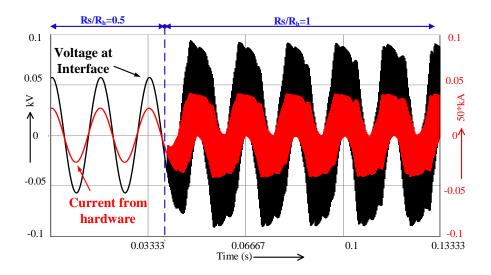

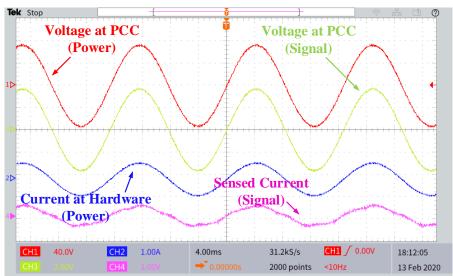

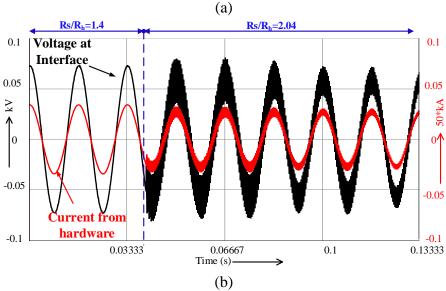

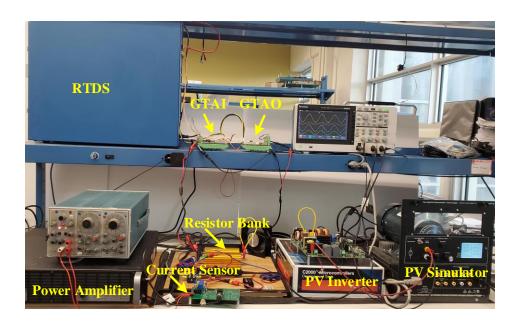

## 3.2. System Description