# Design and Implementation of a Grid-Connected Solar Micro-Inverter using a Single-Stage Galvanically Isolated Topology with Integrated Magnetics

by

Hafis Kolapo Umar-Lawal

A Thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg, Canada

Copyright © 2021 by Hafis Kolapo Umar-Lawal

## **Abstract**

Solar panels have been steadily increasing in capacity and decreasing in cost over the past few years. Given this context, and other incentives designed to increase renewable energy penetration, residential solar adoption is becoming more economically attractive. The solar AC module stands out amongst alternative residential solar technologies, for better modularity, higher efficiency, and ease-of-use. The Micro-Inverter (MI) topology bundled with the AC module then becomes a key factor in the overall cost, safety, and capacity of the system. The Flyback (FB) MI topology is a popular choice, thanks to its low component count and enhanced safety, but as modern residential solar panels trend towards 400 W and up, non-interleaved FB MIs, typically rated around 200 W, must become interleaved. Conventional FB MI interleaving is High Frequency (HF) interleaving, which adds a potentially bulky magnetic device to the topology. This thesis proposes and tests the application of an alternate topology, called the Isolated Manitoba Inverter (ISOMBI). The ISOMBI uses integrated magnetic devices and Low Frequency (LF) interleaving, to match the power rating of HF-interleaved FB MIs, without the extra bulky component. ISOMBI operating principles and analyses are disclosed, and an experimental prototype is constructed to test its ability as a grid connected power generator. The results show near unity Power Factor (PF), acceptable DC current levels and promising Total Demand Distortion (TDD). Overall, these results indicate that the LF-interleaved ISOMBI can be considered as a viable alternative to the HF-interleaved FB MIs in AC modules.

# **Dedication**

To Mom

## **Acknowledgements**

My sincere and utmost gratitude goes to Dr. Carl Ho. My teacher and mentor. 6 years ago, I met you in the undergrad electronics 2 course, and on the verge of quitting electrical engineering. The guidance, mentorship, and most of all passion that you showed inspired me to stick around, and here I am, preparing a master's thesis. I cannot imagine my career progression, without your incredible levels of patience, and the development environment you fostered, where I felt safe and boldened to pursue research. I hope someday you will be proud of having trained me.

I would also like to thank Dr. Philip Ferguson, who placed faith in me, and supported my participation in the Canadian CubeSat project. The training and exposure I received from visiting the Canadian space agency, presenting to them, and having my work evaluated by real industry experts is invaluable and I will forever be grateful. Thank you for your tutelage, most especially on engineering philosophy. I learned from you directly and indirectly, and I am incredibly honored to have been one of your mentees.

I also express appreciation to lab mates in both RIGA lab and STAR lab, who offered advice, assistance, and friendship. Specifically, to Ken Siu, for sharing his deep power electronics theory knowledge; Mandip Pokharel, for patiently teaching me control systems; Jaime Campos, for numerous personal accommodations; and Isuru Jayawardana, for help with all sorts of debugging. Thank you! To all lab mates, for being great friends and radiating warmth even in the cold winters.

I would also like to thank the ECE technical staff. Glen Kolansky, Shrimal Koruwage, Cory Smit, and Zoran Trajkoski. Thank you for always saving the day with your ingenuity. Lastly, I thank my family and friends, especially Clinton Kerwin, for encouraging me and providing a stable emotional backdrop against the ups and downs of research. To my beautiful girlfriend Lolade Olatunde, thank you for making a big deal of my progress and being excited for me, even when you had no idea what I was babbling about. Your constant reassurance made all the difference.

# **Table of Contents**

| Abstract                                             | i    |

|------------------------------------------------------|------|

| Dedication                                           | ii   |

| Acknowledgements                                     | iii  |

| Table of Contents                                    | iv   |

| List of Figures                                      | Viii |

| List of Tables                                       | xi   |

| List of Acronyms                                     | xii  |

| Chapter 1 - Introduction                             | 1    |

| 1.1 Problem Definition                               | 1    |

| 1.2 Research Scope                                   | 2    |

| 1.3 Background                                       | 3    |

| 1.4 Basic Functions of a Residential Solar Inverter  | 4    |

| 1.4.1 Maximum Power Point Tracking (MPPT)            | 4    |

| 1.4.2 DC-AC Power Conversion                         | 5    |

| 1.4.3 Power Decoupling                               | 5    |

| 1.4.4 Voltage Amplification                          | 6    |

| 1.5 Configuration of Residential Solar Installations | 7    |

| 1.5.1 String-inverter System Configuration           | 8    |

| 1.5.2 Micro-Inverter System Configuration            | 11   |

| 1.5.3 AC Modules – Enabled by MIs                    | 13   |

| 1.5.4 Comparisons between PV System Configurations        | 15 |

|-----------------------------------------------------------|----|

| 1.6 Thesis Structure                                      | 17 |

| Chapter 2 - Review of the Flyback Micro-Inverter Topology | 19 |

| 2.1 Overview of FB MIs                                    | 19 |

| 2.2 Single-Stage vs Two-Stage MIs                         | 20 |

| 2.3 FB MI Topology Variants                               | 23 |

| Chapter 3 - The Isolated Manitoba Inverter Topology       | 29 |

| 3.1 Operating Principles                                  | 30 |

| 3.1.1 Positive line Cycle Operation                       | 31 |

| 3.1.2 Negative line Cycle Operation                       | 31 |

| 3.1.3 Summary of Operating Principles                     | 32 |

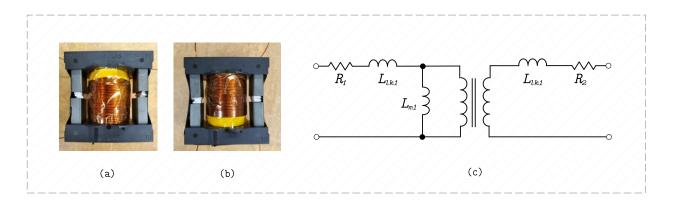

| 3.1.4 Integrated Magnetics                                | 32 |

| 3.2 Steady-State Analysis                                 | 35 |

| 3.2.1 Steady-State Analysis Assumptions                   | 36 |

| 3.2.2 Pseudo-DC link Voltage                              | 37 |

| 3.2.3 Primary Magnetizing Current                         | 38 |

| 3.2.4 Hybrid Mode Duty Ratios                             | 39 |

| 3.2.5 Peak Primary Current                                | 42 |

| 3.3 Component Parameter Derivations                       | 42 |

| 3.3.1 Primary Magnetizing Inductance                      | 42 |

| 3.3.2 Input Decoupling Capacitor                          | 43 |

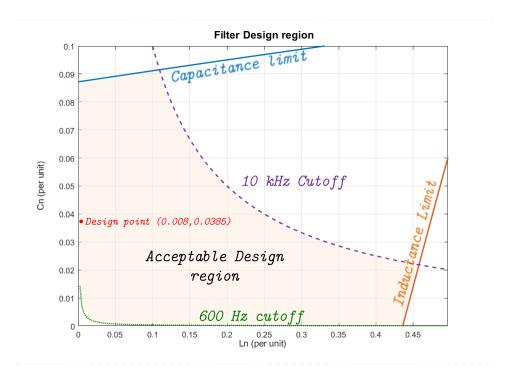

| 3.3.3 Output <i>CL</i> filter                             | 44 |

|-----------------------------------------------------------|----|

| 3.4 Chapter summary                                       | 47 |

| Chapter 4 - The Isolated Manitoba Inverter Control System | 48 |

| 4.1 Inverter Current Loop Overview                        | 49 |

| 4.2 Small-signal Model and Transfer functions             | 51 |

| 4.2.1 Inner Loop: Duty-to-primary-current TF              | 52 |

| 4.2.2 Outer Loop: Primary-current-to-grid-current TF      | 54 |

| 4.3 Compensator Design                                    | 56 |

| 4.3.1 CCM/DCM Hybrid mode                                 | 59 |

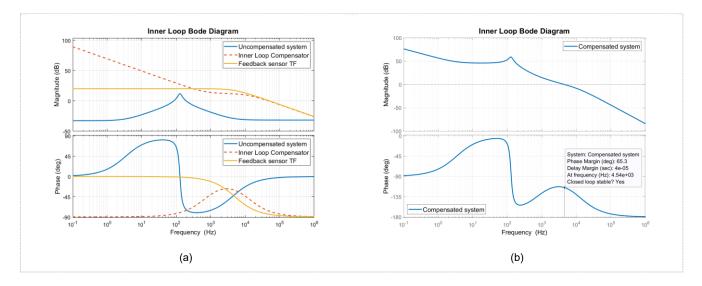

| 4.3.2 Inner loop compensator design                       | 60 |

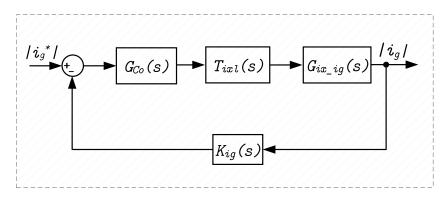

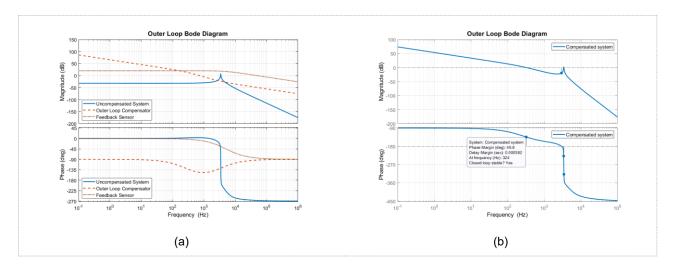

| 4.3.3 Outer loop compensator design                       | 63 |

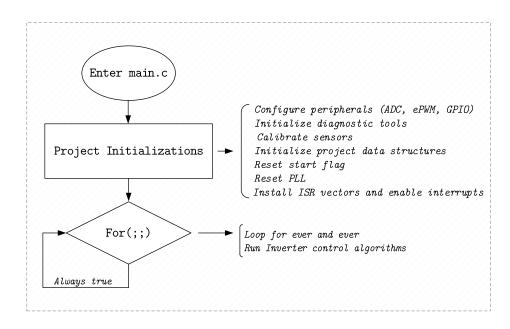

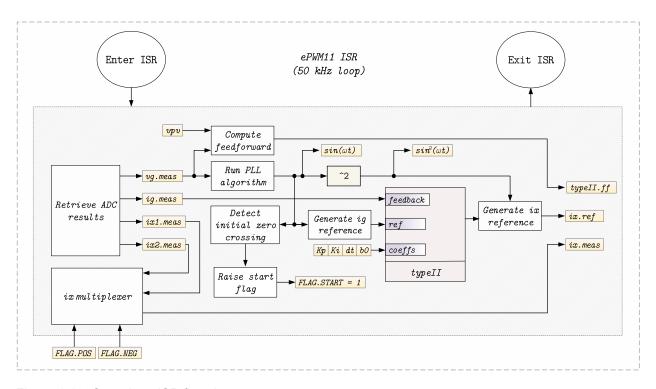

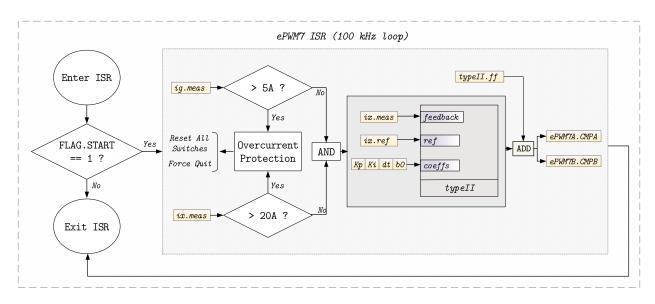

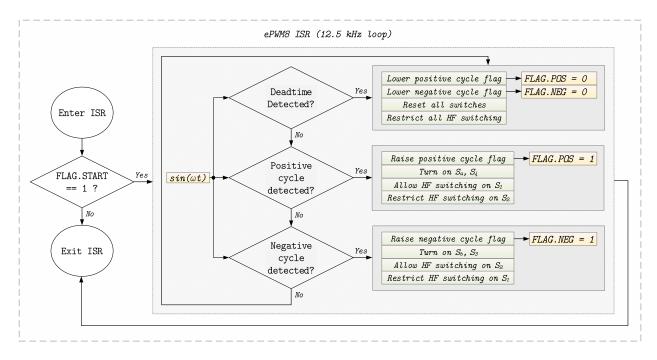

| 4.4 Digital controller implementation                     | 64 |

| 4.5 Chapter summary                                       | 71 |

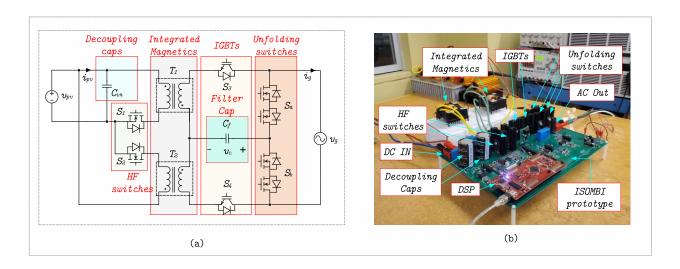

| Chapter 5 - Prototyping and Experimental Verification     | 73 |

| 5.1 Prototype Specifications and Design                   | 73 |

| 5.1.1 <i>CL</i> filter                                    | 74 |

| 5.1.2 Integrated Magnetic Devices                         | 75 |

| 5.1.3 RCD snubber                                         | 77 |

| 5.1.4 DSP Software                                        | 78 |

| 5.2 Experimental verification                             | 78 |

| 5.2.1 Operating Principles                                | 80 |

| 5.2.2 Steady state analysis verification                | 84  |

|---------------------------------------------------------|-----|

| 5.2.3 Control-system Validation                         | 90  |

| 5.2.4 AC Power Quality                                  | 93  |

| 5.2.5 Power Conversion Efficiency                       | 96  |

| 5.3 Chapter Summary                                     | 98  |

| Chapter 6 - Conclusions and Future Work recommendations | 99  |

| 6.1.1 Operating Principles                              | 99  |

| 6.1.2 Steady-State Characteristics                      | 99  |

| 6.1.3 Control System                                    | 99  |

| 6.1.4 AC Power Quality                                  | 100 |

| 6.1.5 Power Conversion Efficiency                       | 100 |

| 6.2 Future work recommendations                         | 101 |

| 6.3 Thesis reflections                                  | 102 |

| Bibliography                                            | 104 |

# **List of Figures**

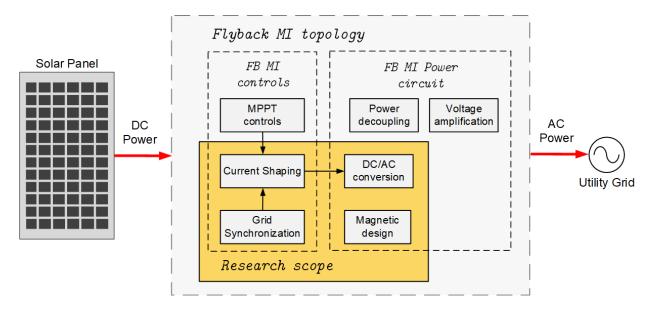

| Figure 1-1. Visual summary of research scope                                                     | 2    |

|--------------------------------------------------------------------------------------------------|------|

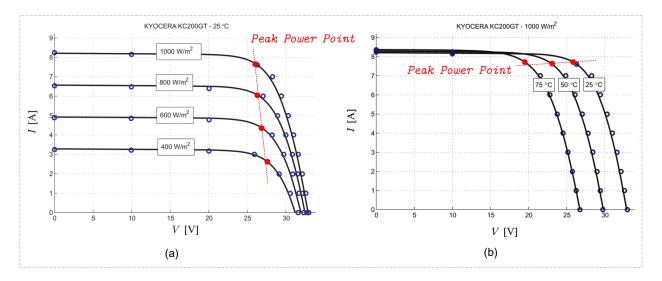

| Figure 1-2. Illustrating variance in panel operating parameters with irradiance level and        |      |

| temperature for the Kyocera KC200GT solar panel (a) I-V curves under different irradiation       |      |

| levels at 25°C, (b) I-V curves at different temperatures [25].                                   | 4    |

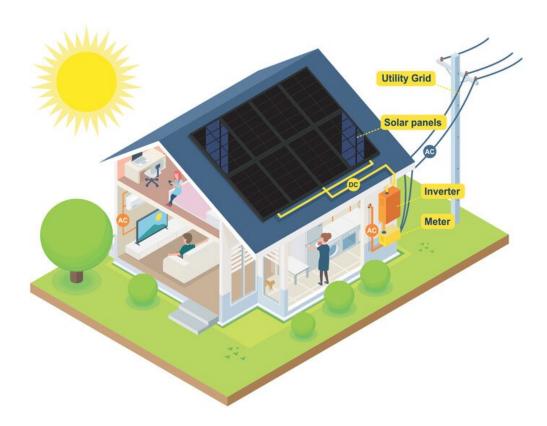

| Figure 1-3. Residential solar infographic [33].                                                  | 7    |

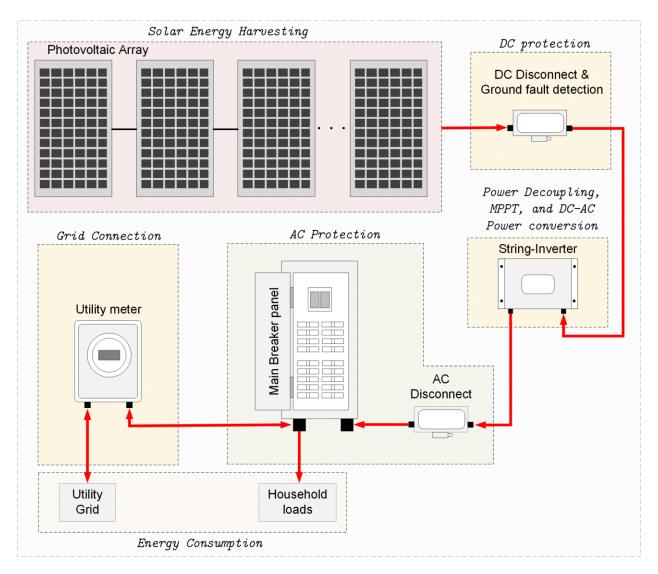

| Figure 1-4. String-inverter PV system schematic, adapted from [34]                               | 8    |

| Figure 1-5. String-inverter system configurations, adapted from [7], [8]. (a) Standard string    |      |

| connection (b) Multi-string connection (c) MLPE-string connection.                               | 10   |

| Figure 1-6. MI system configuration, adapted from [7]                                            | 12   |

| Figure 1-7. An Enphase-Panasonic AC module [36]                                                  | 13   |

| Figure 1-8. PV system schematic with AC modules, adapted from [37]                               | 14   |

| Figure 2-1. Two-stage MI illustration                                                            | 20   |

| Figure 2-2. Single stage MI with PV side decoupling, adapted from [8]                            | 21   |

| Figure 2-3. Single stage MI detailed system diagram                                              | 21   |

| Figure 2-4. single-stage FB MI with active unfolding and CL filter (a) Topology (b) Primary si   | de   |

| operating waveforms (c) Secondary side operating waveforms                                       | 23   |

| Figure 2-5. Centre-tapped transformer variant of the FB MI (a) Topology (b) Primary side         |      |

| waveforms (c) Secondary side waveforms                                                           | 26   |

| Figure 2-6. HF-Interleaved variant of the FB MI                                                  | 27   |

| Figure 3-1: Isolated Manitoba Inverter topology (a) Topology (b) Primary waveforms (c)           |      |

| Secondary waveforms                                                                              | 29   |

| Figure 3-2. ISOMBI circuit configurations in (a) Positive line cycle, and (b) Negative line cycl | e.30 |

| Figure 3-3. ISOMBI Positive line cycle equivalent circuit                                        | 31   |

| Figure 3-4. Negative line cycle equivalent circuit.                                              | 32   |

| Figure 3-5. Integrated magnetics functionality, (a) as coupled-winding inductor in FB transfor | mer |

|------------------------------------------------------------------------------------------------|-----|

| mode, and (b) as single-winding grid filter Inductor                                           | 34  |

| Figure 3-6. ISOMBI steady-state equivalent circuit                                             | 35  |

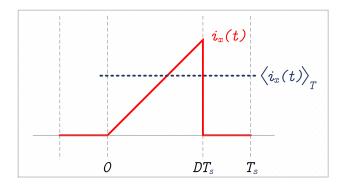

| Figure 3-7. DCM current waveform                                                               | 40  |

| Figure 3-8. Real and reactive power flow diagram, arrows pointing up indicate supply, arrows   | S   |

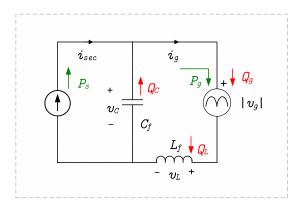

| pointing down indicate dissipation/absorption.                                                 | 45  |

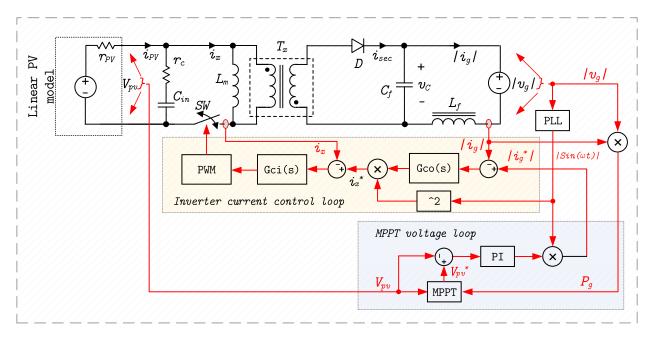

| Figure 4-1. ISOMBI control system                                                              | 48  |

| Figure 4-2. Approximate second-order equivalent circuit for small signal modelling             | 49  |

| Figure 4-3. secondary-current-to-grid-current dynamic model                                    | 55  |

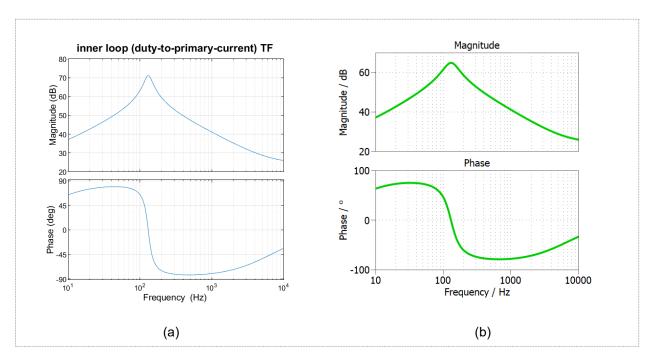

| Figure 4-4. inner loop TF (a) MATLAB analytical model (b) PLECS simulation model               | 57  |

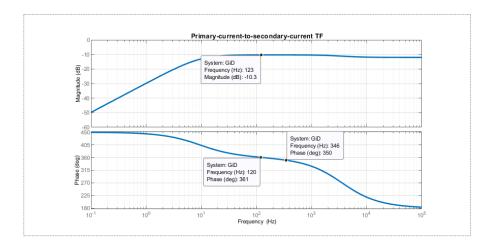

| Figure 4-5. Primary-current-to-secondary-current TF                                            | 59  |

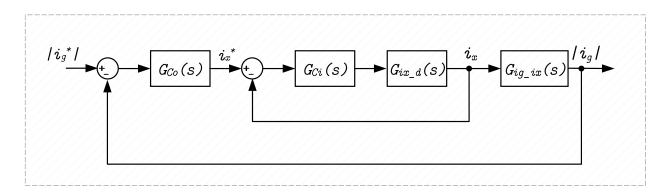

| Figure 4-6. ISOMBI Control Block diagram                                                       | 59  |

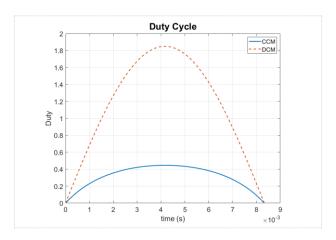

| Figure 4-7. Steady-State DCM and CCM duty ratios                                               | 60  |

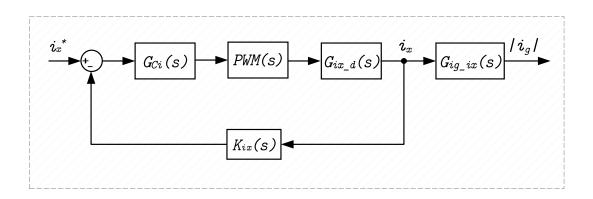

| Figure 4-8. Inner loop control block diagram                                                   | 61  |

| Figure 4-9. Inner Loop Bode plots (a) Uncompensated system (b) Compensated system              | 62  |

| Figure 4-10. Outer loop control block diagram                                                  | 63  |

| Figure 4-11. Outer loop bode plots (a) Uncompensated system (b) Compensated system             | 64  |

| Figure 4-12. Control Software overview flowchart                                               | 67  |

| Figure 4-13. Outer loop ISR flowchart                                                          | 69  |

| Figure 4-14. Inner loop ISR flowchart                                                          | 70  |

| Figure 4-15. Synchronization ISR flowchart                                                     | 71  |

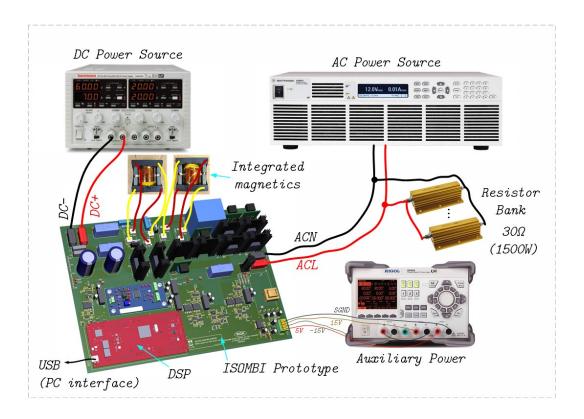

| Figure 5-1. ISOMBI prototype (a) circuit diagram (b) Experimental prototype                    | 74  |

| Figure 5-2. CL filter design region                                                            | 75  |

| Figure 5-3. Integrated magnetics (a) $T_1$ (b) $T_2$ (c) equivalent circuit                    | 76  |

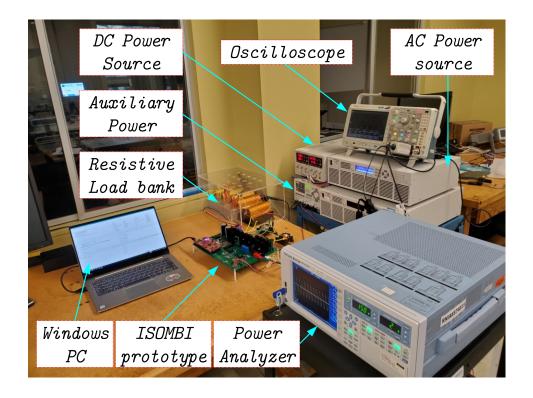

| Figure 5-4. Simplified experimental setup                                                      | 79  |

| Figure 5-5. Laboratory experimental setup.                                                     | 79  |

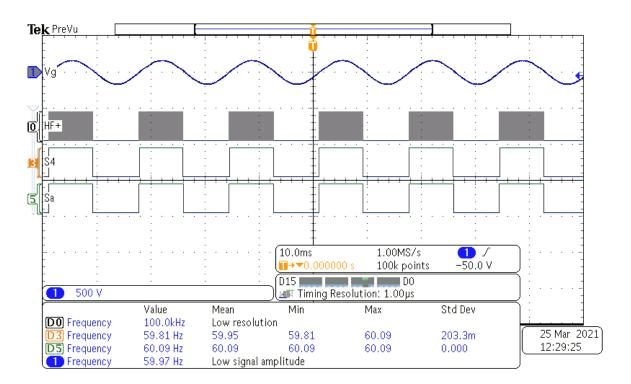

| Figure 5-6. Positive cycle synchronization waveforms                                      | 80 |

|-------------------------------------------------------------------------------------------|----|

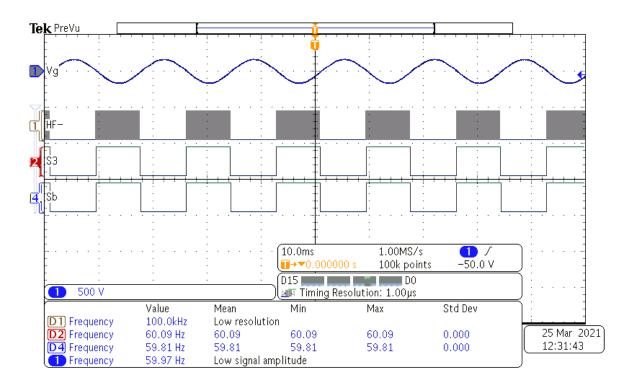

| Figure 5-7. Negative cycle synchronization waveforms                                      | 81 |

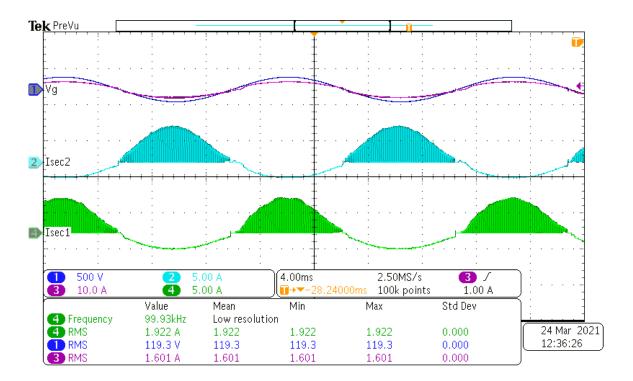

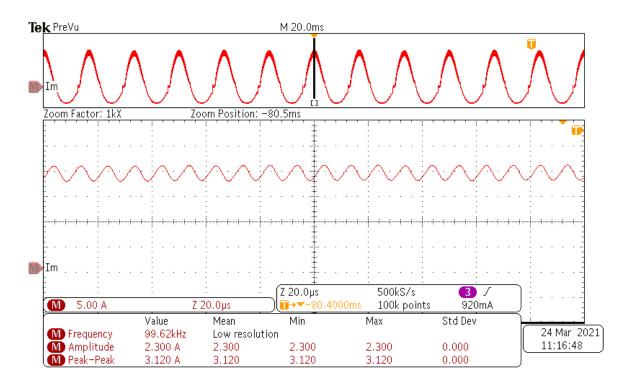

| Figure 5-8. Secondary Current waveforms showing integrated magnetics function             | 82 |

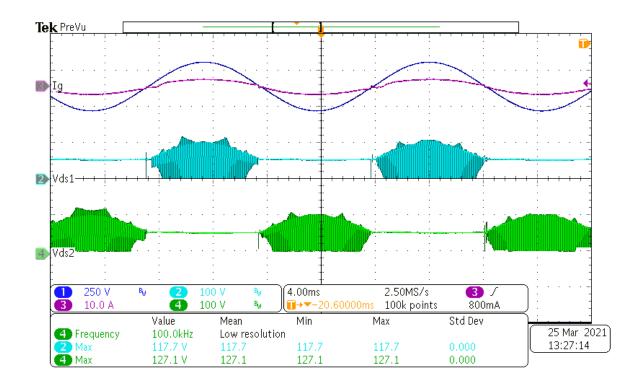

| Figure 5-9. Drain-Source voltage of primary switches                                      | 83 |

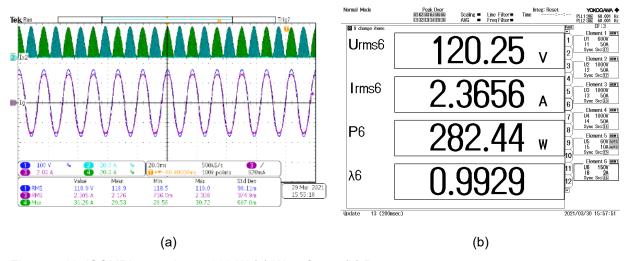

| Figure 5-10. ISOMBI operating at 280 W (a) Waveforms (b) Power measurements               | 83 |

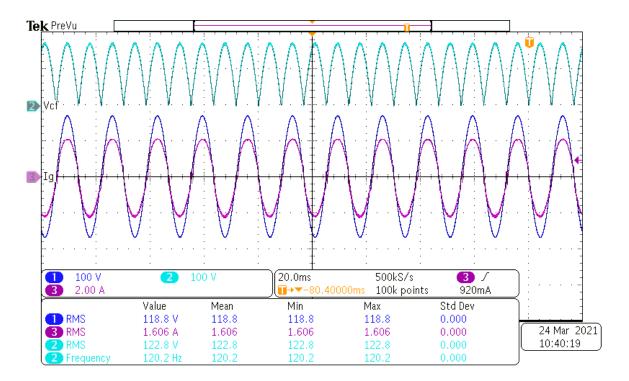

| Figure 5-11. Pseudo DC link voltage waveform                                              | 84 |

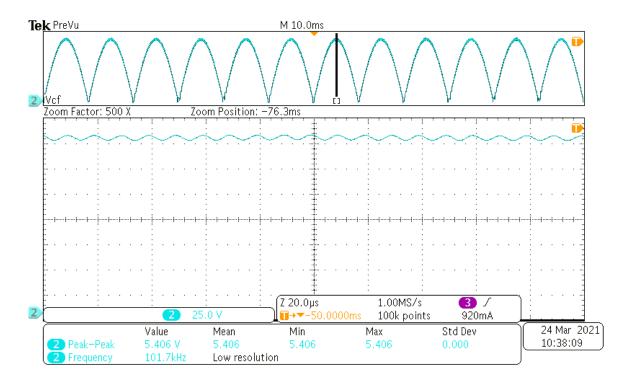

| Figure 5-12. Pseudo-DC-link voltage ripple waveform                                       | 85 |

| Figure 5-13. Magnetizing current waveform                                                 | 86 |

| Figure 5-14. Magnetizing current ripple waveform                                          | 87 |

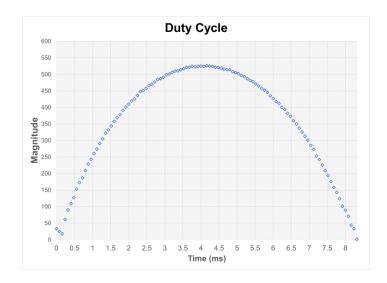

| Figure 5-15. Duty ratio                                                                   | 88 |

| Figure 5-16. Primary Current waveform                                                     | 88 |

| Figure 5-17. Verifying CCM operation (a) close to the peak (b) elsewhere                  | 89 |

| Figure 5-18. Average primary current sampled by DSP                                       | 89 |

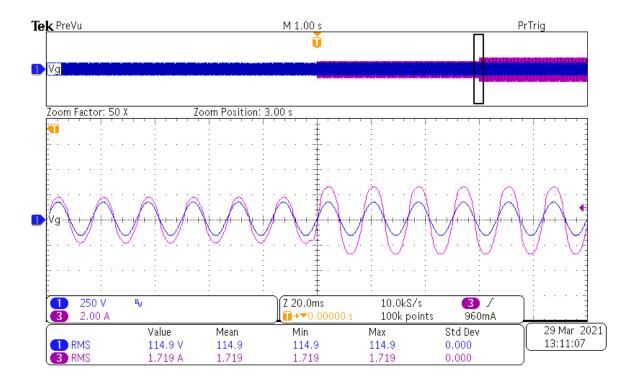

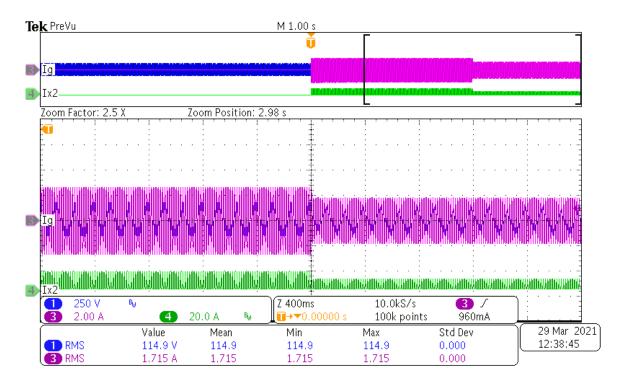

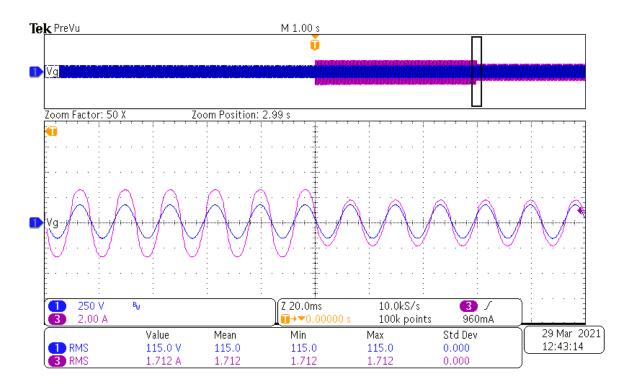

| Figure 5-19. Step-up reference change                                                     | 91 |

| Figure 5-20. Zoomed-in Step up reference change.                                          | 91 |

| Figure 5-21. Step-down reference change                                                   | 92 |

| Figure 5-22. Zoomed-in step-down reference change                                         | 93 |

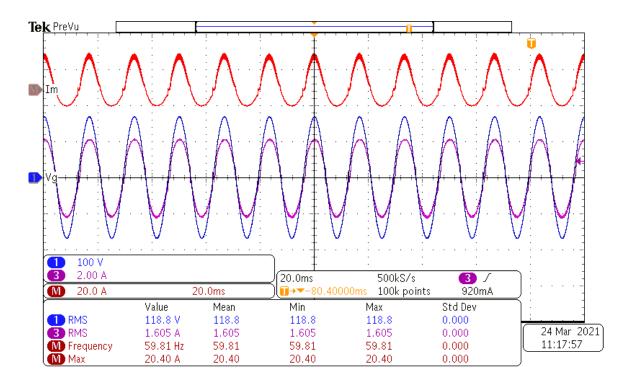

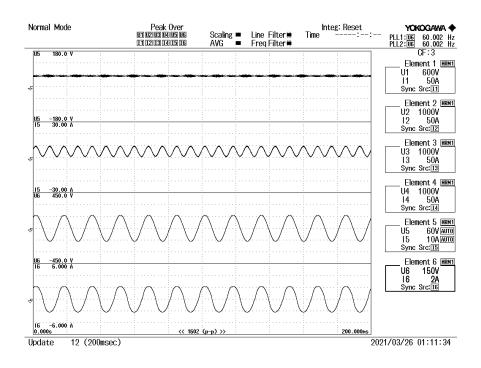

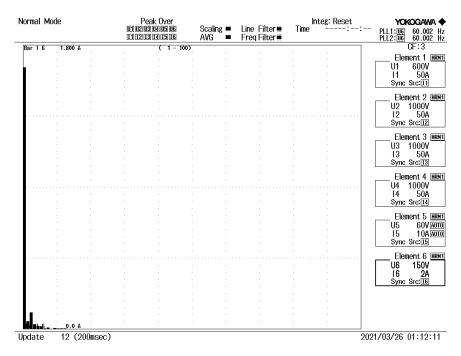

| Figure 5-23. Power analyzer waveforms captured at 200 milliseconds intervals, from top to |    |

| bottom: DC input voltage, pulsating input current, AC voltage, AC output current          | 94 |

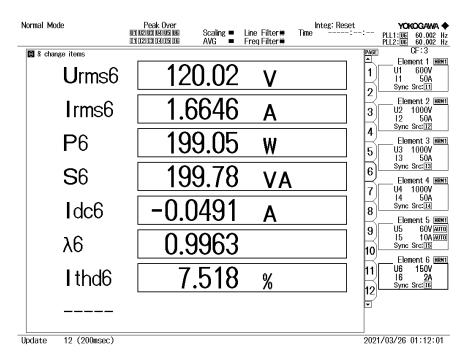

| Figure 5-24. Power analyzer measurements showing DC current level and PF                  | 95 |

| Figure 5-25. Harmonic spectrum obtained from power analyzer                               | 95 |

# **List of Tables**

| Table 1-1. Comparison of PV system configurations                   | 15 |

|---------------------------------------------------------------------|----|

| Table 2-1. Comparison Summary of Single and Two-Stage MI topologies | 22 |

| Table 2-2. Comparison of FB MI variants, with the ISOMBI            | 27 |

| Table 3-1. PF requirements summary based on [28], [52]              | 45 |

| Table 4-1. ISOMBI prototype specifications and circuit parameters   | 57 |

| Table 4-2. Inner Loop Control block diagram TFs                     | 61 |

| Table 4-3. Outer loop control block diagram TFs                     | 63 |

| Table 4-4. ISR information table                                    | 68 |

| Table 5-1. Technical Specifications of the ISOMBI prototype         | 73 |

| Table 5-2. Magnetic simulation results                              | 76 |

| Table 5-3. Properties of magnetic prototypes                        | 77 |

| Table 5-4. Summary of steady-state characteristics at 200 W         | 90 |

| Table 5-5. Total Demand Distortion of odd harmonic components       | 96 |

| Table 5-6. ISOMBI prototype loss estimation model                   | 97 |

## **List of Acronyms**

**24/7** - 24 hours, 7 Days

**A.T.** - Ampere-Turns

AC - Alternating Current

**ADC** - Analog to Digital Converter

**BW** - Bandwidth

**CCM** - Continuous Conduction Mode

**CCS** - Code Composer Studio

**CL** - Capacitor-Inductor (Low pass filter)

**COVID-19** - Coronavirus Disease 2019

**DC** - Direct Current

**DCM** - Discontinuous Conduction Mode

**DSP** - Digital signal processor

**EMI** - Electromagnetic Interference

**ePWM** - Enhanced Pulse Width modulation

**ESR** - Equivalent Series Resistance

FB - Flyback

**GM** - Gain Margin

**HF** - High frequency

**IDE** - Integrated development environment

**IEA** - International Energy Agency

**IEEE** - Institute of Electrical and Electronics Engineers

IGBT - Insulated Gate Bipolar Transistor

**ISOMBI** - Isolated Manitoba Inverter (The proposed topology)

ISR - Interrupt Service Routine

KCL - Kirchoff's Current Law

**LPF** - Low Pass filter

**MATLAB** - Matrix Laboratory (software)

MI - Micro-Inverter

**MLPE** - Module Level Power Electronics

**MMF** - Magnetomotive force

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

**MPPT** - Maximum Power Point Tracking

**NEC** - National Electric Code (of the USA)

PCB - Printed Circuit Board

**PF** - Power Factor

PLECS - Piecewise Linear Electric Circuit Simulator (simulation software)

PLL - Phase Locked Loop

PM - Phase Margin

PV - Photovoltaic

PWM - Pulse Width Modulator

RC - Resistor-Capacitor

**RCD** - Resistor-capacitor-Diode

**RHP** - Right-Half-Plane (of the complex axes)

**RMS** - Root Mean Square

**TDD** - Total Demand Distortion

**TF** - Transfer Function

**THD** - Total Harmonic Distortion

TI - Texas Instruments

US - United States (country)

**USB** - Universal Serial Bus

## **Chapter 1 - Introduction**

#### 1.1 Problem Definition

The US department of energy projects significant cost reductions for solar panels, due to efficiency gains in solar cell research [1]. This could improve the economic appeal of solar power and promote its residential application. As such, AC modules, which consist of solar panels bundled with Micro-Inverters (MIs), and are primarily targeted at residential installations now trend in research and commercially [2]–[7]. The rise of the AC module is largely due to its ease-of-use over the alternative (solar panel with string-inverter arrangement). MIs are power electronics devices that process power from a single solar panel and enable the AC module's plug-and-play (ease-of-use) functionality [8]. However, residential grade solar panels, previously limited to a range of 200-250 W now peak at about 400 W, thanks to improved solar cell efficiency [1], [9]–[11]. MI topology power ratings must therefore be evaluated to keep up with modern solar panels and maintain AC module functionality.

The Flyback (FB) MI topology emerged in MI research, as an efficient single-stage topology, with low component count (low costs), and galvanic isolation (boosts safety), making it a choice MI topology for AC modules [12], [13]. However, in order to match the increasing power output of modern solar panels, the FB MI found in commercial products is applied with High-Frequency (HF) interleaving [12]–[14]. HF-interleaving assists the FB MI to increase output power efficiently, whilst maintaining advantageous single-stage conversion and galvanic isolation. On the other hand, HF-interleaving adds an extra magnetic device to the FB MI, potentially increasing costs, and bulk. This research proposes an alternative, by investigating the application of a new FB-type topology to AC module MIs. The proposed topology uses LF-interleaving and functionally integrated magnetics, to avoid the extra magnetic device associated with HF-interleaving.

#### 1.2 Research Scope

The work done in this thesis investigates the use of a new single-stage FB-type topology as an AC Module MI. The topology, called the Isolated Manitoba Inverter (ISOMBI) uses functionally integrated magnetic components and LF-interleaving for grid synchronized DC-AC power conversion. The thesis also provides a comprehensive analysis of FB MI operating characteristics and proposes a double loop current control strategy for grid-connected FB MIs. Figure 1-1 provides a visual summary of the research scope which explores the following themes:

- a) Review contemporary FB MI topology variants and study their operating principles.

- b) Investigate and compare the ISOMBI topology with contemporary FB MI variants

- c) Derive and validate operating principles for using the ISOMBI topology as a MI, supported by analyses, simulation, hardware implementation, and laboratory experiments.

- d) Design and use functionally integrated magnetic devices for reduced component count.

Figure 1-1. Visual summary of research scope

#### 1.3 Background

Electricity is vital to sustaining today's 24/7 digital economy, especially recently, where COVID-19 pandemic restrictions have catalyzed the adoption of remote activities [15]–[17]. These new forms of work, play and learning have caused a shift in energy profiles [15], such that despite an overall decrease in total energy consumption, residential demand is at an all-time high [15]. The situation thereby introduces an opportunity to restart the economy from clean energy sources [17]–[21]. If remote activity continues to sustain high residential demand, residential solar adoption would be decisive in meeting the International Energy Agency's (IEA) sustainable development goals, of having 49% renewable penetration by 2030 [22].

In residential solar installations, photovoltaic (PV) modules, also known as solar panels, mounted on a rooftop or on the ground, convert incident light photons into Direct Current (DC) electrical energy, to be processed into Alternating Current (AC) by an inverter [23], [24]. The inverter is an active and controllable power processing device, whose basic responsibilities include: Converting DC power to AC power synchronized with the utility grid's phase and frequency, extracting maximum possible power from incident solar radiation, decoupling pulsating AC output power from constant DC input power, and sometimes boosting low DC input voltage to match the peak of the utility grid voltage [8], [25]. Each inverter function is the subject of intense research, resulting in proposals of various topologies, system arrangements and control algorithms [6], [8], [25], [26].

This introductory chapter highlights basic inverter functions and residential solar installation arrangements; introduces the AC module concept; and compares inverter technologies against each other in terms of benefits, drawbacks, and challenges. These discussions are used to support the research scope, and contributions. The chapter concludes by presenting a brief outline for the rest of this thesis.

#### 1.4 Basic Functions of a Residential Solar Inverter

Three basic functions can be identified for all types of residential solar inverters, these are: Maximum Power Point Tracking (MPPT), power decoupling and DC-AC power conversion [8]. With all the aforementioned, MIs specifically are further required to provide voltage amplification, to match the output voltage of a single solar panel with the peak amplitude of the AC grid [12]. These four basic functions are discussed in following subsections.

#### 1.4.1 Maximum Power Point Tracking (MPPT)

To maximize the solar energy harvested by the installation, the operating parameters of a solar panel must be managed by the inverter, such that the panel generates the maximum possible power under prevailing atmospheric conditions [8], [27]. The solar panel is made up of solar cells that generate electric power in proportion to irradiance levels and surrounding temperature. Figure 1-2 demonstrates this by showing the I-V characteristic curves of the Kyocera KC200GT solar panel, obtained from [27].

Figure 1-2. Illustrating variance in panel operating parameters with irradiance level and temperature for the Kyocera KC200GT solar panel (a) I-V curves under different irradiation levels at 25°C, (b) I-V curves at different temperatures [25].

In Figure 1-2(a), operating parameters vary with irradiance level, while in Figure 1-2(b) they vary with temperature [27]. In both figures, A dotted line indicates the optimal operating point, where maximum power can be extracted across varying conditions. Consequently, inverters must employ MPPT algorithms to manage the operating voltage or current of the panel, if they are to extract maximum possible power, despite dynamic changes in atmospheric conditions.

#### 1.4.2 DC-AC Power Conversion

The main function of a grid-connected residential inverter is to convert DC energy into AC energy and synchronize with the AC utility grid. This makes the installation a grid connected power generator. As such, it faces strict requirements governing the quality of power sent to the grid [8]. For instance, a prominent California utility requires residential inverters to maintain unity PF by default (and limit variations between 0.9 leading and 0.9 lagging), limit current TDD to below 5%, and DC current injection to less than 0.5% of the rated current [28].

To meet such requirements, designers place constraints on the design of output filters used by the inverter and actively shape the current using control algorithms. The ideal AC current for unity PF is a pure sine wave at the same phase and frequency as the grid voltage. Hence, current control schemes include tracking and shaping algorithms must ensure phase and frequency synchronization. While output filters are used to smooth and deliver continuous sinusoidal current.

#### 1.4.3 Power Decoupling

Residential solar installations are single-phase AC power systems, which create a pulsating power component at twice the grid frequency on the AC side [8], [12]. To maintain instantaneous equilibrium between the DC input power and AC output power, the pulsating component is reflected onto DC input parameters, [8], [12]. The double line frequency component on the DC input voltage, negatively impacts MPPT, as it causes operating parameters to deviate from the

optimal point [8]. To restore effective MPPT, the DC voltage ripple must be kept below 8.5%, by decoupling instantaneous power between the AC and DC sides [8].

Power decoupling may be active or passive [12]. Passive power decoupling places a high value electrolytic capacitor between the solar panel and the utility grid which reduces DC ripples and buffers the power supplied to the AC side [8], [12]. Electrolytic capacitors are used because they offer higher energy density than other types [29]. However, they are also known to age poorly under temperature extremes, and become a limiting factor in the harsh operating environment of some inverters [8], [29]. This has led to the development of active power decoupling techniques, such that more resilient, lower value film capacitors can be used to achieve the same objectives.

#### 1.4.4 Voltage Amplification

This requirement is unique to MIs, which convert power from a single low-voltage solar panel. The alternative, string-inverter, avoid voltage amplification by using series connected solar panels to increase the DC voltage [8]. A residential grade solar panel, consists between 60 and 72 photosensitive PN junction cells [30], [31], each operating between 0.5 and 1.0 V [8]; Hence, the typical residential panel operates in a voltage range between 24 and 60 V. However, the North American power grid offers a 170 V amplitude at the most accessible interface [32], and as a result, the MI, converting a single panel's power must amplify the voltage to match the grid level.

# 1.5 Configuration of Residential Solar Installations

Figure 1-3 is a simple infographic illustrating a sample grid-connected residential solar energy project [33]. Roof mounted solar panels transfer DC energy to an inverter, which subsequently outputs AC energy to household loads and the utility grid. The depicted inverter is a string-inverter which processes power from all the solar panels. Residential solar installations are classified based on the type of inverter deployed. Hence, they are either string-inverter-based (like Figure 1-3) or micro-inverter-based systems. These are the two distinct inverter types used in residential installations and their impacts on system configuration are presented in following subsections.

Figure 1-3. Residential solar infographic [33].

#### 1.5.1 String-inverter System Configuration

Figure 1-4 shows a simplified schematic of a basic string-inverter system [34]. Energy from the solar array travels through protective disconnects and a string-inverter to household loads and the utility line. Solar panels in a string-inverter based system are series connected (to form strings), such that the series voltage exceeds the grid voltage, and they do not need extra voltage amplification [8]. The string-inverter is so called due to the string-like connection of panels, which form a single DC input to the Inverter. As depicted in Figure 1-4, the string-inverter is responsible for power decoupling, MPPT and DC-AC power conversion of the entire solar array [8].

Figure 1-4. String-inverter PV system schematic, adapted from [34]

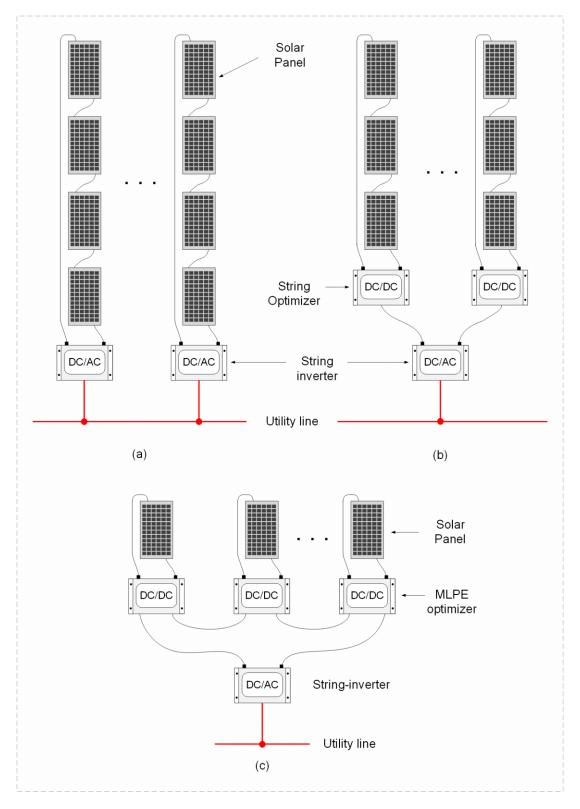

There are three different methods of configuring a string-inverter system [7], [8]. All three methods are illustrated in Figure 1-5. The standard string-inverter configuration of Figure 1-5(a) is one where the solar strings are directly connected to the inverter. About 16 to 20 panels may make up one string to avoid exceeding the voltage ratings of conventional power semiconductors (1000 V) [8], and the use of one string is typical in residential applications to avoid the costs of duplicating inverters, protection equipment and a more demanding installation process.

The arrangement of Figure 1-5(b), is called the Multi-string configuration [8], where the MPPT of a single string is first performed by a DC-DC optimizer stage. Then subsequently, optimized DC outputs are converted to AC power using a single string-inverter, which also handles power decoupling. This configuration is uncommon in residential projects, where a single string is often used, and the DC-DC stage offers no additional benefits over the standard String setup to justify the additional cost of acquiring a DC-DC optimizer.

Finally, Figure 1-5(c) called the "Module-Level Power Electronics (MLPE) optimized" string configuration, introduces MLPE DC-DC optimizers that perform individual MPPT for each panel [7]. Optimized DC outputs are then processed by a single string-inverter into AC with power decoupling. Since MPPT is performed for each panel, the system is not held back by weak, damaged, or shaded modules. The main drawback of this final arrangement is the additional cost of acquiring the MLPE DC-DC optimizers, which place it above the previous arrangements in terms of acquisition costs.

Figure 1-5. String-inverter system configurations, adapted from [7], [8]. (a) Standard string connection (b) Multi-string connection (c) MLPE-string connection.

The use of a single string-inverter for centralized DC-AC conversion of an entire solar panel array facilitates access to the device for maintenance and diagnostics. This also lowers the difficulty of design compared to a potential distributed system and is translated into low acquisition costs [35]. However, the system also becomes susceptible to single-point failures because the malfunction of the sole string-inverter will halt operations. The other main disadvantage of centralizing DC-AC Power conversion for a string of panels, is losing access to individual panel parameters (except for the MLPE-string arrangement). This means that MPPT cannot be truly optimized for every panel, and the weakest, shaded or otherwise damaged panels will hold back the entire system.

It is also relatively tasking to plan and install a string-inverter based systems. String lengths must be carefully configured, considering panel and inverter characteristics, desired power output and budget. The calculations are relatively simple, but quickly become exhausting, considering the large inventory of panels and inverters available at different price points. Yet upon installation, the system is inherently low in modularity and deters capacity upgrades. Adding extra panels may be simple as reconfiguring string wiring, but it is more likely to involve string-inverter resizing. In essence, because string-inverter do not enable plug-and-play functionality, have low modularity, and are complicated to plan, their ease of use is inhibited.

## 1.5.2 Micro-Inverter System Configuration

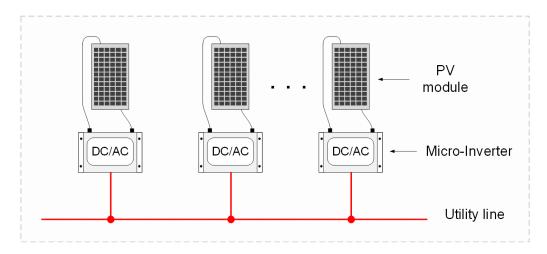

The MLPE-string setup from the previous section represents progress towards solving the issues plaguing string-inverter systems. By decoupling MPPT from DC-AC power conversion at the panel level, it solves the issues of sub-optimal MPPT. However, it disappoints by relying on centralized DC-AC conversion. MIs are essentially MLPE DC-AC devices that convert a single panel's DC energy into AC energy, synchronized with the utility grid. This introduces full system decentralization as well as plug-and-play functionality [7]. Since a MI focuses on an individual panel, the system requires as many MIs as there are solar panels, reflected in Figure 1-6, which

shows the basic setup of a MI system [7]. The name "Micro-Inverter" signifies the devices' low power handling capability, as each MI only processes a fraction of the system power (around 200 to 400 W). Yet, despite such low power handling, the MI design process is much more involved than designing string-inverter [12].

Figure 1-6. MI system configuration, adapted from [7]

First, MIs are intended to be paired with individual solar panels, and reside on rooftops, where harsh environmental conditions complicate their mechanical and thermal design [12]. Then the MI (unlike a string-inverter) must boost the voltage of an individual panel to match the peak of the utility grid [8], [12], and, the MI is still tasked with MPPT and power decoupling [12]. Finally, due to the distributed nature of the system and high number of devices, MIs might include extra control- and auxiliary- electronics to synchronize AC outputs together, and with the utility grid [12]. Despite these challenges however, the advantages of using MIs include unlocking full system modularity, removing single-point failure, and simplifying planning or upgrade processes. From a homeowner's perspective, these benefits outweigh design difficulties, hence, MI design attracts a lot of research attention.

#### 1.5.3 AC Modules – Enabled by MIs

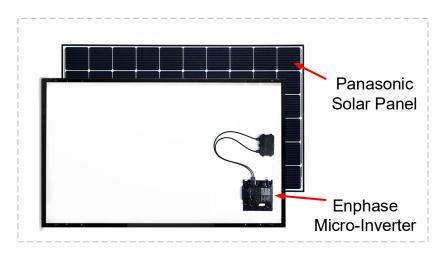

An AC module is a modular device consisting of a solar panel physically bonded to a MI. For example, Figure 1-7 shows the Panasonic N330E HIT ® AC module, which combines a Panasonic HIT ® panel, with an Enphase IQ 7X MI [36]. The AC module is so called because it has no DC terminals and is intended to be used as an AC device through the inverter output terminals.

Figure 1-7. An Enphase-Panasonic AC module [36]

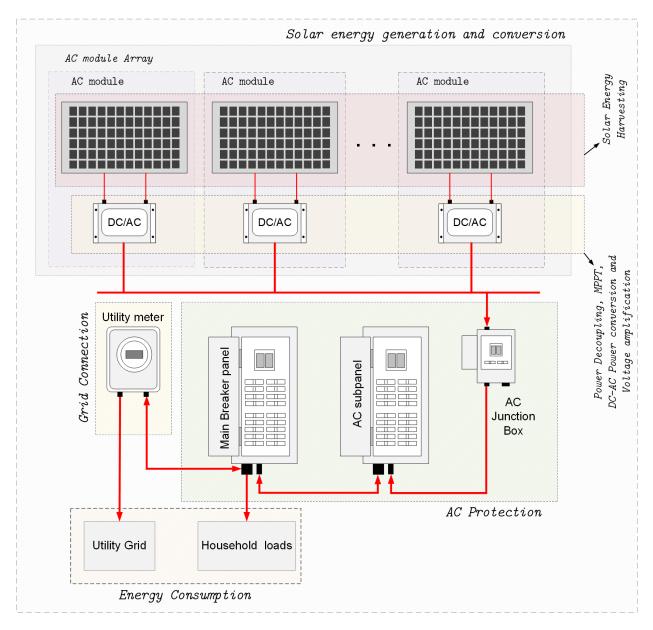

AC modules simplify wiring and present the opportunity to be used in "plug-and-play" fashion. Figure 1-8 presents the simplified schematic of an installation using AC modules [37]. Compared with the string-inverter scheme of Figure 1-4, the system is much more user friendly. Each module connects in parallel, through to an AC junction box, and onwards to the utility grid and household loads. A branch may contain up to 15 AC modules sharing one junction box, limited only by the protective current ratings of the subsequent AC breaker. The system is characteristically modular, such that a project could start as one AC module, build up to the maximum modules per branch, and further to multiple branches. The only limit will be the number of breakers in the AC sub panel, and these expansions could be carried out with minimal rewiring, recalculations, and no resizing of components as in string-inverter based systems. By using AC modules, the system also avoids the use of DC protection equipment.

Figure 1-8. PV system schematic with AC modules, adapted from [37]

#### 1.5.4 Comparisons between PV System Configurations

The average residential solar installation will vary in capacity from 2 to 10 kW<sub>DC</sub> [34], while a single residential grade solar panel produces around 200 to 400 W [9], [10]. This results in a system size of 5 to 50 panels. The system configuration and inverter choice are therefore a critical factor for the overall system cost, ease of installation and system reliability. Table 1-1 summarizes the comparison of residential solar installation options, the discussion of which continues below.

| PV configuration | Control<br>level | Modularity | System efficiency | Inverter serviceability | System cost | Inverter type   |

|------------------|------------------|------------|-------------------|-------------------------|-------------|-----------------|

| Standard string  | String<br>level  | Low        | Low               | Easy                    | Low         |                 |

| Multi-string     | String<br>level  | Good       | Low               | Easy                    | Moderate    | String inverter |

| MLPE-string      | Module<br>level  | Better     | Better            | Easy                    | High        |                 |

| Micro-inverter   | Module<br>level  | Best       | Best              | Difficult               | Highest     | Micro-inverter  |

Table 1-1. Comparison of PV system configurations

String-inverter systems are less user friendly, offer lower modularity, potentially complex planning/installation and possibly inhibited MPPT performance (impacting system efficiency), when compared with MIs. However, by being more pocket friendly, string-inverters have the cost advantage [35]. MLPE systems including the MLPE-string and MI setups improve system reliability by using a distributed architecture and improve efficiency with panel level MPPT. However only the MI setup avoids single point failure. Both MLPE systems also command greater acquisition and installation costs than alternatives.

In terms of modularity, the MI triumphs because of its use in plug-and-play AC modules, which simplifies upgrades and decommissioning of damaged panels. The MLPE-string setup is not far behind, retaining capability of the latter feature but not the former. In terms of efficiency, lack of panel level MPPT hinders the standard-string and multi-string arrangements. While the double

power conversion (DC-DC and DC-AC cascade) of the MLPE-string places it behind the potential singular DC-AC power conversion of the MI system.

However, the MI system falls short in serviceability and system cost. Cost is driven up by design complexity and total number of units required per project. While serviceability is impacted because the solar panel is bundled with the inverter as a roof-mounted AC module. Hence, inverter access is not as easy compared with garage- or utility closet- residing string-inverters. The MLPE-string benefits from the easy inverter access of the string-inverter for servicing but follows right behind MI systems with high costs. MLPE-string optimizers are not as complex to design, but multiple units are needed for the project leading to high costs.

Lastly, the failure of a single MI or AC module panel does not cause a single-point failure as with String-inverter, hence it is still more reliable, and faulty AC modules can be taken out of service to operate the system at lower capacity, without losing efficiency. In contrast, damaged panels in a string-inverter system must be bypassed with diodes placed in the path of full string current and reducing efficiency. Ongoing MI research, including this thesis aim to tackle some MI challenges, in hopes that the cost disadvantage of MIs may become a distant memory.

## 1.6 Thesis Structure

This thesis is organized in 6 chapters. A brief introduction and summary of each chapter follows below, and part of the work presented in this thesis is included in the conference paper:

H. K. Umar-Lawal, C. Ngai Man Ho, and K. K. Man Siu, "An Isolated Single-Stage Single-Phase Micro-Inverter Topology with Integrated Magnetic Components," 2019 IEEE Energy Conversion Congress and Expo. ECCE 2019, pp. 4339–4344, 2019.

**Chapter 1: Introduction**: Chapter one opens the thesis by presenting research problem and scope, followed by background information related to the research work. An overview of residential solar installations is provided, to outline inverter technologies. Then, the concept of an AC module is introduced and discussed before the chapter concludes with a comparison of Inverter technologies.

Chapter 2: Review of the Flyback Micro-Inverter Topology: Chapter two presents a review of FB MI topologies found in research literature. First it distinguishes between single-stage and two-stage topologies as background information for introducing the FB topology as a single-stage MI topology. Then three variants of the FB MI topology are explored briefly, with their operating principles. A discussion of the challenges faced by FB MIs, and comparison between the variants concludes the chapter.

Chapter 3: The Isolated Manitoba Inverter Topology: Chapter three introduces the Isolated Manitoba Inverter (ISOMBI) topology and its operating principles. Operation modes are based on the positive and negative cycles of the grid voltage, and demonstrate crafty use of functionally integrated magnetic components. Magnetic device models are explained, to explore properties that facilitate functional integration. Steady-state characteristics prove that the ISOMBI can

#### Chapter 1 - Introduction

function like conventional FB MIs, and detailed derivation principles are presented for calculating circuit parameters.

Chapter 4: The Isolated Manitoba Inverter Control System: Chapter four details the proposed control system design for the ISOMBI topology. Starting with small-signal dynamic modelling, a procedure is prescribed for designing the control system. The small-signal modelling is verified by simulation and numerical analysis. Finally the controller implementation is presented as a double loop digital compensator using a Digital Signal Processor (DSP). The chapter closes with flowchart descriptions of DSP algorithms.

Chapter 5: Prototyping and Experimental Verification – Chapter five presents experimental results obtained from the research work. The experimental prototype and its specifications are detailed, including constructive results for magnetic component design. Then the experimental setup and measurement instruments are introduced briefly. Finally, measurement waveforms and other experimental data is presented to support theories proposed in chapters 3 and 4.

Chapter 6: Conclusion and Future work Recommendations – Chapter six concludes the thesis, with a reflection and evaluation of the work done in respect to prescribed themes. It discusses and summarizes experimental results, and looks to the future for improvement opportunities. This chapter closes the thesis and is followed by the Bibliography.

# Chapter 2 - Review of the Flyback Micro-Inverter Topology

#### 2.1 Overview of FB MIs

MI topologies are judged by their conversion efficiency, component count, harmonic injection, reliability, power density and isolation [6], [12], [25], [26]. The FB MI is a choice topology that ranks highly in almost all categories. It has built-in galvanic isolation through its FB transformer, is capable of high efficiency operation, enjoys a low component count, and can maintain low TDD, with high reliability [25], [26], [38]–[40]. The FB MI is also a single-stage topology, that transforms DC power to AC power, using a single power processing stage. In most reviewed literature, however the FB MI circuit is rarely used above 200 W [8], [13], [38]–[41], mainly because it is difficult to design an efficient high power FB transformer [13]. The topology is further held back by high peak current stresses and voltage clamping requirements, [5], [38]–[43]. These factors combine to necessitate interleaving for increasing FB MI power ratings.

Single-stage power processing allows the FB MI to maintain a low component count, essential for high reliability and superior power density. Likewise, built-in galvanic isolation is highly desirable. Consider for instance, the US National Electrical Code (NEC) 690 standard, which calls for system grounding and monitoring of solar panels operating above 50 V [8]. Some high-capacity solar panels may operate between 50 and 60 V. Meanwhile, the AC service entry of a residential electrical system is already grounded, so adherence to the standard leads to dual grounding. In non-isolated systems, dual grounding introduces lossy leakage currents [8], [44] [26], but the low interwinding capacitance of a FB transformer is extremely effective at preventing leakage current flow [7], [26]. Also, the enhanced safety leads some electricity boards forgo solar panel grounding altogether in the presence of galvanic isolation [8], and lastly, isolated topologies have been observed to achieve lower TDD, when compared to non-isolated counterparts [26].

#### 2.2 Single-Stage vs Two-Stage MIs

Generally, MI topologies can be divided into single-stage (like the FB MI) and two stage [12], [25], [26]. The key difference between single and two-stage MIs, besides the number of power processing stages and task distribution between them, is where the power decoupling capacitor is placed [8]. Both are reviewed briefly to provide background information for introducing FB MI variants as single-stage topologies.

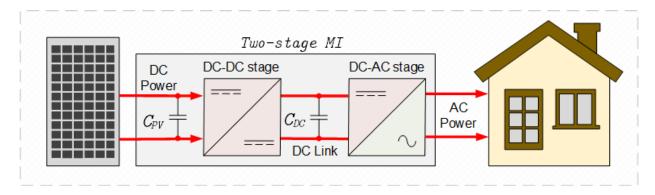

In a two-stage MI topology, illustrated in Figure 2-1, an input DC-DC conversion stage handles voltage amplification and MPPT, while grid current control is tackled by a subsequent DC-AC converter. Passive power decoupling is inherently built into the intermediate DC link capacitor, which does not need to be large because the DC link voltage is relatively high (few 100 volts), and the ripple requirement is loose (few 10's of volts). The DC-DC stage is often an isolated topology to reap the safety benefits of galvanic isolation and minimize leakage currents.

Figure 2-1. Two-stage MI illustration

This configuration allows both stages to be optimized individually, with the control objectives distributed amongst the two stages. Whilst this greatly simplifies the design procedure, the power losses incurred from two High-Frequency (HF) power processing stages negatively affects the total conversion efficiency, and housing two HF power converters also increases component count, resulting in both bulkiness and higher costs.

#### Chapter 2 - Review of the Flyback Micro-Inverter Topology

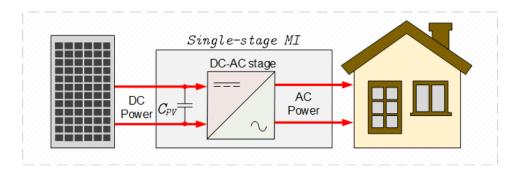

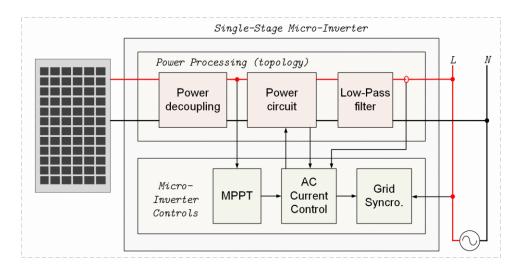

The single-stage MI depicted in Figure 2-2 performs all its functions in a single power conversion. This poses some unique challenges to the designer. First, the power decoupling capacitor must necessarily be placed on the PV side ( $C_{PV}$  in Figure 2-2), to meet ripple requirements for acceptable MPPT function [8]. Then the control system design must manage MPPT, voltage amplification and DC-AC conversion through a single HF power processing stage. Figure 2-3 shows the detailed system diagram of a single-stage MI, which is divided into the topology (power processing) and its associated control system. The topology is further divisible into power decoupling, power circuit (DC-AC switching stage) and a low-pass filter to smooth the output current. The MI controls consists of MPPT, grid synchronization and an AC current control algorithm, used to shape the grid current while transferring maximum possible power.

Figure 2-2. Single stage MI with PV side decoupling, adapted from [8]

Figure 2-3. Single stage MI detailed system diagram

#### Chapter 2 - Review of the Flyback Micro-Inverter Topology

Because the decoupling capacitor is placed on the PV side, where the input voltage is low (10's of volts) and the ripple requirement is tight (few volts), the required capacitance tends to be relatively large (few millifarads), and energy dense electrolytic capacitors become the obvious choice. However, these electrolytic capacitors do not fare well in the harsh rooftop environment, where an AC module MI will operate. The ambitious objectives of single-stage MI topologies also tend to result in unconventional arrangements, which become difficult to model and control.

The FB MI is popular because it is viewed as one of the simplest single-stage MI topologies. However, even the FB MI has control challenges, because a varying Right-Half-Plane (RHP) zero in its main Continuous Conduction Mode (CCM) control-to-output transfer function [40], [41] makes it difficult to guarantee control stability over the entire range of operation. This often results in designers choosing to operate the FB MI in the Discontinuous Conduction Mode (DCM), where the current stresses are higher than observed in CCM and may result in lower efficiencies [41].

Table 2-1. Comparison Summary of Single and Two-Stage MI topologies

|                 | Efficiency | Power Density | Cost   | Reliability |

|-----------------|------------|---------------|--------|-------------|

| Single stage MI | Higher     | Higher        | High   | Lower       |

| Two-stage MI    | High       | Good          | Higher | Higher      |

Table 2-1 summarizes the key differences between single-stage and two-stage MI topologies. Single-stage MIs have better efficiency and power density thanks to their single power conversion. Both are costly (relative to string-inverters), but two-stage MIs are generally more expensive than single-stage MIs. Also, the application of electrolytic power decoupling capacitors impacts the reliability of single-stage MIs, compared with two-stage MIs that can naturally use smaller film capacitors. The single-stage MI challenges are well known, and receive a lot of research attention, specifically aimed at the FB MI that has been recognized for its simplicity, and potential to dominate the single-stage MI category [8], [25]. For instance, active power decoupling techniques,

that allow the use of smaller and more reliable film capacitors have been developed [45]. While, modelling and control techniques that promote CCM operation are also popular topics [38]–[41].

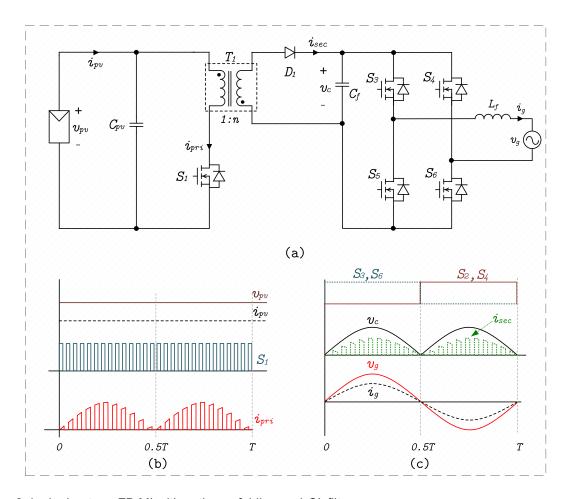

### 2.3 FB MI Topology Variants

The FB MI is based on the popular DC-DC FB topology, but with a modification that replaces the FB output with a pseudo-DC link, whose potential difference is a sinewave (sometimes rectified), coupled to the utility grid through a line frequency unfolding circuit and low-pass filter. The basic variant of the FB MI topology is shown in Figure 2-4(a). Its pseudo-DC link output is a rectified sinewave, where an active full bridge unfolding circuit and *CL* filter are placed, to deliver continuous low ripple current to the grid [40].

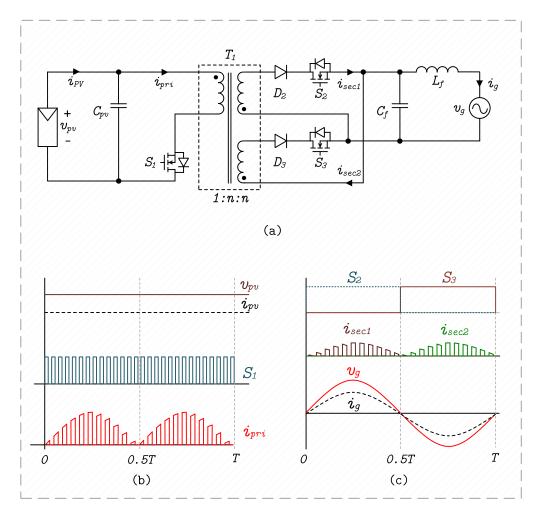

Figure 2-4. single-stage FB MI with active unfolding and *CL* filter (a) Topology (b) Primary side operating waveforms (c) Secondary side operating waveforms

#### Chapter 2 - Review of the Flyback Micro-Inverter Topology

By switching  $s_1$  at High frequency (HF), the control system shapes the primary current ( $i_{prl}$ ) into a HF waveform that has a squared-sine envelope (Chapter 3 shows why it is a squared-sine envelope). Then the HF current is transferred through the FB transformer ( $T_1$ ) to the secondary side as  $t_{sec}$ , where it is unfolded by the full bridge circuit, smoothed by a low-pass CL filter (formed by  $c_f$  and  $t_f$ ) and fed to the grid ( $t_g$ ). The full bridge switches  $t_g$  and  $t_g$  and  $t_g$  and  $t_g$  conduct on the negative cycle. The FB transformer is always used in a step-up configuration, and this considerably helps the control system of the FB MI achieve its voltage amplification objective. The FB MI can be operated in either CCM or DCM. In DCM, the primary switch is subjected to high current peaks. Hence DCM might lead to lower efficiencies [41]. However, control system design in CCM is more complicated, due to the presence of a varying RHP zero on the control (duty cycle) to output (grid current) transfer function [40], [41]. This RHP zero makes it difficult to optimize controller gain and guarantee stability for the whole range of operation [39], [41].

It should be noted that even during CCM operation, the primary current always appears discontinuous. The nature of a FB circuit is such that ampere-turns (MMF) transfer back and forth between windings of the FB transformer, which functions like a coupled-winding-inductor. Given this context, the operation is defined as CCM when the total ampere-turns of primary and secondary windings never dwell at zero [46]. The FB action also generates another problem for this topology. Only energy stored in the magnetizing inductance is transferred to the output as ampere-turns travel back and forth between primary and secondary windings, while energy stored in the leakage inductance does not [42], [43]. All FB transformers, no matter how well constructed, will have non-zero leakage inductance because it is impossible for windings to occupy the same physical space, as needed for lossless energy transfer between them [47].

#### Chapter 2 - Review of the Flyback Micro-Inverter Topology

If no alternate path is provided for the leakage energy, it diverts to the semiconductors, where it resonates with parasitic capacitances to trigger HF ringing and voltage spikes, which then cause Electromagnetic Interference (EMI) issues and threaten semiconductor breakdown. It is therefore necessary to include voltage clamps in the design to limit such voltage spikes and attenuate resonant ringing. On the primary side, an RCD clamp is often used, which consists of a parallel resistor-capacitor branch placed in series with a diode across the primary winding. The leakage energy is then diverted by the diode into the capacitor and subsequently discharged into the resistor. A similar idea is applied on the secondary but using an RC clamp across the secondary diode. By including a resistor, these types of clamps are dissipative and impact both efficiency and ability to scale power ratings. Thus some researchers have been looking into less-dissipative and energy recycling active clamps [48].

Another popular variant of the FB MI is depicted in Figure 2-5. In this configuration, a three-winding transformer is used, with one primary and two secondary windings. This allows for a simpler unfolding circuit because each of the secondary windings receives the ampere-turns transferred from the primary for only half of the line cycle (positive or negative) [41]. Hence, just two switches are needed to activate the appropriate secondary winding, in place of the four-switch full-bridge unfolder included in the first variant. On the positive cycle,  $S_2$  conducts the HF current ( $I_{sec1}$ ) and connects  $I_2$  to the FB switching cell, whilst on the negative cycle  $I_3$  conducts the HF current ( $I_{sec2}$ ) and connects  $I_3$  to the FB switching cell. As such, the pseudo-DC link FB voltage is a full sinewave. The fundamental FB MI control tasks remain similar, where the primary current ( $I_{pri}$ ) is shaped into a HF waveform with a squared-sine envelope, and the transformer still aids with voltage amplification.

Chapter 2 - Review of the Flyback Micro-Inverter Topology

Figure 2-5. Centre-tapped transformer variant of the FB MI (a) Topology (b) Primary side waveforms (c) Secondary side waveforms

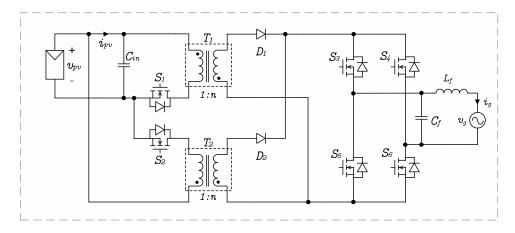

The FB MI variants of Figure 2-4 and Figure 2-5 both use a single HF switch and will subsequently be referred to collectively as non-interleaved FB MI variants. The final variant to be discussed is HF-interleaved variant of the FB MI circuit, presented in Figure 2-6. In this circuit, two non-interleaved FB MIs (of the type in Figure 2-4) are HF-interleaved and share a Pseudo-DC link output where their currents add up for filtering and grid consumption. The advantages of HF-interleaving are that both circuits will share the load equally, while reducing input and pseudo-DC link voltage ripples [38]. Taken individually, each FB MI circuit works as described previously for the non-interleaved circuit in Figure 2-4, but the HF switching commands for  $S_1$  and  $S_2$ , must be complementary to avoid transistor shoot through, and are therefore phase-shifted by 180°.

Chapter 2 - Review of the Flyback Micro-Inverter Topology

Figure 2-6. HF-Interleaved variant of the FB MI

The HF-interleaved variant of the FB MI is valued because it can double the power rating of a similarly constructed non-interleaved FB MI, and it does so while reducing ripples on the input voltage and output current. However, the power rating boost comes with increased component count and concurrent use of two HF switches. Table 2-2 presents a comparison between the reviewed variants of the FB MI and the ISOMBI topology, which uses LF-interleaving and will be introduced in the next chapter.

Table 2-2. Comparison of FB MI variants, with the ISOMBI.

| Tamalami              | Typical<br>Power<br>Range | Semiconductors |              |                   | Magnetic | Copper  | 0    | T-4-1 |

|-----------------------|---------------------------|----------------|--------------|-------------------|----------|---------|------|-------|

| Topology              |                           | HF<br>Switch   | LF<br>Switch | Discrete<br>Diode | core     | Winding | Caps | Total |

| Basic FB MI           | 160-250                   | 1              | 4            | 1                 | 2        | 3       | 2    | 10    |

| Centre tapped variant | 160-250                   | 1              | 2            | 2                 | 2        | 4       | 2    | 9     |

| Interleaved FB<br>MI  | 160-500*                  | 2              | 4            | 2                 | 3        | 5       | 2    | 13    |

| ISOMBI                | 160-500*                  | 2ª             | 6            | 0c                | 2        | 4       | 2    | 12    |

<sup>&</sup>lt;sup>a</sup> The HF switches do not operate concurrently

<sup>&</sup>lt;sup>c</sup> The anti-parallel diodes of LF IGBTs are incorporated into the proposed topology

<sup>\*</sup>Theoretical projection from similarly equipped non-interleaved variants

#### Chapter 2 - Review of the Flyback Micro-Inverter Topology

At first glance, comparing the 13-count total of the HF-interleaved FB MI variant with the others seems trivial. However, Magnetic components are often the bulkiest singular components in a power converter and eliminating one can boost power density whilst also reducing costs [13]. The HF-interleaved FB MI uses 3 Magnetic cores with 5 windings, compared to 2 cores and 4 winding maximums for the others and is the only variant that operates two HF switches simultaneously, requiring extra control arrangements. Depending on the control implementation, this could either be additional auxiliary electronics (analog controller) or extra computation (digital controller). With the LF-interleaved ISOMBI, HF switches are not operated simultaneously, keeping a simple control structure, and using integrated magnetic devices avoids the extra magnetic device. The next chapter introduces the ISOMBI and provides a detailed breakdown of its steady-state characteristics and parameter derivations.

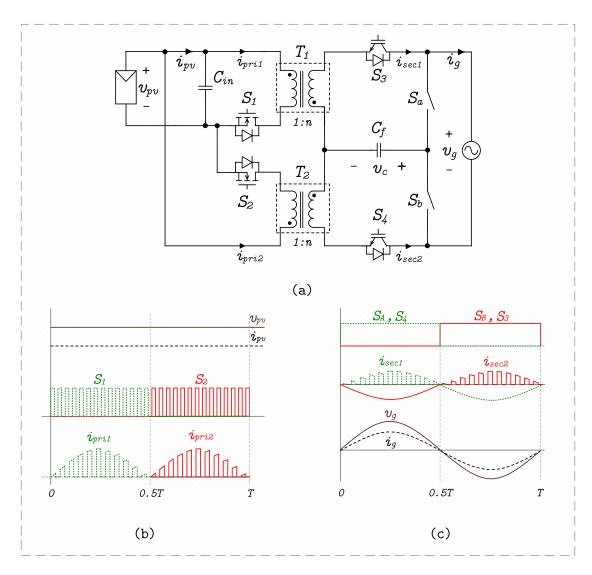

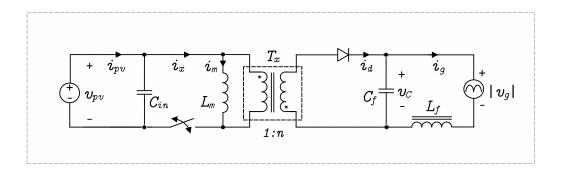

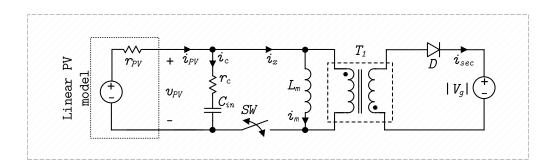

The proposed Isolated Manitoba Inverter (ISOMBI) topology is a current unfolding FB MI topology which uses LF-interleaving and functionally integrated magnetic devices. This chapter introduces the ISOMBI, depicted in Figure 3-1 with key operating waveforms, by detailing its operating modes, integrated magnetics function, steady-state characteristics, and circuit parameter derivations. Part of the work presented in this chapter is included in [49]

Figure 3-1: Isolated Manitoba Inverter topology (a) Topology (b) Primary waveforms (c) Secondary waveforms

# 3.1 Operating Principles

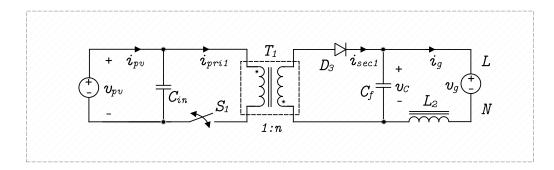

The ISOMBI shares some characteristics with the HF-interleaved FB MI of Figure 2-6 by including two FB circuits that share the power processing duties equally. However, since they are LF-interleaved, the ISOMBI operates only one HF switch at any time. This is reflected in the key operating waveforms of Figure 3-1(b), where on the positive cycle,  $S_1$  is the primary HF switch, transferring energy across  $T_1$ , while on the negative cycle  $S_2$  is the primary HF switch transferring energy across  $T_2$ .

$T_1$  and  $T_2$  are functionally integrated magnetic devices, which means they perform two distinct functions in the same circuit. From Figure 3-1(c), switches  $S_a$ ,  $S_b$ ,  $S_3$  and  $S_4$  are synchronized with the line cycle, leading to the circuit configurations of Figure 3-2, where, on the positive cycle,  $T_1$  and  $T_2$  are FB transformer and grid filter inductor respectively, and on the negative cycle the roles reverse with  $T_1$  as grid inductor and  $T_2$  as FB transformer. This shows in the waveforms of Figure 3-1 (c), where the secondary windings of the magnetic devices conduct HF current and smooth grid current on alternating line cycle periods. In this way the devices integrate the functions of FB transformer and grid inductor into one component.

Figure 3-2. ISOMBI circuit configurations in (a) Positive line cycle, and (b) Negative line cycle

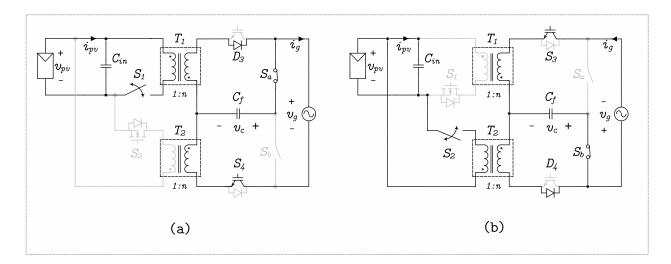

#### 3.1.1 Positive line Cycle Operation

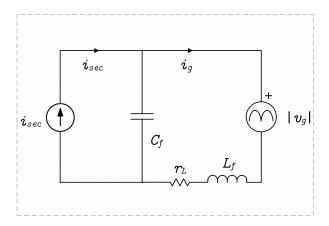

From Figure 3-2, the positive line cycle circuit configuration of the ISOMBI can be further reduced to the equivalent circuit of Figure 3-3. In this mode,  $S_1$  is the HF switch and  $T_1$  is the FB transformer, while bidirectional switch  $S_a$  is gated ON to connect the line terminal of the grid to the filter cap  $C_f$ , and  $S_4$  is gated ON to incorporate the secondary winding of  $T_2$  (denoted  $L_2$  in Figure 3-3) into a CL filter with  $C_f$ . The second bidirectional switch  $S_b$ , and  $S_2$  are gated OFF to disconnect the negative cycle FB circuit during the positive cycle, and finally,  $S_3$  is gated OFF, but its antiparallel diode (denoted  $D_3$  in Figure 3-3) completes the FB switching cell. Given this configuration, the positive line cycle equivalent circuit is a FB MI whose output is a pseudo-DC link that delivers low ripple current to the grid through a CL filter.

Figure 3-3. ISOMBI Positive line cycle equivalent circuit

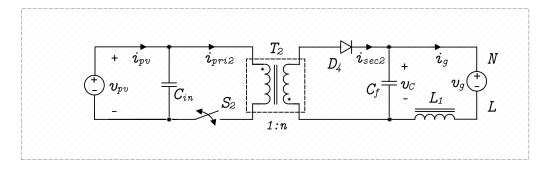

### 3.1.2 Negative line Cycle Operation

From Figure 3-2, the negative line cycle circuit configuration of the ISOMBI can be reduced to the equivalent circuit of Figure 3-4. In this mode,  $S_2$  is the HF switch and  $T_2$  is the FB transformer, while bidirectional switch  $S_b$  is gated ON to connect the neutral terminal of the grid to the filter cap  $c_f$ , and  $S_3$  is gated ON to incorporate the secondary winding of  $T_1$  (denoted  $T_2$  in Figure 3-4) into a  $T_2$  filter with  $T_2$ . The second bidirectional switch  $T_2$  are gated OFF to disconnect the positive cycle FB circuit during the negative cycle, and finally,  $T_2$  is gated OFF, but its anti-parallel diode (denoted  $T_2$  in Figure 3-3) completes the FB switching cell. Given this configuration, the negative

line cycle equivalent circuit is also a FB MI, whose output is a pseudo-DC link that delivers low ripple current to the grid through a *CL* filter.

Figure 3-4. Negative line cycle equivalent circuit

### 3.1.3 Summary of Operating Principles

The positive and negative line cycle equivalent circuits show that the ISOMBI is a FB MI variant, and the functions of FB transformer and grid inductor are integrated into singular components. This is achieved by creating a virtual reference point where the secondary windings of  $T_1$  and  $T_2$  intersect, which becomes the virtual ground reference of the pseudo-DC link voltage. The switches  $S_a$ ,  $S_b$ ,  $S_3$  and  $S_4$  are used to maintain the virtual ground, by reconfiguring the output filter based on the line cycle, such that potential difference,  $v_c$ , across the pseudo-DC link capacitor  $(c_f)$  is always positive, and the output current unfolds into the grid appropriately. On the primary side  $S_1$  and  $S_2$  are the primary HF switches respectively for the positive and negative line cycles. With the described switching sequences, the ISOMBI topology shares power processing responsibility between two HF switches and can potentially match the power ratings of the HF-interleaved topology, but it also keeps the simplicity of operating only one HF switch at a time.

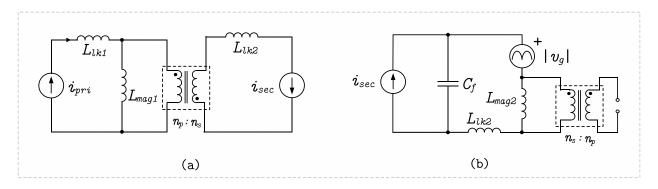

## 3.1.4 Integrated Magnetics

In FB transformer mode, the magnetic devices do not actually perform transformer action as implied by its name. Proper transformer action involves an instantaneous transfer of energy between primary and secondary, with little or no storage in between [47]. Instead, the FB

transformer functions as a coupled-winding inductor, where multiple windings share the same magnetic core and transfer energy between each other with intermediate magnetic energy storage [47]. Energy from the input is stored in the magnetic core (and airgaps), through the primary winding's ampere-turns (MMF) and later retrieved from the secondary winding's ampere-turns, as controlled by the switching cell [46], [47]. Neither winding claims total control of the ampere-turns, and the device cannot be designated as a singular proper inductor. However, the magnetic core (and airgaps) is exposed to the total ampere-turns ripple and behave like a single inductor core [46]. In this way, the FB transformer device acts as a coupled-winding inductor.

The construction of a FB transformer as a coupled-winding inductor is exploited by the ISOMBI in FB transformer mode. However, the same device is used as grid filter inductor, where the primary winding is completely disconnected, and the secondary winding is statically connected to the circuit. This allows the secondary winding to dictate the total ampere-turns seen by the magnetic core (and airgaps) and behave like a single-winding inductor that stores and retrieves energy from the magnetic domain (core and gaps) through the same winding. Also, since voltage amplification is one of the functions of the MI, the FB transformer is applied with a step-up ratio between primary (input) and secondary (output) windings, meaning that the secondary inductance is a significant multiple ( $n^2$ , where n is the turns ratio between primary and secondary) of the primary inductance [50]. This reinforces its capability as grid inductor, because the large secondary inductance is desirable for filtering ripples in the grid current.

Figure 3-5 depicts the functional integration of the magnetics device, the illustration simplifies the ISOMBI operation by only representing the current flows around the magnetics. In Figure 3-5(a), the magnetic device functions as a FB transformer, using both windings to work as a coupled-winding inductor, while Figure 3-5(b) uses only the secondary as a single-winding grid inductor.

Figure 3-5. Integrated magnetics functionality, (a) as coupled-winding inductor in FB transformer mode, and (b) as single-winding grid filter Inductor

Figure 3-5 also illustrates relevant magnetic parameters.  $L_{mag1}$  and  $L_{mag2}$  are the respective magnetizing inductance values of the primary and secondary windings, while  $L_{lk1}$  and  $L_{lk2}$  are the respective leakage inductance values for the primary and secondary windings. In FB transformer mode,  $L_{mag1}$  models the magnetic energy storage, while  $L_{lk1}$  and  $L_{lk2}$  are parasitic elements, which introduce undesired ringing and voltage spikes. In grid inductor mode, however,  $L_{mag2}$  represents the single-winding inductance, but this time  $L_{lk2}$  is not a parasitic, because it increases the grid filter inductance value (although not significantly,  $L_{mag2}$  is typically 100's of  $\mu H$ , while  $L_{lk2}$  is few  $\mu H$ ) and is good for filtering. In summary, by exploiting the coupled-winding inductor magnetic properties of a FB transformer, the ISOMBI can use the same magnetic device as FB transformer and grid Inductor, thus the component is said to be functionally integrated.

### 3.2 Steady-State Analysis

In the previous section, the positive and negative line cycle equivalent circuits of the ISOMBI were shown to be analogous. Hence, the FB circuit of Figure 3-6 is presented as a generic equivalent circuit for analyzing the steady-state characteristics of the ISOMBI.

Figure 3-6. ISOMBI steady-state equivalent circuit

In this equivalent circuit, the ideal transformer is placed in parallel with a magnetizing inductor,  $L_m$ , which models the non-zero core reluctance (energy storage) of a practical FB transformer [51]. The grid voltage is replaced by an equivalent rectified sinewave  $v_g$ , the currents  $i_{pv}$ ,  $i_x$ ,  $i_m$ ,  $i_d$  and  $i_g$  represent the PV current, primary current, magnetizing current, secondary current, and grid current respectively,  $v_{pv}$  is the PV voltage,  $v_c$  is the pseudo-DC link voltage, n is the turns ratio of FB transformer  $T_x$ ,  $C_{in}$  is the power decoupling capacitor,  $L_f$  is the grid filter inductor, and  $C_f$  is the pseudo-DC link/filter capacitor. The steady-state analysis includes expressing the duty ratio, magnetizing current and pseudo-DC link voltage in terms of circuit parameters. Two basic assumptions are consistently applied throughout the steady-state analysis of the ISOMBI topology. First, a distinction is to be made between AC-steady-state and quasi-steady-state, followed by a discussion of the operating mode of the topology, described in terms of the magnetizing current.

#### 3.2.1 Steady-State Analysis Assumptions

The MI output is an AC voltage or current, which causes the MI operation to vary according to the utility grid's AC period. However, because the MI is controlled under HF switching, and the switching period (10's of micro-seconds) is very much smaller than the AC line period (10's of milliseconds), the converter can be justifiably said to settle into a "quasi-steady-state" around instants of the AC period that are much larger than the switching period [41]. Similarly, AC-steady-state is observed in the quantities that change on the order of the line cycle and maintain a uniform period. To complete AC-steady-state analysis, it is assumed that the input power decoupling capacitor is large enough that the input,  $v_{pv}$ , remains constant over an AC cycle and can be used with other AC-Steady-State variables. In summary, AC-steady-state variables change significantly on the order of the line cycle period, while quasi-steady-state variables change significantly on the order of the switching period.

The second concept examines the operation mode, characterized by the current conducted through the FB transformer. When operated with a constant switching frequency, the FB MI is either in DCM or CCM [38], [40]. In DCM, the total ampere-turns of the FB transformer windings is allowed to reach and/or remain at zero during operation, while in CCM mode the total ampere-turns of FB transformer windings never reach or dwell at zero [46]. However, complete CCM operation over the line cycle is never certain because the FB MI inexorably slips into DCM around zero-crossing instants of the AC line cycle [40], [41], Hence CCM is more appropriately called a "hybrid mode" because it has both CCM and DCM scenarios.

It should be noted that regardless of operating mode, the current in individual windings of the FB transformer is highly discontinuous [46]. This is typical of FB action, where the current transfers back and forth (or "flies-back") between primary and secondary windings at the switching frequency [46]. The operating mode of a FB topology is therefore determined by the total ampereturns of all windings and not of individual winding currents. The proposed ISOMBI is intended to

be a CCM design and quasi-steady-state principles will be combined with AC-steady-state variables to describe its steady-state characteristics, such as duty ratios, CCM magnetizing current, CCM primary switch current, and CCM pseudo-DC link voltage. Lastly, it is assumed throughout the analysis, that the ISOMBI meets its design objective and delivers only real power via a continuous in-phase sinusoidal grid current.

### 3.2.2 Pseudo-DC link Voltage

#### a) Pseudo-DC link Average Voltage (AC-steady-state variable)

The Pseudo-DC link voltage is the output voltage of the ISOMBI circuit. It is assumed that the MI's output AC current is sinusoidal, and in phase with the grid voltage. Hence the MI only sends real power across the filter inductor. Equation 3-1 expresses the inductive power transfer relation.

$$P_o = \frac{|V_c||V_g|}{\omega_o L_f} \sin \delta$$

3-1

Where:  $P_o$  - Real output power

$V_c$  - Peak amplitude of Pseudo-DC link voltage

$V_a$  - Peak amplitude of grid voltage

$\omega_o$  - Nominal grid frequency in radians

$L_f$  - Output filter inductance value

$\delta$  - Phase difference between pseudo-DC link voltage and grid voltage

The variables  $V_c$ ,  $V_g$  and,  $\omega_o$  in equation 3-1 are known to be of the same order of magnitude (few 100's). Hence, we can say  $sin\delta$  is directly proportional to  $L_f$ . Since we know that  $L_f$  is small in magnitude (100's of  $\mu H$ ), it follows that  $sin\delta$ , and consequently  $\delta$ , are also small. This small phase difference means there is minimal voltage drop across  $L_f$ , and the average pseudo-DC link voltage is somewhat equal to the grid voltage. Hence:

$$v_c(t) \approx |v_a(t)| = V_a |\sin(\omega_a t)|$$

3-2

Where:  $v_c(t)$  - Average pseudo-DC link voltage

$v_q(t)$  - Instantaneous grid voltage

#### a) Pseudo-DC link Voltage Ripple

Based on the circuit of Figure 3-6, when the primary switch is in the *ON-state*, the grid current can be expressed by equation 3-3:

$$\left|i_g(t)\right| = C_f \frac{\Delta v_c(t)}{D(t)T_s}$$

3-3

Where:  $i_q(t)$  - Instantaneous grid current

$C_f$  - Output filter capacitor value (also pseudo-DC link capacitor value)

D(t) - Duty ratio

$\Delta v_c(t)$  - Pseudo-DC link voltage ripple

$T_s$  - Switching period

From this, it is easy to calculate the Pseudo-DC-Link Voltage ripple as:

$$\Delta v_c(t) = \frac{|i_g(t)|D(t)}{f_s C_f}$$

3-4

Where:  $f_s$  - Switching frequency

### 3.2.3 Primary Magnetizing Current

#### a) Average Primary Magnetizing Current (AC-Steady-State variable)

The average magnetizing current represents the amount of energy (average ampere-turns) transferred to the magnetic domain. It can be derived through quasi-steady-state averaging of the Pseudo-DC link capacitor current. Referring to the circuit of Figure 3-6, this is found as:

$$\langle i_c(t) \rangle_T = \frac{-|i_g(t)|D(t)T_s + \left[ (-i_m(t)/n) - |i_g(t)| \right] (1 - D(t))T_s}{T_s} = 0$$

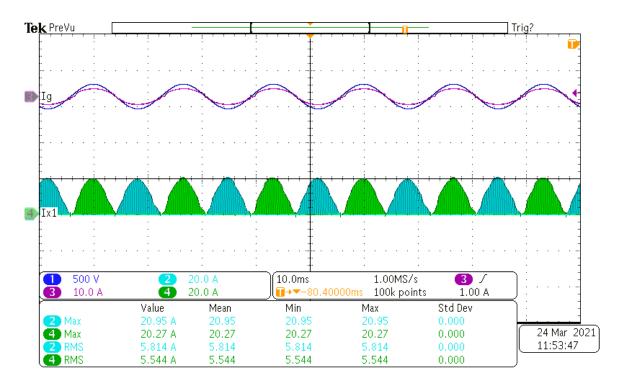

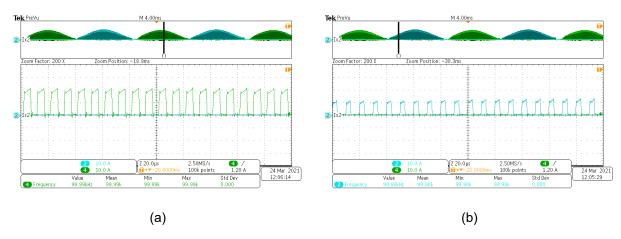

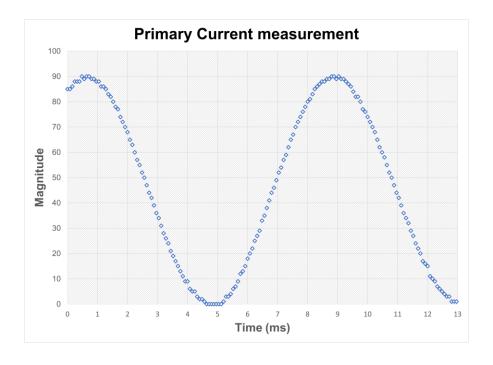

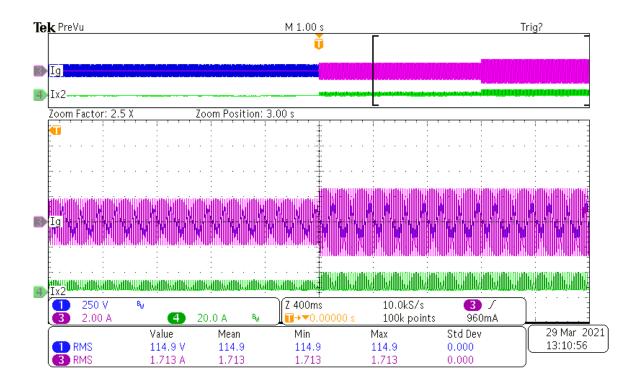

3-5