# Adaptive Phase Locked Loops for VSC connected to weak ac systems

By

Mita Babu Narayanan

A Thesis submitted to the Faculty of Graduate Studies of

The University of Manitoba

in partial fulfillment of the requirements for the degree of

# **Master of Science**

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg, Manitoba, Canada

Copyright © 2015 by Mita Babu Narayanan

#### **Abstract**

The performance of the High voltage dc systems is dependent on the stiffness of the ac bus, it is connected to. With the traditional synchronous reference frame-phase locked loops (SRF-PLL), voltage source converters (VSC) systems with large PLL gains, connected to weak ac networks are shown to be prone to instabilities, when subject to disturbances. Thus, for weak ac systems the plausible operating range for the traditional SRF-PLL is limited.

In this thesis a new Adaptive PLL is designed. This PLL has a frequency adaptive 'pre-filter' architecture, designed to extract the fundamental positive sequence component of the input voltage, to be fed into the traditional SRF-PLL for tracking of its phase angle. The pre-filter comprises of frequency adaptive proportional resonant (PR) filters and all-pass filters, to extract only the fundamental positive sequence component. Compared with other traditional PLL topologies, this Adaptive PLL shows superior immunity to voltage distortions and negative sequence, and also has a faster dynamic performance.

To include the Adaptive PLL into the VSC control system, the control system parameters are optimized. Non-linear Simplex Nelder-Mead algorithm is used for optimization of the control parameters. A modified approach for the objective function formulation, which allows for finer control and improved dynamic performance, has been presented.

The thesis presents a comparative analysis of the performance of the traditional SRF-PLL with the Adaptive PLL in a VSC control system, and its impact on stability for VSCs connected to weak ac systems. In a VSC system, the reduced sensitivity of the system stability, to the PLL gain variation of the Adaptive PLL, is demonstrated.

Further, several tests were devised to compare the stability with the inclusion of the above mentioned PLL designs. Using Electromagnetic Transient Simulation, it is shown that the VSC equipped with the Adaptive PLL can operate into very weak ac systems (i.e. SCR≈1.3) more stably in comparison with widely used SRF-PLL.

# Acknowledgements

I would like to express my deep sense of gratitude to Prof. Aniruddha Gole, for his continued guidance during the course of this research. To work under you and experience your enthusiasm for research, first hand, has been a privilege.

I would also like to thank Prof. Udaya Annakkage for the invaluable knowledge that he imparted during the course work. I would also like to acknowledge the contribution of Dr. Tomas Yebra Vega and Dr. X. Chen when I needed their guidance the most.

Lastly, I would like to thank my friends and family, for their seamless patience and support.

# **Dedication**

To my beloved Mother.

# **Table of Contents**

| Abstract                                               | i    |

|--------------------------------------------------------|------|

| Acknowledgements                                       | iii  |

| Dedication                                             | iv   |

| Table of Contents                                      | V    |

| List of Figures:                                       | ix   |

| List of Tables:                                        | xii  |

| List of Abbreviations:                                 | xiii |

| Chapter I: Introduction                                | 1    |

| 1.1 Background                                         | 1    |

| 1.2 Project objective and outline of this thesis       | 4    |

| 1.3 Scientific contributions of this thesis            | 6    |

| Chapter II: VSC HVdc Systems: Transmission and Control | 7    |

| 2.1 Introduction and background of HVdc                | 7    |

| 2.1.1 Types of HVdc systems:                           | 9    |

| 2.2 VSC: Operation and control                         | 13   |

| 2.2.1 Components of the VSC HVdc system:               | 15   |

| 2.2.2 Pulse width modulation                           | 18   |

| 2.   | 2.3    | Capability curves for VSC:                      | . 22 |

|------|--------|-------------------------------------------------|------|

| 2.3  | Cor    | ntrol system for the VSC                        | . 23 |

| 2.   | 3.1    | Vector current control:                         | . 24 |

| 2.   | 3.2    | Power angle control:                            | . 35 |

| 2.4  | Sur    | nmary                                           | . 35 |

| Chap | ter II | I: Design and Analysis of the Adaptive PLL      | . 36 |

| 3.1  | Pha    | se Locked Loops: Background and architecture    | . 36 |

| 3.   | 1.1    | Significance of the PLL in a VSC control system | . 37 |

| 3.   | 1.2    | Anatomy of typical PLL:                         | . 38 |

| 3.2  | Tra    | ditional d-q-z PLL                              | . 40 |

| 3.   | 2.1    | Architecture:                                   | . 40 |

| 3.   | 2.2    | Problems with the d-q-z PLL                     | . 41 |

| 3.3  | Me     | thodology                                       | . 42 |

| 3.4  | Des    | sign of the Adaptive PLL                        | . 44 |

| 3.   | 4.1    | Fundamental component filter:                   | . 44 |

| 3.   | 4.2    | Positive sequence filter:                       | . 46 |

| 3.   | 4.3    | Synchronous reference frame–PLL (SRF-PLL):      | . 47 |

| 3.5  | Dyı    | namic performance analysis of the Adaptive PLL  | . 48 |

| 3.   | 5.1    | Optimization of the PLL parameters:             | . 48 |

| 3.5   | 5.2    | Dynamic response studies and performance analysis under distorted volta  | ige  |

|-------|--------|--------------------------------------------------------------------------|------|

| cond  | itions | S:                                                                       | . 48 |

| 3.6   | Sur    | nmary                                                                    | . 56 |

| Chapt | ter IV | 7: Optimization of the VSC Controls                                      | . 58 |

| 4.1   | Intr   | oduction and background                                                  | . 58 |

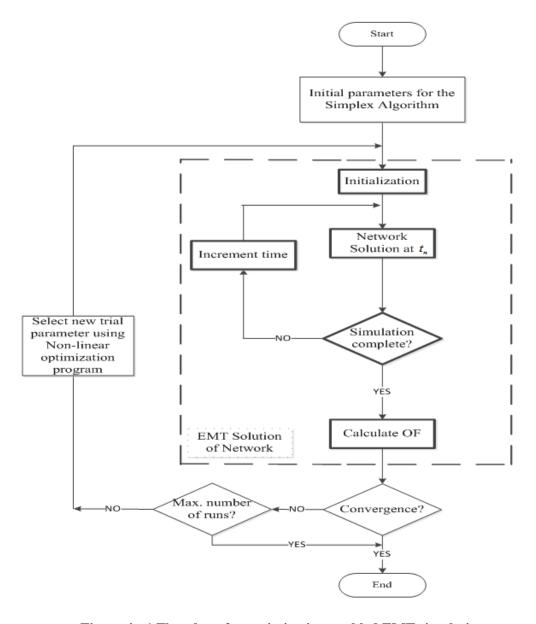

| 4.2   | Opt    | timization enabled EMTS                                                  | . 60 |

| 4.2   | 2.1    | Optimization algorithm: Non-linear Simplex Nelder-Mead method            | . 63 |

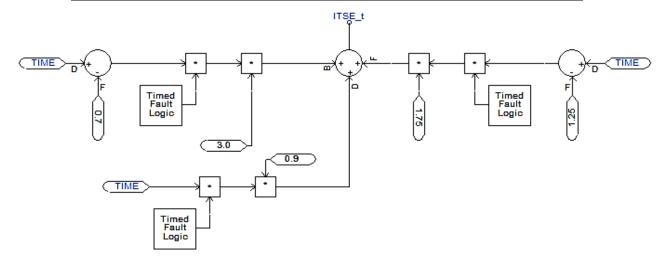

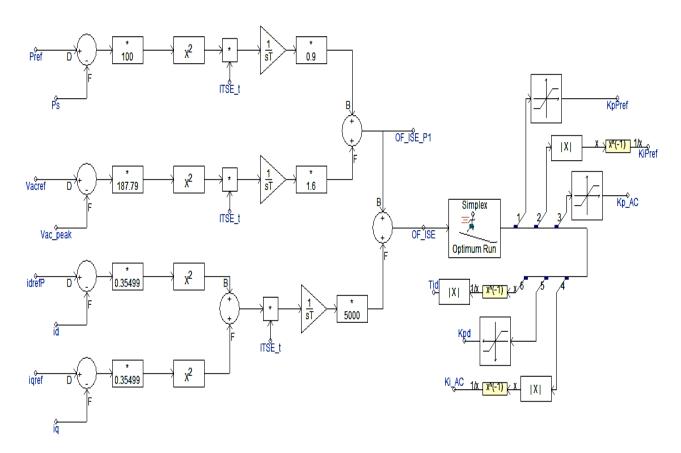

| 4.3   | For    | mulation of the objective function (OF)                                  | . 64 |

| 4.3   | 3.1    | Selection of weights for optimization                                    | . 66 |

| 4.3   | 3.2    | Initial parameters and tolerance setting for the Simplex algorithm       | . 68 |

| 4.4   | Res    | sults and analysis                                                       | . 69 |

| 4.5   | Sur    | nmary                                                                    | . 71 |

| Chapt | ter V  | : Adaptive PLL for the VSC                                               | . 72 |

| 5.1   | Intr   | oduction and background                                                  | . 72 |

| 5.1   | 1.1    | Stability of VSC                                                         | . 73 |

| 5.1   | .2     | PLL and VSC                                                              | . 73 |

| Te    | st sys | stem:                                                                    | . 74 |

| 5.2   | Ope    | erating range for PLL                                                    | . 75 |

| 5.3   | EM     | IT Tests to study impact of the PLL architecture on the system stability | . 79 |

| 5.3   | R 1    | Variation of active power reference:                                     | 79   |

| 5.3.2     | Maximum transmissible Power:                                       | 82      |

|-----------|--------------------------------------------------------------------|---------|

| 5.3.3     | Sudden change in the SCR of the ac system:                         | 84      |

| 5.3.4     | Fault recovery ability, for symmetrical and asymmetrical faults at | the VSC |

| termin    | nals                                                               | 86      |

| 5.3.5     | Summary of the Simulation tests:                                   | 90      |

| 5.5 St    | ummary                                                             | 91      |

| Chapter ' | VI: Conclusions and Future Work                                    | 93      |

| 6.1 C     | Contributions and conclusions                                      | 93      |

| 6.2 Fu    | uture work                                                         | 95      |

| Reference | es                                                                 | 97      |

| Appendix  | <u> </u>                                                           | 101     |

# **List of Figures:**

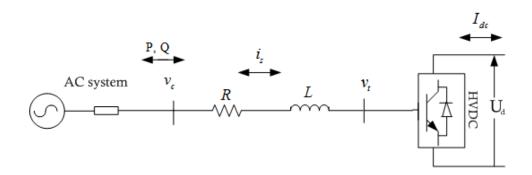

| Figure 2- 1 VSC terminal connected to an ac system                                     | 13  |

|----------------------------------------------------------------------------------------|-----|

| Figure 2- 2 Schematic of a two-terminal VSC system                                     | 15  |

| Figure 2- 3 Two-level converter topology                                               | 17  |

| Figure 2- 4 Equivalent circuit of the single terminal system, neglecting the ac filter | 19  |

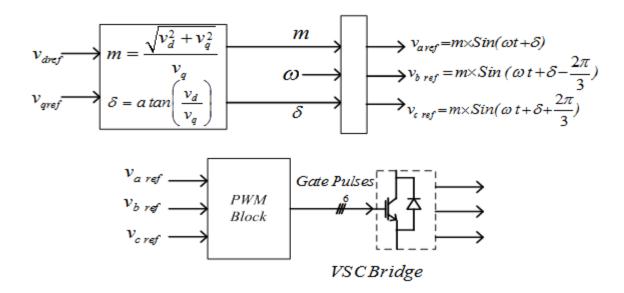

| Figure 2- 5 Generation of reference waveforms                                          | 20  |

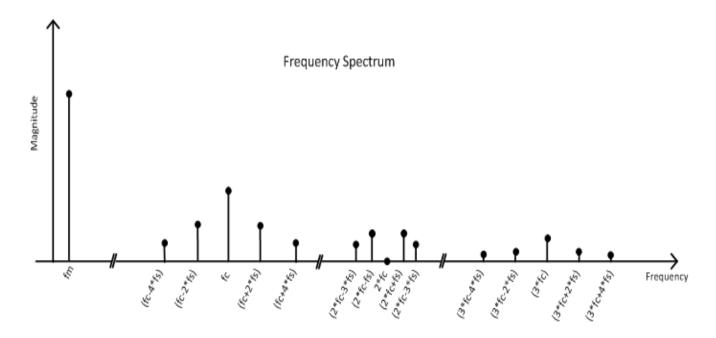

| Figure 2- 6 Frequency spectrum of the pulse width modulated waveform [25]              | 21  |

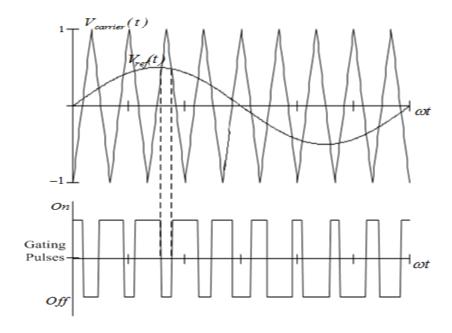

| Figure 2- 7 Generation of gating pulses for IGBT valves [taken by permission from H    | Vdc |

| course notes of Dr. A. M. Gole]                                                        | 21  |

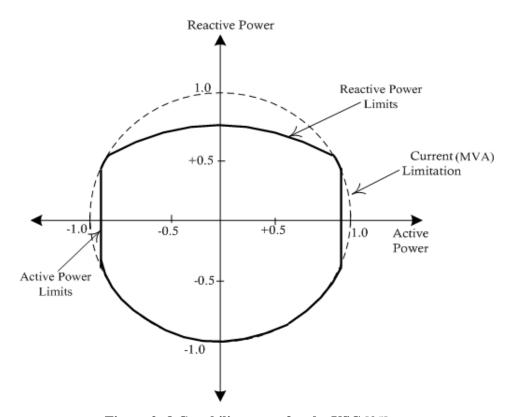

| Figure 2- 8 Capability curve for the VSC [35]                                          | 22  |

| Figure 2- 9 Simplified single line diagram of the HVdc system                          | 25  |

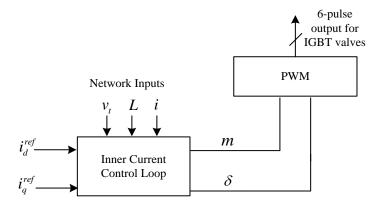

| Figure 2- 10 Conceptual Block diagram of the Inner current control loop                | 26  |

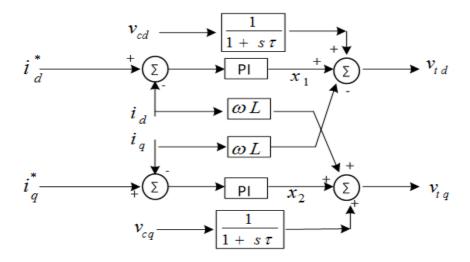

| Figure 2- 11 Inner current control of the Vector current control method                | 28  |

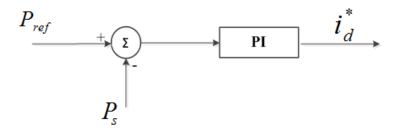

| Figure 2- 12 Active power control loop                                                 | 31  |

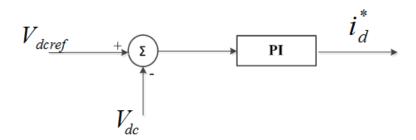

| Figure 2- 13 DC voltage control loop.                                                  | 31  |

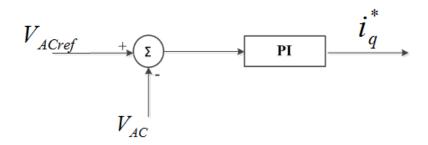

| Figure 2- 14 AC voltage control loop.                                                  | 32  |

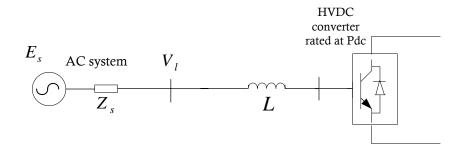

| Figure 2- 15 Equivalent representation of the HVdc system                              | 34  |

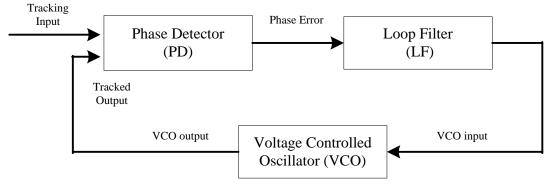

| Figure 3- 1 Schematic of a typical Phase Locked Loop [51]                              | 38  |

| Figure 3- 2 Synchronous Reference Frame PLL (d-q-z PLL) [51]                           | 40  |

| Figure 3- 3 Block diagram of the Adaptive PLL                                          | 44  |

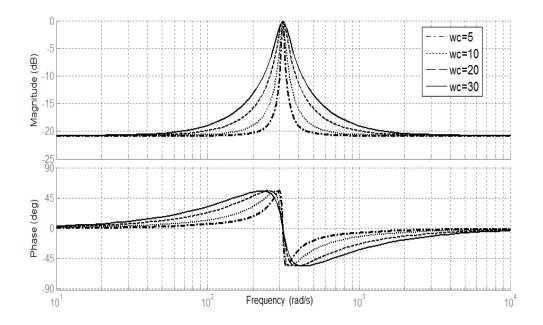

| Figure 3- 4 Frequency Response of the Proportional-Resonant (PR) filter with varying cut |   |

|------------------------------------------------------------------------------------------|---|

| off frequencies                                                                          | 6 |

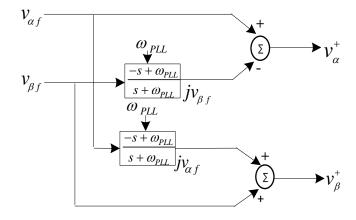

| Figure 3- 5 Control system of the positive sequence filter                               | 7 |

| Figure 3- 6 Synchronous reference frame PLL 4                                            | 7 |

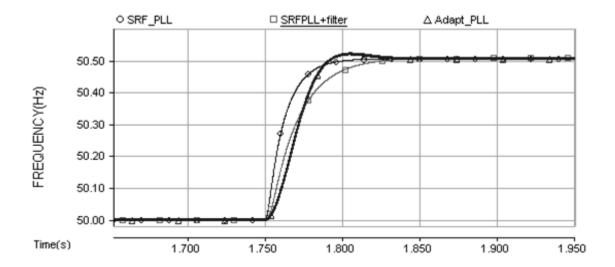

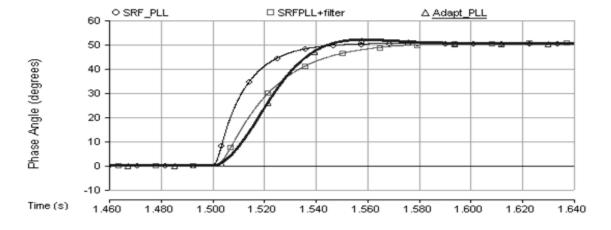

| Figure 3- 7 Step change in frequency of 1%                                               | 9 |

| Figure 3- 8 Step change in Phase angle of 50°                                            | 0 |

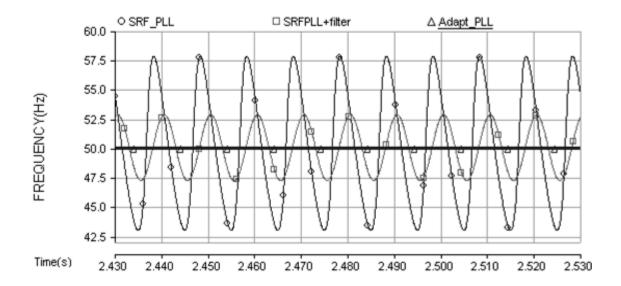

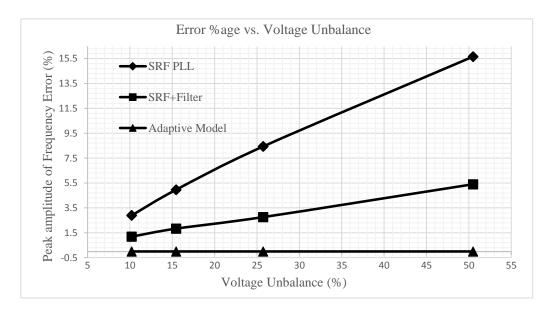

| Figure 3- 9 Frequency output of the PLL with 50% Voltage Unbalance in the input 5        | 2 |

| Figure 3- 10 Error Percentage in frequency vs. Percentage unbalance in voltage input 5   | 2 |

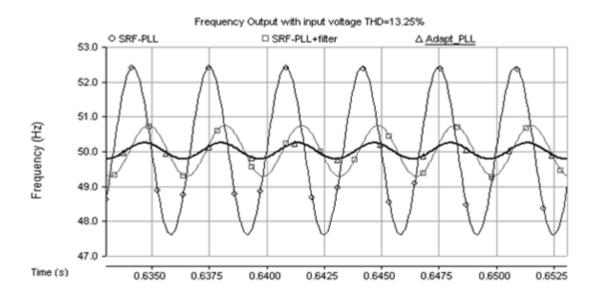

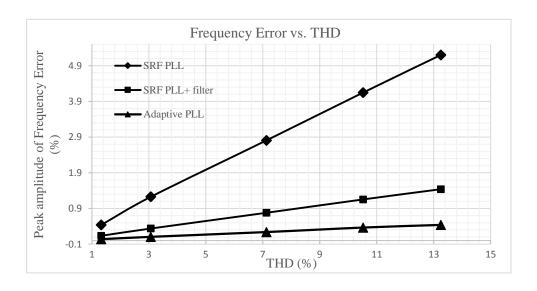

| Figure 3- 11 Frequency output of the PLL with input voltage THD=13.25%                   | 4 |

| Figure 3- 12 Error percentage in frequency vs. THD of the input voltage                  | 4 |

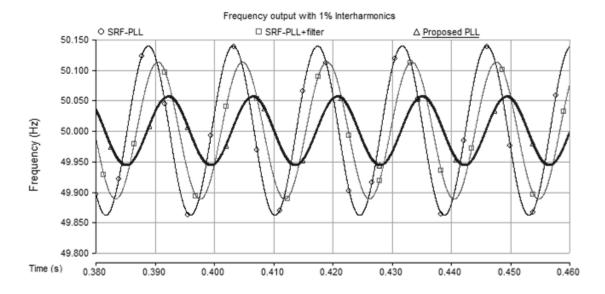

| Figure 3- 13 Output frequency with 1% interharmonics of 120Hz in the input voltage 5     | 5 |

| Figure 4 - 1 Flowchart for optimization enabled EMT simulation                           | 1 |

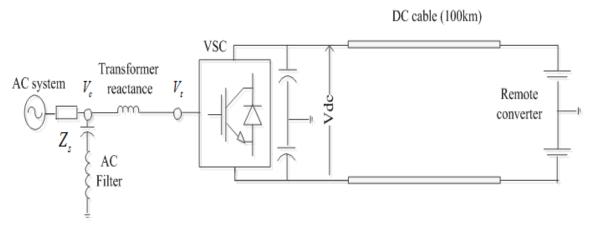

| Figure 4 - 2 Test network for the Single converter system                                | 2 |

| Figure 4 - 3 Block diagram to calculate the weighted time for the ITSE terms 6           | 7 |

| Figure 4 - 4 Block diagram for the OF calculation in OE-EMTS, showing each of the sub-   |   |

| objective functions6                                                                     | 8 |

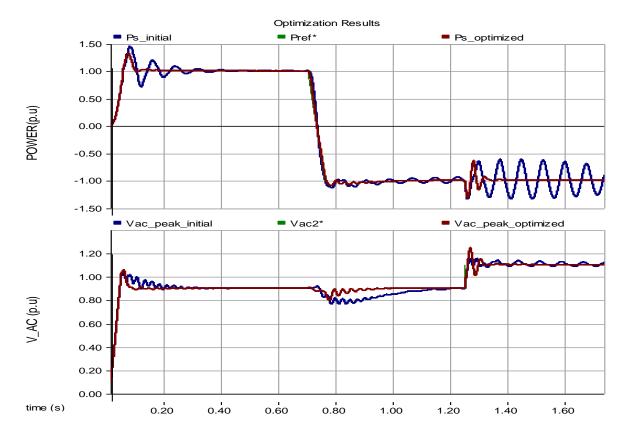

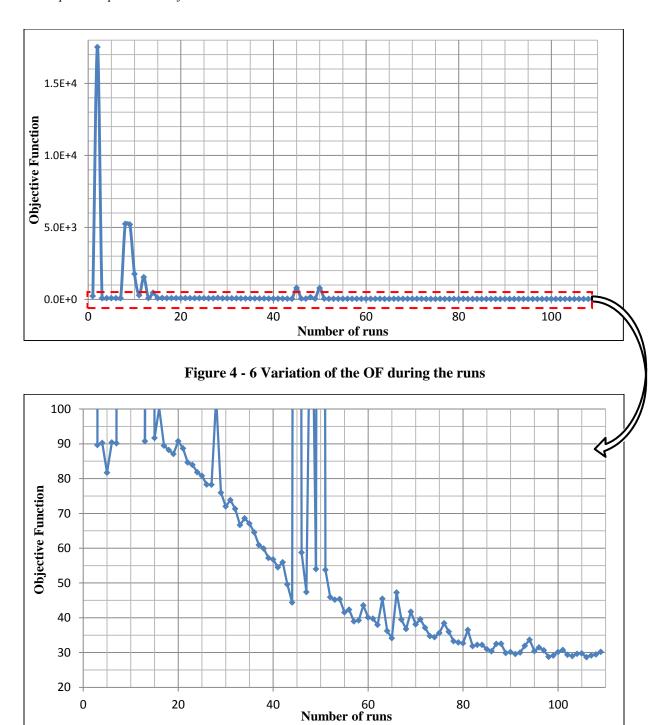

| Figure 4 - 5 Power and Voltage at the VSC terminals, prior to and after optimization 6   | 9 |

| Figure 4 - 6 Variation of the OF during the runs                                         | 0 |

| Figure 4 - 7 Zoomed in version of the OF variation using the Simplex method              | 0 |

| Figure 5 - 1 Single converter test system                                                | 5 |

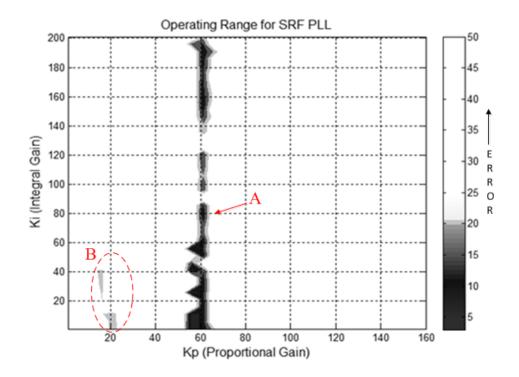

| Figure 5 - 2 Operating Range for SRF-PLL                                                 | 8 |

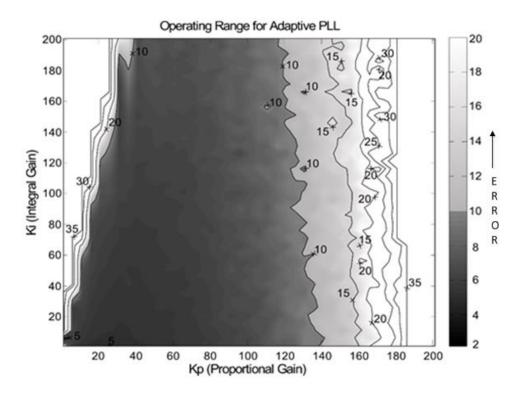

| Figure 5 - 3 Operating Range for Adaptive PLL                                            | 78 |

|------------------------------------------------------------------------------------------|----|

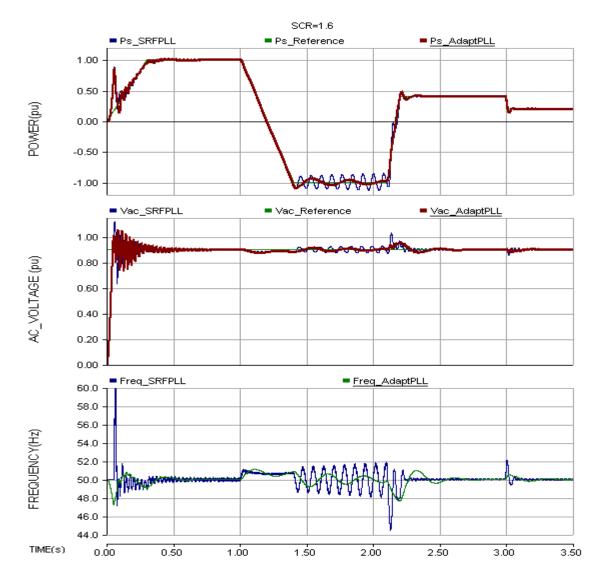

| Figure 5 - 4 Response to change in Power Reference to the VSC for SCR=1.6, with the      | e  |

| SRF-PLL and Adaptive PLL                                                                 | 80 |

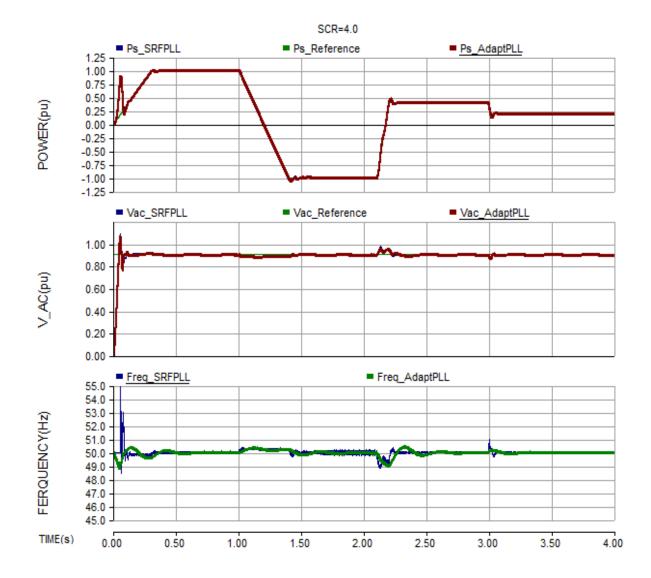

| Figure 5 - 5 Response to change in Power Reference to the VSC for SCR=4.0, with the      | e  |

| SRF-PLL and Adaptive PLL                                                                 | 81 |

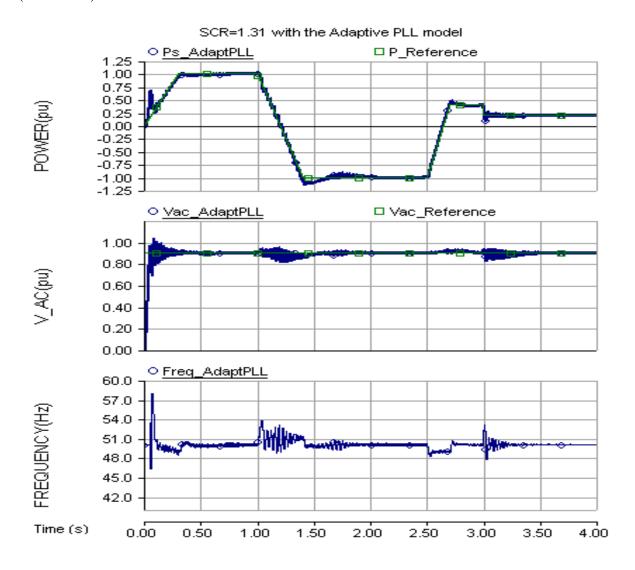

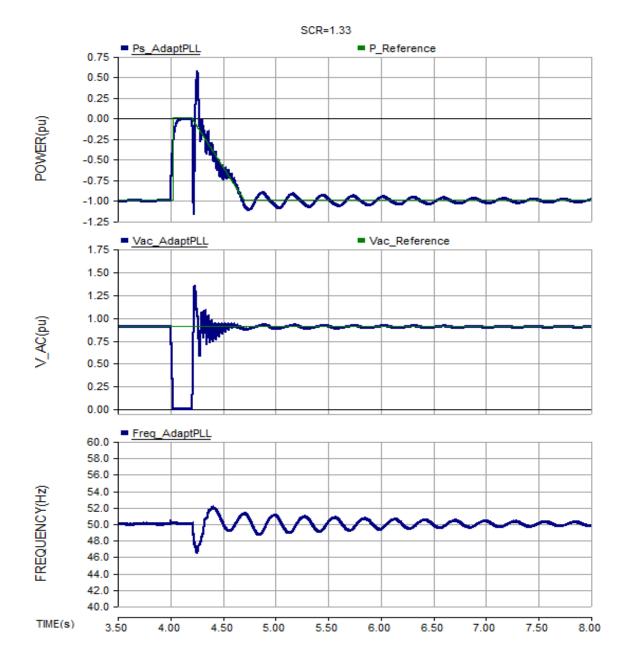

| Figure 5 - 6 Change in Power Reference to the VSC for SCR=1.31, with the Adaptive PLL    | 82 |

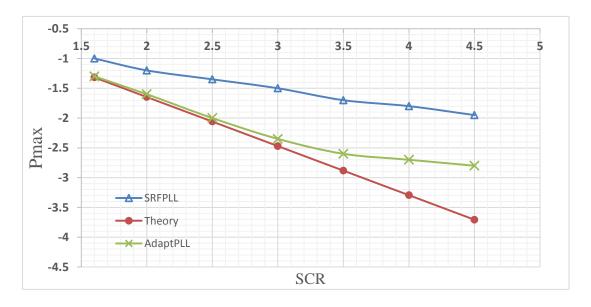

| Figure 5 - 7 Pmax vs. SCR of the ac system in the rectifier mode of operation            | 83 |

| Figure 5 - 8 Response to sudden change in the SCR of the ac system with the SRF-PLL an   | d  |

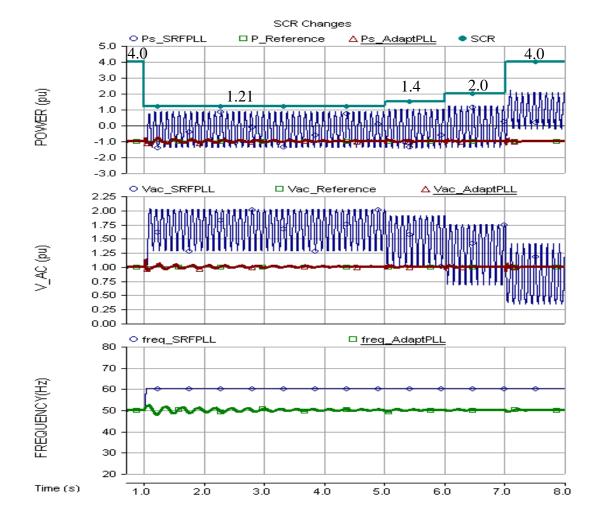

| Adaptive PLL                                                                             | 85 |

| Figure 5 - 9 Three Phase to ground at the VSC terminals, for SCR=4.0, with the SRF-PLI   | Ĺ  |

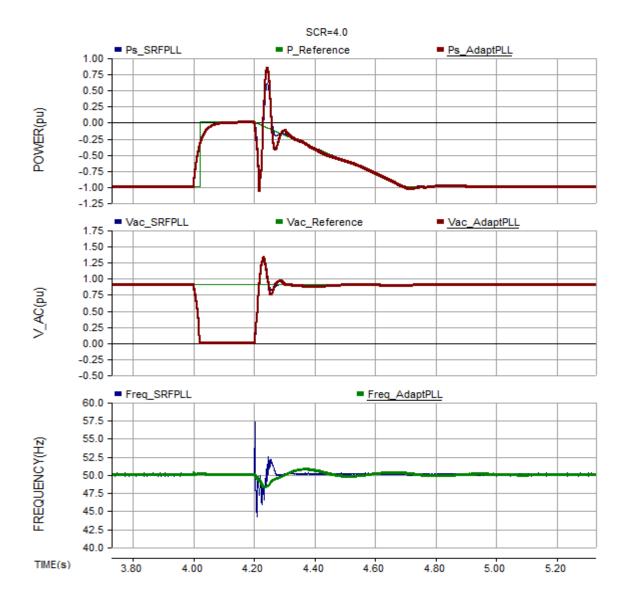

| and Adaptive PLL                                                                         | 87 |

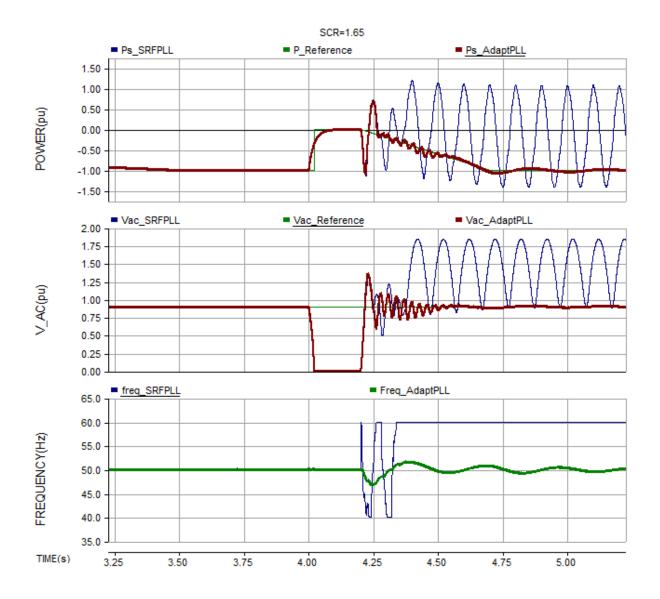

| Figure 5 - 10 Three Phase to ground at the VSC terminals, for SCR=1.65, with the SRF-PLI | L  |

| and Adaptive PLL                                                                         | 88 |

| Figure 5 - 11 Three phase to Ground fault at the VSC terminals, for SCR=1.33 with the    | e  |

| Adaptive PLL                                                                             | 89 |

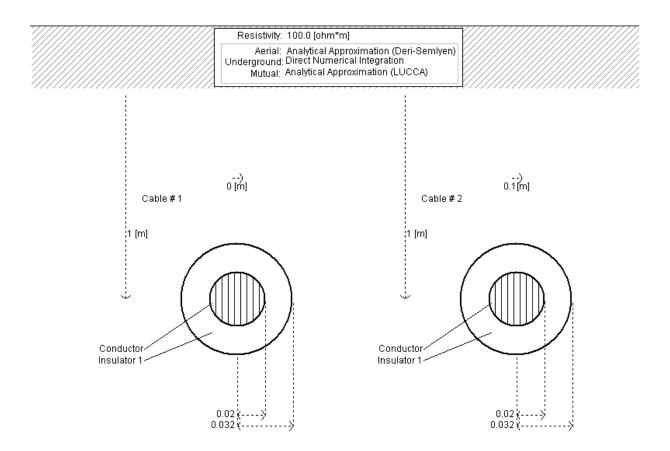

| Figure A- 1 Cross section of the DC cable model                                          | 02 |

# **List of Tables:**

| Table 3. 1 Dynamic Response for 1% step change in frequency                | 49  |

|----------------------------------------------------------------------------|-----|

| Table 3. 2 Optimized gains for the PLL                                     | 49  |

| Table 3. 3 Dynamic Response for 50 <sup>0</sup> step change in phase angle | 50  |

| Table 3. 4 Frequency Output for Input with 50% Unbalance                   | 51  |

| Table 3. 5 Input Voltage with Harmonic content                             | 53  |

| Table 3. 6 Frequency Output for Voltage input with THD=13.25%              | 53  |

| Table 3. 7 Frequency Output for Voltage input with 1% interharmonics       | 56  |

| Table 4. 1 Weights chosen for each individual disturbance                  | 67  |

| Table 4. 2 Weights chosen for each individual VSC control loop             | 68  |

| Table 4. 3 Initial and optimized PI gains for the VSC control loops        | 69  |

| Table A- 1 AC system parameters of the test network                        | 101 |

| Table A- 2 Bergeron model parameters                                       | 101 |

| Table A- 3 Coaxial cable parameters                                        | 101 |

## **List of Abbreviations:**

HVdc High Voltage Direct Current

VSC Voltage Source Converters

LCC Line Commutated Converters

CCC Capacitor Commutated Converters

SCR Short Circuit Ratio

ESCR Effective Short Circuit Ratio

PLL Phase Locked Loop

SRF Synchronous Reference Frame

PWM Pulse Width Modulation

SPWM Sinusoidal PMW

pu Per Unit

ITSE Integral of time multiplied by square of error

ISE Integral of square of error

THD Total harmonic distortion

PR Proportional Resonant

PI Proportional Integral

EMT Electromagnetic Transients

OE-EMTS Optimization Enabled EMT Simulation

# Chapter 1

#### Introduction

#### 1.1 Background

The Power System broadly comprises of three components, namely, generation, transmission and finally, the distribution network [1]. The generation largely comprises of synchronous generators in the grid, which are typically located in remote areas. Lately, with the advent of distributed generation, relatively smaller sources are now connected into the grid, allowing for the integration of cleaner sources of energy. In Canada, the main source of generation is hydro power [2] and hence, eco-friendly. Other popular traditional sources of power generation include thermal, gas and nuclear power plants, to list a few. Around the world, among the distributed generation sources, wind [3] [4] and solar farms [5] are fast becoming viable options.

The transmission system forms the conduit between the distribution network and the generators. High voltage ac systems are commonly used for transmission distances less than 500km [6], owing to their cheap cost. But, the integration of the renewable energy sources into the network has posed several challenges for network engineers, owing to the wide range of

frequency variations in these networks [4]. And thus, High Voltage DC (HVdc) systems are imperative for the inclusion of these sources into the network.

At present, HVdc transmission systems are the preferred choice for bulk transmission of power. The increased efficiency and improved voltage profile over long distance power transmission, are just some of the major advantages that this technology offers. Moreover, to cross large water bodies, DC cables [7] are the only solution. In Chapter 2, a comparison between HVac and HVdc systems has been provided.

The traditional line commutated converters (LCC) HVdc systems based on thyristors have served well for about six decades now [8]. There are several large projects currently in operation, based on the traditional LCC systems, including the collector system in Manitoba, (Bipole I and Bipole II), popularly known as the Nelson River System [9]. By controlling the firing angle of the LCC converters at either ends, it is possible to control the active power flow in the DC lines. At present, there are well established control systems for the LCC converters, even for contingency conditions. But, the requirement of additional reactive power support at the converter and also, the need for considerable filtering at the ac side (Chapter 2), are just some of the limitations of the LCC system.

Despite the increased installation costs, with the ability to independently control both the active and reactive power supply, voltage source converters (VSC) are fast becoming viable alternatives to the LCC systems. In contrast to the LCC, the VSC has several performance advantages, such as its reduced susceptibility to ac system disturbances and its ability to generate reactive power[6]. For reasons ranging from increased flexibility, in terms of the control system design (including DC grids), to easier integration of the renewable sources of generation into the power network, the future of VSC HVdc looks promising.

Based on self-commutated switches, the voltage source converter (VSC) HVdc allows for very high switching frequencies, ranging up to several kHz, thus eliminating the need for large ac filters. Especially, with the Modular Multilevel Converter (MMC) topology [10], the VSC can generate an almost perfect sinusoidal waveform, with no additional filtering required on the ac side. Alternatively, with the two-level converters the technique of pulse width modulation (PWM) is popularly used in VSCs to generate the firing pulses for the switching valves.

One of the main reasons for the large interest in the VSC technology is its ability to connect into weaker ac systems, compared to the LCC. The strength of the ac network connected to the converter is quantized by the Short Circuit Ratio (SCR) [8], which is defined as the ratio of the Short Circuit MVA (SCMVA) at the ac bus to rated power,  $P_{dc}$ , of the converter as shown in equation (1-1).

$$SCR = \frac{SCMVA}{P_{dc}} \tag{1-1}$$

For LCC systems it widely accepted that for SCR<2.5, (implying an ESCR≈2.0) the system is considered weak. In contrast, [11] defines this limit for networks connected to VSC systems to be SCR=1.6. Further, [11] also reported the results of the small signal studies on the VSC system, upon performing sensitivity studies on the impact of the control gains of the VSC on the overall system stability. Considering the nature of small signal studies, these results are optimistic in nature. The conclusions from [11], pointed to the significant impact that the PLL gains have on the stability when SCR of the ac system is greater than 1.6. These results formed the motivation for this research. In this thesis, a new Adaptive PLL design is developed, which works well under conditions where the VSC is connected to very weak ac

systems. It is also important to note, that the studies in this thesis are done on EMT software, PSCAD/EMTDC, which allows for detailed modeling of the non-linear VSC HVdc system.

#### 1.2 Project objective and outline of this thesis

Phase Locked Loop (PLL) tracks the phase angle and frequency of the fundamental positive sequence component of the input ac voltage. The PLL provides the reference phase angle for the VSC control system. Typically, the Synchronous reference frame PLL (SRF-PLL) is used. However, this has posed some stability issues when operating in weak ac systems. The emphasis of this thesis is to address the issue of the sensitivity of the VSC to the PLL, when it is connected to weak ac systems. This research aims to provide a solution in the form of a new PLL design, which shows good performance when providing the reference angle to VSC systems, even when they are connected to very weak ac system, up to SCR=1.31.

The broad outline of this thesis is as follows:

#### Chapter 1: Introduction

This chapter provides a brief introduction to HVdc systems and touches upon the organization of this thesis.

#### Chapter 2: VSC HVdc systems: Transmission and Control

In this Chapter, a comparison between the ac and dc systems is conducted, for bulk power transmission. The advantages of HVdc systems over the ac systems are categorized. The traditional LCC systems are contrasted with the VSC systems. The four quadrant operation of the VSC is explained, with in depth analysis of the dq-decoupled control system.

#### Chapter 3: Design and Analysis of the Adaptive Phase Locked Loop

Owing to the tracking errors with the SRF-PLL design, in the presence of voltage distortions in the input, it is essential to design a PLL architecture which can extract true phase angle output i.e., the fundamental positive component of the input voltage. In Chapter 3, a new Adaptive PLL design is introduced, which is designed to extract this component. The methodology and design for this PLL is presented. The criterion for the selection of PLL gain parameters is established. Further, the gains of the Adaptive PLL and that of the SRF-PLL and SRF-PLL+filter designs are optimized for good dynamic performance. Using these optimized gains, the comparison between them is done with distorted input voltages, including unbalance, harmonics and interharmonics.

#### Chapter 4: Optimization of the VSC Controls

Using the non-linear Simplex algorithm, the VSC control parameters are tuned using objective functions that quantify the dynamic performance of the VSC. This chapter explains the criterion for the formulation of the objective Function for the VSC terminal.

#### Chapter 5: Adaptive PLL for the VSC

Using the optimized controls from chapter 4, studies are done using the electromagnetic transient simulation program, EMTDC/PSCAD, to study the performance of the Adaptive PLL providing angle reference to the VSC control system, when connected into a weak ac system. The performance of the VSC is compared with the traditionally used SRF-PLL. Several large disturbance tests are formulated and studied, thereof, to establish the impact of the Adaptive PLL on the stability. It is proved that with the inclusion of the Adaptive PLL, the stability of the VSC system improves considerably for small as well as large disturbances, even when connected to very weak ac systems (SCR≈1.31).

#### Chapter 6: Conclusions and Future Work

This chapter lists the conclusions from this research. Also, possible future works are suggested.

#### 1.3 Scientific contributions of this thesis

- Development of a new Adaptive PLL design which can operate well under distorted voltage conditions, causing minimal errors in the phase and frequency output of the Phase Locked Loop

- Optimization enabled- electromagnetic transient simulation (OE-EMTS) based optimization of the VSC controller parameters enabling greater control over the final optimized parameters

- Study of the operating range for the standard SRF-PLL and the Adaptive PLL for VSCs connected to weak ac systems

- Demonstration of the improved immunity of the VSC to large disturbances when the Adaptive PLL design is used, with very weak ac systems

## Chapter 2

# **VSC HVdc Systems: Transmission and Control**

This Chapter begins with explaining the need for HVdc systems and certain distinct advantages it offers over its ac counterparts. The types of HVdc systems are introduced and the traditional LCC converters are contrasted with the VSC. Further, the components of typical VSC HVdc system are introduced. The various control systems employed typically in a VSC system are also explored. In addition, the Phase Locked Loops and their significance in the VSC control system is studied. Thereafter, the impact that the ac system parameters can have on the VSC performance is also discussed in brief.

### 2.1 Introduction and background of HVdc

The contest between ac systems and DC systems is an old one. Back in the 1880s, what is now known as, the 'War of currents' [12] commenced between Tesla, who championed the idea of ac networks, and Thomas Edison, of DC networks. Edison later went on to pioneer the first electrical network, with DC transmission at low voltages, in the year 1882. Soon after, there was a proliferation of ac systems, with the main advantage being the ease of voltage transformation to different levels, which proved beneficial long distance transmission. At

present, although most of the electrical network is ac, there is still a huge interest in High Voltage DC (HVdc) Transmission.

Commissioned in 1954, the first fully commercial HVdc scheme was installed in Gotland [13]. With a rating of  $100 \ kV$ ,  $20 \ MW$  the monopolar HVdc cable links the Sweden Mainland with the Gotland Island. The first Canadian HVdc link, however, went into service in 1969, a  $312 \ MW$ ,  $\pm 130 \ kV$  [14] scheme stretching 41km. At present, the longest HVdc link, still under construction is the 2071km long,  $\pm 800 \ kV$ , 6400 MW line connecting the Xiangjiaba Dam to Shanghai [15], in the People's Republic of China.

Despite the large installation costs of converters, HVdc Transmission systems find prominence due to certain distinct features that the ac systems cannot adequately measure up to or in some cases cannot offer. The salient points are discussed below [8]:

- <u>Interconnecting asynchronous networks</u>: Interconnecting two ac networks using an ac interconnection can result in undesired oscillations in voltage and power, following a disturbance [1]. HVdc systems provide a solution to this, since for interconnecting two networks through HVdc, the frequency and phase angle considerations, are not critical [8]. The back to back converter topologies allow for power transfer between asynchronous grids.

- <u>Integration of renewable energy sources</u>: Power generated from renewable energy sources such as solar and wind farms [16] [5], can have undesirable harmonics, voltage and frequency fluctuations. Connecting them directly into the ac network would have devastating effects on the loads connected in close proximity. HVdc provides the necessary interface to connect these sources into the network, without affecting the nearby loads.

- <u>Undersea cables</u>: Due to large charging currents in ac cables (for lengths greater than 50 km), it is not a practical solution to use them, for long distance transmission, such as undersea links. The HVdc cables form the only plausible solution in such cases.

- Reduced right of way (ROW) for transmission corridors: For places where land acquisition can be difficult, HVdc proves to be beneficial, considering the reduced ROW it requires, compared to ac transmission lines, for the same power level.

- Absence of reactive power consumption in transmission lines: One of the primary advantages of DC transmission is that there are only resistive losses in the DC lines. In contrast, for ac lines in long distance transmission, large reactive power compensation would be needed at regular intervals, so as to maintain an acceptable voltage profile.

- <u>Improved stability</u>: Unlike ac systems, with HVdc transmission, the phase angles of the ac system at either ends, are not critical. Therefore, forming interconnections are simpler. In [17], studies have shown that upon the inclusion of an HVdc link between two ac systems, the overall stability of the network improves. For instance, connecting an HVdc line between two ac networks, would reduce the impact that a fault in one network would have on the other ac network in the absence of an HVdc link.

- <u>Lower insulation levels needed</u>: For a given insulation level, the DC lines can transmit more power compared to the ac lines [18], primarily due to the sinusoidal nature of ac voltage.

#### 2.1.1 Types of HVdc systems:

Depending on the converter topology and design, the following are the widely used types of HVdc systems [19]:

1. Current source converters /Line commutated converters (CSC/LCC)

- 2. Voltage source converters (VSC)

- 3. Capacitor commutated converters (CCC)

In the traditional CSC/LCC systems, the flow of the DC current is unidirectional and the power reversal takes place through the reversal of the voltage polarity. Based on line commutated devices, such as thyristors (in older systems with mercury arc valves), making high frequency switching infeasible in such systems. Therefore, they introduce significant lower order voltage harmonics into the ac side and hence, large filters are needed at the PCC (point of common coupling) in order to remove these harmonics. In addition, these converters are highly inductive in nature, and thus require additional reactive power support to maintain the ac voltage at the filter bus (typically 0.6 pu of the converter rating). Further, in LCC systems, during low ac voltages at the inverter side (possibly due to a nearby fault) or for operation with high DC currents, commutation failure [20] of the valves can occur. commutation failures occur due to improper turn-off of thyristor valves, resulting in the failure to transfer current from one valve to the next. Recovery from successive commutation failures require temporary cessation of power transfer which can lead to other major power system problems. Through control mechanisms (such as Voltage dependent current limiter (VDCL) [21]), commutation failure issues can be addressed partially, to prevent successive commutation failures. The DC side faults are also dealt with using the control mechanisms, such as Force Retard [21], where the rectifier is forced to act as an inverter, allowing for clearing of the dc fault. In [22], the Multi In-feed HVdc (MIHVdc) topology has been studied, where multiple LCC converters are connected in close proximity, which in certain situations have improved immunity to commutation failures in contrast to the single in-feed systems. However, due to the large reactive support requirement of the LCC, it is prone to transient

over-voltages (TOV) upon sudden tripping of loads. Further, since the direct current is unidirectional and power reversal requires a voltage reversal, the implementation of a large interconnected DC grid is not feasible with the traditional LCC.

On the other hand, for VSCs, the power reversal entails current reversal [23] [24] [7], with constant voltage polarity and hence the implementation of DC grids is feasible. Based on fastswitching devices, with precise control mechanisms such as pulse width modulation (PWM) [25] (or advanced topologies such as the Modular Multilevel Converter), the VSCs require only marginal high pass filtering at the PCC bus. These converters are capable of operating in all four power quadrants and hence, in principle, do not require any external reactive power compensation at the converter terminals, as the converter itself can absorb or deliver reactive power to maintain the ac voltage. Nevertheless, recent studies in [11] have shown, that with additional capacitive compensation at the PCC, the maximum transmissible power of the VSC increases, because the MVA rating of the VSC is now available for active power transfer and not wasted in providing reactive power. In addition, in theory, they have the black start capability [6], i.e. the ability to provide power to an ac system with no voltage source. VSCs, based on IGBTs, do not have problems such as commutation failure or that of transient overvoltage, which plague the LCC systems. Further, due to the reduced harmonic content, specialized transformers on the ac side which are needed for the LCC systems, are not required for the VSC, which can use typical commercial transformers. Currently, a major problem with the VSC system, is its performance during DC faults, considering the reverse diodes provide an uninterruptible path for the fault currents to feed the fault. Also, even though VSC systems have a smaller footprint [24], the installation costs of the converter are higher than that of the LCC.

Combining the LCC and the VSC, in [26], the dual in-feed topology has been studied, and is shown to have a higher MAP(Maximum Available Power) for the LCC converter when the VSC provides ac voltage support (reactive power) at the bus with minimal active power supply.

MTDC [27] or DC grids are HVdc systems, where 3 or more VSC converters are interconnected which allow for multi-directional flow of power. Just as in the case of an ac network, where the frequency is constant throughout [1], in a DC grid (assuming zero losses in interconnecting lines) the DC voltage is constant [27]. In [28] and [29], various control mechanisms such as the master slave, voltage margin and even autonomous control mechanisms are presented to control power flow in the DC grids.

As noted previously, upon the occurrence of a DC fault, the diodes in the typical two-level VSC converter would continually feed the fault. In the absence of commercial DC breakers, the lack of control on the DC side would mean that ac breakers would be the only possible mechanism to break the path of the fault current. However, using ac breakers would take longer and also, result in loss of power. It is in this scenario, that alternative topologies were introduced. The Modular Multilevel Converters (MMC) [10] topology, where each module (consisting of individual capacitors and valves) is independently switched in and out, is gaining momentum. The full bridge MMC topology, is popular due to their ability to block DC faults. In [10] the control system of the MMC is also explored. Depending on the number of modules, the sinusoidal wave thus generated, is near ideal, and does not require any filtering.

Capacitor commutated converters (CCC) [30], are a modification of the traditional LCC converters, with added capacitors in each phase, each connected in series between the

converter transformer and the valves. Primarily, this allows for reactive power generation [10] (i.e. four quadrant operation), and also reduces the minimum extinction angle [10] for valves, thus reducing the probability of commutation failures. Recently, there is some renewed interest in the CCC owing to the high installation costs of the VSC and also lack of a DC breaker model, as of yet. But, the over-voltage and protection remains a challenge [10].

In this thesis, the 2-level VSC topology is of primary interest. Thus, the following sections are devoted to elucidating the various components of the VSC HVdc and the common control systems employed.

#### 2.2 VSC: Operation and control

The voltage source converter, generates a controlled sinusoidal ac voltage at the VSC ac terminals, from a DC source [6] [24]. The ac voltage thus generated, is by the controlled switching of self-commutated devices (such as IGBTs, GTO etc.) in the converter. The VSC allows for four-quadrant power operation [24], which means it allows for control of active and reactive power supplied to, or absorbed from the connected ac network.

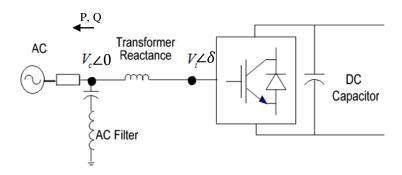

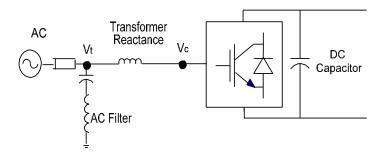

Figure 2- 1 VSC terminal connected to an ac system

Figure 2-1 represents the typical configuration of a VSC connected to an ac system, represented by its Thevenin equivalent. By modulating the magnitude and phase angle of the generated ac voltage at the VSC terminals,  $V_c$ , the active (P) and reactive power (Q) output of the VSC are controlled [24] [31], based on equation (2-1) and (2-2).

$$P = \frac{V_t V_c}{X} Sin(\delta)$$

(2-1)

$$Q = \frac{V_c^2 - V_t V_c}{X} Cos(\delta)$$

(2-2)

Where  $\delta$  is the phase angle between the fundamental voltages of  $V_t$  and  $V_c$ ,

$V_t$  is the fundamental component of the converter's internal voltage,

$V_c$  is the fundamental component of voltage at the ac filter bus,

*X* is the combined reactance of the transformer and the phase reactor.

The line resistance is ignored in these power equations. If the generated ac voltage is greater than the VSC terminal voltage, then reactive power is fed to the ac system (and vice versa). Further, if the phase angle of the generated voltage leads that of the VSC terminals, active power is then supplied to the ac system (and vice versa).

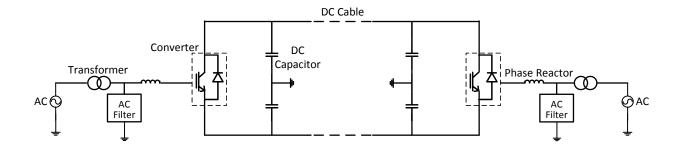

Power reversal in VSC systems is accomplished by reversing the DC current, while keeping the voltage polarity constant. Self-commutating switches such as IGBTs, are capable of high-frequency switching, and hence can generate precise, high quality ac waveforms, of the desired magnitude, phase & frequency. Figure 2-2 shows the schematic depicting the basic anatomy of a two terminal VSC HVdc system. In the following section, the various components in a VSC HVdc system are explained, in some detail.

Figure 2- 2 Schematic of a two-terminal VSC system

#### 2.2.1 Components of the VSC HVdc system:

Referring to Figure 2-2, the main components of a VSC HVdc system are as follows:

- DC Capacitor

- Converter Bridges

- Phase Reactor

- Converter Transformer

- ac filters

- DC Cables/OH lines

#### DC Capacitor:

The main purpose of the DC capacitor is to store energy to reduce the ripple in the DC voltage. Additionally, the capacitor forms the low inductive path for the turn-off current [24]. The size of the DC capacitor ( $C_{dc}$ ) is dependent on the DC voltage rating and would in turn determine its immunity to voltage transients due to disturbances in the ac system.

The response of the DC capacitor in general, is characterized by its "time constant". The time constant (typically  $\approx 5ms$ ) is proportional to the size of the capacitor, implying that a

larger capacitance would result in slower dynamics, and vice versa. The time constant  $(\tau)$  of the capacitor  $(C_{dc})$  is defined in equation (2-3) [17].

$$\tau = \frac{0.5C_{dc}V_{dc}^2}{S_N} \tag{2-3}$$

Where,  $V_{dc}$ : Rated DC voltage

$S_N$ : Nominal Apparent Power of the converter.

#### Converter Bridge:

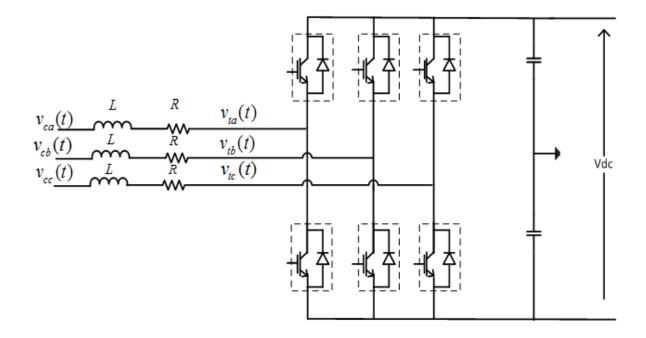

Each valve of the VSC consists of an IGBT connected with the freewheeling diode in antiparallel. Depending on the rating, many individual switches are connected in series so as to withstand higher voltages, thereby, also reducing the reverse blocking voltage of each IGBT [24]. The anti-parallel freewheeling diode forms the path for the current in the reverse direction. The switching frequency of the IGBTs are typically in the order of a few kHz. The topology of the basic 2-level converter is shown in Figure 2-3. As the number of voltage levels in the converter is increased, the generated ac voltage approaches the pure sine wave. Thus, with the increase in the levels of the converter, the filtering required at the ac bus reduces. The 2-level converter topology is the most basic module, with two voltage levels:  $+V_{dc}/2$  and  $-V_{dc}/2$  [10]. The 3-level converter with the clamped neutral [32], has three voltage levels:  $+V_{dc}/2$ , and so on. Generating voltage levels greater than three, result in very complex converter topologies, and are hence not recommended [10].

The Modular Multilevel converter (MMC) topology [10] uses the concept of dividing the converter into smaller modules (of full bridge or half bridge topology), each consisting of its own capacitor. Depending on the control signals generated, in order to track the reference sinusoidal waveforms, the modules are switched in and out, thus creating incremental steps,

which connected in series form the resultant ac output waveform [10]. With the MMCs, it is possible to generate near perfect sinusoidal ac waveforms, with no need for filtering. The external controls that develop the voltage orders for the MMC and the two level VSC are identical. However, the internal control system for the VSC with the MMC topology are very different from the traditional two- or three-level VSC, since factors such as the voltage balancing of the capacitors in each phase ought to be taken into consideration.

Figure 2- 3 Two-level converter topology

#### Phase Reactor:

The phase reactor (component of X) is crucial in the control of the active and reactive power control, as seen in equation (2-1) and (2-2). Additionally, this reactance provides a large impedance path for the high-frequency current harmonic components introduced due to PWM (explained in Section 2.2.2).

#### Converter Transformer:

The transformer is useful in transforming the ac side system voltage to a suitable value for the converter. The type of transformer winding connections would determine the dynamics of the transformer [17]. The combined reactance of the transformer and the phase reactor is typically about  $0.3 \ pu$ .

#### ac Filters:

The ac filters which act as high pass filters (or tuned filters), remove the higher order voltage harmonics in the waveforms generated by the PWM [25]. Considering that the PWM switching frequencies are selected to be an integral multiple of the fundamental frequency, the cut-off frequency (or the tuned frequency) of the filters are quite high. The analysis of the harmonic content of the PWM generated waveforms is explained in detail in Section 2.2.2.

#### HVdc Transmission Lines/Cables:

For long distance bulk transmission of power, transmission lines or cables are used. Since ground return is possible for HVdc, installation costs can be further reduced [24]. Further, the undersea cables form the backbone to connect two networks separated by large water bodies. HVdc cables thus facilitate the power exchange between such networks.

#### 2.2.2 Pulse width modulation

Pulse width modulation (PWM) is the controlled switching of the IGBT valves to generate a switched (pulse) waveform, to reproduce the reference voltages at the terminals of the VSC [25]. The most commonly employed method is the Sinusoidal PWM (SPWM). Other approaches include the CRPWM [33], OPWM [34] etc. Using the modulation index (m), phase angle  $(\delta)$  and the frequency  $(f_s)$  as in equation (2-4) and (2-5), the three phase *reference* signal is generated. In each phase, this reference signal is compared against the *carrier*

waveform, which is typically a triangular waveform (with frequency:  $f_c$ ). The output, from this modulation, provides the switching pulses for the valves in each converter leg.

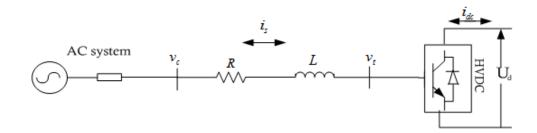

Figure 2- 4 Equivalent circuit of the single terminal system, neglecting the ac filter

The ratio of the frequency of the carrier wave with that of the reference wave is termed as the frequency modulation ratio  $(m_f)$ :

$$m_f = \frac{f_c}{f_s} \tag{2-4}$$

The Figure 2-4 shows the equivalent circuit for the single terminal system. The generated voltage waveform  $(V_t)$  has the fundamental component as defined in equation (2-5). The Figure 2-5, is the block diagram of the generation of the ac voltage waveform the dq-components of the voltage.

$$V_t = m * Sin(\omega t + \delta)$$

(2-5)

Where *m*: Modulation index

$\delta$ : Phase angle of voltage

$\omega$ : Frequency of the sinusoidal waveform.

By controlling the modulation index & the phase angle of voltage, as explained in Section 2.2, it is possible to control the reactive power & the active power supplied to/from the VSC terminals, respectively.

Figure 2- 5 Generation of reference waveforms

Generally, the converter control system generates orders for the direct and quadrature component ( $v_{dref}$  and  $v_{qref}$ ) of the ac voltage which can be considered as the magnitudes of the VSC voltage component in phase and in quadrature with the ac bus bar.

With SPWM, when the modulation index (m), is less than unity, the frequency spectrum of the generated voltage at the VSC terminals, contains harmonics at:  $(k * f_c \pm p * f_s)$  [25]. Where, k and p are integers, such that, if k is even, p is odd and vice versa. Figure 2-6 shows the frequency spectrum of the pulse width modulated waveforms.

Although, at higher switching frequencies, the harmonic content in the voltage is reduced, the switching losses are high. Therefore, a suitable value of  $m_f$ , which forms as a tradeoff between these two is selected. In addition, it is recommended to select a frequency which is 3n times the fundamental to eliminate the zero sequence harmonics, if any [25]. Also, the due to symmetry considerations, the  $m_f$  is recommended to be an odd number.

Figure 2- 6 Frequency spectrum of the pulse width modulated waveform [25]

The output of the VSC control system, are the dq-components of the reference voltage, i.e.  $v_d$  and  $v_q$ .

Figure 2-7 Generation of gating pulses for IGBT valves [taken by permission from HVdc course notes of Dr. A. M. Gole]

The gating pulses for each leg of the converter are generated, as shown in the above figure (Figure 2-7), are provided to the IGBT valves in each phase. In Section 2.3, the commonly used approaches for the VSC control system are explained.

#### 2.2.3 Capability curves for VSC:

The VSC can operate in all four power quadrants, allowing for the supply/absorption of the active and reactive power to/from the ac system it is connected to. As with any practical device, there are limitations to the operating range of the VSC. These constraints are essentially depicted by the Capability Curves of the VSC. The capability curves (Figure 2-8), therefore, show the confines within which the VSC operates.

Figure 2-8 Capability curve for the VSC [35]

The following are the limits imposed on the VSC operation based on the ratings of the converter and the ac system it is connected to [35]:

- 1. MVA limitation: The limitation in terms of the maximum permissible current through the IGBT valves, determines the maximum MVA the VSC can supply to the ac system. The resultant circle, as shown in Figure 2-8, is the product of the maximum permissible current and the actual ac voltage.

- 2. Maximum DC current: The active power limits of the converter are limited by the maximum permissible DC current. This limit of the maximum active power that can be supplied by the VSC, manifests itself as a vertical line in the PQ plane, as shown in Figure 2-8. Depending on the magnitude of the DC voltage, these limits may or may not intersect the maximum MVA circle.

- 3. Reactive Power Limits: The maximum permissible reactive power that can be supplied by the VSC, is dictated by the limits of the maximum voltage that the VSC can generate at the terminals. The reactive power limit is obtained by solving the expression for Q as defined in Section 2.2. The resultant solution is a circle centered at  $(0, -V^2/X)$  in the PQ plane, Figure 2-8. The variation of the ac voltage with respect to the constant DC voltage would result in a change in the radius of the circle.

# 2.3 Control system for the VSC

Selecting an optimal structure as well as the parameters for the VSC control system is very important. In simple terms, the VSC control system is a non-linear, coupled, double input double output system [36]. The accuracy with which the actual system dynamics are modeled in the control system, would largely determine its efficacy.

The following sections are devoted to the two existing control methodologies, namely:

#### 1. Power Angle control

#### 2. Vector Current control

In Power Angle control approach [37], the non-linear, analytical equations for active and reactive power with the power orders, are used to directly compute the modulation index (m) and the phase angle  $(\delta)$  of the reference voltage. The active power & reactive power are the *controlled* variables, and the modulation index and the phase angle of voltage are the *controlling* variables. The non-linear equations relating the controlled and the controlling variables form the basis of this approach (as explained in Section 2.3.2). Although the method is simple & efficient, the main shortcoming is that, in this approach, the valve currents are not limited [36]. Therefore, under faulted conditions, for instance, limiting the over-currents would prove to be a challenge.

In contrast, the vector current control or dq-decoupled control [24] [38], is a current control method. In this approach, the power control loops (P and Q) are independently controlled by the d and q-components of current, respectively. The control system is designed so as to allow for the independent control of the power control loops.

In literature, alternative methods of control can be found, such as the Power Synchronization Loop (PSL) [39] and predictive methods, as in [40], but are not discussed here. In this thesis, the vector current control approach has been used, which is the most common.

# 2.3.1 Vector current control:

The vector control method, allows for the independent control of the active (P) and reactive power (Q), by controlling the d and q-components of current, respectively. These controlled currents, are thereafter used to determine the magnitude and phase angle (using m and  $\delta$ ) of the converter's internal voltage. Based in the SRF (synchronous reference frame) domain, the

vector control approach depends substantially on the continuous synchronization of the reference *d*-axis with the filter ac bus voltage. In order to do so, Phase Locked Loops are used.

Consider the simplified network as shown in Figure 2-9.

Using the same notation as in equation (2-1) and (2-2), assuming the line resistance (R) and line inductance (L), to be equal for all phases, equation (2-6) is obtained.

Figure 2- 9 Simplified single line diagram of the HVdc system

$$L\frac{di_{sn}}{dt} + Ri_{sn} = v_{tn} - v_{cn} \tag{2-6}$$

For n=a,b,c, corresponding to each phase.

Upon using the Park's transformation (equation (2-8)), the above voltage equations are transformed to the synchronous domain, using the transformation angle  $(\theta)$  at the ac filter bus.

$$\begin{bmatrix} f_a(t) \\ f_q(t) \end{bmatrix} = \frac{2}{3} T(\theta) \begin{bmatrix} f_a(t) \\ f_b(t) \\ f_c(t) \end{bmatrix}$$

(2-7)

$$T(\theta) = \begin{bmatrix} \cos(\theta) & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \\ \sin(\theta) & \sin(\theta - \frac{2\pi}{3}) & \sin(\theta + \frac{2\pi}{3}) \\ 1/2 & 1/2 & 1/2 \end{bmatrix}$$

(2-8)

The dq-transformed voltage equations, thus obtained are as follows:

$$L\frac{d}{dt}i_{q} = \omega Li_{d} - Ri_{q} + v_{tq} - v_{cq}$$

$$L\frac{d}{dt}i_{d} = \omega Li_{q} - Ri_{d} + v_{td} - v_{cd}$$

(2-9)

The overall control system can be divided into the *outer control* and *inner current control* loops, connected in cascade. The outer control loops provide the desired reference currents as inputs to the inner current control loops. Depending on the control objective at the concerned VSC terminal, the outer loop controls are selected. The output of the inner current control loop is the VSC's internal voltage in the dq-domain, which would further, provide the m and  $\delta$ , for the PWM.

# **2.3.1.1** Inner Current Control Loop:

Primarily, the inner current control constitutes the control system design, which takes into account the network equations, to determine the desired terminal voltage, which would exist, when the desired "reference" currents flow through the phase reactor. Therefore, reiterating the point that the efficacy of the control system indeed depends on the accuracy of the network model.

Figure 2- 10 Conceptual Block diagram of the Inner current control loop

With the reference currents  $(i_d^{ref} \& i_q^{ref})$  as the input, the *inner current control loop* provides the mechanism to determine the reference voltage, as shown in Figure 2-10. In order to facilitate the decoupling of  $i_q \& i_d$  control loops, Schauder et al. in [40], proposed the 'Inverter type 1' control system, which has been described above as the Vector Current control method.

In the following section, the inner loop control system of the VSC is developed. From the equation (2-9), the cross coupling between dq-equations is evident, due to the presence of the terms, " $\omega Li_d$ " & " $\omega Li_q$ " in the equations for  $i_q$  &  $i_d$ , respectively.

The equation (2-9) is rewritten in the matrix form as follows:

$$L\frac{d}{dt}\begin{bmatrix} i_{sd} \\ i_{sq} \end{bmatrix} + \begin{bmatrix} R & -\omega L \\ \omega L & R \end{bmatrix} \begin{bmatrix} i_{sd} \\ i_{sq} \end{bmatrix} = \begin{bmatrix} v_{td} - v_{cd} \\ v_{tq} - v_{cq} \end{bmatrix}$$

(2-10)

From equation (2-10), the converter's internal voltages  $v_{td}$  &  $v_{tq}$  can be controlled as per equation (2-11).

$$v_{td} = x_1 + v_{cd} - \omega L i_{sq}$$

$$v_{tq} = x_2 + v_{cq} + \omega L i_{sd}$$

(2-11)

Upon substituting for the controlled voltages, into equation (2-10), the decoupled control for  $i_d \& i_q$ , are obtained as shown in equation (2-12).

$$L\frac{d}{dt} \begin{bmatrix} i_{sd} \\ i_{sq} \end{bmatrix} + \begin{bmatrix} R & 0 \\ 0 & R \end{bmatrix} \begin{bmatrix} i_{sd} \\ i_{sq} \end{bmatrix} = \begin{bmatrix} x_1 \\ x_2 \end{bmatrix}$$

(2-12)

It is evident from this equation, that a change in control input  $x_1$ , would result in a change in only  $i_d$ , and to the same effect, a change in  $x_2$  would cause a change in  $i_q$  alone. Subsequently, the control system design can be concluded by defining  $x_1$  and  $x_2$  as follows:

$$x_{1} = \left(K_{p} + \frac{K_{i}}{s}\right) \left(i_{d}^{*} - i_{d}\right)$$

$$x_{2} = \left(K_{p} + \frac{K_{i}}{s}\right) \left(i_{q}^{*} - i_{q}\right)$$

(2-13)

The resultant control system, based on these equations, is shown in Figure 2-11. The VSC terminal reference voltages, thus obtained, i.e.  $v_{td} \& v_{tq}$ , are used to calculate the modulation index and phase angle, which form the input for the PWM block, computed using equation (2-14).

$$m = \frac{\sqrt{v_{td}^2 + v_{tq}^2}}{v_{tq}}$$

$$\delta = \tan^{-1} \left(\frac{v_{tq}}{v_{td}}\right)$$

(2-14)

Here  $v_{cd}$  and  $v_{cq}$ , are dq-components of the voltage measured at the ac filter bus. The delay due to this measurement is represented by the transfer function  $H_{LPF}(s) = 1/(1+s\tau)$ ; where  $\tau$  tis a measurement related delay. The combined control system, within the inner current control loop is shown in Figure 2-11.

Figure 2- 11 Inner current control of the Vector current control method

The current references,  $i_d^*$  and  $i_q^*$ , are the output of the outer control loops. The gains of the PI controllers are usually high, since the inner current controller is expected to provide, near instantaneous tracking of the reference currents.

#### 2.3.1.2 Outer Control Loops:

Depending on the ac system parameters and the network operating conditions, typically, the functionality is assigned to the outer control loops. In multi terminal DC (MTDC) systems, for instance, a unique converter (preferably with the highest SCR) is assigned with the task of DC voltage control [11], while the dc voltage at the other converters would be relative to this bus voltage, minus the losses. In this section, a brief analysis of the possible types of outer loop controllers is presented.

In order to better understand the dynamics of the outer loop controls, the equations for P and Q are linearized [38]. The instantaneous active (P) and reactive power (Q) output at the ac filter bus (Figure 2-9), are defined as follows:

$$P = Re(v_t i_s^*)$$

$$Q = Im(v_t i_s^*)$$

(2-15)

The following equations are obtained upon transforming the voltages and currents in the dq-domain and linearizing equation (2-15) [38].

$$\Delta P = \begin{bmatrix} i_{sd0} \\ i_{sq0} \end{bmatrix}^T \begin{bmatrix} \Delta v_{ul} \\ \Delta v_{uq} \end{bmatrix} + \begin{bmatrix} u_{ul0} \\ u_{uq0} \end{bmatrix}^T \begin{bmatrix} \Delta i_{sd} \\ \Delta i_{sq} \end{bmatrix}$$

$$\Delta Q = \begin{bmatrix} i_{sd0} \\ -i_{sq0} \end{bmatrix}^T \begin{bmatrix} \Delta v_{uq} \\ \Delta v_{ul} \end{bmatrix} + \begin{bmatrix} u_{ul0} \\ u_{uq} \end{bmatrix}^T \begin{bmatrix} -\Delta i_{sq} \\ \Delta i_{sd} \end{bmatrix}$$

(2-16)

For a network with stiff ac bus voltage, the change in the bus voltage magnitude is negligible, therefore, it can be assumed that  $\Delta v_{tq}$  and  $\Delta v_{td}$  are both, zero. Hence, equation (2-16) can be rewritten as follows:

$$\Delta P = \begin{bmatrix} u_{ul \, 0} \\ u_{ul \, 0} \end{bmatrix}^T \begin{bmatrix} \Delta i_{sd} \\ \Delta i_{sq} \end{bmatrix}$$

$$\Delta Q = \begin{bmatrix} u_{ul \, 0} \\ u_{ul \, 0} \end{bmatrix}^T \begin{bmatrix} -\Delta i_{sq} \\ \Delta i_{sd} \end{bmatrix}$$

(2-17)

Also, at steady state, with rated conditions, the dq-transformed values of the voltage are:  $u_{ud0} = 1 \& u_{uq0} = 0$ . As a result, the above equation further simplifies to, equation (2-18).

$$\Delta P = \Delta i_{sd}$$

$$\Delta Q = \Delta i_{sd}$$

(2-18)

Accordingly, a change in  $\Delta P$  would cause a proportional change in  $\Delta i_{sd}$ . And correspondingly, a change in  $\Delta Q$  would result in a change in  $\Delta i_{sq}$ . These equations form the essence of the design of the outer loop controls.

In this thesis, a single terminal converter system is considered, with active power and ac voltage control. As mentioned previously, only one of the converters should control the dc voltage in the HVdc system. In the system under consideration, the dc voltage control terminal is modeled by a simple DC source, representing an ideal dc voltage controlled converter. In the following sections, though, for the sake of completeness, all possible combinations (including those for dc voltage control) for the outer loop controls of the VSC have been explained.

#### **Active Power Control:**

Equation (2-18) depicts the strong coupling between  $i_{sd}$  and P. To control the active power supplied by the VSC to the ac system, based on the demand  $(P_{ref})$ , a simple PI controller structure as shown in Figure 2-12, is used. The output of the PI controller forms the reference current,  $i_d^*$ . The instantaneous power is typically filtered  $(P_s)$ , prior to providing it to the controls.

Figure 2- 12 Active power control loop

#### **DC Voltage Control:**

In a two-terminal network, one of the converters must have the DC voltage control ability, while the other terminal is made to control the power. In a DC grid, the DC voltage control can only be assigned to one converter. Typically, this converter is chosen to be the one connected to the strongest ac system (i.e. highest SCR), as shown in [11]. The other converters would have a DC voltage which is derived from this terminal, minus the transmission line losses. Thus, to maintain a stable DC voltage across the grid, it is imperative to have a strong ac system connected to the DC controlling converter. Figure 2-13 shows the typical control system to regulate the DC voltage.

Figure 2-13 DC voltage control loop

#### **Frequency Control:**

Typically used in isolated networks, the frequency control loop provides a mechanism to control the frequency of isolated networks [24] which can be, further, integrated into a larger

network. The control architecture is similar to that of the active power control loop (PI controller), the output of which is the reference current  $i_d^*$ .

#### ac voltage Control:

Controlling the magnitude of the ac voltage at the VSC terminals directly, is essentially a form of the reactive power control. The anatomy of the ac voltage control is as shown in Figure 2-14.

Figure 2-14 AC voltage control loop

#### **Reactive Power Control:**

Controlling the reactive power fed into/out of the ac system is analogous to controlling the ac voltage at the bus terminals. The control architecture for the reactive power control is identical to that of the active power control loop i.e. using PI controllers.

## **Outer loop control selection for Multi Terminal DC systems:**

Some broad paradigms for the design of MTDC systems are listed below:

1. There can only be one converter with DC voltage control [27]. Else, multiple converters would compete with one another, which is not desirable. Although, there can be multiple converters with the dc droop characteristics [5].

- 2. The DC voltage control terminal cannot regulate power flow and therefore, another converter should be assigned this task. In a two terminal system, both converters cannot have DC voltage control or active power control.

- 3. In an MTDC system, in case of loss of the DC voltage control converter, a backup converter can be assigned to take over. Which is, in essence, a combination of the Master-Slave approach with the voltage margin method [28] [27]. Borrowing the terminology from communications, typically, the one main converter is referred to as the Master converter and the other converters (slaves), which take over if the Master converter fails to operate for some reason.

- 4. Intuitively, it makes sense to assign the task of active power control to be assigned to the converter which acts mostly as the inverter. Additionally, if the rectifier end does not have DC voltage control, the risk of DC overvoltage emerges [27]. This might occur in cases when there is load tripping at the inverter end, causing sudden drop in power demand.

Currently, the determination of optimal power flow in MTDC grids [41], [42] remains a topic of interest. Considering the enormous challenges in the solving the non-linearities involved in optimal power flow, there is still a lot of ground to cover. But, new topologies including the Current Flow Controllers [43] are a step in that direction.

# 2.3.1.3 Phase Locked Loop (PLL):

Phase locked loops provide the phase angle and frequency input of the filter bus voltage to the control system of the VSC. Since with the Vector current control approach, the control systems are largely based in the synchronous (dq) domain, the performance of the PLL plays a very crucial role in its operation [44] [11]. In addition, it also provides the reference to the

PWM block, in generating precise gating pulses for the IGBT valves. PLLs are discussed in detail in Chapter 3.

#### 2.3.1.4 Strength of the ac system: Short Circuit Ratio (SCR)

As mentioned previously, the performance of the Vector current control method is dependent on the strength of the system [44] [38], quantized by the SCR.

For a VSC system with rated power of  $P_{dc}$ , and rated line to line voltage  $V_l$  (Figure 2-15) connected to an ac network with the impedance of  $Z_s$ , the Short Circuit ratio (SCR) is defined as the ratio of the SCMVA to  $P_{dc}$ , as shown in equation (2-19).

Figure 2- 15 Equivalent representation of the HVdc system

$$SCR = \frac{SCMVA}{P_{dc}} = \frac{\left(V_l^2 / |Z_s|\right)}{P_{dc}}$$

(2-19)

In [11], the limit of SCR=1.6, has been prescribed to be the boundary between *strong* and *weak* systems. The angle of the Thévenin impedance of the equivalent ac system also has a significant impact on the power transmission ability of the VSC, as explained in the later sections. Therefore, the SCR is also represented with this angle.

#### 2.3.2 Power angle control:

The power angle control approach is an alternative approach for VSC controls. Based on the non-linear analytical equations for the active and reactive power [36] derived from equation (2-1) and (2-2), the method is not preferred due to its lack of current controlling ability.

The strong coupling between the  $\delta$  & P, and, voltage magnitude (m) & Q, form the basic premise of this method. The *controlled* variables (modulation index and phase angle) are computed, using analytical equations, involving the reference values of the *controlling* variables (P and Q). These (computed) controlled variables from the power references, m &  $\delta$ , and their respective corrective terms  $\Delta m$  &  $\Delta \delta$ , obtained from the measured (actual) power supplied by the VSC, in combination, result in the final m &  $\delta$  output [37] [36]. The modulation index and phase angle thus obtained, is provided to the PWM control system.

In addition to the lack of current control, the method is also incapable of damping resonance in the ac system, which can permeate into the DC network [38]. Hence, this method is not commonly used.

# 2.4 Summary

In this chapter, a comparison between the traditional LCC technology and the VSC is presented. The inner control system of the VSC HVdc and the components in a VSC HVdc system are explained in detail. Two possible control mechanisms for the VSC, namely the power angle control and the vector current control are explored. Further, the crucial concept of the SCR of an ac system has been established. The impact of the SCR on the working of the vector current control method, will be explained in the following chapters.

# Chapter 3

# Design and Analysis of the Adaptive PLL

With standard Phase Locked Loop (PLL) designs, distortions (such as harmonics, interharmonics, unbalance etc.) in the input voltage, permeate into the phase and frequency outputs of the PLL causing errors. In this Chapter, a new PLL design is developed and introduced to address this problem. The proposed design includes a frequency adaptive 'prefilter' structure, which extracts the fundamental positive sequence component of the input voltage and hence, mitigates possible distortion errors in the PLL outputs. This adaptive filter changes its parameters according to the measured frequency to always give the designed performance. This is expected to make the dynamic response of the PLL faster than would be possible with a wider band passive filter. Further, the dynamic performance of the PLL is studied and the effect of voltage distortions on the Adaptive PLL is compared with that of the other traditional PLL designs.

# 3.1 Phase Locked Loops: Background and architecture

In FACTS [6] [45] and HVdc systems [8] [46] [24], Phase Locked Loops (PLLs) provide the reference phase angle and frequency of the ac bus voltage input. In conventional LCC HVdc systems, the PLL provides precise zero crossings for the firing controls of the thyristor

valves [8]. Likewise in FACTS devices, be it the IGBT-based STATCOM [6], or thyristor based SVC [6], they depend on PLLs for accurate tracking of the phase angle of the ac bus voltage at the PCC. These high frequency switching devices can be used for the purpose of providing reactive power support [6] in transmission systems or for end-user power quality conditioning applications such as active filtering [47], load balancing [48] etc.

For a VSC HVdc system with the vector current control approach (Chapter 2), the control system is largely based in the Synchronous reference frame (SRF) domain. Therefore, intuitively, the PLL performance should have a significant impact on the VSC. Also, in networks with high distortion, such as islanded systems or upon the integration of renewable sources such as wind [16], the inclusion of the frequency adaptive characteristic in the PLL design is important. In literature, there are prominent PLL designs such as, the EPLL(Enhanced PLL) in [16] and the DSOGI (Double second order generalized integrator) PLL in [49] which are designed to operate in such networks.

# 3.1.1 Significance of the PLL in a VSC control system

The vector control method is based on decoupling the control equations in the dq-domain, to independently regulate the outer control loops. In essence, provided that the ac bus voltage is stiff, a change in the current reference of  $i_d$  cannot introduce a change in  $i_q$ , and vice versa [38]. However, in weak ac systems, the ac voltage is prone to disturbances. Consequently, the PLL itself has a hard time following the ac voltage phase in non-stiff systems. Therefore, the performance of the vector control method is in turn dependent on the strength of the system, which is quantized by the SCR (Section 2.3.1).

For a VSC connected into an ac system with high impedance, the voltage at the PCC is prone to disturbances, and no longer stiff. In this scenario, the PLL performance is crucial.

This has been studied in [38] and [11]. In [38], the anatomy of the vector current control method has been explained. In [11], the small signal model of the VSC system, with the inclusion of the PLL, has been developed and stability studies are done thereof. These studies show the significant impact of the PLL parameters on the small signal and transient stability, especially for low SCR systems. In fact, in weak systems the PLL gains are shown to have a higher impact on stability, in comparison with the gains of the inner and outer control loops [11]. It is shown that the traditional PLL designs are not well suited for weak ac systems, considering that for SCR<1.6, they can have a detrimental impact on stability.

The primary objective of this research, therefore, is to design and implement a new PLL design for the VSC control system, to study its impact on stability, especially, when the VSC is connected into very weak ac systems.

# 3.1.2 Anatomy of typical PLL:

The primary objective of the PLL is to track the frequency and the phase angle of the fundamental positive sequence component of the input voltage. There are several ways to realize this, the most basic design being the d-q-z PLL(or SRF-PLL), which was first proposed by Ainsworth in [46] and further analyzed and EMT validated in [50]. In this section the broad PLL architecture is explored.

Figure 3-1 Schematic of a typical Phase Locked Loop [51]

Based on functionality, the PLL architecture can be divided into 3 sections [52] [51] (Figure 3-1):

- 1. Phase detector (PD)

- 2. Loop filter (LF)

- 3. Voltage controlled oscillator (VCO)

The *phase detector* [51], determines the phase angle error between the voltage input and the PLL output. The implementation of the PD may vary with the design, but essentially, it performs the operation akin to multiplication.

This phase error is passed onto the *loop filter*, which may be a simple PI controller, or alternatively PI controller in conjunction with a LPF, or even higher-order lead lag filters etc. The selection of the Loop filter is based on the desired complexity (in terms of its order) and of course the operating conditions in the network. A higher-order filter design, offers improved accuracy, but affects the dynamic performance adversely. Therefore, the selection of the Loop filter is important.

The output of the loop filter is provided to the *voltage controlled oscillator* (VCO), which generates a periodic signal with a frequency dependent on the VCO input voltage. In a properly working PLL, the output of the loop filter will change so as to eliminate the phase error between the PLL output and that of the input voltage.

In general, every PLL has a *base frequency* which provides the initial output for the PLL. Depending on the "*lock in range*"[52] of the PLL, the output of the PLL eventually locks onto the frequency of the input signal i.e. matches it in frequency and is in phase with it. In power systems, since the range of frequency does not vary significantly, it is presumed that the frequency always falls within this range. If the PLL phase angle is not locked onto that of the

input ac voltage, the phase error is non-zero. In its most basic form, this phase error is passed through a simple PI controller.

# 3.2 Traditional d-q-z PLL

#### 3.2.1 Architecture:

The architecture of the SRF-PLL is best explained, when correlated with the anatomy of the PLL, as explained in Section 3.1.1 (depicted by the demarcation in Figure 3-2).

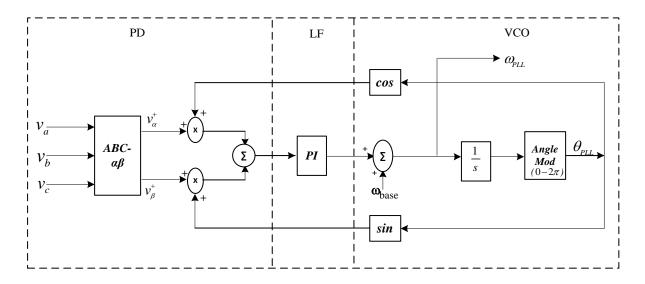

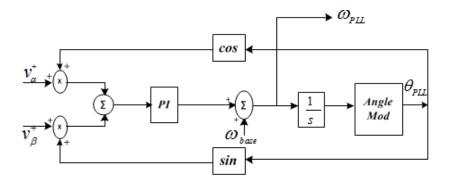

Figure 3- 2 Synchronous Reference Frame PLL (d-q-z PLL) [51]

In the SRF-PLL, the PD transforms the abc-components of the input voltage into the Clarkes' components [53] of the voltage (stationary reference frame) (i.e.  $v_{\alpha}$  and  $v_{\beta}$ ). These  $\alpha\beta$ -components are further transformed into the rotating (synchronous) reference frame, dq-components. This transformation is based on the angle  $\theta_{PLL}$ , provided as feedback from the PLL output (in essence, the VCO output). The d-component of the voltage is the Phase Error which forms the input to the PI controller (loop filter stage).

The output of this PI controller forms the corrective term for the VCO stage, which is added to the base frequency,  $\omega_{base}$ . Further, the phase angle is calculated from this corrected

frequency and again provided as feedback to the PD stage. The PLL is perfectly locked, if the *d*-component of the voltage is zero.

## 3.2.2 Problems with the d-q-z PLL

Under circumstances where there are voltage distortions in the input, the frequency response of the LF block determines the extent of error that propagates into the PLL output [51]. In such a case, the PI controller has a limitation in the range of frequencies it can provide a filtering action for. A filter with lower cut-off frequency (i.e. higher bandwidth) and higher-order, would result in reduced errors in the PLL output. Simultaneously, due to the reduced bandwidth, the overall dynamic response would deteriorate. Therefore, depending on the input voltage distortion, the selection of the LF is a tradeoff between the accuracy and the response time of the PLL.

To understand the extent to which distortions in the input voltage propagate into the PLL output, it is useful to perform an analytical study of the same. This can provide useful insight into the design criterion of the pre-filter structure in the Adaptive PLL. For a given transfer function (F(s)) of the Loop Filter block, the error can be calculated analytically, for all distorted voltage conditions, as shown in [51]. Theoretically, the phase error can be calculated as follows [51]:

$$G_f(s) = \frac{\hat{\theta}(s)}{\theta(s)} = \frac{K_d * F(s)}{s + K_d * F(s)}$$

(3-1)

Where,  $\theta(s)$ : Actual phase angle of the input signal

$\hat{\theta}(s)$ : Estimated phase angle PLL output

$K_d$  is a constant gain.

This equation is indicative of the relationship between the filtering properties of the F(s) block and the errors in the phase and frequency output. Essentially, depending on the type of

voltage distortion, the frequency response i.e. the transfer function of F(s) is designed, so as to reduce the errors permeating into the output phase angle. With quantifiable errors, this analysis was used to design the loop filter block in the Adaptive PLL.

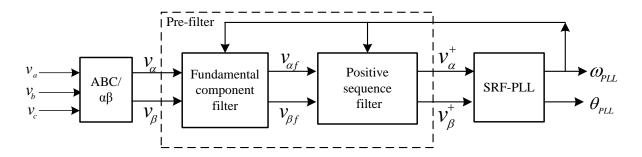

# 3.3 Methodology

In order to mitigate the effect of the input voltage distortions on the PLL output, in this work, a "pre-filter" architecture is developed. The inclusion of this pre-filter structure (preceding the SRF-PLL), facilitates the extraction of the fundamental positive sequence of the input voltage, thus providing precise tracking of the phase angle and frequency.