## Investigation of a Cascade Multi-Level Inverter as an Advanced Static Compensator

by

### Husam K. Al-Hadidi

#### A Thesis

submitted to the Faculty of Graduate Studies in partial fulfillment of the requirements for the Degree of

Masters of Science

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg, Manitoba, CANADA.

© August, 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-79921-2

#### THE UNIVERSITY OF MANITOBA

## FACULTY OF GRADUATE STUDIES

\*\*\*\*

#### **COPYRIGHT PERMISSION PAGE**

# INVESTIGATION OF A CASCADE MULTI-LEVEL INVERTER AS AN ADVANCED STATIC COMPENSATOR

BY

#### **HUSAM K. AL-HADIDI**

A Thesis/Practicum submitted to the Faculty of Graduate Studies of The University of Manitoba in partial fulfillment of the requirements of the degree

of

#### **Master of Science**

### HUSAM K. AL-HADIDI © 2002

Permission has been granted to the Library of The University of Manitoba to lend or sell copies of this thesis/practicum, to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film, and to University Microfilm Inc. to publish an abstract of this thesis/practicum.

The author reserves other publication rights, and neither this thesis/practicum nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

## Acknowledgements

I would like to express the deepest appreciation to Dr. R. W. Menzies, the author's thesis supervisor, for his excellent guidance, advice, encouragement and considerable amount of work throughout this study. For which, I am deeply grateful to him.

Sincere thanks are extended to Dr. A. M. Gole and all staff and colleagues of the power Tower for their kindness and friendship which have made this period a memorable and enlightening experience. I also thank my family back home, especially my parents who have devoted most of their time and energy for the well being of their children.

Finally, I express my deep appreciation to my beloved wife, Mona, for her continuous support, understanding and encouragement in all ways.

## Abstract

An advanced static var compensator or STATCOM is a reactive power source applied for the dynamic compensation in power systems to provide voltage support, increase transient stability margin and improve damping of power systems. The thesis investigates the possibility of using a cascade M-level inverter consists of (M-1)/2 H-bridges in which each bridge has its own separate dc source as an advanced static compensation or STATCOM, in which the design of the seven level inverters as well as corresponding switching methods, harmonic spectrum and control strategies are carefully developed. The basic operation features of a STATCOM is simulated in a simple ac system.

The merit of the cascade converter configuration over the other two multilevel converter configurations, diode-clamped converter configuration, and flying-capacitor converter configuration, is that the cascading configuration uses a small number of diode and capacitors. Moreover, packaging and physical layout is very easy due to its modular structure. An efficient control strategy based on the control of the phase angle of switching pattern is developed in this thesis. A switching scheme of rotated fundamental pattern is applied to control the dc voltage balancing. The simulation results indicate that the proposed design of the cascade M-STATCOM and corresponding control strategies are successful, cost efficient and easy to implement, which make it emerge as an practical alternative approach.

## **Contents**

| Acknowledgem    | ents                                         | i   |

|-----------------|----------------------------------------------|-----|

| Abstract        |                                              | ii  |

| Contents        |                                              | iii |

| List of Figures |                                              | vi  |

| List of Tables  |                                              | ix  |

| List of Symbols |                                              | x   |

| Chapter 1 - In  | troduction                                   | 1   |

|                 | 1.1 Background                               | 1   |

|                 | 1.2 Conventional static var compensator      | 2   |

|                 | 1.3 Principle of the STATCOM                 | 4   |

|                 | 1.4 The basic STATCOM                        | 6   |

|                 | 1.5 Advantages of STATCOM over SVC           | 8   |

|                 | 1.6 The scope of the Thesis                  | 9   |

| Chapter 2 - Ana | lysis of a multilevel GTO thyristor inverter | 12  |

|                 | 2.1 Introduction                             | 12  |

|                 | 2.2 Diode-clamped multilevel inverter        | 13  |

|                | 2.3 Cascade multilevel inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1       |  |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

|                | 2.3.1 Circuit and working princible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1       |  |  |  |  |  |

|                | 2.3.2 The advantages and disadvantages of cascade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |  |  |  |  |  |

|                | multilevel inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1       |  |  |  |  |  |

|                | 2.3.3 The output voltage control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1       |  |  |  |  |  |

|                | 2.4 Fundamental frequency switching (FFS) of GTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2       |  |  |  |  |  |

|                | 2.5 Pulse width modulation switching techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2       |  |  |  |  |  |

|                | 2.5.1 Subharmonics pulse width modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2       |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3       |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3       |  |  |  |  |  |

|                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3       |  |  |  |  |  |

|                | <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3       |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3       |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3<br>3. |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |  |  |  |  |  |

| Chapter 3 - Sy | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4       |  |  |  |  |  |

|                | 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |  |  |  |  |  |

|                | 3.2 STATCOM operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •       |  |  |  |  |  |

|                | 3.3 Control strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4       |  |  |  |  |  |

|                | 3.4 Main control loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4       |  |  |  |  |  |

|                | 3.5 A rotated switching scheme of fundamental frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4       |  |  |  |  |  |

|                | 3.6 Method of pre-charging the inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4       |  |  |  |  |  |

| Chapter 4 - Te | est studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5       |  |  |  |  |  |

|                | 4.1 EMTDC system model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4       |  |  |  |  |  |

|                | multilevel inverter  2.3.3 The output voltage control  2.4 Fundamental frequency switching (FFS) of GTO  2.5 Pulse width modulation switching techniques  2.5.1 Subharmonics pulse width modulation  2.5.2 Phase shifting PWM technique  2.5.3 Switch frequency optimal PWM  2.6 Comment on different techniques of PWM  2.7 Comparison between FFS and PWM methods  2.7.1 Total harmonic distortion  2.7.2 Power losses  2.7.3 Transient response  3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

|                | 4.2.1 Start-up of the STATCOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5       |  |  |  |  |  |

|                | 4.2.2 Steady state operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5       |  |  |  |  |  |

|                | 4.2.3 Transient operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5       |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5       |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6       |  |  |  |  |  |

|                | 4.3.1Steady state operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6       |  |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |  |  |  |  |  |

|                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62      |  |  |  |  |  |

| Chapter 5 - Co | onclusions and Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6       |  |  |  |  |  |

|                | 5.1 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6       |  |  |  |  |  |

|                | 2.5 Pulse width modulation switching techniques  2.5.1 Subharmonics pulse width modulation  2.5.2 Phase shifting PWM technique  2.5.3 Switch frequency optimal PWM  2.6 Comment on different techniques of PWM  2.7 Comparison between FFS and PWM methods  2.71 Total harmonic distortion  2.7.2 Power losses  2.7.3 Transient response  3.1 Introduction  3.2 STATCOM operation  3.3 Control strategies  3.4 Main control loops  3.4.1 Phase locked loop  3.5 A rotated switching scheme of fundamental frequency  3.6 Method of pre-charging the inverter  pter 4 - Test studies  4.1 EMTDC system model  4.2 Operational characteristics  4.2.1 Start-up of the STATCOM  4.2.2 Steady state operation  4.2.3 Transient operation  4.2.4 Capacitor voltage balance  4.3 The sysyem performance with PWM  4.3.1 Steady state operation  4.4. Comparation between PWM and FFS response during dynanic operation  4.4 Comparation between PWM and FFS response during dynanic operation  5.1 Conclusions |         |  |  |  |  |  |

|                | A WAVIAGE ALVOVAMIANVANGHOUNCE !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6       |  |  |  |  |  |

| Appendix A - | 71 |

|--------------|----|

| Appendix B - | 72 |

# **List of Figures**

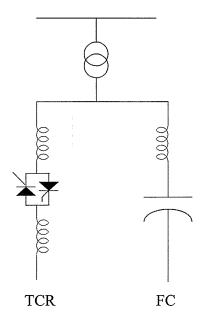

| Fig. 1. 1  | A Simplified Diagram of FC/TCR SVC                       | 3  |

|------------|----------------------------------------------------------|----|

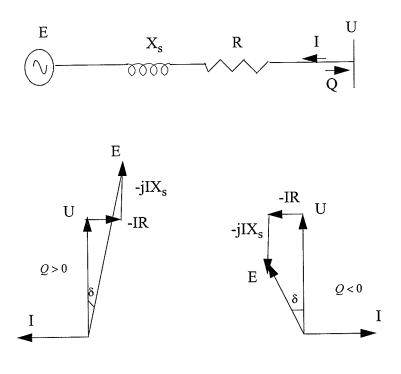

| Fig. 1. 2  | An Equivalent Circuit and Vector Diagram of the          |    |

|            | Synchronous Condenser.                                   | 5  |

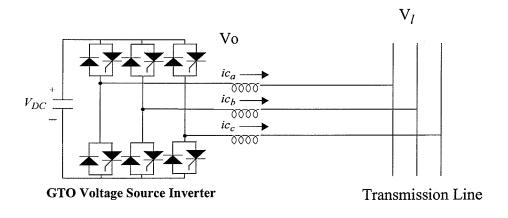

| Fig. 1. 3  | Basic STATCOM with Elementary Six-pulse Inverter         | 7  |

| Fig. 1. 4  | Comparison of VAR Output between                         |    |

|            | Conventional SVC and STATCOM.                            | 9  |

| Fig. 2. 1  | One Phase of Diode-clamped N-level Inverter              | 4  |

| Fig. 2. 2  | Five-Level Diode-clamped Inverter Waveform 1             | .5 |

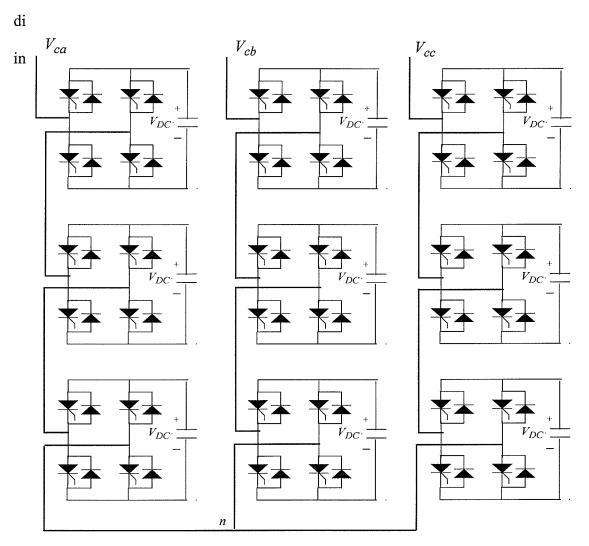

| Fig. 2. 3  | The Three Phase Y-structure 7-level Cascaded Inverter1   | 6  |

| Fig. 2. 4  | The H-bridge Inverter and its Three Level                |    |

|            | Output Voltage Waveform                                  | 7  |

| Fig. 2. 5  | The One Phase 7-level Cascaded Inverter                  | 2  |

| Fig. 2. 6  | The Output Voltage Waveform for Each H-bridge 2:         | 3  |

| Fig. 2. 7  | The 7-Level Stepped-waveform.                            | 4  |

| Fig. 2. 8  | The Output 7-level Voltage Waveform Using                |    |

|            | FFS Method.                                              | 28 |

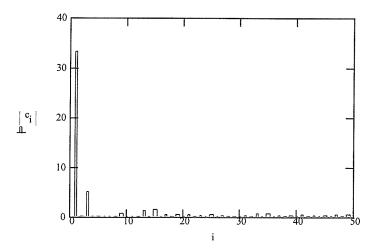

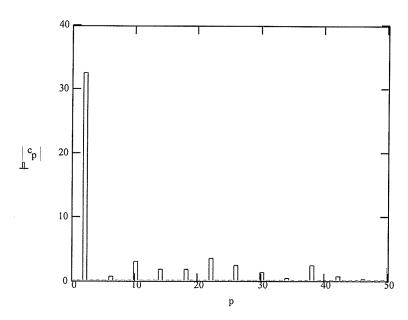

| Fig. 2. 9  | Harmonic Spectra For Line-neutral 7-level Voltage Output |    |

|            | Waveform Using FFS Method                                | 8  |

| Fig. 2. 10 | The Principle of The SHPWM for n=7, k=7,and MI=1.0.      | 31 |

| Fig. 2. 11   | The Principle of The PS-PWM for $n = 5$ ,          |      |

|--------------|----------------------------------------------------|------|

|              | k = 9, and MI = 1.0                                | 30   |

| Fig. 2. 12   | The Principle of The SFO PWM for n=7, k=7,and      |      |

|              | MI=1.0                                             | 34   |

| Fig. 3. 1    | STATCOM Operation Principle                        | 41   |

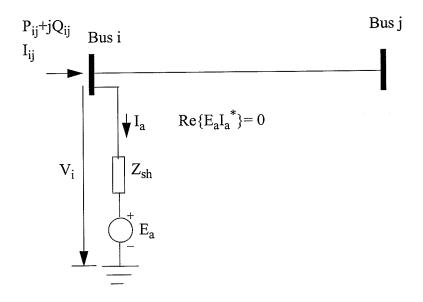

| Fig. 3. 2    | STATCOM Equivalent Circuit.                        | 42   |

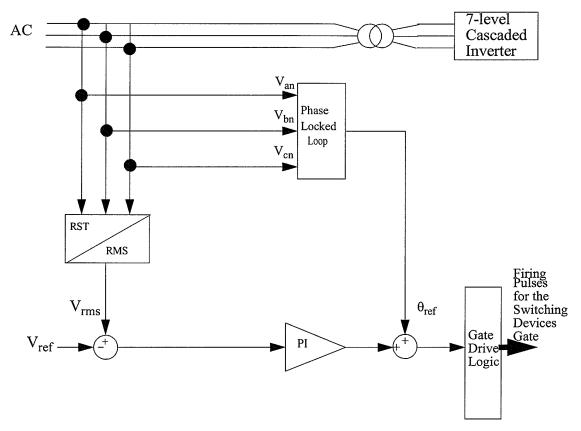

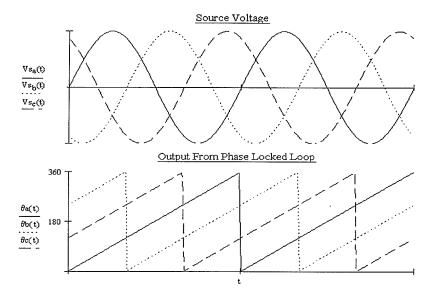

| Fig. 3. 3    | Basic Control Loops for The M-STATCOM              | 45   |

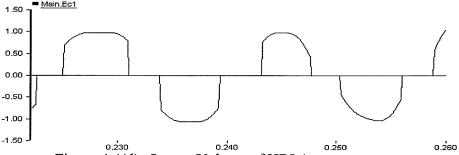

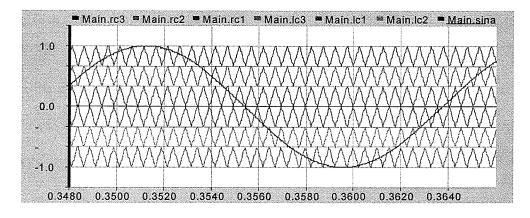

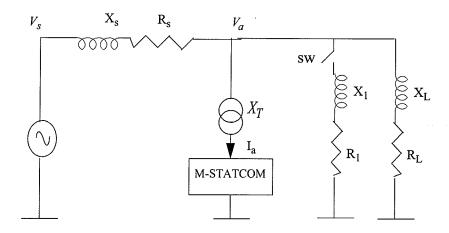

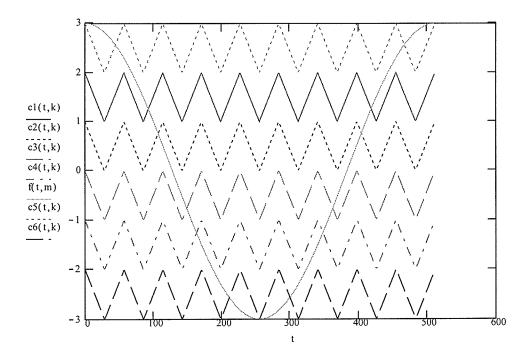

| Fig. 3. 4    | Output Signals from Phase Locked Loop.             | . 46 |

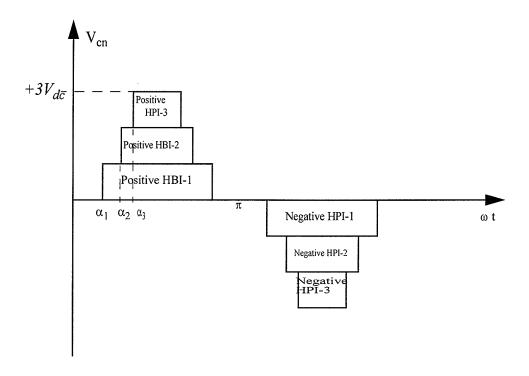

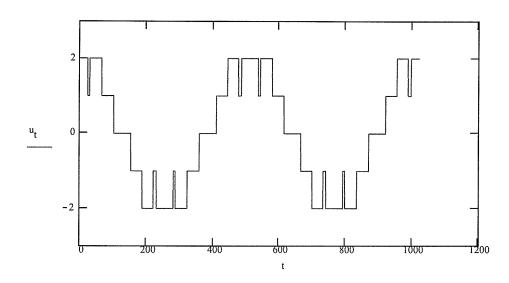

| Fig. 3. 5    | Waveforms of The 7-level Cascaded Inverter         | . 47 |

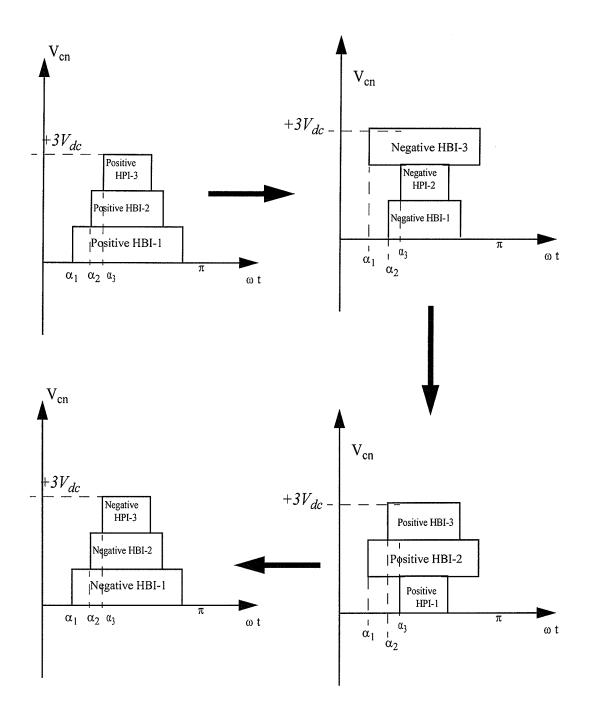

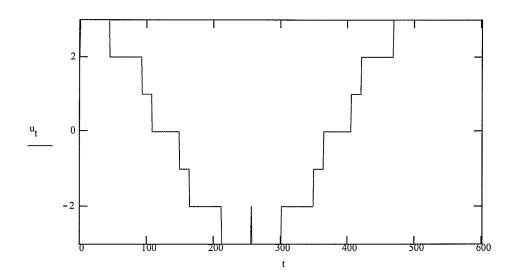

| Fig. 3. 6    | Method of Signal Pulse Rotation Every Half Cycle   | 49   |

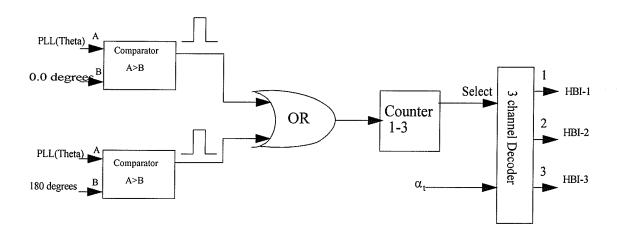

| Fig. 3. 7    | The control logic scheme of Rotated                |      |

|              | Switching Pattern                                  | 50   |

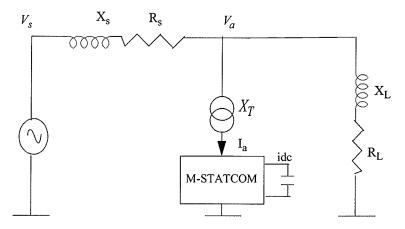

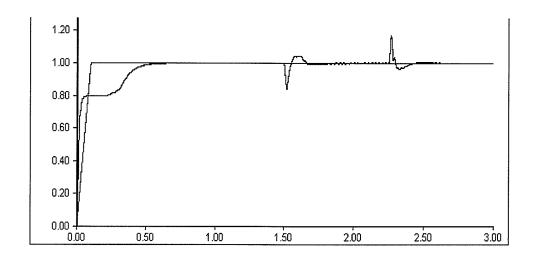

| Fig. 4. 1    | A Schematic Diagram of The Simulation Test System. | 53   |

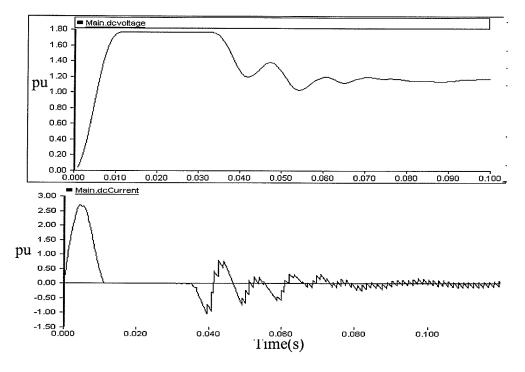

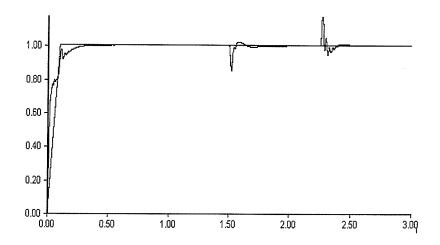

| Fig. 4. 2    | The capacitance voltage and current Without        |      |

|              | a Pre-insertion Resistor.                          | 54   |

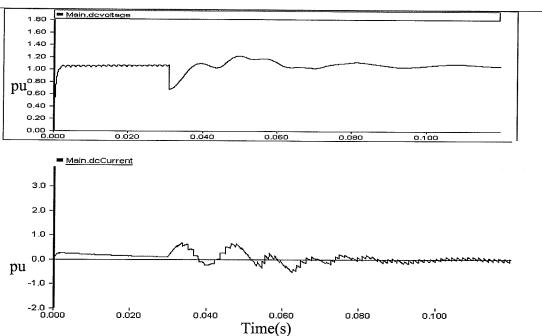

| Fig. 4. 3    | The capacitance voltage and current With           |      |

|              | a Pre-insertion Resistor.                          | 55   |

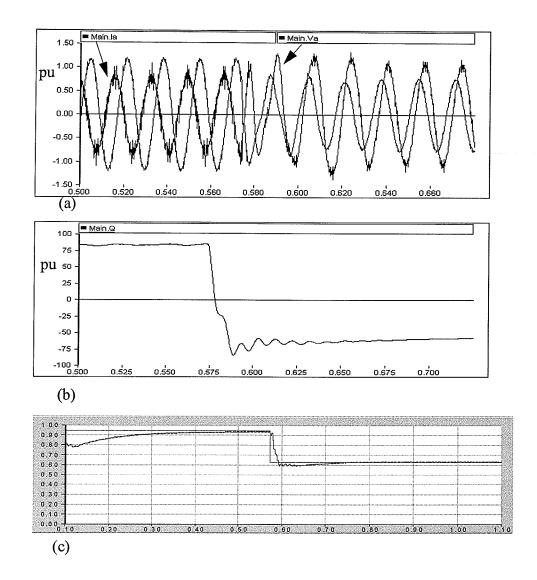

| Fig. 4. 4(a) | The Inverter Output Voltage and Current            |      |

|              | at the a.c Side                                    | 56   |

| Fig. 4. 4(b) | The Forurier Analysis of The Compensator Current.  | 56   |

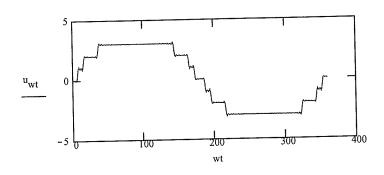

| Fig. 4. 5    | The Transient Response of The M-STATCOM            | 58   |

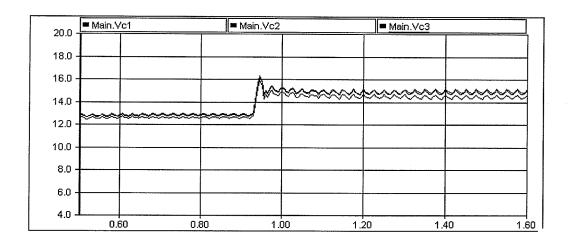

| Fig. 4. 6    | The Capacitive Voltage With Non-Rotated            |      |

|              | Switching Pattern.                                 | 59   |

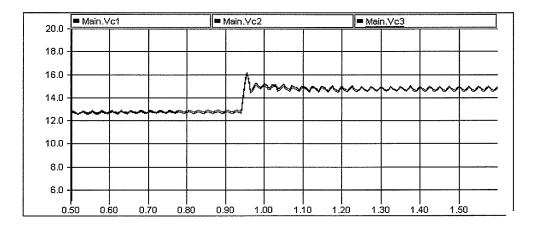

| Fig. 4. 7    | The Capacitive Voltage With Rotated                |      |

|              | Switching Pattern                                  | 59   |

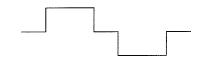

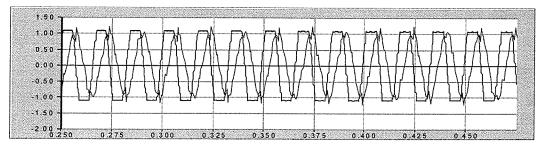

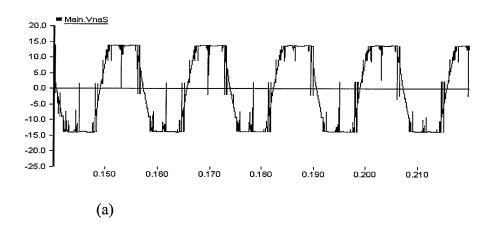

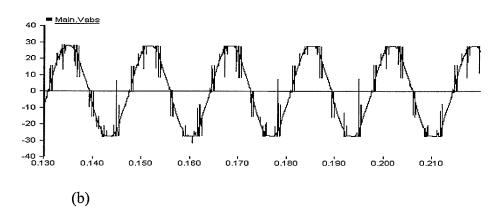

| Fig. 4. 8                                              | 4. 8 Multi-carrier Waveform Technique             |    |  |  |  |  |

|--------------------------------------------------------|---------------------------------------------------|----|--|--|--|--|

| Fig. 4. 9 Inverter Output Voltage When PWM is Applied. |                                                   |    |  |  |  |  |

|                                                        | a) Phase Voltage, and b) Line Voltage             | 61 |  |  |  |  |

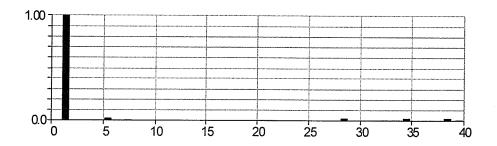

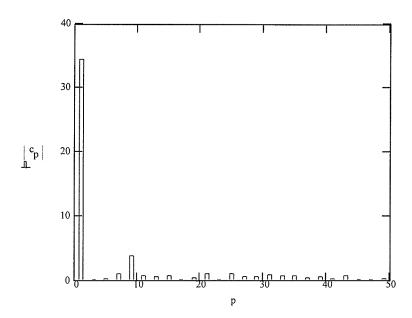

| Fig. 4. 10                                             | Line Voltage Spectrum.                            | 62 |  |  |  |  |

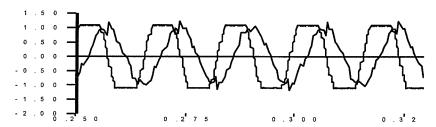

| Fig. 4. 11                                             | The Dynamic Response of The STATCOM with PWM.     | 63 |  |  |  |  |

| Fig. 4. 12                                             | The Dynamic Response of The STATCOM with FFS.     | 63 |  |  |  |  |

| Fig. 4.13                                              | A Schematic Diagram of The Simulation Test System |    |  |  |  |  |

|                                                        | under dynamic                                     | 64 |  |  |  |  |

## **List of Tables**

| Table 2. 1 | The Gate Logic for Five-level Diode-clamped Inverter | 15 |

|------------|------------------------------------------------------|----|

| Table 2. 2 | The Calculated Switching Angle for Different MI      | 27 |

| Table 2. 3 | Typical Calculating Result Using FFS Method          | 37 |

| Table 2. 4 | Typical Calculating Result Using SH-PWM Method       | 36 |

| Table 2. 5 | Typical Calculating Result Using SEO-PWM Method      | 37 |

## List of Symbols

Some of the most frequently occurring abbreviation and symbols used in the Thesis are tabulated below. Others are explained where they are used.

## Table A.2

| i abic A.2                                   |                                                   |  |  |  |  |

|----------------------------------------------|---------------------------------------------------|--|--|--|--|

| Ac                                           | Peak-to-peak amplitude of the carriers            |  |  |  |  |

| ac                                           | Alternating current                               |  |  |  |  |

| $A_{m}$                                      | Amplitude of the modulating signal                |  |  |  |  |

| A <sub>c</sub> Amplitude of the carrier wave |                                                   |  |  |  |  |

| dc                                           | Direct current                                    |  |  |  |  |

| EMTDC                                        | Electromagnetic Transient Program for dc system   |  |  |  |  |

| FC                                           | Fixed capacitor                                   |  |  |  |  |

| $ m f_{c}$                                   | Frequency of the carriers                         |  |  |  |  |

| FFS                                          | Fundamental frequency switching                   |  |  |  |  |

| $f_{m}$                                      | Frequency of the modulating signal                |  |  |  |  |

| GTO                                          | Gate Turn Off thyristor                           |  |  |  |  |

| HVDC                                         | High Voltage Direct Current                       |  |  |  |  |

| k                                            | Frequency ratio                                   |  |  |  |  |

| kA                                           | Kiloampere                                        |  |  |  |  |

| kV                                           | Kilovolt                                          |  |  |  |  |

| MI                                           | Modulation index                                  |  |  |  |  |

| M-STATCOM                                    | Multilevel GTO thyristor inverter type of STATCOM |  |  |  |  |

| Mvar                                         | Mega-var                                          |  |  |  |  |

| PI                                           | Proportional integral                             |  |  |  |  |

| PLL                                          | Phase Locked Loop                                 |  |  |  |  |

| PWM                                          | Pulse Width Modulation                            |  |  |  |  |

### Table A.2(continued)

SC Synchronous condenser

SFO-PWM Switching frequency optimal PWM

SH-PWM Sub harmonic PWM

STATCOM Voltage source inverter type of the var compensator

SVC Static var compensator

TCR Thyristor controlled reactor

THD Total Harmonic Distortion

TSC Thyristor switched capacitor

var Volt-ampere reactive

VSI Voltage Source Inverter

ω System frequency

### **CHAPTER 1**

## CHAPTER 1 Introduction

#### 1.1 BACKGROUND

In an ac power system the transmittable electric power is related to the transmission line voltage profile under steady state and dynamic conditions over a wide range of network contingencies. It is known that the voltage profile along the transmission line can be controlled in a more effective way by controlling the reactive power flow in the line.

INTRODUCTION 2

The application of the reactive power conditioner is a well established practice and it is termed as 'reactive power compensation'. The methods that have long been employed to increase the steady state power of the line are fixed or mechanically switched capacitors and reactors. The reactors are installed in shunt at intervals along the line and large capacitors are connected in series or in parallel. With the development of high power solid state devices such as the thyristor along with electronic controls, new devices have emerged which offer smooth continuous control of reactive power. Thyristor controlled series compensators (TCSC) can control the amount of series compensation of the transmission line and static var compensators (SVC) can control the amount of the reactive power injected into or absorbed from the transmission system. During the last decade it has been convincingly demonstrated that both the transient and dynamic stability of the power system can be improved, and voltage collapse can be prevented [1] with rapid continuously variable control accomplished by such solid state technology. A few years ago the integrated gate commutated thyristor (IGCT) was developed which has power ratings comparable to that of the conventional thyristor. This has led to the development of self commutated converters for reactive power sources. This new technology has resulted in equipment that is fundamentally different from the conventional thyristor-controlled static var compensator (SVC). The new equipment is called the Advanced Static Var Compensator or STAT-COM. It has many technical advantages over the conventional SVC.

#### 1.2 CONVENTIONAL STATIC VAR COMPENSATOR (SVC)

The traditional static var compensators use either banks of shunt connected capacitors or thyristor-switched capacitors with thyristor controlled reactors to provide the needed

3

controlled shunt reactive power compensation. A simplified diagram of a fixed capacitor / thyristor control reactor (FC/TCR) type of compensator is shown in Figure 1.1 and its elements are:

- I) The fixed capacitor (FC), provides a permanently connected generation of reactive power, designed also to act as suitable harmonic filter.

- II) The thyristor controlled reactor (TCR) consisting of anti-parallel thyristors connected in series with shunt reactors usually in a delta configuration. These controlled reactors are used to absorb reactive power. The thyristor may be switched at any point over the half wave (90 to 180 electrical degrees behind the voltage sine wave) to provide a fully adjustable control from 100 percent to zero of rated reactive power absorption.

- III) Power transformer to connect to the high voltage busbar.

Figure 1.1 A Simplified Diagram of FC/TCR SVC

The disadvantages of the SVC here are [2]:

- a) The ac capacitor banks consist of capacitor units in parallel. Therefore, particular care must be exercised to ensure proper separation between capacitor groups in the event of an external flashover.

- b) Due to their physical size and other considerations, the reactor and the capacitor banks are mounted outdoors, in the switchyard. Their insulation system must withstand harsh environmental conditions.

- c) The FC tends to lower system resonant frequency.

For these reasons, the traditional static var compensators form quite a large system, requiring considerable equipment at significant cost. This may limit their application in densely populated areas where severe environmental and space restrictions are imposed.

## 1.3 Principles of the STATCOM

The shunt static compensator or STATCOM (for Static Compensator) is an electronic equivalent of the synchronous condenser, synchronous machine not driven by a prime mover connected to the power system. The equivalent circuit and Phasor diagram of the synchronous condenser are shown in Figure 1.2. By varying the magnitude of the excitation, or field current, both the amount and the direction of the reactive power produced by

the synchronous condenser can be changed. That is, if the excitation current is increased up to such level that the amplitude of the internal voltage of the synchronous condenser is higher than the voltage of the equivalent ac system (E>U), then the current flows through the synchronous reactance and winding resistance from the synchronous condenser to the ac system, and the synchronous condenser generates reactive power for the ac system (capacitive). If

Figure 1. 2 A Equivalent Circuit and Phasor Diagram of the Synchronous condenser

the excitation current is decreased to a level such that the internal voltage is less than the voltage of the equivalent ac system (E < U), then the current flows through the reactance and resistance from the ac system to the synchronous condenser, and the synchronous condenser absorbs reactive power from the ac system (inductive). If the amplitude of the

INTRODUCTION 6

internal voltage of the synchronous condenser is equal to the voltage of the equivalent ac system (E = U), the reactive power exchange is zero. As the stator resistance, R, is much less than the synchronous reactance,  $X_s$ , the angle  $\delta$  is very small and E and U are essentially in phase. The only power flow into the synchronous machine is to overcome the losses of the machine.

#### 1.4 The Basic STATCOM.

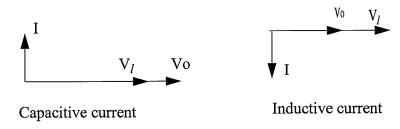

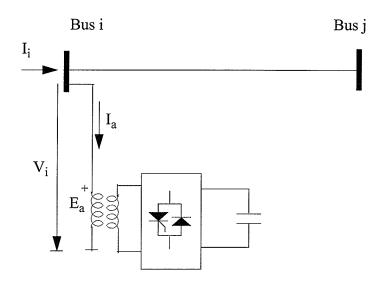

The STATCOM is based on a simple concept. A GTO based power converter is used to produce an alternating voltage source in phase with the transmission line voltage, and is connected to the line through a series inductance (usually the transformer leakage). When the voltage source is greater than the line voltage, leading reactive current is drawn from the line and the equipment acts as a capacitor. When the voltage source is smaller than the line voltage, lagging reactive current is drawn from the line and the equipment acts as inductor. In practice a small amount of real power is also drawn from the line to supply the losses of the converter. The basic electronic building block for a STATCOM is a voltage-sourced inverter that converts the dc voltage at its input terminals into a threephase set of output voltages. A six-pulse inverter, the simplest implementation of such an inverter, is illustrated in Figure 1.3, together with a typical line-to-line output voltage waveform. In practice, a quasi-square waveform such as this would produce unacceptable current harmonics when connected to a line. Consequently a practical STATCOM must use some technique to control the harmonics. The approaches have been to use many such inverters, appropriately phase shifted, with their outputs combined magnetically to produce a nearly sinusoidal resultant waveform [3], to use some kind of PWM switching technique, and/or to use the multilevel inverter to improve the harmonics.

7

If

$$V_l = V_0$$

,  $I = 0$

If  $V_l < V_0$ , I is capacitive

If  $V_l > V_0$ , I is inductive

Inverter output line-to-line voltage

Phasor Diagram of the STATCOM

Figure 1. 3 Basic STATCOM with Elementary Six-pulse Inverter.

#### 1.5 ADVANTAGES OF STATOM OVER SVC

The advantages of the STATCOM design over the traditional fixed capacitor/thyristor controlled reactor (FC/TCR) or thyristor switched capacitor/thyristor controlled reactor (TSC/TCR) type design are:

- a. The voltage source converter is more compact and requires only a small coupling reactance, usually the ac system transformer leakage and a single dc capacitor about one-eighth of the size of the capacitor in a SVC of the same rating [4]. This leads to a significant reduction in equipment size and installation cost.

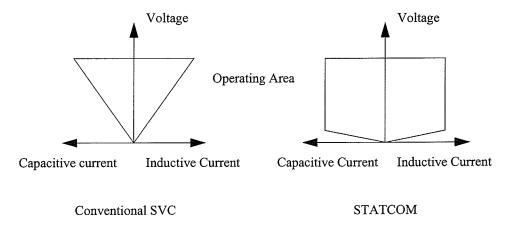

- b. The design offers a fast continuous variation of reactive output power from capacitive to inductive, and more effective reactive power generation during undervoltages. The improvement in var output of the STATCOM during under voltage conditions is illustrated in Figure 1.4.

- c. Better control stability [5] which translates to superior performance during major transients and, ultimately, increased system transient stability and improved damping.

However, many design considerations lie in the path of the development of the STATCOM, such as system configuration, control of the switching losses and harmonic distortion, the balancing of the dc voltage of STATCOM and the system response to the step change of reactive power.

Figure 1. 4 Comparison of VAR output between Conventional SVC and STATCOM

For these reasons, the multilevel-STATCOM(M-STATCOM) using cascaded multilevel inverters is studied in this thesis, which will offer an interesting alternative to other circuit topologies being considered for the STATCOM.

### 1.6 The Scope Of The Thesis

1.6.1 Review of different topologies of multilevel inverters.

There are mainly three different system configurations of multilevel voltage source inverters suitable for STATCOM application. They are:

- 1- Diode-clamped converter configuration

- 2-Flying-capacitor converter configuration.

- 3- Cascade converter configuration.

INTRODUCTION 10

The first and third configuration will be discussed in Chapter 2. A 7-level cascade GTO inverter was chosen as the candidate design of the M-STATCOM in Chapter 4.

#### 1.6.2 Investigation of the switching methods

For a 7-level cascade inverter, both the fundamental frequency switching (FFS) and pulse width modulation (PWM) technique will be studied to determine which switching method is best.

#### 1.6.3 Control Strategy Study

Development of suitable control strategies which will be aimed at:

- 1- Maintaining individual dc capacitor voltages at desired levels.

- 2- Realizing the reactive current output control.

- 3- Obtaining excellent dynamic performance with high control stability.

### 1.6.4 Digital Simulation

A 7 level cascade multilevel inverter based STATCOM will be simulated using the electromagnetic transient simulation program called PSCAD/EMTDC<sup>TM</sup> which is the product of Manitoba HVDC Research Centre, Canada.

1.6.5 In Chapter 5, some of the results and conclusions from the above studies will be listed.

INTRODUCTION 11

## CHAPTER 2 Analysis of a Multilevel GTO Thyristor Inverter

#### 2.1 Introduction

MULTILEVEL power conversion has been receiving increased attention in the past few years for high-power applications [6]. Numerous topologies and modulation strategies have been introduced and studied extensively for utility and drive applications in the recent literature [7]. These converters are suitable in high-voltage and high-power applications due to their ability to synthesize waveforms with better harmonic spectrum and attain higher voltages with a limited maximum device rating. In this multilevel voltage source inverter (VSI) based on STATCOM category, there are mainly three different system configurations. They are 1) diode-clamped converter configuration [8], 2) cascade converter configuration [9] and 3) flying-capacitor converter configuration. In this chapter the first configuration will be analyzed in brief and focus will be given to the second configuration to develop STATCOM system in this thesis.

#### 2.2 Diode-Clamped Multilevel Inverter

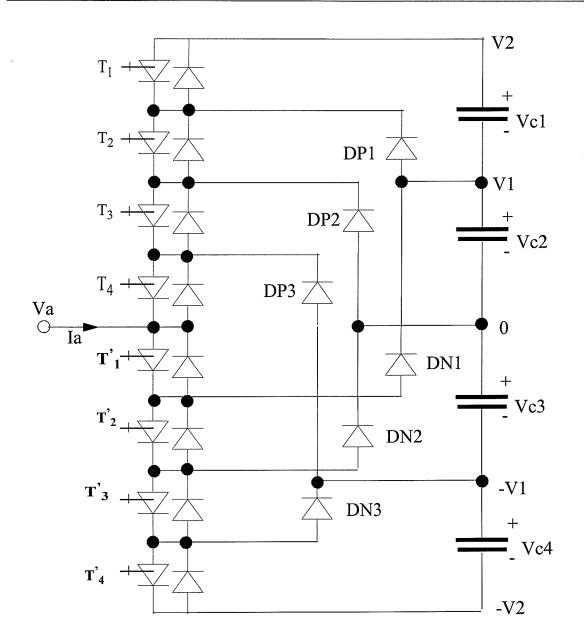

The diode-clamped multilevel inverter uses one dc bus subdivided into a number of voltage levels by a series string of capacitors [10]. A generalized structure of one phase of an 5-level GTO inverter is shown in Figure 2.1 where the level number N=5. The dc capacitors are shared by the other phases, and possibly by the other bridges in higher pulse number designs. In a three-phase bridge configuration the number of level in the line-toline voltage will be 2N+1. The advantages of such a structure is that the thyristor needs only block the voltage of its own level and not the full dc voltage. Furthermore, each GTO thyristor is well protected against overvoltage by the clamping action of the dc capacitors. The lower group of GTO thyristors requires the complementary gating pulses of the upper group of the same number. That is if T2 is on, then T'2 must be off. It should be mentioned that for each voltage step only one GTO thyristor must turn on and one GTO thyristor must turn off. For example, if  $T_1$  is off, then  $T_2$ ,  $T_3$ ,.... $T_{N-1}$  and  $T_1$  are on, and the terminal V1 is connected to the output terminal through  $DP_1$ ,  $T_2$ ,  $T_3$ ,.... $T_{N-1}$  for positive current, or through  $T_1$  and  $DN_1$  for negative currents. As described above, taking one single phase into account, the five voltage levels could be achieved at the output terminal if the gate logic in Table 2.1 is followed, a stepped output voltage of the five level inverter shown in Figure 2.2, which is a simple sum of the two rectangular waveforms. It should be noted that the clamping diodes are required to block different voltages, e.g. DP<sub>1</sub> must block the voltage of a single dc level, V, while DP<sub>N-2</sub> must block (N-2)Vc, assuming that all the capacitor voltage are equal to Vc.

Figure 2.1: One Phase of Diode-clamped 5-level Inverter

Table 2.1 The Gate Logic for Five-level Diode-clamped Inverter

| output            | The state of GTO thyristors |       |                       |       |                 |     |     |                 |

|-------------------|-----------------------------|-------|-----------------------|-------|-----------------|-----|-----|-----------------|

| (E <sub>a</sub> ) | $T_1$                       | $T_2$ | <b>T</b> <sub>3</sub> | $T_4$ | T' <sub>1</sub> | T'2 | T'3 | T' <sub>4</sub> |

| $+2V_{c}$         | 1                           | 1     | 1                     | 1     | 0               | 0   | 0   | 0               |

| $+V_c$            | 0                           | 1     | 1                     | 1     | 1               | 0   | 0   | 0               |

| 0                 | 0                           | 0     | 1                     | 1     | 1               | 1   | 0   | 0               |

| $-V_c$            | 0                           | 0     | 0                     | 1     | 1               | 1   | 1   | 0               |

| $-2V_c$           | 0                           | 0     | 0                     | 0     | 1               | 1   | 1   | 1               |

In the above Table we assumed that  $V_{c1} = V_{c2} = V_{c3} = V_{c4} = V_c. \label{eq:Vc2}$

Figure 2.2: Five level Diode-clamped Inverter Waveform Voltage

## 2.3 Cascade Multilevel Inverters

## 2.3.1 Circuit and Working Principle

The cascade inverter is made up from series connected single phase full bridge inverters, each with their own isolated dc bus [11]. Figure 2.3 illustrates the connection

Figure 2.3 The Three Phase Y-structure 7-level Cascade Inverter

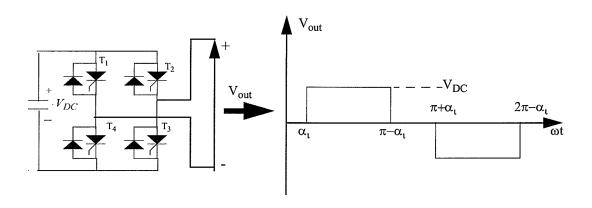

It is clear from Figure 2.3 that to have M-level cascade multilevel inverters we need  $\left(\frac{M-1}{2}\right)$  H-bridge units in each phase. Each H-bridge inverter can generate three level outputs,  $V_{dc}$ , 0, and  $-V_{dc}$ . Figure 2.4 shows the structure of one unit of H-bridge inverter and its three level output voltage waveform. And the output voltage of M-level inverter is a simple sum of the M-rectangular waveform from each H-bridge inverter for each phase. There are many switching techniques to control the output voltage of the H-bridge inverter. We will discuss two of them the Fundamental Frequency Switching (FFS) method and the Pulse Width Modulation (PWM) technique in a later section.

Figure 2.4. The H-bridge Inverter and its Three Level Output Voltage Waveform

### 2.3.2 The Advantages and Disadvantages of Cascade Multilevel Inverter

There are three types of multilevel inverters as stated before, the most common two of them are the cascade type and the diode-clamped type. The following are some of the advantages of the cascade type compared to diode-clamped type.

- 1- The diode-clamped configuration requires a very large number of clamping diodes where the cascade configuration does not require clamping diodes.

- 2- In the case of the cascade configuration, the packaging and physical layout is very simple in comparison with diode-clamped configuration due to its modular structure. It is constructed by cascading several voltage source H-bridge inverters.

- 3-The problem of dc voltage unbalancing between the capacitors is more severe in the case of the diode-clamped configuration than in case of the cascade configuration, as in case of cascade type each H-bridge can be controlled independently.

The cascade converter has the following disadvantages:

- 1) The dc voltage unbalancing between the capacitors of each inverter makes it difficult to regulate the output voltage of the STATCOM with cascade multilevel inverter.

- 2) The dc voltage unbalancing makes system design, maintenance and stocking of spare parts complicated.

Different methods and control strategies have been investigated in resent years to overcome the dc voltage unbalancing between the capacitors of each H-bridge inverter. An installation with one of these methods is in service where an SVC, rated 0 to +225 Mvar at 400 kV is operating in East Claydon substation in Buckinghamshire, England [20]. The SVC comprises a fixed filter of 23 Mvar, a conventional TSC of 127 Mvar and GTO-based 33-level cascade inverter STATCOM rated at +/- 75 Mvar. The dc capacitor voltage

charging and balancing is accomplished by using a dual IGBT rectifier/inverter at each H-bridge, which are connected to an auxiliary power transfer bus at earth potential via a fully insulated auxiliary power isolating transformer (APIT). The rating of the inverter/APIT combination is 5 kVA at 7.5 kHz. Although the test study on the system showed good results, these results were accomplished at the expense of adding more devices and complicating the control system. On other hand, in this thesis an alternative approach illustrated in Chapter 3 based on the rotated switching scheme [19] of fundamental frequency is studied, which is more cost efficient and easier to implement.

#### 2.3.3 The Output Voltage Control of the Cascade Multilevel Inverter

It is clear by examining the cascade inverter structure as described in Section 2.3.1 that the H-bridge inverter forms the building block of the cascade multilevel inverter, therefore by controlling of the individual H-bridge voltages, we can control the total output voltage of the cascade inverter. By referring to Figure 2.4 we can see that there are mainly three methods to control the output voltage of the H-bridge inverter. These method are as follows:

- 1- By controlling the output voltage pulse width by Fundamental Frequency Switching (FFS) method or PWM technique while keeping the dc voltage fixed. This can be done by controlling the firing angle value of the GTO.

- 2- By controlling the dc voltage value while keeping the output voltage pulse width fixed or by controlling the modulation index in case of PWM.

3- By controlling the both values of dc voltage and the output voltage pulse width.

The basis of selecting the method of controlling the inverter output voltage is dependent on the ability to control the total harmonic distortion. The second method will be adopted in this thesis to control the inverter output voltage as it makes it easier to implement the Selected Harmonic Elimination method (SHE), illustrated in the coming section, which keeps the total harmonic distortion low in the output voltage of the inverter. The dc voltage magnitude of the inverter will be controlled by controlling the phase angle difference between the fundamental of the converter output voltage  $(V_0)$  and the ac system voltage, which leads to control, of the magnitude of  $V_0$  and the reactive current produced by the STATCOM. There are mainly two switching methods to achieve the above objective, the Fundamental Frequency Switching (FFS) and the Pulse Width Modulation (PWM) Switching Techniques.

#### 2.4 Fundamental Frequency Switching (FFS) of GTO's

Using the fundamental frequency switching (FFS) method [12], each GTO thyristor is switched on and off once during a power frequency (60 Hz) cycle.

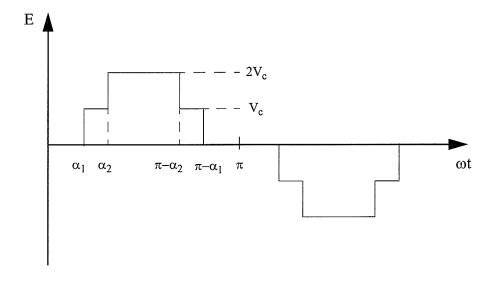

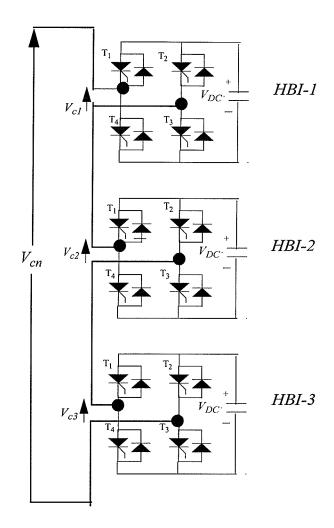

As mentioned earlier, the H-bridge inverter forms the building block of the cascade multilevel inverters. For simplification let us consider one phase of a 7-level cascaded multilevel inverter as shown in Figure 2.5, it is clear from the figure that it consists of three H-bridge inverters per-phase, called HBI-1, HBI-2 and HBI-3.

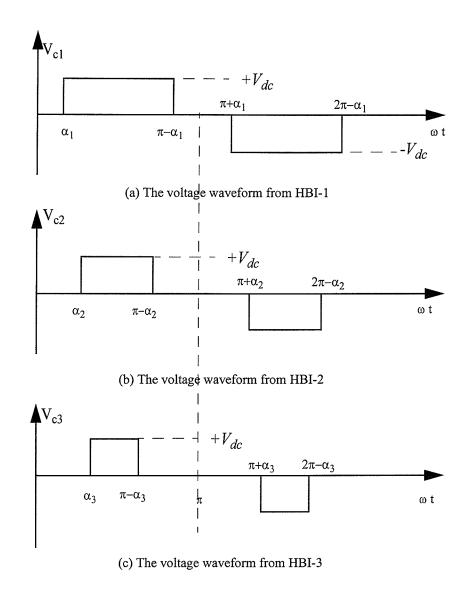

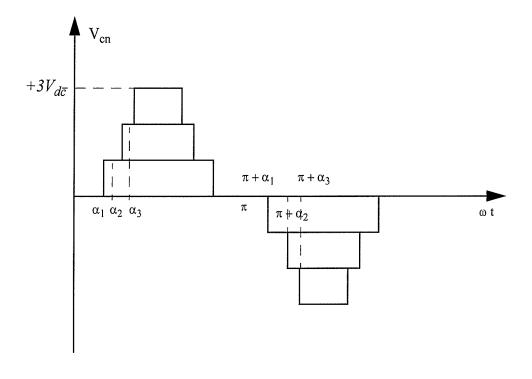

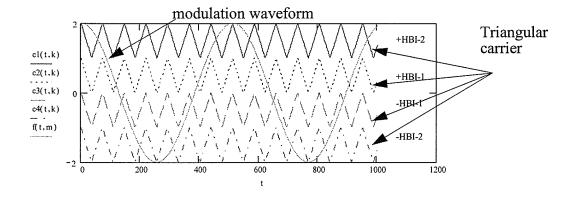

To generate 7-level voltage waveform at the output terminal of the 7-level, single phase cascaded inverter shown in Figure 2.5, by applying FFS technique to each H-bridge inverter, let us start by examine the first H-bridge inverter (HBI-1). We can see that the main switching devices  $T_1$ ,  $T_2$ ,  $T_3$  and  $T_4$  can be any self-commutated devices such as a IGCT or an IGBT transistor (for lower rating). In one cycle period each switch must be turned on for  $\pi$  period and turn off for the remaining  $\pi$  period. If the H-bridge inverter switching devices turned on for  $\pi$  period, each switch as follow:  $T_1$  at  $-\alpha$  angle,  $T_4$  at  $(\pi - \alpha_1)$ ,  $T_3$  at  $\alpha_1$  angle and  $T_2$  at  $(\pi + \alpha_1)$  angle and turn them off at  $(\pi - \alpha_1)$ ,  $2\pi - \alpha_1$ ,  $(\pi + \alpha_1)$  and  $2\pi + \alpha_1$  angle, respectively. The inverter output voltage will be as follow: between the period zero to  $\alpha_1$ ,  $T_1$  and  $T_2$  are on then the load terminal will be connected to zero voltage, between the period  $\alpha_1$  to  $(\pi - \alpha_1)$ ,  $T_1$  and  $T_3$  are on then the load terminal will be connected to the positive dc supply, between the period  $(\pi - \alpha_1)$  to  $(\pi + \alpha_1)$ ,  $T_4$  and  $T_3$ are on then the load terminal will be connected to zero voltage, between the period  $(\pi + \alpha_1)$ to  $2\pi - \alpha_1$ ),  $T_2$  and  $T_4$  are on at this period the load terminal will be connected to negative dc supply voltage and between the period  $2\pi - \alpha_1$ ) to  $(2\pi)$ ,  $T_1$  and  $T_2$  are on then the load terminal will be connected to zero voltage. By this way three level outputs  $+ V_{dc}$ , 0,  $- V_{dc}$ can be generated, as shown in figure 2.6 (a). If the same role is applied to other two Hbridge inverter HBI-2 and HBI-3 but with different firing angles  $\alpha_2$  and  $\alpha_3$ . Where

$$\alpha_1 < \alpha_2 < \alpha_3 < \frac{\pi}{2}$$

Figure 2.5: One Phase of a 7-Level Cascaded Multi-Level Inverters

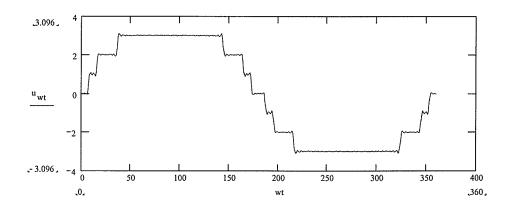

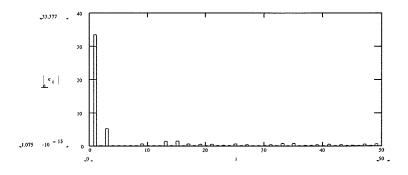

we generate an output voltage from each H-bridge as shown in Figure 2.7 (b & c). Then by simple sum of the three rectangular waveforms generated from HBI-1, HBI-2 and HBI-3 we can achieved our 7-level voltage waveform as shown in Figure 2.7.

Figure 2.6 The Output Voltage Waveform for Each H-Bridge

Performing the Fourier Transform for this waveform, the total output voltage can be obtained as:

$$E(\omega t) = V_c(\alpha_1, \omega t) + V_c(\alpha_2, \omega t) + V_c(\alpha_3, \omega t)$$

Where

$$V_c(\alpha_x, \omega t) = \frac{4V_c}{\pi} \sum_n \frac{1}{n} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{2} - n\alpha_x\right) \sin(n\omega t)$$

Where

$$x = 1,2 \text{ or } 3$$

$n = 1, 3, 5, 7,...$

$$E(\omega t) = \frac{4V_c}{\pi} \sum_{n} \frac{1}{n} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{2} - n\alpha_1\right) \sin(n\omega t) + \frac{4V_c}{\pi} \sum_{n} \frac{1}{n} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{2} - n\alpha_2\right) \sin(n\omega t)$$

$$\frac{4V_c}{\pi} \sum_{n} \frac{1}{n} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{2} - n\alpha_3\right) \sin(n\omega t)$$

$$E(\omega t) = \frac{4V_c}{\pi} \sum_{n} \frac{1}{n} [\cos(n\alpha_1) + \cos(n\alpha_2) + \cos(n\alpha_3)] \sin(n\omega t)$$

Where n = 1, 3, 5, 7,...

From the formula (2.1), the magnitude of the Fourier coefficients can be obtained, which is equal to the magnitude of the  $n^{th}$  harmonic normalized to  $V_c$  as follows:

$$H(n) = \frac{4}{\pi n} [\cos(n\alpha_1) + \cos(n\alpha_2) + \cos(n\alpha_3)]$$

Eq....2.2

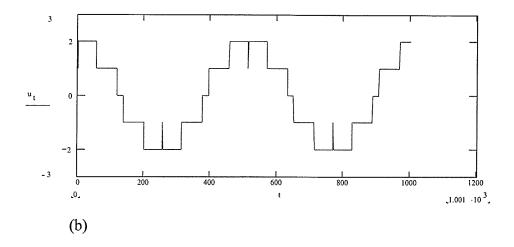

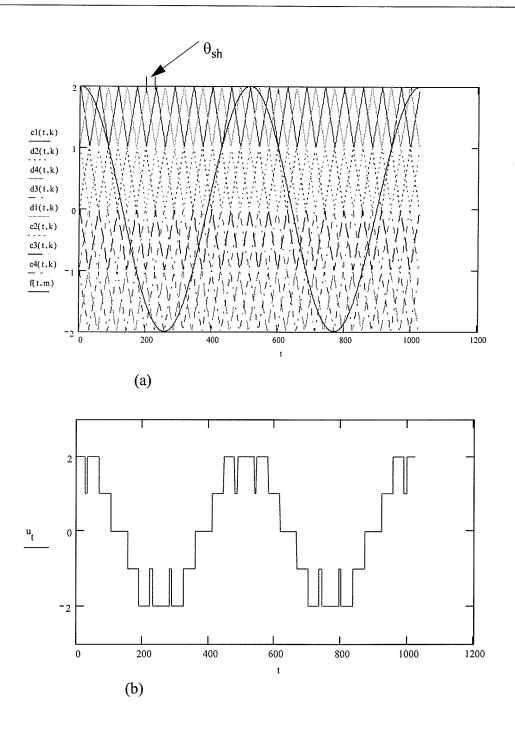

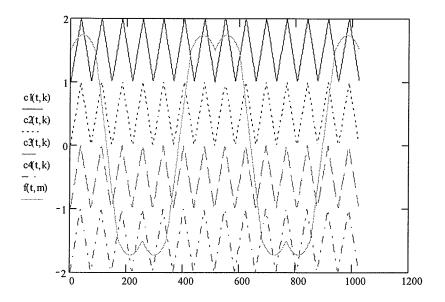

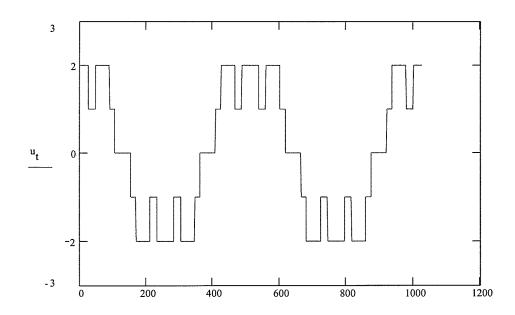

Where n = 1, 3, 5, 7,...