# HIGH SPEED SEQUENTIAL DEMODULATOR BASED ON SHIFT REGISTER SYSTOLIC PRIORITY QUEUE ARCHITECTURE

by Hoo Man Ng

#### A Thesis

Presented to the Faculty of Graduate Studies in Partial Fulfillment of the Requirements for the Degree

Master of Science

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg, Manitoba

© May, 1993

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse disposition la des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-85931-8

Name

Dissertation Abstracts International is arrangea by broad, general subject categories. Please select the one subject which most nearly describes the content of your dissertation. Enter the corresponding four-digit code in the spaces provided.

Electronics & Electrical

SUBJECT CODE

SUBJECT TERM

### **Subject Categories**

#### THE HUMANITIES AND SOCIAL SCIENCES

| COMMUNICATIONS AND THE Architecture Art History Cinema Dance Fine Arts Information Science Journalism Library Science Mass Communications Music Speech Communication Theater                                                                                                                                                            | 0729<br>0377<br>0900<br>0378<br>0357<br>0391<br>0399<br>0399 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| EDUCATION General Administration Adult and Continuing Agricultural Art Bilingual and Multicultural Business Community College Curriculum and Instruction Early Childhood Elementary Finance Guidance and Counseling Health Higher History of Home Economics Industrial Language and Literature Mathematics Music Philosophy of Physical |                                                              |

| y               | JUCIAL                                                                                                                      | <i><b>Seiena</b></i>      |                                                                                                      |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------|

| R S S S S S S S | sychology eading eligious ciences econdary ocial Sciences eciology of eacher Training eachnology ests and Measure ocational |                           | 0527<br>0714<br>0533<br>0534<br>0340<br>0529<br>0530                                                 |

| L               | ANGUAGE, LITEI<br>INGUISTICS                                                                                                |                           |                                                                                                      |

|                 | Ancient<br>Linguistics                                                                                                      |                           | 0289                                                                                                 |

|                 | General                                                                                                                     | glish)<br>nnch)<br>n<br>n | 0294<br>0295<br>0297<br>0298<br>0316<br>0591<br>0305<br>0352<br>0355<br>0593<br>0311<br>0312<br>0315 |

| PHILOSOPHY, RELIGION AND THEOLOGY                                                                          |                                      |

|------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Philosophy                                                                                                 | 0422                                 |

| Religion General Biblical Studies Clergy History of Philosophy of Theology                                 | ומכת                                 |

| SOCIAL SCIENCES American Studies                                                                           | 0323                                 |

| Anthropology Archaeology Cultural Physical Business Administration                                         | 0324                                 |

| General                                                                                                    | 0310<br>0272<br>0770                 |

| General Agricultural Commerce-Business Finance History Labor Theory Folklore Geography Gerontology History | 0503<br>0508<br>0508<br>0510<br>0511 |

| General                                                                                                    | 0578                                 |

#### THE SCIENCES AND ENGINEERING

| BIOLOGICAL SCIENCES                    |        |

|----------------------------------------|--------|

| Agriculture _                          |        |

| General                                | .0473  |

| AgronomyAnimal Culture and             | .0285  |

| Animal Culture and                     |        |

| Nutrition                              | 0475   |

| Animal Pathology<br>Food Science and   | .0476  |

| Food Science and                       |        |

| Technology                             | .0359  |

| Forestry and Wildlite                  | .0478  |

| Plant Culture                          | .0479  |

| Plant Pathology                        | .0480  |

| Plant Physiology                       | .0817  |

| Range Management                       | .0777  |

| Wood Technology                        | .0746  |

| DIGIOGY                                |        |

| General                                | .0306  |

| Anatomy                                | . 0287 |

| AnatomyBiostatistics                   | .0308  |

| Botany                                 | .0309  |

| Cell                                   | .0379  |

| Ecology                                | .0329  |

| Entomology                             | 0353   |

| Genetics                               | 0369   |

| Limnology<br>Microbiology<br>Molecular | .0793  |

| Microbiology                           | .0410  |

| Molecular                              | .0307  |

| Neuroscience                           | .031/  |

| Oceanography                           | .0416  |

| Physiology                             | .0433  |

| Radiation                              | 0821   |

| Veterinary Science                     | .0//8  |

| Zoology                                | .0472  |

| Biophysics                             |        |

| General                                |        |

| Medical                                | .0760  |

|                                        |        |

| EARTH SCIENCES                         |        |

| Biogeochemistry                        | .0425  |

| Geochemistry                           | .0996  |

| *                                                                                                                                                      |                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Geodesy Geology Geophysics Hydrology Mineralogy Paleobotany Paleoecology Paleontology Paleozoology Palynology Physical Geography Physical Oceanography | 0388<br>0411<br>0345<br>0426<br>0418 |

| HEALTH AND ENVIRONMENTA                                                                                                                                | L                                    |

| SCIENCES                                                                                                                                               |                                      |

| Environmental Sciences                                                                                                                                 | 0768                                 |

| Health Sciences                                                                                                                                        | 0. 00                                |

| General                                                                                                                                                |                                      |

| Audiology                                                                                                                                              | 0300                                 |

| Chemotherapy                                                                                                                                           | . 0992                               |

| Dentistry                                                                                                                                              | 036/                                 |

| Education                                                                                                                                              | 0740                                 |

| Hospital Management<br>Human Development                                                                                                               | 0758                                 |

| Immunology                                                                                                                                             | 0982                                 |

| Medicine and Surgery                                                                                                                                   | 0564                                 |

| Immunology  Medicine and Surgery  Mental Health                                                                                                        | 0347                                 |

| NUISING                                                                                                                                                | UJO7                                 |

| Nutrition                                                                                                                                              | 0570                                 |

| Nutrition<br>Obstetrics and Gynecology<br>Occupational Health and                                                                                      | 0380                                 |

| Occupational Health and                                                                                                                                | 0254                                 |

| O-bib-ll                                                                                                                                               | 0334                                 |

| Pathology                                                                                                                                              | 0571                                 |

| Therapy                                                                                                                                                | .0419                                |

| Pharmacy                                                                                                                                               | 0572                                 |

| Physical Therapy                                                                                                                                       | 0382                                 |

| Pharmacy<br>Physical Therapy<br>Public Health                                                                                                          | . 0573                               |

| Radiology                                                                                                                                              | .,05/4                               |

| Recreation                                                                                                                                             | 05/5                                 |

|                                                                                                                                                        |                                      |

| Speech Pathology<br>Toxicology<br>Home Economics                                                                                                                                                                             | 0460<br>0383<br>0386                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| PHYSICAL SCIENCES                                                                                                                                                                                                            |                                                                                      |

| Pure Sciences                                                                                                                                                                                                                |                                                                                      |

| Chemistry General                                                                                                                                                                                                            | 0485                                                                                 |

| Agricultural                                                                                                                                                                                                                 | 0749                                                                                 |

| Agricultural<br>Analytical                                                                                                                                                                                                   | .0486                                                                                |

| Biochemistry                                                                                                                                                                                                                 | 0487                                                                                 |

| Inorganic                                                                                                                                                                                                                    | 0488                                                                                 |

| Nuclear                                                                                                                                                                                                                      | 0738                                                                                 |

| Organic                                                                                                                                                                                                                      | 0490                                                                                 |

| Pharmaceutical                                                                                                                                                                                                               | 0491                                                                                 |

| Physical                                                                                                                                                                                                                     | 0.494                                                                                |

| Polymer<br>Radiation                                                                                                                                                                                                         | 0754                                                                                 |

| Mathematics                                                                                                                                                                                                                  |                                                                                      |

| Physics                                                                                                                                                                                                                      |                                                                                      |

| General                                                                                                                                                                                                                      | 0.405                                                                                |

| Ocherul                                                                                                                                                                                                                      | 0003                                                                                 |

| Acoustics                                                                                                                                                                                                                    | 0986                                                                                 |

| Acoustics                                                                                                                                                                                                                    | 0986                                                                                 |

| Acoustics                                                                                                                                                                                                                    | 0986                                                                                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science                                                                                                                                                                     | 0986<br>0606<br>0608                                                                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science                                                                                                                                                                     | 0986<br>0606<br>0608                                                                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and                                                                                                         | 0986<br>0606<br>0608<br>0748<br>0607                                                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and                                                                                                         | 0986<br>0606<br>0608<br>0748<br>0607                                                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and High Energy Fluid and Plasma                                                                            | 0986<br>0606<br>0608<br>0748<br>0607                                                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and High Energy Fluid and Plasma Molecular                                                                  | 0986<br>0608<br>0748<br>0607<br>0798<br>0759<br>0609                                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and High Energy Fluid and Plasma Molecular Nuclear                                                          | 0986<br>0608<br>0748<br>0607<br>0798<br>0759<br>0609                                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and High Energy Fluid and Plasma Molecular Nuclear Optics                                                   | 0986<br>0606<br>0608<br>0748<br>0607<br>0798<br>0759<br>0609<br>0610                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and High Energy Fluid and Plasma Molecular Nuclear Optics Radiation                                         | 0986<br>0606<br>0608<br>0748<br>0607<br>0759<br>0609<br>0610<br>0752                 |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and High Energy Fluid and Plasma Molecular Nuclear Optics Radiation Solid State                             | 0986<br>0606<br>0608<br>0748<br>0607<br>0759<br>0609<br>0610<br>0752<br>0756         |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and High Energy Fluid and Plasma Molecular Nuclear Optics Radiation Solid State Statistics                  | 0986<br>0606<br>0608<br>0748<br>0607<br>0759<br>0609<br>0610<br>0752<br>0756         |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and High Energy Fluid and Plasma Molecular Nuclear Optics Radiation Solid State Statistics Applied Sciences | 0986<br>0606<br>0608<br>0748<br>0607<br>0759<br>0609<br>0752<br>0756<br>0611<br>0463 |

| Acoustics Astronomy and Astrophysics Atmospheric Science Atomic Electronics and Electricity Elementary Particles and High Energy Fluid and Plasma Molecular Nuclear Optics Radiation Solid State Statistics                  | 0986<br>0606<br>0608<br>0748<br>0607<br>0759<br>0609<br>0752<br>0756<br>0611<br>0463 |

| Engineering General Aerospace Agricultural Automotive Biomedical                                                                   | 0538<br>0539<br>0540         |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Chemical Civil Electronics and Electrical Heat and Thermodynamics Hydraulic Industrial                                             | 0543<br>0544<br>0348<br>0545 |

| Marine Materials Science Mechanical Metallurgy Mining Nuclear                                                                      | 0794<br>0548<br>0743<br>0551 |

| Packaging Petroleum Sanitary and Municipal System Science Geotechnology Operations Research Plastics Technology Textile Technology | 0765<br>0554                 |

| Textile Technology PSYCHOLOGY                                                                                                      | 0994                         |

| General Behavioral Clinical Developmental Experimental Industrial Personality Physiological Psychobiology                          | 0384<br>0622<br>0620<br>0623 |

## HIGH SPEED SEQUENTIAL DEMODULATOR BASED ON SHIFT REGISTER SYSTOLIC PRIORITY QUEUE ARCHITECTURE

BY

#### HOO MAN NG

A Thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

© 1993

Permission has been granted to the LIBRARY OF THE UNIVERSITY OF MANITOBA to lend or sell copies of this thesis, to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publications rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's permission.

## **ABSTRACT**

The sequential algorithm has been applied to channels with intersymbol interference (ISI). It is superior to the Viterbi algorithm for channels with long or even infinite intersymbol interference, since the computation and storage complexity of the sequential algorithm does not grow exponentially with the length of the channel memory. However the time required for the complete stack reordering procedure in the conventional sequential stack algorithm is long and depends on the number of entries in the stack, hence places severe limitations on the decoding speed and thus the real—time implementation of the algorithm.

In this thesis, the Shift Register Systolic Priority Queue is used to substitute the stack of the conventional sequential stack algorithm to eliminate the complete stack reordering problem. With the systolic priority queue architecture, complete stack reordering is no longer required and the path with the largest path metric is guaranteed to appear at the top of the stack within a fixed and short interval of time regardless of the number of paths in the stack.

Hardware algorithms for storing the explored paths and evaluating the metrics are developed in this thesis. A sequential demodulator based on the Shift Register Systolic Priority Queue architecture and the developed algorithms was implemented. The design is capable of handling input blocks of 256 bits and a maximum of 9 interference terms. It has a maximum allowable stack size of 1024. An 8-bit representation is used for the sufficient statistic  $z_k$  and a 16-bit representation for the metric.

## **ACKNOWLEDGEMENTS**

The author wishes to express his sincere thanks to Professor E. Shwedyk for his supervision and guidance throughout the course of the research.

I hereby declare that I am the sole author of this thesis. I authorize the University of Manitoba to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Hoo Man Ng

I further authorize the University of Manitoba to reproduce this thesis by photocopying or by other means, in whole or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Hoo Man Ng

## **Table of Contents**

| Chap  | oter 1 Introduction                                                       | 1    |

|-------|---------------------------------------------------------------------------|------|

| Chap  | oter 2 Background and Theory                                              | 5    |

| 2.1   | Channel Model and Receiver Structure for Intersymbol Interference (ISI) . | 5    |

| 2.2   | Viterbi Algorithm (VA)                                                    | 14   |

| 2.3   | Sequential Algorithm (SA)                                                 | 16   |

| 2.3.1 | Stack Algorithm                                                           | 18   |

| 2.3.2 | Problems with the Practical Implementation of Stack Algorithm             | 21   |

| 2.4   | Systolic Priority Queue                                                   | 23   |

| 2.4.1 | Random Access Memory (RAM) Systolic Priority Queue                        | 24   |

| 2.4.2 | Shift Register (SR) Systolic Priority Queue                               | 35   |

| 2.4.3 | Concluding Remarks on Systolic Priority Queues                            | 50   |

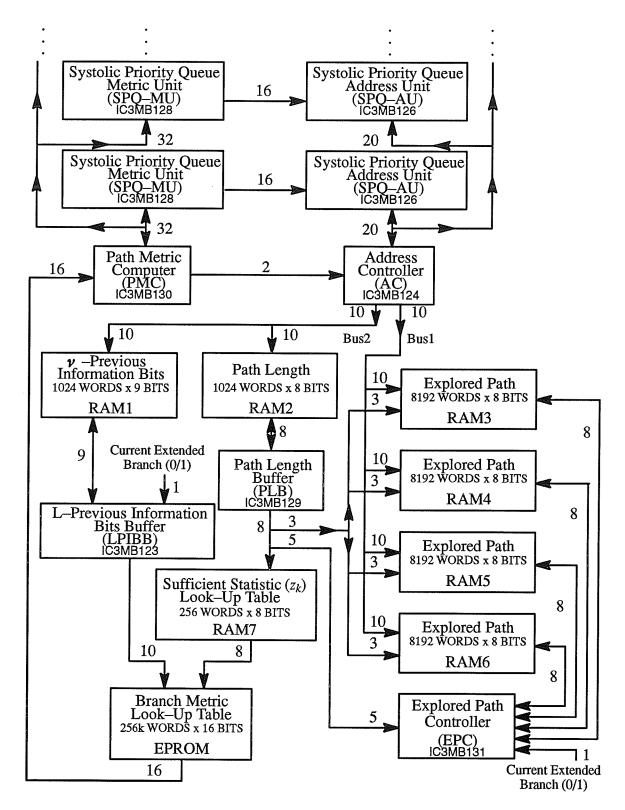

| Chap  | oter 3 Design of the Sequential Demodulator                               | 51   |

| 3.1   | General Description of the Sequential Demodulator                         | 51   |

| 3.2   | Storage Configuration                                                     | 52   |

| 3.3   | Operation of the Sequential Demodulator                                   | 56   |

| 3.3.1 | Duplication of data in RAM1, RAM2 and RAM3–6                              | 56   |

| 3.3.2 | Path extension                                                            | 58   |

| 3.4   | Hardware Design                                                           | 63   |

| 3.4.1 | Systolic Priority Queue-Metric Unit (SPQ-MU) and Systolic Priority        | rity |

| Queue | -Address Unit (SPQ-AU)                                                    | 63   |

| 3.4.2 | Path Metric Computer (PMC)                           | 73 |

|-------|------------------------------------------------------|----|

| 3.4.3 | Address Controller (AC)                              | 74 |

| 3.4.4 | L-Previous Information Bits Buffer (LPIBB)           | 75 |

| 3.4.5 | Path Length Buffer (PLB)                             | 76 |

| 3.4.6 | Explored Path Controller (EPC)                       | 77 |

| Chap  | oter 4 Test Result and Discussion                    | 78 |

| 4.1   | Test Result                                          | 78 |

| 4.2   | Applicability of the Sequential Demodulator          | 81 |

| 4.2.1 | Number of interference terms in the ISI channel      | 81 |

| 4.2.2 | Length of input to the ISI channel                   | 81 |

| 4.2.3 | Stack overflow problem                               | 82 |

| Chap  | oter 5 Conclusions and Suggestions for Further Study | 83 |

| 5.1   | Conclusions                                          | 83 |

| 5.2   | Suggestions for Further Study                        | 84 |

| REF   | ERENCES                                              | 85 |

Š

## **List of Figures**

| 2.1  | PAM communication system                                                              |

|------|---------------------------------------------------------------------------------------|

| 2.2  | Maximum-likelihood sequence estimator                                                 |

| 2.3  | Whitened matched filter $w(-t)$                                                       |

| 2.4  | Finite-state machine model                                                            |

| 2.5  | Equivalent channel model of the finite-state machine model                            |

| 2.6  | A four–state trellis                                                                  |

| 2.7  | Code tree of a finite state machine model for an ISI channel with binary inputs and a |

|      | channel memory of $\nu = 2$                                                           |

| 2.8  | Flowchart of the conventional sequential stack algorithm                              |

| 2.9  | Basic structure of linear systolic priority queue                                     |

| 2.10 | Building unit of the Random Access Memory Systolic Priority Queue 24                  |

| 2.11 | Flowchart of the insertion of a succeeding path metric in Random Access Memory        |

|      | Systolic Priority Queue                                                               |

| 2.12 | Example of the insertion operation in the Random Access Memory Systolic Priority      |

|      | Queue                                                                                 |

| 2.13 | Flowchart of the deletion of the largest path metric in Random Access Memory          |

|      | Systolic Priority Queue                                                               |

| 2.14 | Example of the deletion operation in the Random Access Memory Systolic Priority       |

|      | Queue                                                                                 |

| 2.15 | Flowchart of the RAM scheme stack algorithm for a channel with binary                 |

|      | inputs                                                                                |

| 2.16 | Example of a code tree for an ISI channel with binary inputs                          |

| 2.17 | Array contents of the stack decoding of the ISI tree shown in figure 2.16 with Rando   | m   |

|------|----------------------------------------------------------------------------------------|-----|

|      | Access Memory Systolic Priority Queue.                                                 | 34  |

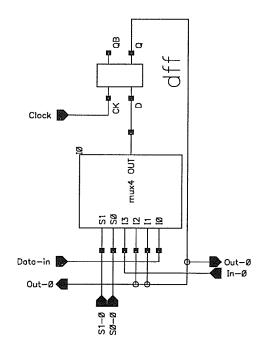

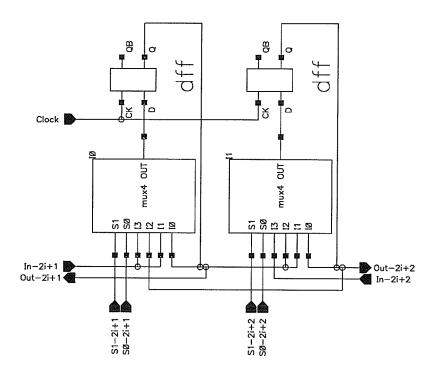

| 2.18 | Building units of the Shift Register Systolic Priority Queue                           | 35  |

| 2.19 | Flowchart of the insertion of a succeeding path metric in Shift Register Systo         | lic |

|      | Priority Queue.                                                                        | 37  |

| 2.20 | Example of the insertion operation in the Shift Register Systolic Priority Queue.      | 38  |

| 2.21 | Flowchart of the deletion operation of the largest path metric in Shift Register Systo | lic |

|      | Priority Queue.                                                                        | 40  |

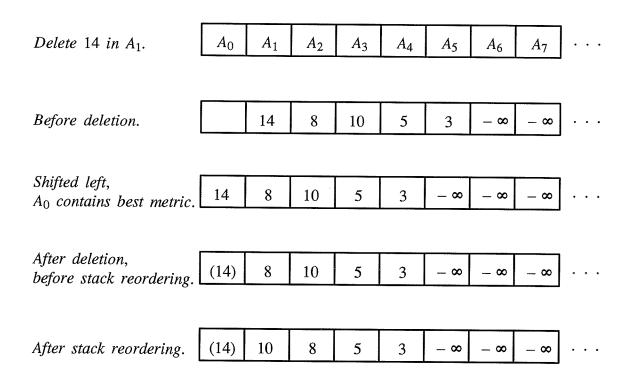

| 2.22 | Example of the deletion operation in the Shift Register Systolic Priority Queue.       | 41  |

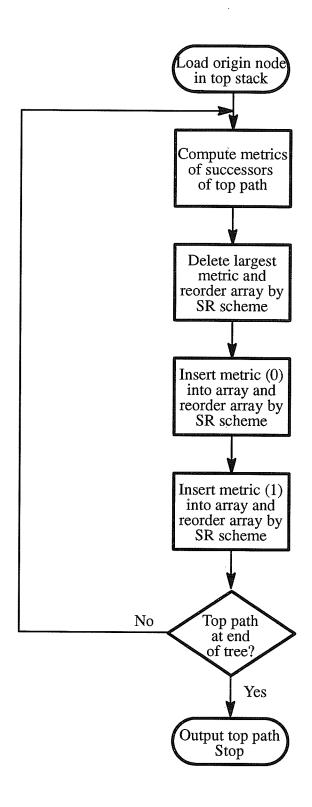

| 2.23 | Flowchart of the SR scheme stack algorithm for a channel with binary inputs.           | 43  |

| 2.24 | Array contents of the stack decoding of the ISI tree shown in figure 2.16 with Sh      | ift |

|      | Register Systolic Priority Queue.                                                      | 44  |

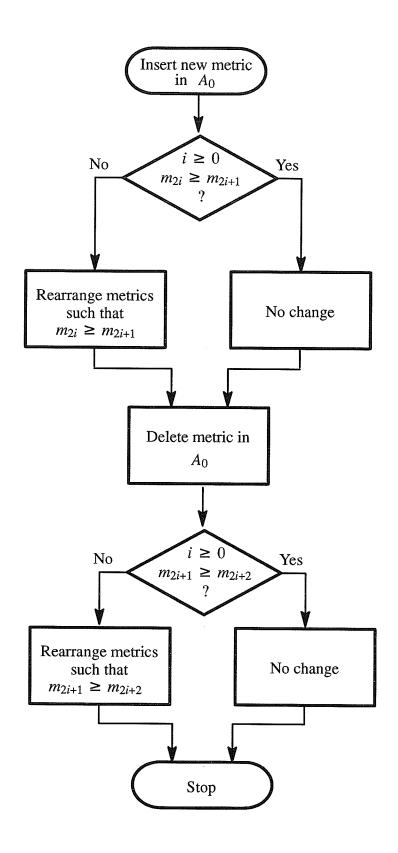

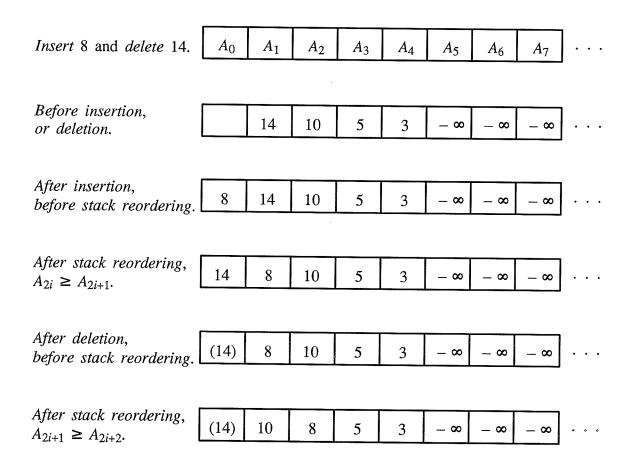

| 2.25 | Flowchart of simultaneous insertion of a succeeding path metric and deletion of t      | he  |

|      | largest path metric in SR Systolic Priority Queue.                                     | 46  |

| 2.26 | Example of the simultaneous insertion and deletion operations in Shift Regist          | er  |

|      | Systolic Priority Queue.                                                               | 47  |

| 2.27 | Flowchart of the modified version of the SR scheme stack algorithm for a channel wi    | .th |

|      | binary inputs                                                                          | 49  |

| 5.1  | block diagram of the sequential demodulator based on a systolic priority queue         |

|------|----------------------------------------------------------------------------------------|

|      | architecture                                                                           |

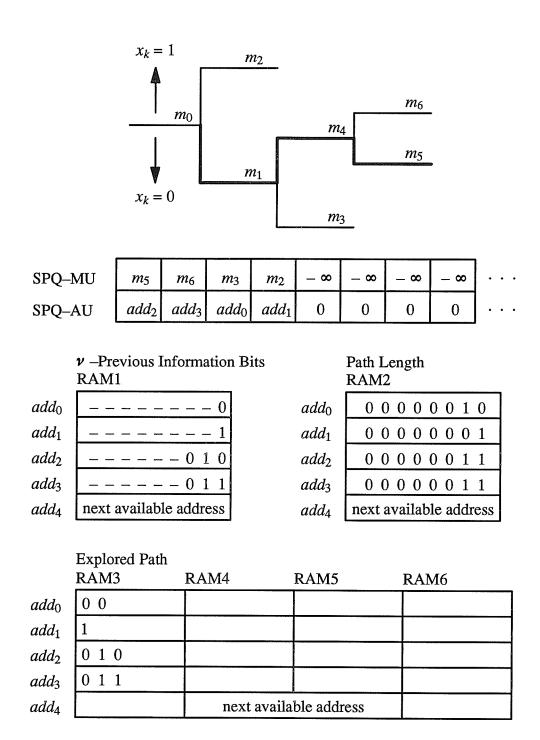

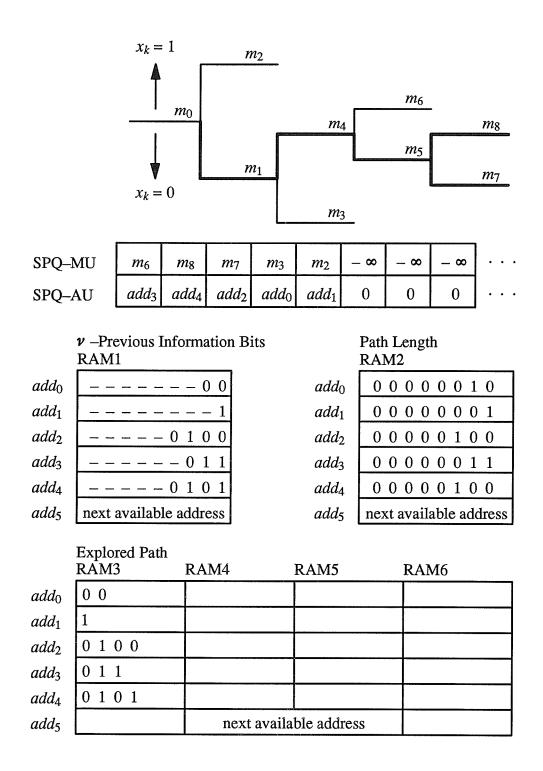

| 3.2  | The relation of a sample code tree with the systolic priority queue contents and the   |

|      | stack contents                                                                         |

| 3.3  | Explored path storage configuration                                                    |

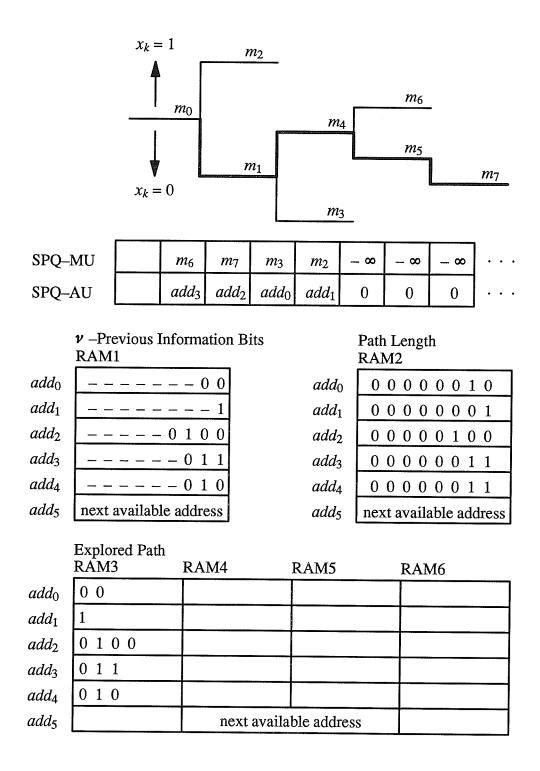

| 3.4  | The relation of a sample code tree with the systolic priority queue contents and the   |

|      | stack contents after extending branch (0) of the explored path (010) 61                |

| 3.5  | The relation of a sample code tree with the systolic priority queue contents and the   |

|      | stack contents after extending branch (0) and branch (1) of the explored path          |

|      | (010)                                                                                  |

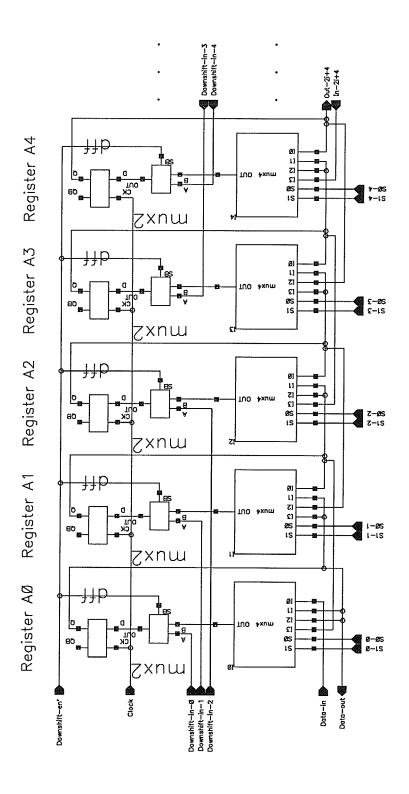

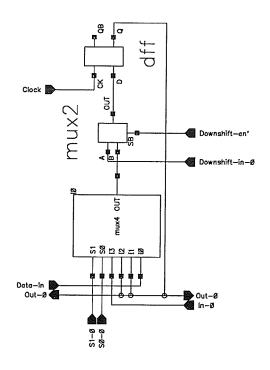

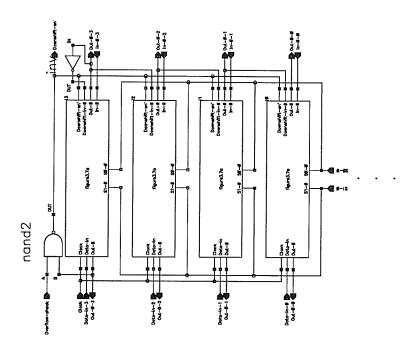

| 3.6  | Basic structure of the SR Systolic Priority Queue for the stack algorithm 64           |

| 3.7  | Basic building units of the SR Systolic Priority Queue for the stack algorithm. 66     |

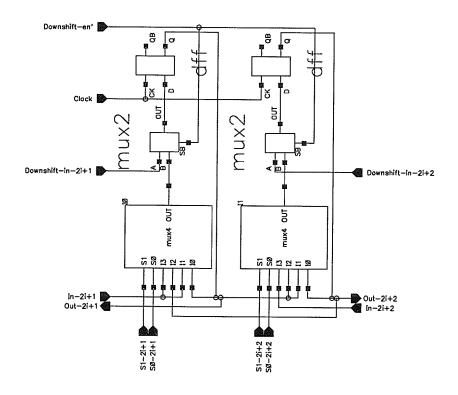

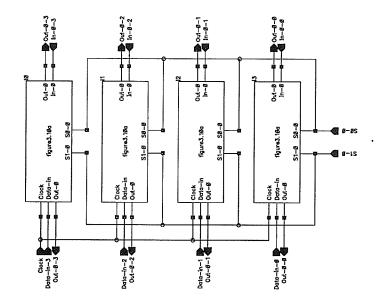

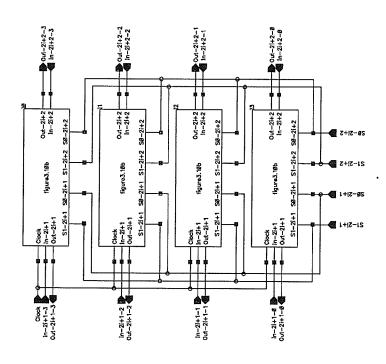

| 3.8  | Paralleling the building units of the SR Systolic Priority Queue for the stack         |

|      | algorithm                                                                              |

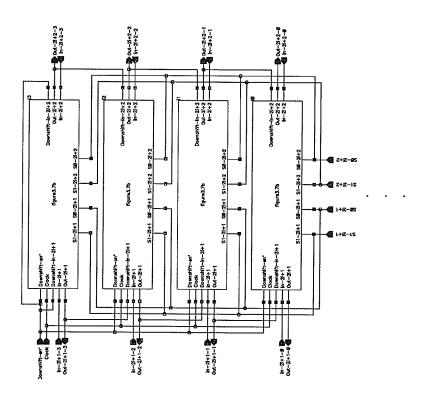

| 3.9  | M-bit registers of the SR Systolic Priority Queue for the stack algorithm with         |

|      | comparator and selector added                                                          |

| 3.10 | Basic building units of the address SR Systolic Priority Queue for the stack           |

|      | algorithm                                                                              |

| 3.11 | Paralleling the building units of the address SR Systolic Priority Queue for the stack |

|      | algorithm                                                                              |

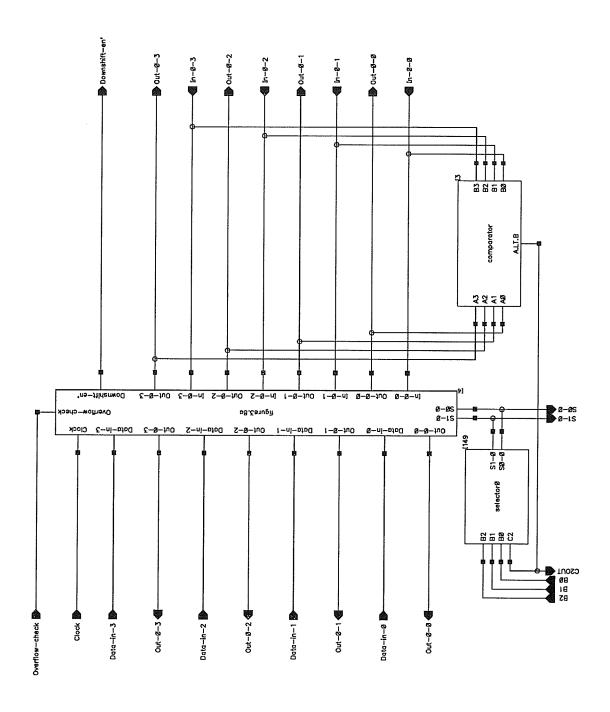

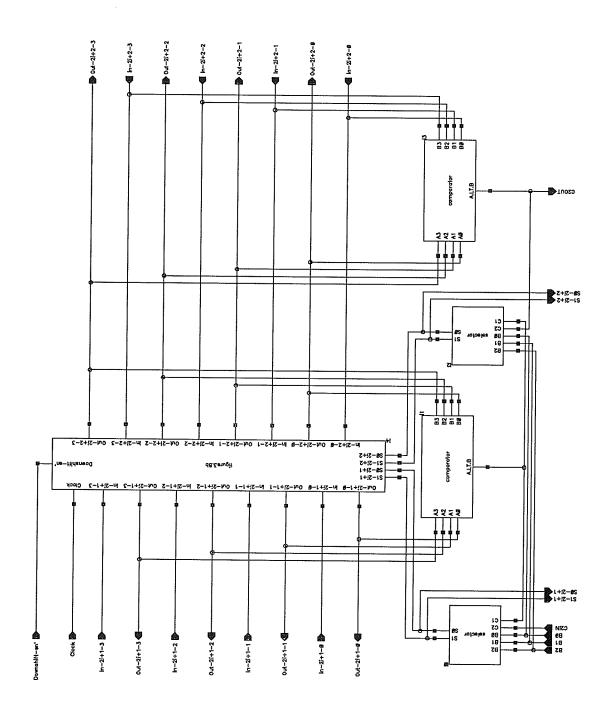

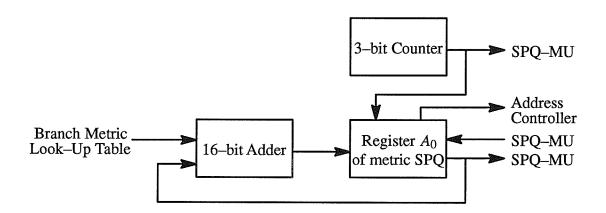

| 3.12 | Block diagram of the Path Metric Computer                                              |

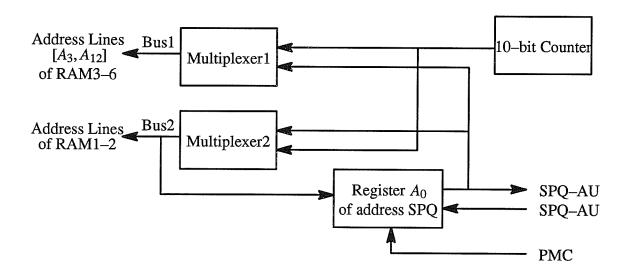

| 3.13 | Block diagram of the Address Controller                                                |

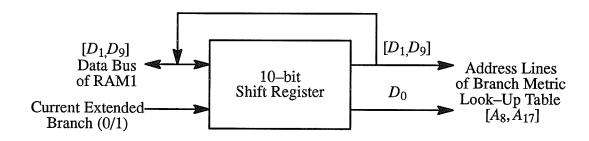

| 3.14 | Block diagram of the L-Previous Information Bits Buffer 75                             |

| 3.15 | Block diagram of the Path Length Buffer                                                |

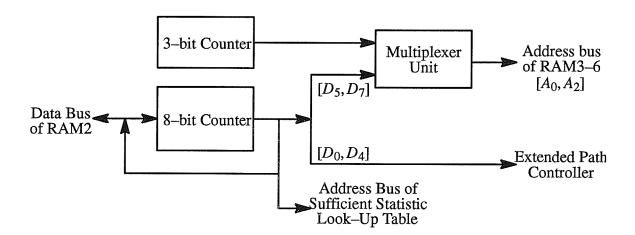

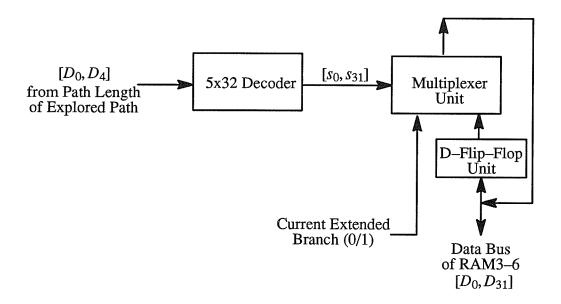

| 3.16 Block diagram of the Explored Path Controller. |  |  |  |  |  |  |  |  |  |  |  |  | 7 | 77 |

|-----------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|---|----|

|-----------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|---|----|

## **List of Tables**

| 3.1 | Truth table for the register | $A_0$ | and register | $A_i$ | in figure 3.6. |   |   |   |   |   |   |   | 61 |

|-----|------------------------------|-------|--------------|-------|----------------|---|---|---|---|---|---|---|----|

|     |                              | ~ ~ U |              |       |                | • | • | • | • | • | • | • |    |

## **Chapter 1** Introduction

The increasing demand for higher rate digital data transmission makes digital communication an area of intensive research. Due to physical constraints, communication channels are bandlimited. One example is the voice—grade—telephone channel that has a bandwidth of approximately 4,000 Hz despite the fact that modems are transmitting data over this channel at a rate of approximately 24,000 bits/sec. The bandlimited characteristic results in intersymbol interference (ISI) [4], a phenomenon where each transmitted pulse stretches beyond the time interval allocated to that particular pulse and overlaps with pulses in other time intervals. The occurrence of ISI is caused by the time—dispersive characteristics of bandlimited channels. The number of pulses interfering with a particular pulse is called the memory of the channel ( $\nu$ ) or the length of the ISI. In high speed data transmission over bandlimited channels with high signal—to—noise (SNR) ratios, the existence of ISI becomes the major obstacle to reliable communication.

Various techniques for combating ISI have been studied. In 1928, Nyquist [19], being the first researcher to develop techniques for combating ISI, introduced baseband spectrum shaping for zero ISI. This eliminates ISI by using an equivalent filter at the receiver to suppress the ISI terms at any sampling instant. In 1963, Lender [15] introduced the duobinary signaling technique which allows the existence of one ISI term. Lender's technique allows ISI in a controlled manner so that it can be removed at the receiver. In 1966, Lender [16] and Kretzmer [12, 13] generalized the duobinary signaling technique to partial response or correlative coding which allows any number of ISI terms. During 1968–1969, Tomlinson [24] from the United Kingdom and Harashima [10, 11] from Japan invented the precoding technique [9]. With the assumption that the channel response is known at the transmitter, the input sequence is coded in a unique way before transmission through the channel. Equalization techniques were also introduced for combating ISI during the late 1960's. Channel equalization is performed by the receiver that usually consists of a matched

filter followed by a sampler and an equalizer. There are three main categories of equalization techniques [9, 22], namely linear equalization (LE), decision–feedback equalization (DFE), and maximum—likelihood sequence estimation (MLSE). In linear equalization [18], the present and past outputs of the matched filter are weighted by estimated gains and summed to produce the output. Decision–feedback equalization [2] is the simplest form of non–linear equalization. A decision–feedback equalizer improves upon a linear equalizer by passing the output of a linear equalizer through a second equalizer with feedback. MLSE, a sequence estimation technique, is considered the optimum equalization structure for communication channels with finite ISI and is found to have an error performance superior to the conventional symbol–by–symbol decision receivers mentioned above. In 1972, Forney [7] showed MLSE can be realized for channels with finite ISI. The maximum–likelihood sequence estimator consists of a whitened matched filter followed by a Viterbi processor. The detection task is modelled as a search for the best (maximum–likelihood) path through a regular structure called a trellis.

The Viterbi Algorithm [8, 17] was invented by Viterbi in 1967 as a method for decoding convolutional codes. Since the ISI channel characteristic is equivalent to that of the convolutional encoder, Forney [7] applied the VA to ISI channels. During the decoding process, the VA visits all the paths through the trellis in order to find the maximum–likelihood path. The fixed number of computations and the regular decoding procedure make the Viterbi processor very easy to implement. However, the computational complexity and the storage complexity of the VA grow exponentially with the length of the channel memory. For ISI channels with large or infinite memory, implementation of the maximum–likelihood sequence estimator using VA becomes impractical.

In order to reduce the computational complexity of the VA, a great deal of effort has been made to reduce the number of states in the trellis to which the VA is applied. The techniques used for reducing the number of trellis states are known as RSVA (Reduced–State Viterbi Algorithm) [1, 5, 6, 14, 20, 21, 23, 25]. These techniques reduce the number of trellis states

either by reducing the number of the most likely paths to be searched or the length of the channel memory. The RSVA techniques have the advantage of retaining the structure of MLSE-VA while reducing the computational complexity of MLSE-VA. However, for any specific technique, gains in computational complexity comes with a loss in detection performance.

In 1989, Xiong [26] developed the application of the sequential algorithm (SA) [17] to ISI channels. The sequential algorithm is another technique for decoding convolutional codes. Since the ISI channel characteristic is equivalent to that of the convolutional encoder, Xiong applied the SA to ISI channels. Unlike the VA, the SA visits only a small number of paths through the tree. The computational complexity of the SA is almost independent of the length of the channel memory and its detection performance is essentially maximum—likelihood. This property makes the SA applicable to ISI channels with large or even infinite memory. Compared to the VA for ISI channels, the sequential approach is able to handle more severe ISI channels (large or infinite memory) and therefore allows data to be transmitted at higher rates.

Although the sequential approach is superior to the Viterbi approach in its ability to handle a greater number of interference terms, it involves a very time consuming stack reordering. Not only is the time required for stack reordering long, but it also varies with the number of paths in the stack. It is undesirable for the operation time to be dependent upon the number of paths in the stack since this number increases after each decoding step. Since the only purpose of stack reordering is to have the best path placed at the top of the stack for the next decoding step. Chang and Yao [3] proposed the use of a Systolic Priority Queue. With the systolic priority queue architecture complete stack reordering is not necessary and the best path is always placed within a fixed and short period of time at the top of the stack for the next decoding step.

The objective of this thesis is to examine the VLSI implementation of a sequential demodulator based on the systolic priority queue architecture applicable to ISI channels. Chapter 2 provides a general background of the ISI channels, followed by a description of the Viterbi algorithm, sequential algorithm and Systolic Priority Queue. Chapter 3 describes the details in the development of the sequential demodulator. Chapter 4 presents the testing result and the discussion of the design. Chapter 5 gives the conclusions and suggestions for further study.

## Chapter 2 Background and Theory

## 2.1 Channel Model and Receiver Structure for Intersymbol Interference (ISI)

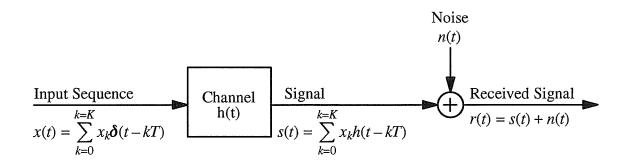

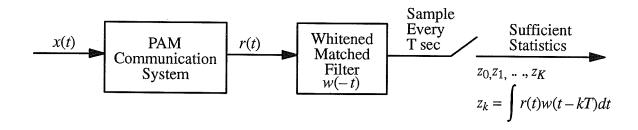

Intersymbol interference (ISI) arises in all pulse—modulation systems whenever the impulse response of the channel is longer than one transmission time period (T). Pulse amplitude modulation (PAM) system is the simplest digital communication system that can be used to illustrate ISI. Figure 2.1 shows a simplified version of the baseband PAM communication system. The input data x(t) is modeled as a train of impulses equally spaced at T—seconds intervals with specific weights  $x_k$ , where  $x_k$  are drawn from a discrete finite alphabet  $\{0,1,\ldots,m-1\}$ .

$$x(t) = \sum_{k=0}^{k=K} x_k \delta(t - kT) , \qquad (2.1)$$

K may be finite or infinite. h(t) is the finite impulse response of the channel with a length of L symbol intervals, i.e. L is the smallest integer such that h(t) = 0 for  $t \ge LT$ . The impulse response h(t) is assumed to be square—integrable,

$$\|h\|^2 \stackrel{\Delta}{=} \int_{-\infty}^{\infty} h^2(t)dt < \infty . \tag{2.2}$$

If h(t) has nonzero values at sampling instants  $t = t_0 \pm kT$  for k = 1, 2, ..., K, then ISI occurs. The number of nonzero sampling values in h(t) (except at  $t = t_0$ ) is called the length of ISI or the channel memory (v), where v = L - 1. The output of the channel impulse response, which is the convolution sum of x(t) and h(t), is denoted as s(t).

Figure 2.1: PAM communication system.

Figure 2.2: Maximum-likelihood sequence estimator.

$$s(t) = x(t) * h(t) ,$$

$$= \sum_{k=0}^{k=K} x_k h(t - kT) .$$

(2.3)

The output signal s(t) is corrupted by additive white Gaussian noise n(t) to yield the received signal r(t).

$$r(t) = s(t) + n(t) ,$$

$$= \sum_{k=0}^{k=K} x_k h(t - kT) + n(t) .$$

(2.4)

r(t) is the received signal corrupted by white Gaussian noise and intersymbol interference. If r(t) is sampled at t = jT, where  $t_0$  accounts for the channel delay and sampler phase, then

$$r(t_0 + jT) = x_j h(t_0) + \sum_{k \neq j} x_k h(t_0 + jT - kT) + n(t_0 + jT) .$$

Desired Output ISI Noise (2.5)

The output is corrupted by ISI unless h(t) is zero at all sampling instants except at  $t=t_0$ . The first term on the right side is the desired output produced by the input symbol at t=jT, the second term is the intersymbol interference and the last term is the additive white Gaussian noise. The presence of ISI is the primary impediment to reliable high–rate digital data transmission over high signal—to—noise ratio bandlimited channels such as voice—grade telephone circuits.

In 1972, Forney [7] developed a receiver structure for the maximum—likelihood estimation of digital sequences in the presence of ISI. The receiver consists of a whitened matched filter, a symbol—rate sampler and a Viterbi processor as shown in Figure 2.2. The sampled

outputs of the whitened matched filter form a set of sufficient statistics  $\{z_k\}$  for the estimation of the input sequence  $\{x_k\}$ .

Equation (2.3) shows that s(t) can be expressed as a linear combination of a set of square—integrable basis functions h(t-kT). In the detection of signals that are a linear combinations of a set of square—integrable basis functions, the outputs of a bank of matched filters, each matched to a basis function, form a set of sufficient statistics for estimating the input sequence. Thus the K+1 quantities

$$a_k \stackrel{\Delta}{=} \int_{-\infty}^{\infty} r(t)h(t - kT)dt , \qquad 0 \le k \le K$$

(2.6)

form a set of sufficient statistics for the estimation of the input sequence  $\{x_k\}$ ,  $0 \le k \le K$ , where K may be finite or infinite. But  $a_k$  are just the convolution integral of r(t) and h(-t), i.e.  $a_k$  are the sampled outputs of a filter h(-t) matched to the channel impulse response h(t).

By applying the D-transform to the matched-filter output sequence  $a_k$ , equation (2.6) can be defined as

$$a(D) \stackrel{\Delta}{=} \sum_{k=0}^{k=K} a_k D^k . \tag{2.7}$$

Since

$$a_k \stackrel{\Delta}{=} \int_{-\infty}^{\infty} r(t)h(t - kT)dt$$

$$= \int_{-\infty}^{\infty} \sum_{j=0}^{K} x_j h(t - jT)h(t - kT)dt + \int_{-\infty}^{\infty} n(t)h(t - kT)dt$$

$$= \sum_{j=0}^{K} x_j \int_{-\infty}^{\infty} h(t - jT)h(t - kT)dt + \int_{-\infty}^{\infty} n(t)h(t - kT)dt$$

$$= \sum_{j=0}^{K} x_j R_{k-j} + n_k' , \qquad (2.8)$$

the D-transform of  $a_k$  can be expressed as

$$a(D) = x(D)R(D) + n'(D)$$

(2.9)

In equation (2.8),

$$R_{k-j} \stackrel{\Delta}{=} \begin{cases} \int_{-\infty}^{\infty} h(t-jT)h(t-kT)dt & |k-j| \leq \nu \\ 0 & |k-j| \geq \nu + 1 \end{cases}$$

(2.10)

are the pulse autocorrelation coefficients of h(t). It follows that

$$R(D) \stackrel{\Delta}{=} \sum_{k=-\nu}^{k=\nu} R_k D^k \tag{2.11}$$

is the D-transform of the pulse autocorrelation function or the spectral function of h(t). Since R(D) is finite with  $2\nu+1$  nonzero terms, it has  $2\nu$  complex roots. Furthermore, since  $R(D)=R(D^{-1})$ , the inverse  $\boldsymbol{\beta}^{-1}$  of any root  $\boldsymbol{\beta}$  is also a root of R(D). Thus, the  $2\nu$  complex roots of R(D) may be grouped into  $\boldsymbol{\nu}$  inverse pairs. If f'(D) is any polynomial of degree  $\boldsymbol{\nu}$  whose roots consist of one root from each of the  $\boldsymbol{\nu}$  inverse pairs of R(D), then R(D) has the spectral factorization

$$R(D) = f'(D)f'(D^{-1})$$

(2.12)

By letting  $f(D) = D^n f'(D)$  for any integer delay n, equation (2.12) can further be generalized to

$$R(D) = f(D)f(D^{-1})$$

(2.13)

n'(D) in equation (2.9) is the zero-mean colored Gaussian noise with autocorrelation function  $\sigma^2 R(D)$ , since

$$E\{n_{k}'n_{j}'\} = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} E\{n(t)n(\tau)\}h(t-kT)h(\tau-jT)dtd\tau$$

$$= \sigma^{2}R_{k-j} \tag{2.14}$$

where  $\sigma^2$  is the spectral density of the white noise n(t) and  $E\{n(t)n(\tau)\} = \sigma^2\delta(t-\tau)$ .

If n(D) is the zero-mean white Gaussian noise with autocorrelation function  $\sigma^2$ , then the colored Gaussian noise n'(D) can be expressed as

$$n'(D) = n(D)f(D^{-1})$$

(2.15)

since n'(D) has the autocorrelation function  $\sigma^2 f(D^{-1}) f(D) = \sigma^2 R(D)$ . The autocorrelation function entirely specifies the zero-mean Gaussian noise.

By combining equations (2.9), (2.13) and (2.15), the D-transform of the output sequence of the matched-filter h(-t) can be expressed as

$$a(D) = x(D)f(D)f(D^{-1}) + n(D)f(D^{-1}) . (2.16)$$

If

$$z(D) \stackrel{\Delta}{=} \frac{a(D)}{f(D^{-1)}}$$

, (2.17)

then

$$z(D) = x(D)f(D) + n(D)$$

(2.18)

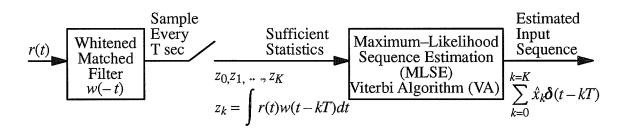

where n(D) is the zero-mean white Gaussian noise and z(D) is defined as the D-transform of the sampled output sequence  $\{z_k\}$  of the cascade of a matched filter h(-t) with a transversal filter  $1/f(D^{-1})$  as shown in figure 2.3. The cascade in figure 2.3 is called a whitened matched filter w(-t) since the noise component n(D) of the output sequence is whitened with a constant spectral density of  $\sigma^2$ .

Figure 2.3: Whitened matched filter w(-t).

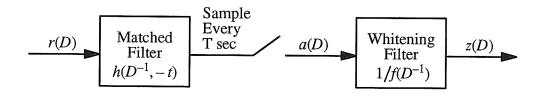

Figure 2.4: Finite-state machine model.

Figure 2.5: Equivalent channel model of the finite-state machine model.

More generally, for any spectral factorization of the form  $R(D) = f(D)f(D^{-1})$ , the filter w(t) with a chip D-transform

$$w(D,t) \stackrel{\Delta}{=} \frac{1}{f(D)} h(D,t) \tag{2.19}$$

is well defined and its time reversal w(-t) can be used as a whitened matched filter. Hence the sampled outputs  $z_k$  of w(-t)

$$z_k \stackrel{\Delta}{=} \int_{-\infty}^{\infty} r(t)w(t - kT)dt \tag{2.20}$$

satisfy equation (2.18) and thus form a set of sufficient statistics for the maximum-likelihood estimation of the input sequence  $\{x_k\}$  in the presence of ISI and zero mean white Gaussian noise.

However for an arbitrary spectral factorization of R(D), the causality of the whitening filter  $1/f(D^{-1})$  is not guaranteed. To actually realize w(-t), the factorization of R(D) has to be such that the whitening filter  $1/f(D^{-1})$  is stable and causal, and preferably real.

In equation (2.18), the signal sequence

$$y(D) \stackrel{\Delta}{=} x(D)f(D) \tag{2.21}$$

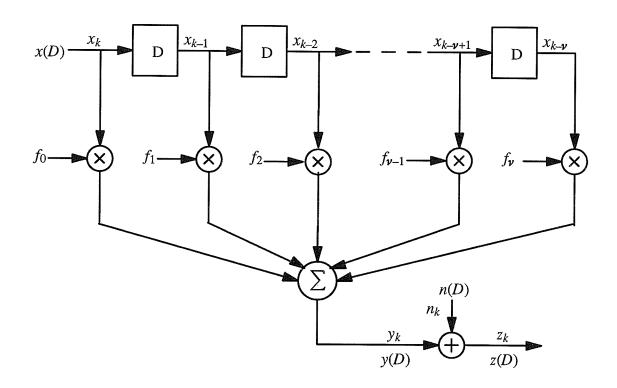

is the convolution of the input sequence x(D) with the finite channel impulse response f(D), and the received sequence z(D) is the sum of the signal sequence y(D) and a white Gaussian noise sequence n(D). Thus, the relationship in equation (2.18) can be modeled as a finite-state machine (FSM) as shown in figure 2.4. An equivalent communication channel model is depicted in figure 2.5. The finite-state machine may be imagined as having a shift register of  $\boldsymbol{v}$  memory elements that store the  $\boldsymbol{v}$  most recent inputs  $x_{k-i}$ ,  $1 \le i \le \boldsymbol{v}$ . The

signal  $y_k$  may be taken as the weighted sum of the  $\nu$  most recent inputs and the weighted current input  $x_k$ .

In the time domain the outputs of the finite-state machine can be expressed as

$$z_k = y_k + n_k \tag{2.22}$$

where  $n_k$  is a zero mean white Gaussian noise with spectral density  $\sigma^2$ , and

$$y_k \stackrel{\Delta}{=} \sum_{i=0}^{i=\nu} f_i x_{k-i} , \qquad (2.23)$$

where  $f_i$ ,  $i = 0, 1, ..., \nu$  are the coefficients of f(D). Note that equation (2.23) reflects the effect of ISI on the output signal.

The  $n_k$  are statistically independent zero mean Gaussian random variable with variance  $\sigma^2$ . Consequently, for a given input sequence  $\{x_k\}$ ,  $z_k$  is (conditionally) statistically independent Gaussian random variable with mean  $y_k$  and variance  $\sigma^2$  since  $z_k$  is a linear combination of  $y_k$  and  $n_k$ .

Based on the FSM model and the statistical properties of  $x_k$ ,  $y_k$ , and  $z_k$ , Forney [7] introduced the application of the Viterbi algorithm to produce the maximum-likelihood estimate of the input sequence  $\{x_k\}$  in the presence of ISI.

## 2.2 Viterbi Algorithm (VA)

The Viterbi algorithm [8, 17] was first introduced as a decoding method for convolutional codes. It is equivalent to a dynamic programming solution to the problem of finding the shortest path through a weighted graph. The Viterbi algorithm searches through a structure called trellis for the code word that gives the largest value of a log—likelihood function called path metric. The output of the Viterbi—decoder is always the code word that gives the largest path metric, thus it is in fact a maximum—likelihood decoding algorithm. Since the channel memory in an ISI channel is analogous to the encoder memory in a convolutional code the Viterbi algorithm can be used to produce the maximum—likelihood estimate of the sequence transmitted over an ISI channel.

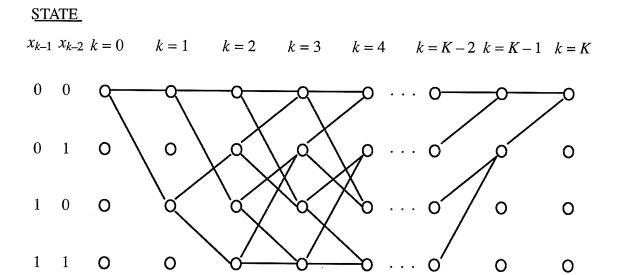

On the basis of the finite-state machine model as depicted in figure 2.4, the one-to-one mapping relationship between the input sequence  $\{x_k\}$  and the signal sequence  $\{y_k\}$  in equation 2.23 can be described by a trellis. A trellis contains information of all the possible state sequences. Each node corresponds to a distinct state at a given time, and each branch represents a state transition at the next instant of time. For any ISI channel, the channel memory  $\nu$  determines the number of states that exist in the trellis. Each possible state sequence in the trellis corresponds to a possible input sequence transmitted over the ISI channel and is represented by a unique path through the trellis. In the general case of a finite ISI channel with  $\nu$  interference terms and m input alphabets, there are  $m^{\nu}$  states in the trellis and m branches entering and leaving each state/node. The trellis of an ISI channel with binary input and a channel memory of  $\nu = 2$  is shown in figure 2.6 as an example.

Associated with each branch is a branch metric which determines the likelihood of the occurrence of the state transition represented by the branch. The accumulation of the branch metrics of a particular path forms the path metric which determines the likelihood of the occurrence of the input sequence represented by the path. At the terminal node of the trellis, the path with the largest path metric is the maximum–likelihood path. Thus, to find the

maximum-likelihood path through the trellis, the Viterbi algorithm has to visit all the possible paths in order to compute and compare the path metrics.

During the decoding process, the Viterbi algorithm computes and compares the metrics of the m paths entering each of the  $m^{\nu}$  states at each decoding step. The path with the largest path metric at each state is called the survivor. The fixed number of computations and the regular decoding procedure make a Viterbi processor very easy to implement. However, the number of states is  $m^{\nu}$  and thus the computational complexity grows exponentially with the length of the channel memory  $\nu$ . For ISI channels with large or infinite memory, the implementation of the maximum-likelihood sequence estimator using the Viterbi approach becomes impractical.

Figure 2.6: A four-state trellis.

## 2.3 Sequential Algorithm (SA)

The sequential algorithm [17] was introduced by Wozencraft as the first practical decoding method for convolutional codes. Fano introduced a new version of sequential decoding, subsequently referred to as the Fano algorithm [17]. Later, Zigangirov and Jelinek discovered independently another version of sequential decoding initially called ZJ algorithm but now commonly known as the stack algorithm [17]. In 1989, Xiong [26] developed the application of the sequential algorithm to the sequence estimation for ISI channels.

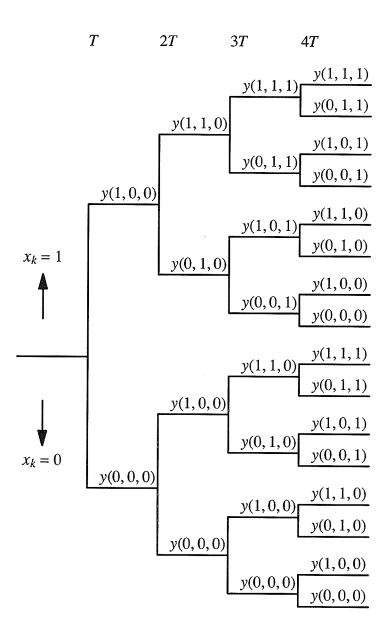

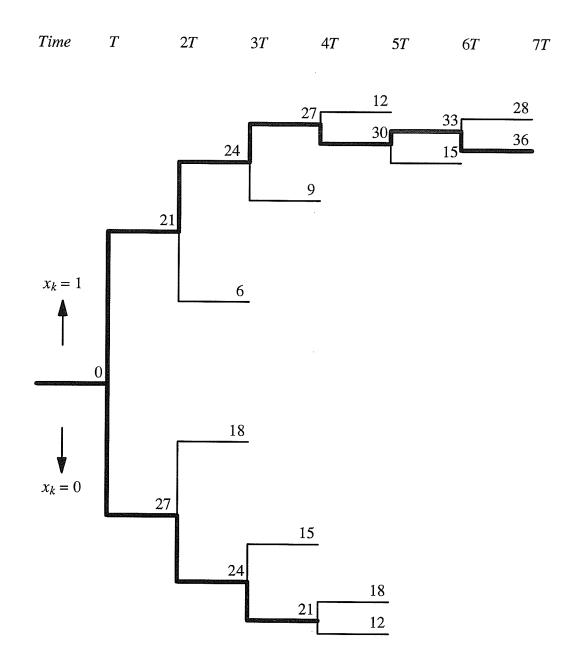

In the sequential decoding, the input and output relationship of the finite—state machine model is represented as paths through a code tree. Figure 2.7 shows an example of a code tree for an ISI channel with binary inputs and a channel memory of v = 2. Each node in the code tree represents a path through part of the tree, and each possible input sequence  $\{x_k\}$  transmitted over the ISI channel is represented by a unique path through the code tree. The purpose of a sequential decoding algorithm is to search through the nodes of the code tree in an efficient way so as to find the maximum—likelihood path. As in the Viterbi algorithm, whether or not a particular path is likely to be part of the maximum—likelihood path depends on the metric value associated with that path.

The most important difference between the Viterbi algorithm and the sequential decoding algorithms is that during the decoding process the Viterbi algorithm examines all the nodes in the trellis while the sequential decoding algorithms examine only a number of the nodes in the code tree. Thus, the computational complexity of the sequential algorithms does not grow exponentially with the channel memory  $\nu$  as for the case of the Viterbi algorithm, but is essentially independent of the channel memory  $\nu$ . This property makes sequential decoding algorithms applicable to ISI channels with large or even infinite memory. The number of nodes visited by the sequential decoding algorithms is determined by the noise level of the ISI channel. Moreover, for a given ISI channel the error probability of sequential

Figure 2.7: Code tree of a finite state machine model for an ISI channel with binary inputs and a channel memory of v = 2. Note:  $y_k = y(x_k, x_{k-1}, x_{k-2})$ .

decoding is essentially the same as for Viterbi decoding.

In this research, only the stack algorithm is considered. A very time consuming step known as the complete stack reordering in the conventional sequential stack algorithm is shown to be not fully needed. The stack reordering procedure of the stack algorithm is then modified so that the stack can be efficiently implemented by a very special type of systolic array called the systolic priority queue as proposed by Chang and Yao [3]. The details of systolic priority queue will be discussed in the next section. The Fano algorithm is not considered in this research since it has an irregular decoding structure which makes the Fano decoder unsuitable for the parallel and pipeline processing characteristics of the systolic array implementation.

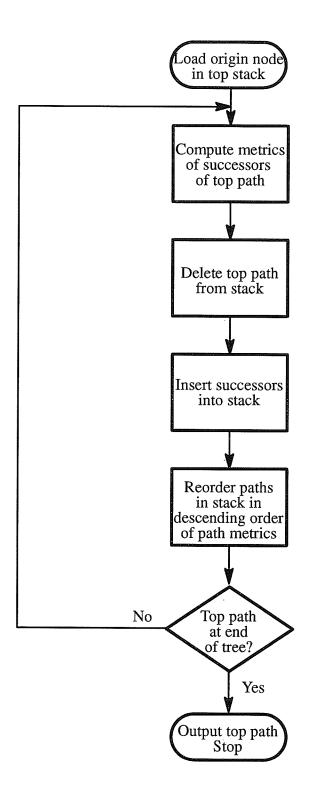

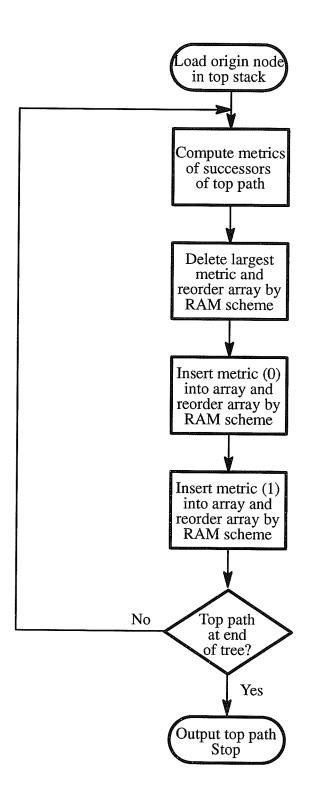

#### 2.3.1 Stack Algorithm

In the stack algorithm, a memory structure called the stack is required to store the previously examined paths of the code tree. Each stack entry holds a path along with its associated metric. The path with the largest metric is placed at the top of stack while the others are placed in a descending order of their associated metrics. The basic idea of the stack algorithm is to move forward along the path with the largest metric until the end of the code tree is reached. Each decoding step consists of extending the path at the top of the stack by computing the branch metrics of its m succeeding branches, and then adding these m branch metrics to the metric of the top path to form the m path metrics for the m successors of the top path. The top path is then deleted from the stack and the m succeeding paths are inserted into the stack. All of the paths in the stack are then rearranged in a descending order of their associated metric values so that the path with the largest metric is at the top of the list. The decoding steps are repeated until the top path reaches the end of the code tree. The top path is then taken as the decoded path and the algorithm terminates. The stack algorithm is summarized as follows.

The stack algorithm:

- Step 1) Load the stack with the origin node in the code tree, whose metric is taken to be zero.

- Step 2) Compute the metric of the m successors of the top path in the stack.

- Step 3) Delete the top path from the stack.

- Step 4) Insert the *m* new paths in the stack, and rearrange the stack in a order of descending metric values.

- Step 5) If the top path in the stack reaches the end of the code tree, stop. Otherwise, return to step 2.

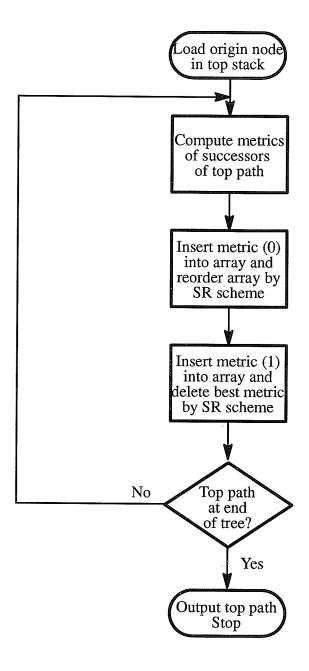

A complete flowchart for the stack algorithm is shown in figure 2.8.

Figure 2.8: Flowchart of the conventional sequential stack algorithm.

## 2.3.2 Problems with the Practical Implementation of Stack Algorithm

There are three practical problems associated with the implementation of the stack algorithm. The first problem is input buffer overflow which results in a loss of data, or an erasure. A sequential stack decoder has to search for the maximum–likelihood path by tracing back and forth from node to node through the code tree, an input buffer must be present to store the incoming received data while they are waiting to be processed. In the case of a very noisy channel, the decoder may have to perform long searches so as to find the current best path without using any received data held in the input buffer. Under such a circumstance, the received data in the input buffer will accumulate which eventually leads to an overflow of the input buffer. When an input buffer overflows, incoming received data will force undecoded received data to be shifted out of the buffer. These bits are then lost which results in an erasure.

The second problem with the stack algorithm is stack overflow. In any practical implementation of the stack algorithm, the number of entries in the stack has to be finite. For a channel with m input alphabets, m paths are inserted into the stack while only one path is deleted from the stack in each decoding step. There is always some probability that the stack will fill up before decoding is completed, especially for the case of a noisy channel. The most common way of handling this problem is to allow the path at the bottom of the stack to be pushed out of the stack on the next decoding step. If the stack size is large enough, the probability that a path at the bottom of the stack would recover to reach the top of the stack and be extended is very small and the loss in performance due to stack overflow is negligible.

The third problem with the stack algorithm is the complete stack reordering of the paths in a descending order of their associated metric values after each decoding step. The complete reordering of the stack is not only time consuming but also dependent upon the number of paths exists in the stack. It is undesirable for the decoding time to be dependent upon the number of paths in the stack since this number increases by m-1 after each decoding step.

The complete stack reordering can become quite time consuming as the number of paths in the stack becomes large, and places severe limitations on the decoding speed that can be achieved with the basic algorithm.

This research concentrates only on solving the complete stack reordering problem of the stack algorithm. The complete stack reordering is not fully required in the stack algorithm. The only purpose of complete stack reordering is to have the current best path placed on the top of the stack so that it is ready to be extended in the next decoding step. To achieve the goal of having the current best path placed on the top entry of the stack, it is not necessary to have all the paths arranged in a descending order. On the basis of the operational characteristics of a special type of systolic array called the systolic priority queue, the stack reordering procedure of the conventional stack algorithm is modified in such a way that the best path is placed on the top entry of the stack without having the rest of the paths arranged in a descending order of their associated metric values. No matter how many paths are in the stack, the systolic array is always able to complete its task within a fixed and short interval of time.

## 2.4 Systolic Priority Queues

As described in the stack algorithm, there is an associated path metric stored with each path in the stack/array. Since the location of a particular path in the array depends on the magnitude of its associated path metric, the operations of the different systolic priority queues are explained in terms of the magnitudes of the path metric  $m_k$ . Thus in the examples illustrated in this section, each entry  $A_i$  in the array is denoted by only a number  $m_k$  representing the path metric of a particular path.

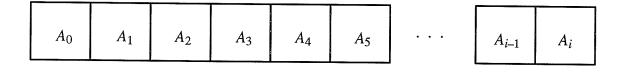

The requirement for the systolic array is that it be able to place the largest metric at the top of the array so that it can be extended in the next decoding step. Extending the largest/best metrics involves the deletion of the current best metric and the insertion of m new succeeding metrics. In particular, the time involved for the above three operations must be fixed, short and independent of the number of metric values in the array and the size of the array. This type of systolic array is known as the systolic priority queue. Two general types of linear systolic priority queues are discussed. They share the linear array structure shown in figure 2.9, where  $A_i$  is a sequence of registers used to store the path metrics  $m_k$ .

Figure 2.9: Basic structure of linear systolic priority queue.

The two types are called the Random Access Memory Systolic Priority Queue and the Shift Register Systolic Priority Queue. The primary difference between them is in the method for rearranging the order of the metrics. By implementing the stack in the stack algorithm with either one of the two linear systolic priority queues named above, the stack reordering can be carried out in parallel rather than sequentially as imposed by the conventional complete stack reordering procedure. Thus, the best path is always placed at the top of the array within a fixed and short interval of time. The Shift Register Systolic Priority Queue is used in this research for the final VLSI implementation of a sequential demodulator.

## 2.4.1 Random Access Memory Systolic Priority Queue (RAM-SPQ)

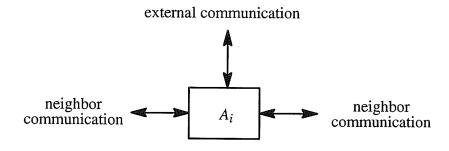

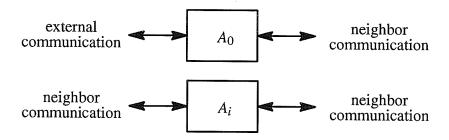

Figure 2.9 shows the basic structure of the RAM-SPQ, where  $A_i$ , i = 0, 1, 2, ..., is a sequence of registers for storing the metric values. Figure 2.10 shows the building unit  $A_i$  of the RAM-SPQ. Each register  $A_i$  can exchange data with its two adjacent neighbors inside the array and an external device as shown in figure 2.10.

Figure 2.10: Building unit of the Random Access Memory Systolic Priority Queue.

In the random access memory scheme, each register is initialized to a path metric value of positive infinity (in practice a large positive number). A global control signal PT which serves as a pointer to locate a particular register in the array is initialized to zero (PT is pointing at register  $A_0$ ).

Insertion and deletion of path metric values in this type of systolic priority queue are very similar to the push and pop operations of a stack. After each insertion or deletion, the path metric values in the queue are rearranged in a unique pairwise manner so as to ensure that the best metric is located at register  $A_{PT-1}$  (analogous to the top of the stack), where  $A_{PT}$  is the next available register. Since the metrics are reordered in pairs of two, reordering of the entire array proceeds in a parallel manner. The insertion operation takes place according to the procedure described below.

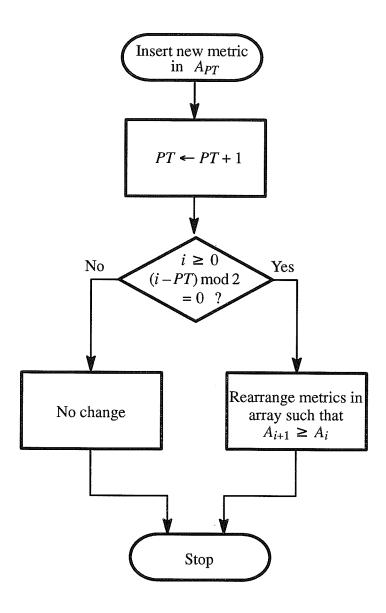

Insertion of a succeeding path metric  $m_k$  in RAM–SPQ:

- 1) Insert the succeeding path metric  $m_k$  into register  $A_{PT}$ ,  $A_{PT} \leftarrow m_k$ .

- 2) Increment PT by one after insertion of  $m_k$ ,  $PT \leftarrow PT + 1$ .

- 3) If i satisfies  $(i-PT) \mod 2 = 0$ , for  $i \ge 0$ , then rearrange the metric values in  $A_i$  and  $A_{i+1}$  such that the metric value in  $A_{i+1}$  is greater than or equal to the metric value in  $A_i$ ,  $A_{i+1} \ge A_i$ .

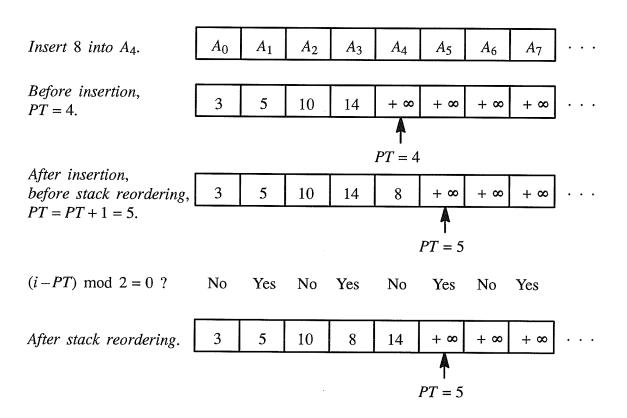

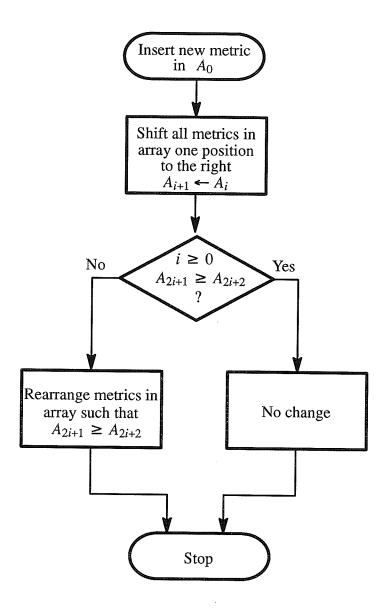

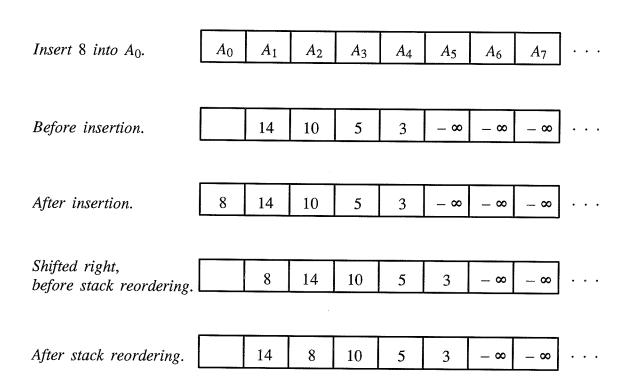

A flowchart for the insertion operation is shown in figure 2.11. An example of the insertion operation in the Random Access Memory Systolic Priority Queue is shown in figure 2.12.

Figure 2.11: Flowchart of the insertion of a succeeding path metric in Random Access Memory Systolic Priority Queue.

Figure 2.12: Example of the insertion operation in the Random Access Memory Systolic Priority Queue.

The deletion operation takes place according to the procedure described below.

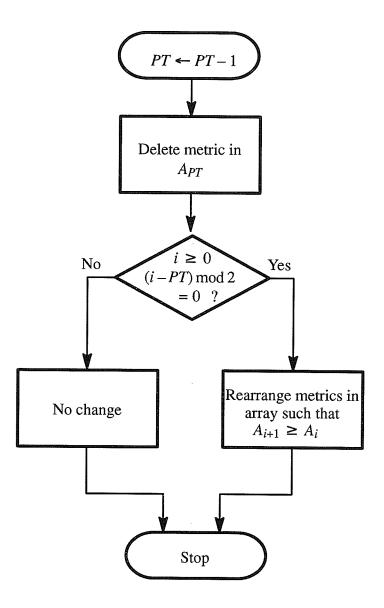

Deletion of the largest path metric  $m_k$  in RAM-SPQ:

- 1) Decrement PT by one,  $PT \leftarrow PT 1$ .

- 2) Empty  $A_{PT}$ , which contains the largest path metric  $m_k$ .

- 3) If i satisfies  $(i-PT) \mod 2 = 0$ , for  $i \ge 0$ , then rearrange the metric values in  $A_i$  and  $A_{i+1}$  such that the metric value in  $A_{i+1}$  is greater than or equal to the metric value in  $A_i$ ,  $A_{i+1} \ge A_i$ .

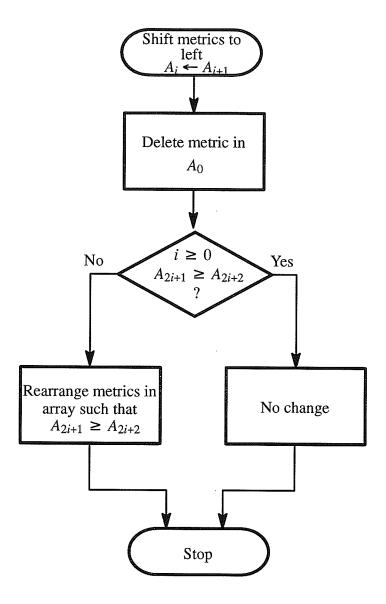

Figure 2.13 shows a flowchart for the deletion operation. Figure 2.14 shows an example of the deletion operation in the Random Access Memory Systolic Priority Queue.

Figure 2.13: Flowchart of the deletion of the largest path metric in Random Access Memory Systolic Priority Queue.

Figure 2.14: Example of the deletion operation in the Random Access Memory Systolic Priority Queue. Note: The path metric inside the parenthesis () is overwritten by the path metric in the next insertion step.

The examples shown in figure 2.12 and figure 2.14 illustrate the following properties of the Random Access Memory Systolic Priority Queue.

- 1). Only one control signal PT is required. PT is either incremented by one (PT+1) to locate the next available register for insertion of a new metric or decremented by one (PT-1) to locate the register which holds the largest metric value for deletion.

- 2). After each insertion or deletion, the order of metric values in the array are reordered in pairs of two adjacent registers and the stack reordering can be done in a parallel or pipeline manner. Thus, the array reordering procedure can be done in a fixed and short interval of time and the time required is independent of the number of metric values in the array.

- 3). After each array reordering, although the path metric values are only in a partly descending order,  $A_{PT-1}$  will always contain the largest path metric value ready for the next deletion and  $A_{PT}$  is always the next available register ready for insertion of a new metric.

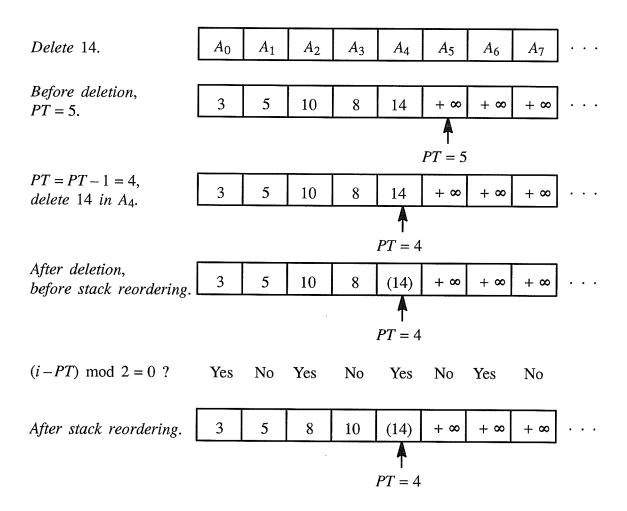

With a basic understanding in the insertion, deletion and array reordering procedure of the RAM–SPQ, the application of this particular type of systolic priority queue in the stack algorithm is demonstrated by an example. Figure 2.15 shows the flowchart of the RAM scheme stack algorithm. Figure 2.16 shows an ISI tree to which the RAM scheme stack algorithm is applied. The number labeled at each node is the path metric of the path represented by that particular node. Several steps in decoding the ISI code tree shown in figure 2.16 is considered. The contents of the RAM–SPQ at each decoding step is shown in figure 2.17.

Figure 2.15: Flowchart of the RAM scheme stack algorithm for a channel with binary inputs.

Figure 2.16: Example of a code tree for an ISI channel with binary inputs.

| Step | Operation | $A_0$ | $A_1$ | $A_2$ | $A_3$          | $A_4$ | $A_5$      | $A_6$ | $A_7$ | $A_8$ | ]     |

|------|-----------|-------|-------|-------|----------------|-------|------------|-------|-------|-------|-------|

| ыср  | operation | + &   | + ∞   | + ∞   | + ∞            | + ∞   | + <b>∞</b> | + ∞   | + ∞   | + ∞   |       |

|      |           |       |       | , ,,  | 1              |       | 1 33       |       | 1 00  | 1 ~   |       |

| 1    | insert 27 | 27    | + ∞   | + &   | + ∞            | + ∞   | + ∞        | +∞    | + ∞   | + ∞   |       |

|      | insert 21 | 27    | 21    | + ∞   | + ∞            | + ∞   | +∞         | + ∞   | +∞    | + ∞   |       |

| 2    | delete 27 | 21    | (27)  | + ∞   | + ∞            | + ∞   | + ∞        | + ∞   | + ∞   | + ∞   |       |

| 2    | insert 24 | 21    | 24    | + ∞   | + ∞            | + ∞   | + ∞        | + ∞   | + ∞   | + 8   |       |

|      | insert 18 | 21    | 24    | 18    | + ∞            | + ∞   | + ∞        | + ∞   | + &   | + 8   |       |

|      | <i></i>   |       |       |       |                |       | ·          |       |       | •     |       |

| 3    | delete 24 | 21    | 18    | (24)  | +              | + 8   | + 8        | + 8   | + ∞   | + ∞   | • • • |

|      | insert 21 | 18    | 21    | 21    | + &            | + 8   | +          | + 8   | + &   | + 8   |       |

|      | insert 15 | 18    | 21    | 21    | 15             | + ∞   | + ∞        | + ∞   | + &   | + &   | • • • |

|      |           | 10    |       |       | / <b>A</b> 4 \ |       |            |       |       |       |       |

| 4    | delete 21 | 18    | 21    | 15    | (21)           | + ∞   | + ∞        | + 8   | + ∞   | + ∞   |       |

|      | insert 12 | 18    | 15    | 21    | 12             | + ∞   | +∞         | + ∞   | + ∞   | + ∞   |       |

|      | insert 18 | 15    | 18    | 12    | 21             | 18    | + ∞        | +∞    | + ∞   | + ∞   |       |

| _    |           | 1,-   | 10    | 4.0   | 10             | (0.1) |            |       |       |       |       |

| 5    | delete 21 | 15    | 12    | 18    | 18             | (21)  | + ∞        | + ∞   | + ∞   | + ∞   |       |

|      | insert 6  | 12    | 15    | 18    | 18             | 6     | + ∞        | + ∞   | +∞    | + ∞   |       |