# Waveform Relaxation Based Hardware-in-the-Loop Simulation

# By Mohammad (Monty) Goulkhah

# A thesis Submitted to the Faculty of Graduate Studies in partial fulfilment of the requirements for the degree of

## Doctor of Philosophy

Department of Electrical and Computer Engineering

Faculty of Engineering

University of Manitoba

Winnipeg, Manitoba

© Copyright by Mohammad (Monty) Goulkhah 2015

#### Abstract

This thesis introduces an alternative potentially low cost solution for hardware-in-the-loop (HIL) simulation based on the waveform relaxation (WR) method. The WR technique is extended so that, without the need for a real-time simulator, the behaviour of an actual piece of physical hardware can nevertheless be tested as though it were connected to a large external electrical network. This is achieved by simulating the external network on an off-line electromagnetic transients (EMT) simulation program, and utilizing iterative exchange of waveforms between the simulation and the hardware by means of a specialized Real-Time Player/Recorder (RTPR) interface device. The approach is referred to as waveform relaxation based hardware-in-the-loop (WR-HIL) simulation.

To make the method possible, the thesis introduces several new innovations for stabilizing and accelerating the WR-HIL algorithm. It is shown that the classical WR shows poor or no convergence when at least one of the subsystems is an actual device. The noise and analog-digital converters' quantization errors and other hardware disturbances can affect the waveforms and cause the WR to diverge. Therefore, the application of the WR method in performing HIL simulation is not straightforward and the classical WR need to be modified accordingly.

Three convergence techniques are proposed to improve the WR-HIL simulation convergence. Each technique is evaluated by an experimental example. The stability of the

WR-HIL simulation is studied and a stabilization technique is proposed to provide sufficient conditions for the simulation stability.

The approach is also extended to include the optimization of the parameters of power system controllers located in geographically distant places. The WR-HIL simulation technique is presented with several examples. At the end of the thesis, suggestions for the future work are presented.

# Acknowledgments

I would like to express my sincere gratitude to my advisor, Prof. A. Gole, for the continuous support of my PhD work, for his patience, motivation, and immense knowledge. His guidance helped me in accomplishing this research work and writing of this thesis.

I would like to thank the thesis examining committee, Dr. S. Filizadeh, Dr. J. Morrison, and Dr. B. Johnson, for their insightful comments and encouragement to widen my research from various perspectives and help me present a better work.

I thank Dr. A. M. Kulkarni, who introduced the waveform relaxation simulation method to me when he visited our university in 2011. He provided me with a number of references to start studying the waveform relaxation method. We had many useful discussions about this project while he was in Winnipeg and even after he left.

I thank my fellow labmates for the stimulating discussions, for making an ideal environment to research, and for all fun and unforgettable moments they created during my PhD study. I especially thank Dr. Tomas Yebra Vega, who dedicated a lot of time and effort to implement the proposed algorithms as a neat and easy-to-use simulation package.

I would like to thank my wife, Mana Yazdani, who devotedly dedicated a significant amount of time and effort to help me design many of the proposed approaches in this thesis while she was working on her PhD work as well. I could not imagine a more enjoyable PhD work without her love and her great support academically and spiritually.

# Dedication

I proudly dedicate this thesis to my wife, Mana Yazdani, my parents, Zahra and Gholamali Goulkhah, my mother in law, Guity Khadjehzadeh, my father in law, Manouchehr Yazdani, and my PhD supervisor, Prof. A. M. Gole.

# Contents

| Fr | ont I | Matter   |                                               |            |

|----|-------|----------|-----------------------------------------------|------------|

|    | Con   | tents    |                                               | j          |

|    | List  | of Tab   | oles                                          | <b>v</b> i |

|    | List  | of Fig   | ures                                          | vi         |

|    | List  | of Cor   | pyrighted Material                            | xii        |

| 1  | Intr  | oducti   | on                                            | 7          |

|    | 1.1   | Powe     | r Systems Simulation                          | 7          |

|    |       | 1.1.1    | Load flow simulation                          | g          |

|    |       | 1.1.2    | Transient stability simulation.               | g          |

|    |       | 1.1.3    | Electromagnetic transient simulation (EMT)    | 10         |

|    |       | 1.1.4    | HIL simulation                                | 11         |

|    |       | A.       | The Power Systems HIL method and applications | 11         |

|    |       | В.       | HIL simulation challenges                     | 13         |

|    | 1.2   | Intro    | duction to Waveform Relaxation                | 14         |

|    |       | 1.2.1    | Gauss-Seidel WR                               | 18         |

|    |       | 1.2.2    | Gauss-Jacobi WR                               | 21         |

|    |       | 1.2.3    | Advantages of Waveform Relaxation             | 22         |

|    |       | 1.2.4    | Classical WR Acceleration techniques          | 24         |

|    | 1.3   | Thesi    | s Outline                                     | 26         |

| 2  | Circ  | euit Sir | mulation Using WR                             | 29         |

|   | 2.1 | WR Applications in Circuit Simulation                          | 29 |

|---|-----|----------------------------------------------------------------|----|

|   |     | 2.1.1 Application in transient stability                       | 30 |

|   |     | 2.1.2 Application in power electronics                         | 30 |

|   |     | 2.1.3 Extension of WR to perform HIL simulation                | 31 |

|   | 2.2 | WR Based Circuit Simulation Example                            | 32 |

|   |     | Application of Time Windowing [25, 28, 33, 34]:                | 36 |

|   | 2.3 | WR Based HIL Simulation                                        | 39 |

|   |     | 2.3.1 WR-HIL method                                            | 39 |

|   |     | 2.3.2 Advantages of WR-HIL method                              | 43 |

|   | 2.4 | Concluding Remarks                                             | 45 |

| 3 | Phy | sical Implementation of WR-HIL                                 | 46 |

|   | 3.1 | Function of the Real-Time Player/Recorder                      | 46 |

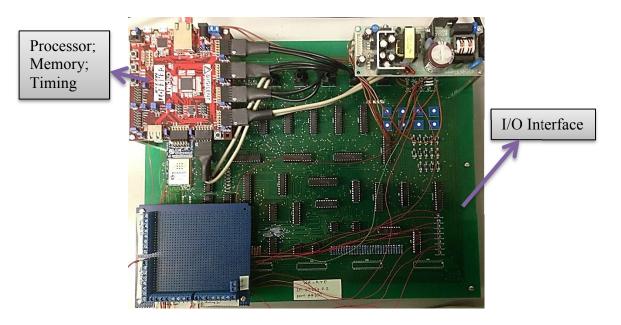

|   | 3.2 | Designed RTPR Prototype                                        | 48 |

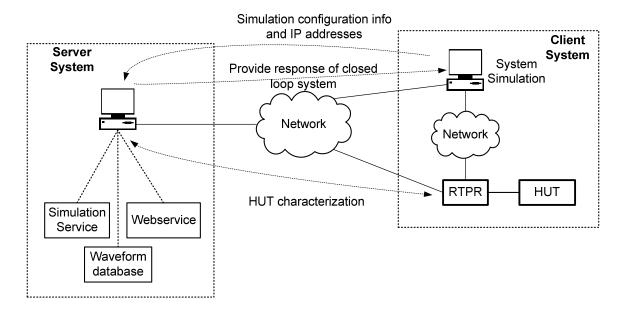

|   | 3.3 | Server-Based WR-HIL Implementation                             | 50 |

|   | 3.4 | WR-HIL Examples                                                | 51 |

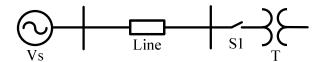

|   |     | 3.4.1 PHIL simulation example                                  | 51 |

|   |     | 3.4.2 WR-HIL based test of relay example                       | 54 |

|   | 3.5 | Concluding Remarks                                             | 60 |

| 4 | Cha | llenges in WR-HIL Convergence                                  | 62 |

|   | 4.1 | Convergence of WR                                              | 62 |

|   | 4.2 | WR Stability for Circuits Simulation                           | 63 |

|   |     | 4.2.1 Algebraic equations                                      | 63 |

|   |     | 4.2.2 Ordinary differential equations                          | 64 |

|   |     | 4.2.3 Differential-algebraic equations                         | 64 |

|   |     | 4.2.4 WR convergence for the resistive voltage divider circuit | 66 |

|   |     | 4.2.5 WR convergence for the R-L circuit                       | 67 |

|   | 4.3 | WR-HIL Convergence Problems                                    | 68 |

|   |     | 131 Noise                                                      | 68 |

|   |      | 4.3.2 Analog-digital converters and interface amplifiers     | 68  |

|---|------|--------------------------------------------------------------|-----|

|   |      | 4.3.3 Initial state of the hardware under test               | 69  |

|   |      | 4.3.4 WR-HIL convergence problem in testing relays           | 69  |

|   | 4.4  | Concluding Remarks                                           | 70  |

| 5 | Stal | pilization and Accelerated Convergence Techniques for WR-HIL | 71  |

|   | 5.1  | WR-HIL Stabilization Technique                               | 72  |

|   |      | 5.1.1 Method                                                 | 72  |

|   |      | 5.1.2 Example                                                | 74  |

|   | 5.2  | Accelerated Convergence Solutions for WR-HIL                 | 78  |

|   |      | 5.2.1 Piecewise Fixed Convergence Method (WR-PWFC)           | 79  |

|   |      | Algorithm                                                    | 79  |

|   |      | Experimental example                                         | 80  |

|   |      | 5.2.2 WR with internal control model (WR-ICM)                | 83  |

|   |      | Approach 1 (WR-ICM1)                                         | 84  |

|   |      | Approach 2 (WR-ICM2)                                         | 86  |

|   |      | Experimental example                                         | 87  |

|   |      | 5.2.3 Waveform Relaxation averaging method (WR-AM)           | 91  |

|   |      | Algorithm                                                    | 91  |

|   |      | Experimental example                                         | 93  |

|   | 5.3  | Parametric Analysis of WR Convergence Techniques             | 95  |

|   | 5.4  | WR-HIL Technique for Relay Testing                           | 98  |

|   |      | 5.4.1 Experimental example                                   | 99  |

|   |      | A. Fault duration <i>T<sub>f-dur</sub></i> =0.05 seconds     | 102 |

|   |      | B. Fault duration $T_{f-dur}$ =0.1 seconds                   | 105 |

|   |      | C. Fault duration $T_{f-dur}$ =0.25 seconds                  | 108 |

|   | 5.5  | Concluding Remarks                                           | 110 |

| 6 | Con  | troller Optimization with WR-HIL                             | 112 |

|   | 6.1  | Power System Controller Ontimization                         | 112 |

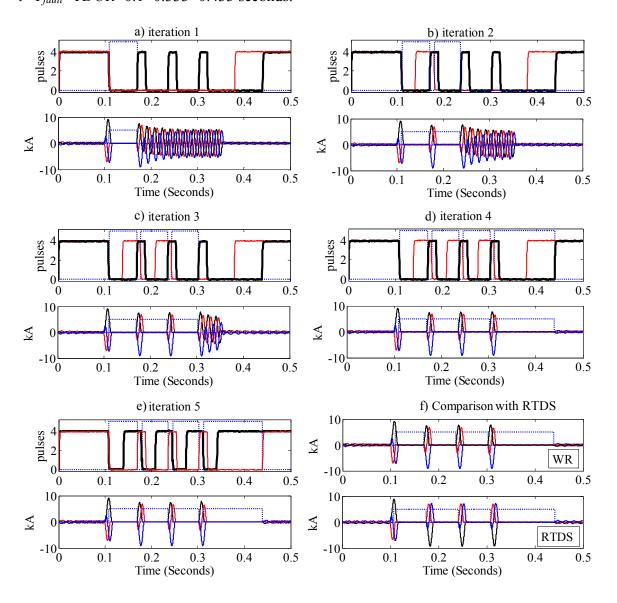

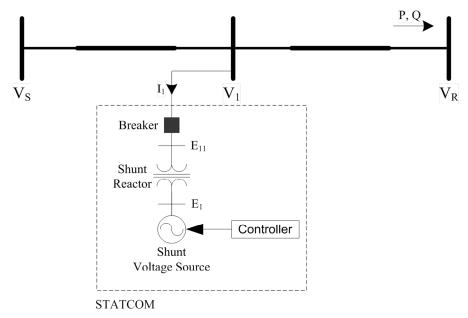

|   | 6.2      | WR-HIL Based Controllers Optimization                                        |

|---|----------|------------------------------------------------------------------------------|

|   |          | 6.2.1 Basic optimization algorithm with offline (non-WR) simulation          |

|   |          | 114                                                                          |

|   |          | 6.2.2 Proposed solution                                                      |

|   | 6.3      | Nonlinear Simplex Optimization Method                                        |

|   | 6.4      | Experimental Examples                                                        |

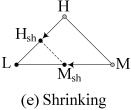

|   |          | 6.4.1 STATCOM PI controller tuning                                           |

|   |          | 6.4.2 HVDC controllers optimization                                          |

|   | 6.5      | Concluding Remarks                                                           |

|   |          |                                                                              |

| 7 | Pote     | ential WR-HIL applications 132                                               |

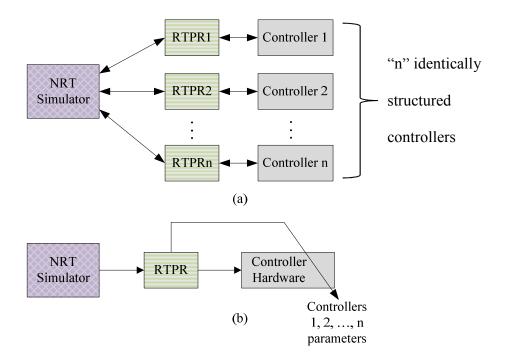

|   | 7.1      | Testing of Coupled Wide Area Controllers                                     |

|   | 7.2      | Simplified Test of Multiple Controllers with Identical Structure $\dots 135$ |

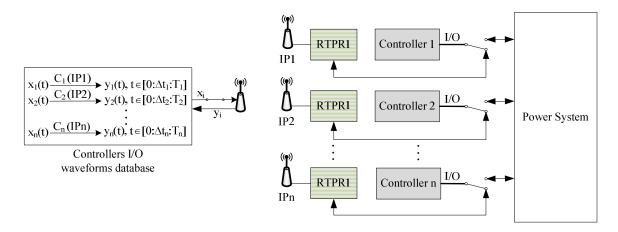

|   | 7.3      | Rapid Detection of Faulty Hardware                                           |

|   | 7.4      | Concluding Remarks                                                           |

| _ | <b>a</b> |                                                                              |

| 8 |          | tributions, Conclusions, and Future Work  141                                |

|   | 8.1      | Main Contributions of the Thesis                                             |

|   |          | 8.1.1 Hardware implementation of the method                                  |

|   |          | 8.1.2 Identifying WR-HIL challenges and proposing solutions 143              |

|   |          | 8.1.3 Optimization of controller parameters using WR-HIL 145                 |

|   |          | 8.1.4 Suggested potential applications for WR-HIL146                         |

|   | 8.2      | Recommended Future Work                                                      |

|   |          | 8.2.1 Implementation of suggested applications for WR-HIL                    |

|   |          | simulation in Chapter 7                                                      |

|   |          | 8.2.2 Accelerating WR-HIL convergence for testing black box                  |

|   |          | controllers                                                                  |

|   |          | 8.2.3 Parallel simulation of the power system models in WR-HIL               |

|   |          | approach                                                                     |

| 9  | Reference | es                              | 149 |

|----|-----------|---------------------------------|-----|

| Ap | pendix 1  | Gauss-Seidel WR Operator Matrix | 158 |

# List of Tables

| Table 2-1. Summary of WR simulation results with time windowing                 | acceleration   |

|---------------------------------------------------------------------------------|----------------|

| technique.                                                                      | 38             |

| Table 6-1. Initial guess parameters for Simplex algorithm and the optimization  | ation results. |

|                                                                                 | 123            |

| Table 6-2. 12 pulse HVDC CIGRE Benchmark [54] Model data                        | 126            |

| Table 6-3. OF values for the initial vertices, a random point, and the optimize | zation result. |

|                                                                                 | 129            |

# List of Figures

| Figure 1-1. Time frames of different power system transient phenomena [1]                               | 8  |

|---------------------------------------------------------------------------------------------------------|----|

| Figure 1-2. HIL simulation configuration.                                                               | 12 |

| Figure 1-3. Application of Relaxation techniques at different stages of solving a systematical systems. | em |

| of nonlinear differential equations [17].                                                               | 16 |

| Figure 1-4. GS-WR method for solving a set of two ordinary differential equations                       | 20 |

| Figure 1-5. GJ-WR method for solving a set of two ordinary differential equations                       | 21 |

| Figure 2-1. (a) A buck converter, (b) partitioning of the system of (a) into t                          | WO |

| subsystems.                                                                                             | 33 |

| Figure 2-2. Flow chart for WR implementation of Figure 2-1.                                             | 34 |

| Figure 2-3. Output voltage response in each WR iteration.                                               | 35 |

| Figure 2-4. Comparison of output voltage responses from WR and direct simulation                        | 36 |

| Figure 2-5. (a) Hardware connected to the physical system, (b) testing the hardware using               | ng |

| real-time simulators, (c) testing hardware using WR-HIL technique.                                      | 40 |

| Figure 2-6. Hardware-in-the-Loop simulation using the WR method.                                        | 42 |

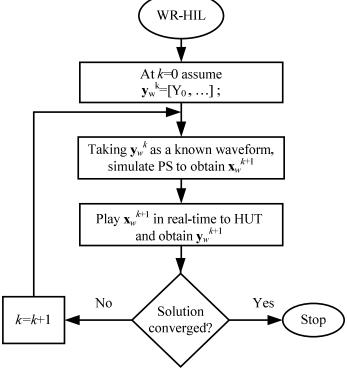

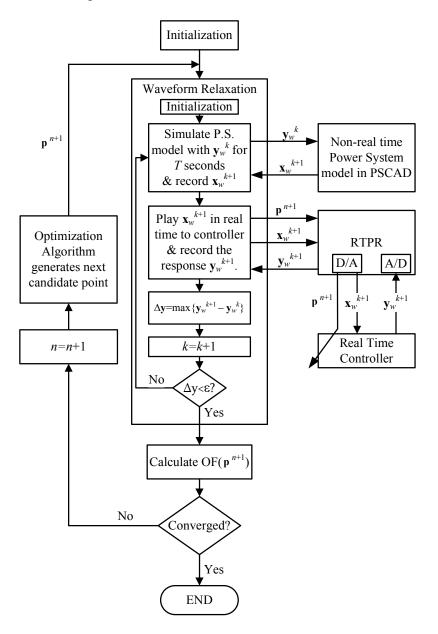

| Figure 2-7. Iterative WR-HIL simulation algorithm.                                                      | 42 |

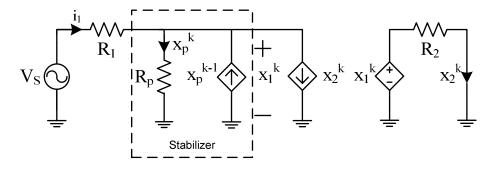

| Figure 3-1. Designed RTPR device circuit.                                                               | 48 |

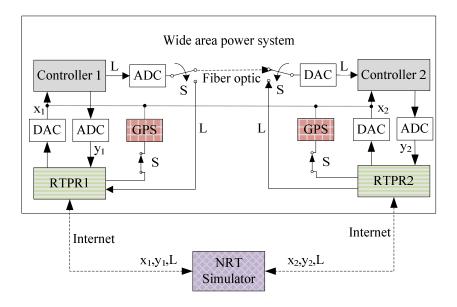

| Figure 3-2. Server based WR-HIL simulation.                                                             | 50 |

| Figure 3-3. Power system configuration.                                                                 | 52 |

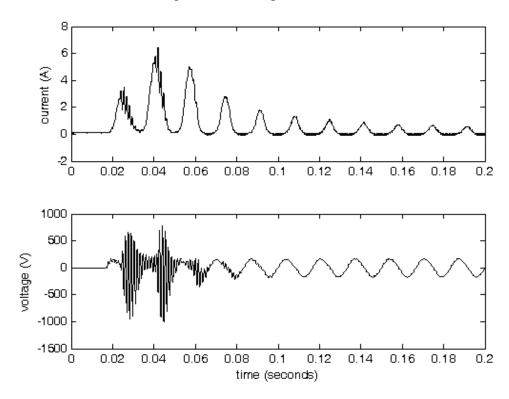

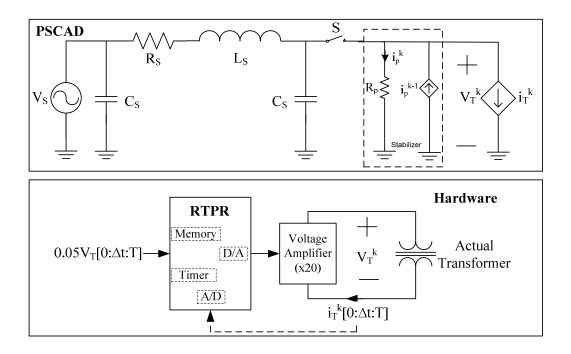

| Figure 3-4. Simulation and hardware setup for the WR-PHIL simulation of the actua        |

|------------------------------------------------------------------------------------------|

| transformer. 52                                                                          |

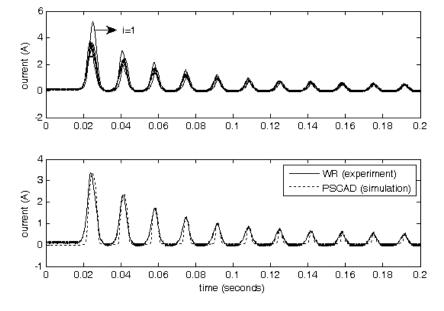

| Figure 3-5. WR-HIL response for the transformer's inrush current in each WR iteration    |

|                                                                                          |

| Figure 3-6. WR-HIL converged response for the transformer's inrush current compared      |

| to PSCAD/EMTDC transformer direct simulation. 54                                         |

| Figure 3-7. Waveform Relaxation based closed loop relay test example [45] 56             |

| Figure 3-8. Experimental results of the WR based closed loop relay test example          |

| compared to RTDS [45]                                                                    |

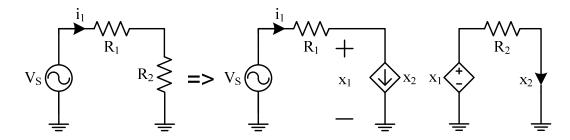

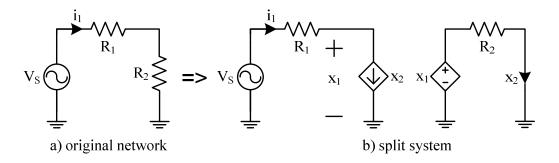

| Figure 4-1. The voltage divider circuit splitting using voltage type of ITM interface 66 |

| Figure 4-2. The R-L circuit partitioned by voltage type of ITM interface                 |

| Figure 5-1. The voltage divider circuit splitting using voltage type of ITM interface 72 |

| Figure 5-2. The voltage divider circuit with the proposed damping resistor to study the  |

| WR stability                                                                             |

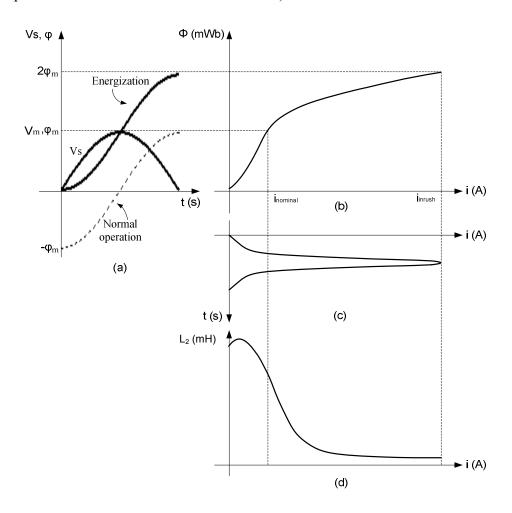

| Figure 5-3. Inrush current and magnetizing inductance of a typical power transformer 75  |

| Figure 5-4. WR-HIL nonconvergence for the long model of the transmission line in the     |

| transformer energization example (see Figure 3-4)                                        |

| Figure 5-5. Addition of the stabilizing circuit to the PSCAD/EMTDC system model 77       |

| Figure 5-6. Stability of WR-HIL in the transformer energization example with longer      |

| transmission line by application of the proposed stabilization technique                 |

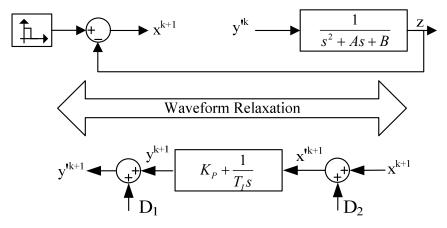

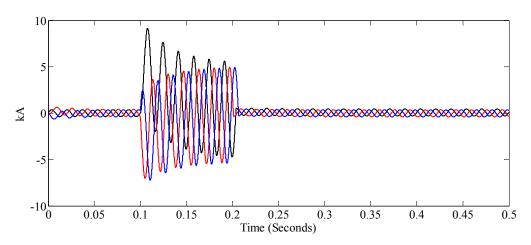

| Figure 5-7. WR-HIL simulation affected by hardware distortions D1 and D2                 |

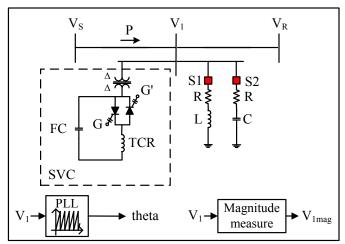

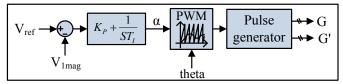

| Figure 5-8. WR-PWFC example for testing an SVC controller hardware                       |

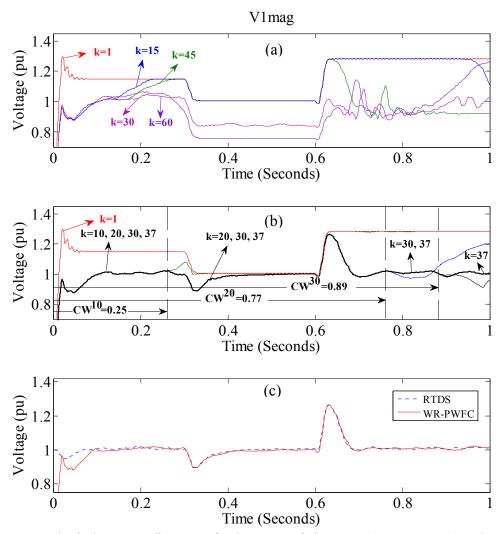

| Figure 5-9. (a) Classical WR-HIL divergence for the system of Figure 5-8, (b) WR-        |

|------------------------------------------------------------------------------------------|

| PWFC based HIL convergence shown for V1mag, (c) Comparison of V1mag waveform             |

| obtained from RTDS and WR-PWFC.                                                          |

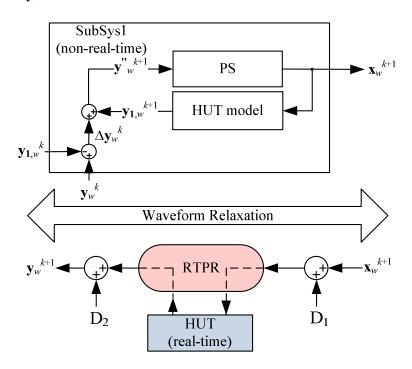

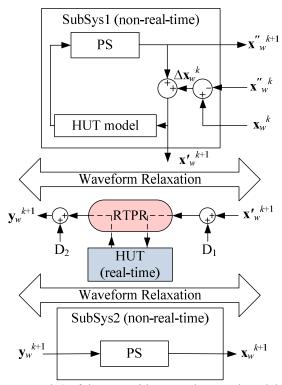

| Figure 5-10. Approach 1 of the WR with Internal Control model (WR-ICM1) 85               |

| Figure 5-11. Approach 2 of the WR with Internal Control model (WR-ICM2)                  |

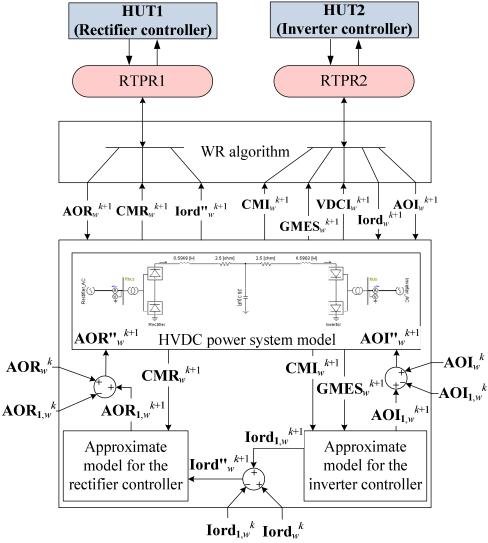

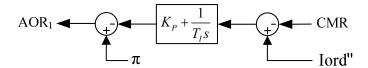

| Figure 5-12. WR-ICM1 for testing HVDC controllers: AOI: inverter angle order, AOR:       |

| rectifier angle order, VDCI: inverter DC voltage, CMI: dc current measured at inverter   |

| side, CMR: dc current measured at rectifier side, GMES: Gamma angle measured at          |

| inverter, <i>Iord</i> : rectifier current order from inverter.                           |

| Figure 5-13. A PSCAD/EMTDC approximate model for the rectifier controller                |

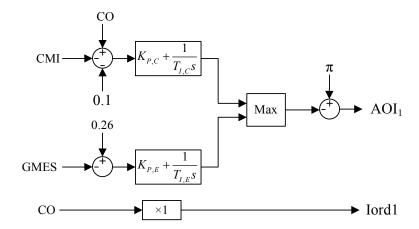

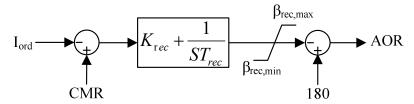

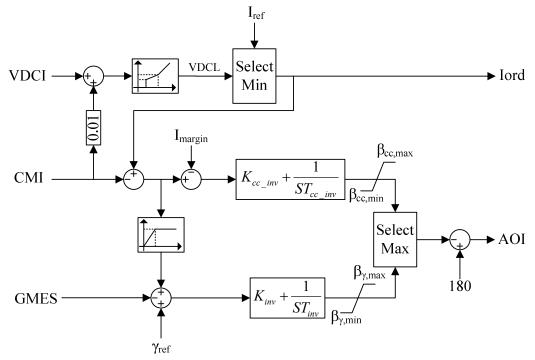

| Figure 5-14. Approximate model for the inverter controller. CO: reference current 89     |

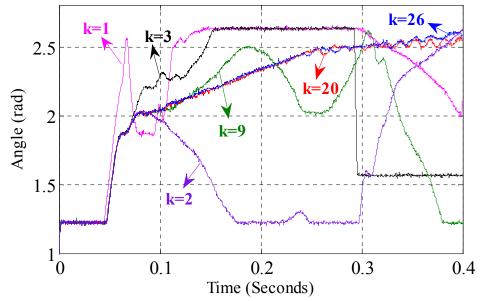

| Figure 5-15. Inverter angle order waveform in WR-ICM1 iteration. 90                      |

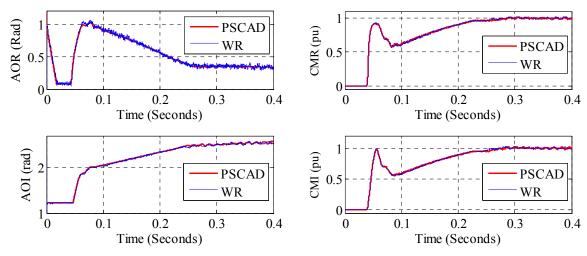

| Figure 5-16. Comparison of WR-ICM1 converged waveforms with direct                       |

| PSCAD/EMTDC simulation in testing HVDC rectifier and inverter controllers hardware.      |

| 90                                                                                       |

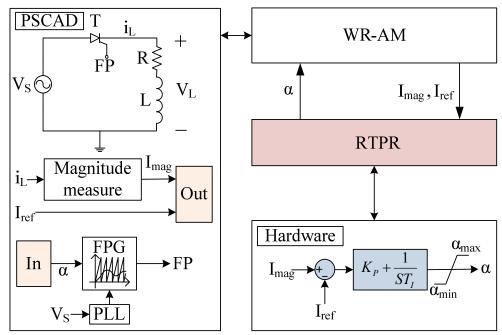

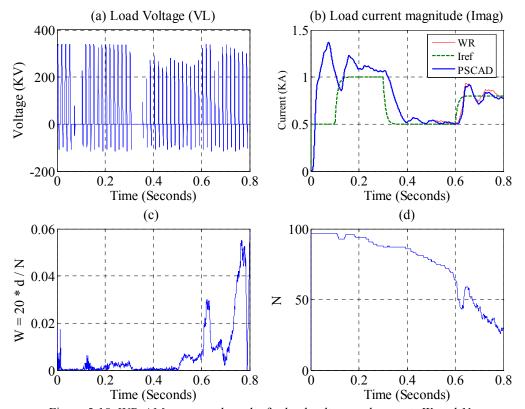

| Figure 5-17. PI controller in-the-loop with simulated rectifier using WR-AM              |

| Figure 5-18. WR-AM converged results for load voltage and current, W, and N 94           |

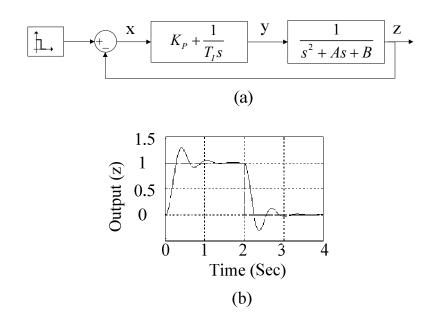

| Figure 5-19. A simple closed loop test system. 96                                        |

| Figure 5-20. Splitting system of Figure 5-19(a) in two subsystems for application of WR. |

| 96                                                                                       |

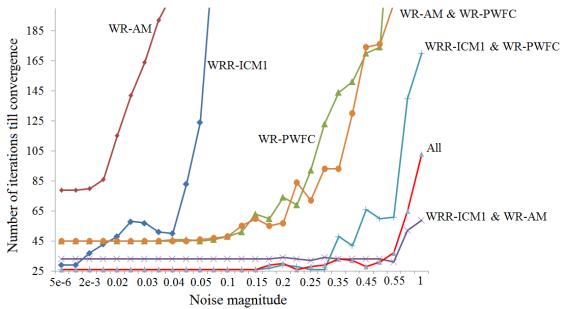

| Figure 5-21. Number of iterations required for convergence as a function of noise for    |

| different WR convergence techniques individually and in combination 97                   |

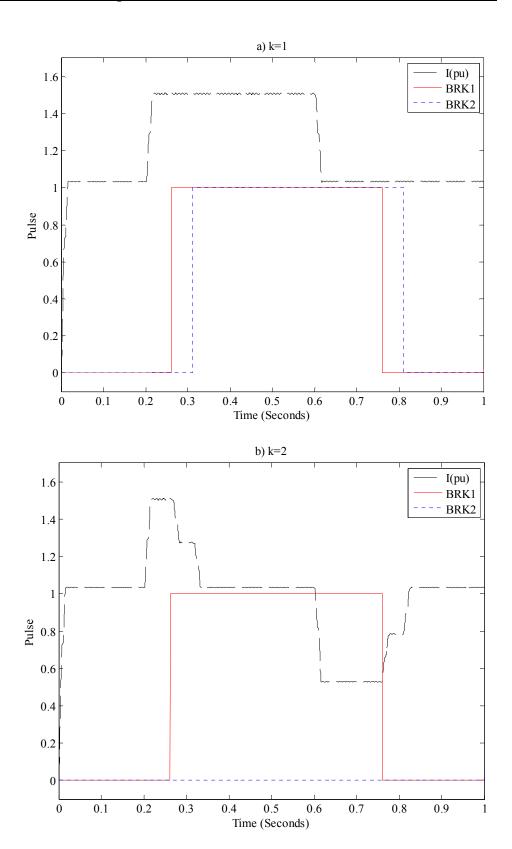

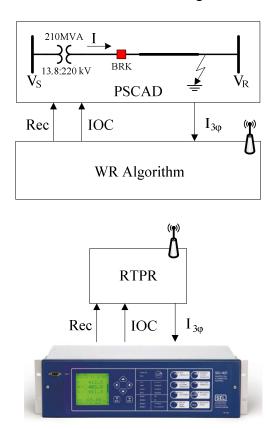

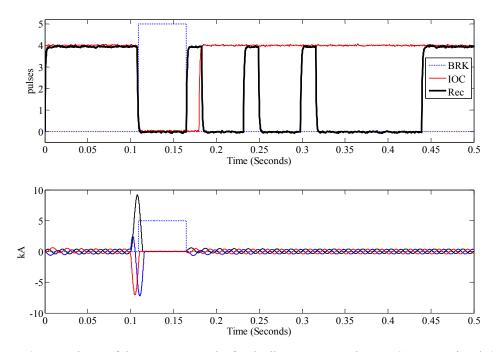

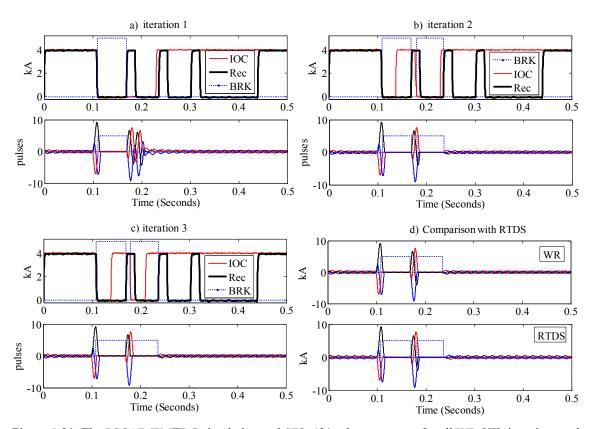

| Figure 5-22. Testing an instantaneous overcurrent (IOC) relay on SEL-421 platform with       |

|----------------------------------------------------------------------------------------------|

| the reclosing (Rec) function using the WR-HIL method [56].                                   |

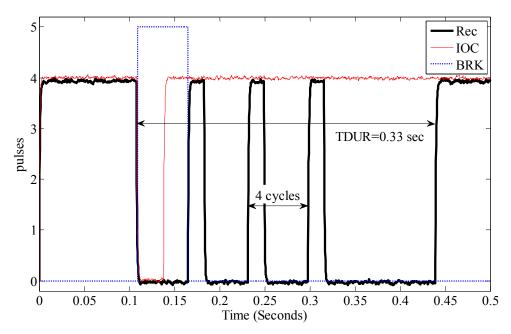

| Figure 5-23. An example of different trip signals used for testing the reclosing function of |

| SEL-421 [56]                                                                                 |

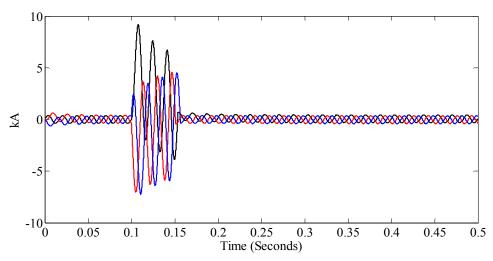

| Figure 5-24. Line's three phase currents: the initialization of the WR-HIL with simulating   |

| PSCAD/EMTDC power system with relay pulses <i>IOC</i> and <i>Rec</i> set to zero [56]        |

| Figure 5-25. Iteration 1 of the WR-HIL results for the line currents and SEL-421 output      |

| signals [56]                                                                                 |

| Figure 5-26. Iteration 2 of the WR-HIL results for the line currents and SEL-421 output      |

| signals [56]                                                                                 |

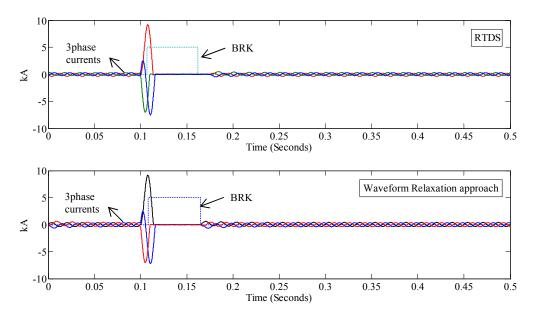

| Figure 5-27. Comparison of the WR-HIL converged results and the RTDS closed loop             |

| response for the example of $T_{f-dur}$ =0.05 seconds [56]                                   |

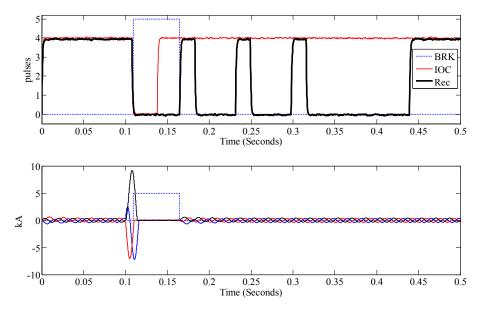

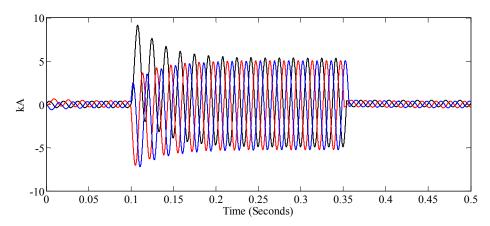

| Figure 5-28. Line's three phase currents: the initialization of the WR-HIL with simulating   |

| PSCAD/EMTDC power system with relay pulses <i>IOC</i> and <i>Rec</i> set to zero [56] 106    |

| Figure 5-29. The PSCAD/EMTDC simulation and SEL-421 relay responses for all WR-              |

| HIL iterations and comparison with RTDS closed loop simulation results [56] 107              |

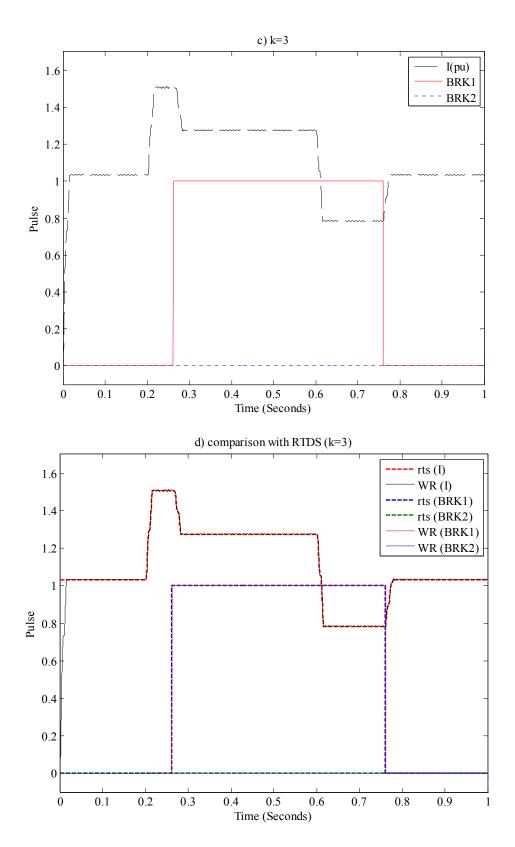

| Figure 5-30. Line's three phase currents: the initialization of the WR-HIL with simulating   |

| PSCAD/EMTDC power system with relay pulses <i>IOC</i> and <i>Rec</i> set to zero [56]        |

| Figure 5-31. The PSCAD/EMTDC simulation and SEL-421 relay responses for all WR-              |

| HIL iterations and comparison with RTDS closed loop simulation results [56] 109              |

| Figure 6-1. Basic optimization algorithm of a controller model within a power system         |

| modeled in PSCAD/EMTDC                                                                       |

| Figure 6-2. WR-HIL based optimization of an actual controller's parameters                   |

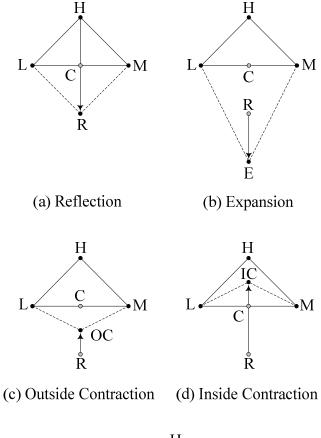

| Figure 6-3. Geometric operations used in the Simplex optimization algorithm (OF(L) <               |

|----------------------------------------------------------------------------------------------------|

| OF (M) < OF(H)). a) Reflection: moving the worst vertex (H) towards the minimum                    |

| point, b) Expansion: if $OF(R) \le OF(L)$ , c) Outside contraction: if $OF(L) \le OF(R) \le OF(R)$ |

| OF(M), d) Inside contraction: if $OF(R) > OF(M)$ , e) Shrinking: if $OF(OC)$ or $IC) > OF(M)$      |

| OF(H)                                                                                              |

| Figure 6-4. Power system and STATCOM modelled in PSCAD/EMTDC                                       |

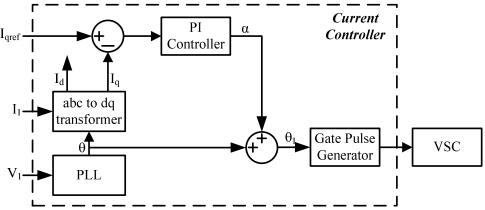

| Figure 6-5. STATCOM current controller implemented in hardware                                     |

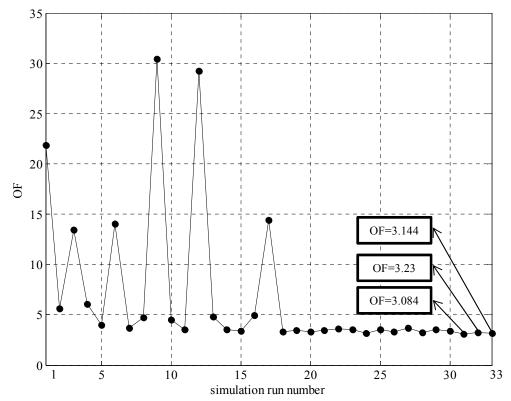

| Figure 6-6. Variation of OF in every Simplex iteration                                             |

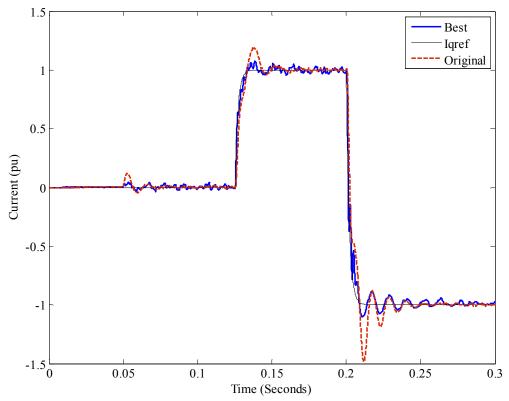

| Figure 6-7. STATCOM injected reactive current for the optimum point and the original               |

| point [63]                                                                                         |

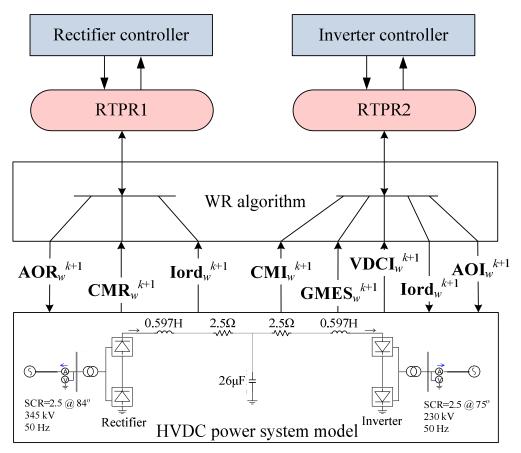

| Figure 6-8. WR-HIL based optimization of HVDC controllers: AOI: inverter angle order,              |

| AOR: rectifier angle order, VDCI: inverter dc voltage, CMI: dc current measured at                 |

| inverter side, CMR: dc current measured at rectifier side, GMES: Gamma angle                       |

| measured at inverter, Iord: rectifier current order from inverter                                  |

| Figure 6-9. HVDC rectifier controller (implemented in real-time hardware)                          |

| Figure 6-10. HVDC inverter controller (implemented in real-time hardware)                          |

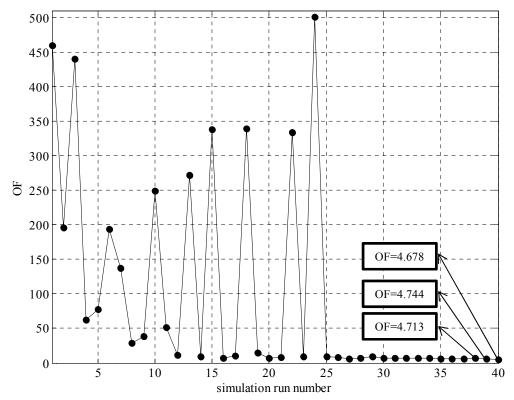

| Figure 6-11. Variation of OF at each Simplex iteration. 129                                        |

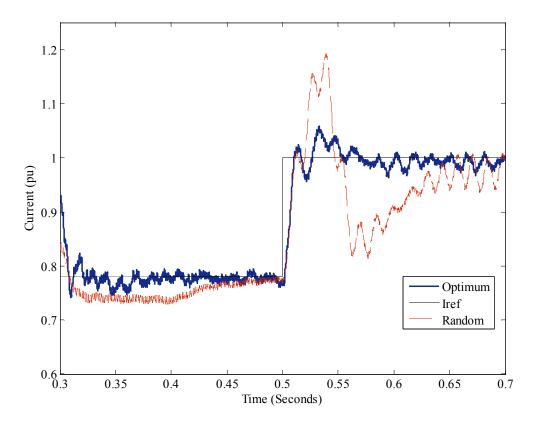

| Figure 6-12. Rectifier DC current comparison for the optimized and random controllers              |

| parameters. 130                                                                                    |

| Figure 7-1. Closed loop test of wide area controllers excluding or including the                   |

| communication link                                                                                 |

| Figure 7-2. Simplified test of multiple hardware with the same structure                           |

| Figure 7-3. Using RTPRs for rapid detection of faulty controller(s)                                |

# List of Copyrighted Material

- I. Figure 1-1 from the University of Manitoba dissertation (Xi Lin) [1].

- II. Figure 1-3 from the University of Saskatchewan dissertation (A. D. Jalnapurkar) [17].

- III. Figures 3-7 and 3-8 from Cigre-Canada conference paper (M. Goulkhah et al) [45].

- IV. Figures 5-22 to 5-31 from IEEE conference paper (M. Goulkhah et al) [56].

# Chapter 1

# Introduction

This thesis extends a traditional iterative method called waveform relaxation (WR) to perform hardware-in-the-loop (HIL) simulations in a new approach called Waveform Relaxation based Hardware-in-the-Loop simulation (WR-HIL).

In this chapter, an introduction to the HIL simulation and the related challenges are presented. Two popular WR methods are introduced and acceleration techniques, which are used to speed up the convergence of the traditional WR methods, are presented. At the end of the chapter, the thesis outline is presented.

# 1.1 Power Systems Simulation

Power systems are large and complex dynamic systems with thousands of buses, transmission lines, generators, transformers, ..., which all work together to supply the necessary power to the world. The nonlinear and complex behavior of a power system makes it difficult to study the transient and steady state response of the network within the context of variety of system disturbances such as faults, lightning strikes, switching,

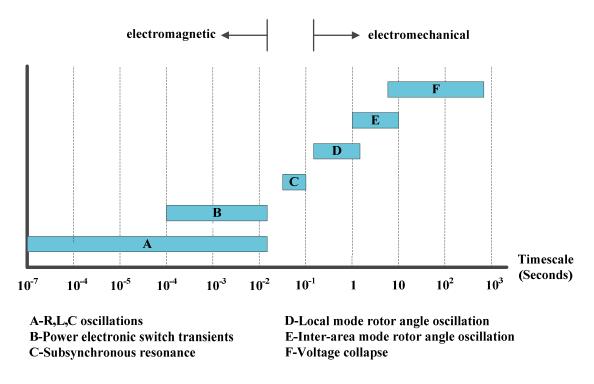

equipment failures, etc. Additionally, the time frames of important behaviors of the power systems range from microseconds to hours. For example, a voltage collapse may involve induction machine stalling, which occurs within a few seconds; or a transformer tap changer, whose time interval is tens of seconds; or an automatic generation control (AGC) actions, whose time frame is minutes; and many other actions with time frames ranging from seconds to tens of minutes. Power system dynamics are complicated and precise classification of the time frames in which various actions take place is difficult. Figure 1-1 shows a rough classification of these phenomena [1].

Figure 1-1. Time frames of different power system transient phenomena [1].

Load-flow study tools are used to analyze the steady state operation of power systems. These tools do not use detailed models of power system components and therefore cannot study the transient behaviour of power grids.

Digital time-domain simulation tools have been extensively used in power system studies to accurately study power system transients. In digital time-domain simulations, nonlinear differential equations, representing the model of the power system, are solved using numerical integration techniques. Two types of digital time-domain simulation tools are considered in power system studies: electromechanical transient simulation (also known as transient stability analysis (TSA)) and electromagnetic transient simulation (EMT). Different power system simulation tools are briefly described in the following section.

#### 1.1.1 Load flow simulation

A load- or power-flow study is a numerical calculation method for the flow of power from generators to loads under typical steady state conditions of power systems. Steady state voltage magnitudes and phase angles for every bus, real power and reactive power in generation and load buses, as well as transmission line flows can be obtained from a load-flow analysis. Load-flow analysis can identify flow congestion on power transmission corridors and can also determine whether voltages in the network are within their permissible thresholds. A load-flow study is valuable in planning future expansion of power systems and determining the best operation of existing power systems [2].

## 1.1.2 Transient stability simulation

This type of simulation tool is mainly used for predicting whether a large power system can regain a stable equilibrium point after being subjected to large disturbances such

as short circuit faults, disconnection of transmission lines, generators, transformers, controller failures, etc. [1]. In transient stability analysis (TSA), the dynamic behaviors of large-inertia power system components, such as electrical generators, and the dynamic interactions between them, which cause large energy flow variations are studied. In such studies, the major part of the electrical network is represented with a phasor (complex-algebraic) model, with the large-inertia components being represented with time-domain differential equations. TSA analysis provides information about the long term stability of the electro-mechanical network, but is not meant for fast dynamics such as power electronic interactions or transients caused by switching surges or lightning.

### 1.1.3 Electromagnetic transient simulation (EMT)

EMT simulation is a digital time-domain simulation tool that focuses on emulating the detailed behavior of the components of a power system, such as voltage spikes, current surges, voltage and current waveform distortions, harmonics, etc. [1]. One of the major applications of EMT simulation tools is simulating detailed semiconductor switching transients in power electronic devices. EMTP and PSCAD/EMTDC [3] are well known EMT simulation tools. EMT simulation uses the most detailed representation of the power network, and hence gives the most accurate results. However, it is computationally slower than TSA simulation.

### 1.1.4 HIL simulation

Hardware-in-the-Loop (HIL) is a closed loop system simulation, where part of the system is a computer model simulated in real-time and the other part is the actual hardware component under test. In this scheme, the real-time simulation of the computer model mimics an actual system to which the hardware component is to be connected in the real-life application. The real-time simulator is generally a real-time implementation of the EMT simulation described in Section 1.1.3.

## A. The Power Systems HIL method and applications

Today, the design of power system controllers, protective relays, power electronic converters, electric drives, and aerospace systems are becoming increasingly complex and expensive. The increased complexity and demand for the control systems increase the time and cost of design, implementation, and testing of new systems [4]. Traditionally, off-line simulation of computer models of systems was used to design controllers. The hardware implementation of the designed systems was then verified in field, i.e., by connecting the hardware implementation to an actual system. This, of course, increases not only the design time, but also the risk of damaging the control system itself and the controlled system, which is usually prohibitively expensive. Also, it is impractical, inaccurate, and too expensive and risky to test the system designs under a variety of system conditions, e.g., different fault locations and durations in a power system.

In recent years, HIL simulators have become commercially available as a safe solution to test and verify newly designed controller hardware by interfacing them with the simulated computer models of power systems. The principal requirement of HIL simulators is to ensure that the system simulation is performed in real-time by means of several powerful processing units. The instantaneous real-time values are exchanged at the interface between the simulation and the hardware. All signals are exchanged within each simulation time-step specified in the real-time (digital) simulator. Appropriate interface algorithms and hardware are required to minimize the delays in data communication between the simulation and hardware systems. Existence of such communication delays may lead to inaccurate and in some cases unstable simulations.

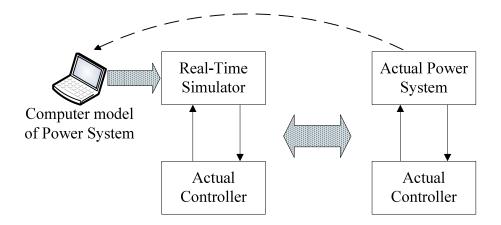

Figure 1-2. HIL simulation configuration.

Figure 1-2 displays a typical HIL simulation configuration, where a computer model of the power system is simulated in real-time by using the real-time simulators and the actual controller is connected to the system simulation for designing, testing, and verification steps. The closed loop results from connecting the controller and the simulated power system and then to the actual power system are identical if the simulated power system is accurate. In cases where the hardware under test (HUT) needs higher voltage or

current levels than what the real-time simulator interface can provide, voltage or current amplifiers are used in the interface between the real-time simulator and the HUT.

### B. HIL simulation challenges

*High costs:* The cost of HIL simulation can be very high. The main portion of the high costs is the expensive and often customized powerful processing units needed to simulate the system models in real-time.

Power system simulation size: Modern power systems often cover large geographic areas and can include components such as HVDC and FACTS controllers for the simulation for which small time-steps are required. The large size of the simulated power network models coupled with the small simulation time-steps imposes significant challenges for performing real-time simulations [4] as it requires fast parallel processing computers. This problem is partially addressed by advances in development of fast processors such as in digital signal processing (DSP) and FPGA technologies [5]. Currently, synchronized parallel processors are used for real-time simulation of large scale power systems that include power electronic components [5, 6, 7]. For instance, FPGAs with multiple processor boards are used in [7] for the real-time simulation of power electronic circuits.

Interface: When real-time digital simulators are used in HIL simulation, the simulation software and the real-world hardware must exchange data in every time-step. Particularly for small time-steps, this requires sophisticated and nontrivial interface designs between the real and simulated worlds. The challenge is that when a real-time simulator is interfaced to external hardware, the interface can often result in inaccurate simulation and even in instability [8-16] due to issues such as amplifier bandwidth and delays. There is

no unique interface algorithm that gives the best stable and accurate results for every simulated system. Instead, depending on the system to be simulated, an appropriate interface algorithm must be selected [8]. As a consequence of simulation instability caused by communication delays (either through wire or internet), HIL simulation with a real-time simulator is infeasible for the cases where the hardware under test is geographically remote from the real-time simulator, such as in another city or even another country.

## 1.2 Introduction to Waveform Relaxation

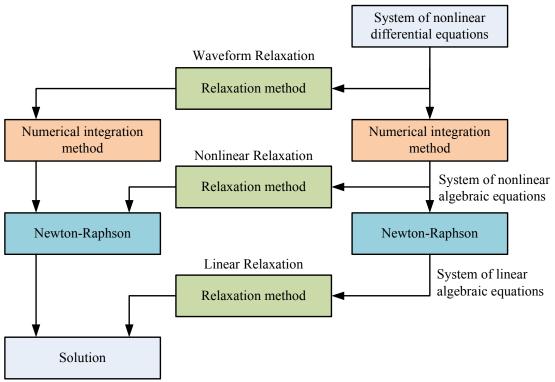

In classical definition, relaxation techniques are iterative numerical techniques to solve sets of linear or nonlinear algebraic, differential, and algebraic-differential equations. Relaxation techniques are usually classified as Linear, Nonlinear, and Waveform [17]. This classification is based on the level of the solution in which the relaxation technique is applied.

Consider a system of nonlinear differential equations. In the following discussion, direct methods as well as different ways of applying relaxation methods are separately described in solving the system of nonlinear differential equations [17].

<u>Direct methods</u>: An integration formula, such as Backward Euler or Trapezoidal Rule, is used to discretize the time derivative terms in the system of nonlinear equations. The application of integration formulas results in a set of nonlinear algebraic equations. These equations are then solved using a Newton-Raphson algorithm. Application of the Newton-Raphson algorithm results in a set of linear algebraic equations which then can be solved using any direct method, such as Gaussian elimination. Direct methods such as

the Newton-Raphson can solve a set of equations simultaneously. Depending on the size and complexity of the circuit, the cost of solution by such direct methods can be high. Relaxation techniques are used in order to decouple a set of equations and solve one variable at a time as described below.

Relaxation method: The relaxation technique can be applied at different stages of the solution described above as shown in Figure 1-3, i.e.; before application of the integration formula (labeled as Waveform Relaxation); after application of the integration formula and before applying the Newton-Raphson algorithm (labeled as Nonlinear Relaxation); or ultimately, after both stages of application of the integration formula and the Newton-Raphson algorithm (labeled as Linear Relaxation). All these types of relaxation techniques share a common feature, which is decoupling the resulting set of equations to solve only one variable at a time.

Comparison between Nonlinear Relaxation and direct Newton-Raphson algorithm: The Newton-Raphson algorithm is faster in convergence than Nonlinear Relaxation in solving a set of nonlinear algebraic equations [17]. However, the direct Newton-Raphson method solves a set of coupled simultaneous equations while the Nonlinear Relaxation method involves a set of decoupled equations. Thus, less memory is needed to solve the equations using the relaxation technique. Additionally, the inherent parallelism feature of the relaxation technique allows parallel simulation of the resulting decoupled equations.

<u>Comparison between Linear and Nonlinear Relaxation techniques</u>: This comparison can be made taking into account the size of the resulting equations which are solved by the Newton-Raphson algorithm. In Linear Relaxation technique, the Newton-Raphson algorithm needs to compute the Jacobian matrix of the resulting nonlinear algebraic equa-

tions which is quite expensive. However, in Nonlinear Relaxation technique, the Newton-Raphson algorithm only needs the partial derivative of the resulting nonlinear algebraic function with respect to a single variable, resulting in a considerable saving of the computer time per iteration [17].

Figure 1-3. Application of Relaxation techniques at different stages of solving a system of nonlinear differential equations [17].

<u>Waveform Relaxation</u>: If relaxation methods are applied to solve differential equations, they are called *Waveform Relaxation* methods. Different algorithms are classified by how the relaxation techniques are applied. *Gauss-Jacobi WR and Gauss-Seidel WR* are two of the common methods.

The following provides a brief classification of different types of equation sets that can be solved by WR methods. Such sets of equations, for example, may represent an electric circuit's mathematical model. In the following, it is assumed that [0, T] is the interval of interest in the simulation study.

A) Linear algebraic equations: In (1.1),  $\mathbf{A}$  is an  $m \times m$  matrix,  $\mathbf{x}$  is a vector of m variables,  $\mathbf{b}$  is the vector representing independent sources, and T is the total simulation time.

$$\mathbf{A}\mathbf{x}(t) = \mathbf{b} \quad , \quad t \in [0, T] \tag{1.1}$$

B) Nonlinear algebraic equations: The equations might appear as a set of nonlinear functions with respect to variables. This could be caused by existence of nonlinear elements in circuits such as variable resistors, power electronics switches, etc. Such systems may be represented as (1.2), where  $\mathbf{f}$  is a vector of nonlinear functions with respect to the variables, and  $\mathbf{u}$  is a vector of the inputs (i.e. independent sources).

$$\mathbf{f}(\mathbf{x}(t), \mathbf{u}(t)) = 0$$

,  $t \in [0, T]$  (1.2)

C) Linear ordinary differential equations (ODE):

$$\mathbf{B}\dot{\mathbf{x}}(t) + \mathbf{A}\mathbf{x}(t) = \mathbf{b} , \quad \mathbf{x}(0) = \mathbf{x}_0 , \quad t \in [0, T]$$

(1.3)

D) Nonlinear ordinary differential equations: (**f** is a vector of nonlinear functions).

$$\mathbf{f}(\dot{\mathbf{x}}(t), \mathbf{x}(t), \mathbf{u}(t)) = 0$$

,  $\mathbf{x}(0) = \mathbf{x}_0$  ,  $t \in [0, T]$  (1.4)

E) Differential-algebraic Equation (DAE): Later in Chapter 4, two main classes of such problems, Index-II and Index-II, are discussed and the WR convergence for DAE equations is studied.  $\mathbf{f}$  and  $\mathbf{g}$  in (1.5) are vectors of linear or nonlinear functions,  $\mathbf{x}$  is a vector of differential variables,  $\mathbf{z}$  is a vector of algebraic variables, and  $\mathbf{u}$  is inputs vector.

$$\begin{cases}

\dot{\mathbf{x}}(t) = \mathbf{f}(\mathbf{x}(\mathbf{t}), \mathbf{z}(\mathbf{t}), \mathbf{u}(t), t) , & \mathbf{x}(0) = \mathbf{x}_0 \\

\mathbf{z}(t) = \mathbf{g}(\mathbf{x}(\mathbf{t}), \mathbf{z}(\mathbf{t}), \mathbf{u}(t), t) , & t \in [0, T]

\end{cases}$$

(1.5)

Specific properties of different classes of equations, as briefly mentioned above, and the WR convergence properties when applied to solve these equations can be found in [17-27]. Also, a brief discussion about the WR convergence properties as applied to each set of above equations is presented in Chapter 4.

In following, the two common WR techniques, Gauss-Seidel and Gauss-Jacobi, are briefly explained.

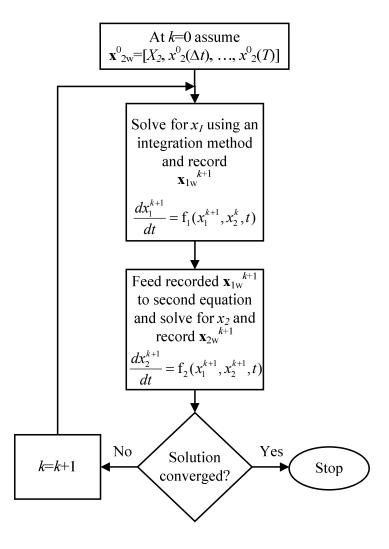

#### 1.2.1 Gauss-Seidel WR

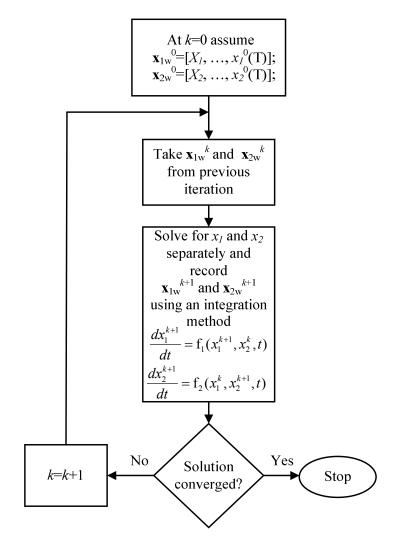

Gauss-Seidel Waveform Relaxation (GS-WR) method [17] is the sequential iterative solution of subsystems generated by partitioning the original set of equations. Here, this algorithm is explained for the initial value problem of the ODE system of (1.6) as an example, where  $f_1$  and  $f_2$  are linear or nonlinear functions, and  $x_1$  and  $x_2$  are the system variables with initial values  $X_1$  and  $X_2$ , respectively.

$$\begin{cases} \frac{dx_1}{dt} = f_1(x_1, x_2, t); & x_1(0) = X_1\\ \frac{dx_2}{dt} = f_2(x_1, x_2, t); & x_2(0) = X_2 \end{cases}$$

(1.6)

First, the order of subsystems to be solved is specified. In this example, the first equation of (1.6) is solved first. Then, the total simulation time T as well as the simulation time-step for each subsystem,  $\Delta t_1$  and  $\Delta t_2$ , are assigned. If the time-steps  $\Delta t_1$  and  $\Delta t_2$  are different values, interpolation methods are used to reconstruct the waveforms. As it will be seen later in this section, the algorithm needs to start from initial guess waveforms for the variables. The initial waveform guess for a variable must include the initial condition  $x_2(0)=X_2$ . For example, consider the initial guess (k=0, where k is the iteration count) for

the waveform  $\mathbf{X}_{2w}^{k}$ for variable  $x_2$ . It is of the form  $\mathbf{x}_{2w}^{k=0} = [x_2^0(0), x_2^0(\Delta t_2), x_2^0(2\Delta t_2), \dots, x_2^0(N\Delta t_2 = T)],$  where the w subscript implies that  $\mathbf{x}_{2w}$  is a waveform within the time interval of [0, T] constructed by sampled values of the variable  $x_2$ . The initial guess waveform for the variable  $x_2$  can be, for example, formed as  $\mathbf{x}_{2w}^{k=0} = [X_2, 0, 0, ..., 0]$ . Figure 1-4 describes the Gauss-Seidel WR algorithm for solving the set of differential equations as in (1.6). In Figure 1-4, it is assumed that both equations are solved with the same time-step of  $\Delta t_1 = \Delta t_2 = \Delta t$  for simplicity.

The initial guess of the waveform  $\mathbf{x}_{2\mathrm{w}}$ , i.e.  $\mathbf{x}^0{}_{2\mathrm{w}}$ , is fed into the first equation as a known fixed input. Then a numerical integration method is used to calculate the value of  $x_I$  at each simulation time-step  $\Delta t_I$  taking into account that  $x_I(0)=X_I$ . The value of  $x_I$  at each simulation time-step  $\Delta t_I$  is recorded into the memory as the waveform  $\mathbf{x}^1{}_{1\mathrm{w}}$ . When T seconds of simulation ends, the recorded waveform  $\mathbf{x}^1{}_{1\mathrm{w}}$  is fed back into the second equation as a fixed input signal. Then the numerical integration method solves for  $x_I$  and the value of  $x_I$  is recorded at every simulation time-step,  $\Delta t_I$  to give  $\mathbf{x}^1{}_{2\mathrm{w}}$ . This process is continued iteratively to convergence, i.e., when both  $\mathbf{x}^k{}_{1\mathrm{w}}$  and  $\mathbf{x}^k{}_{2\mathrm{w}}$  do not change significantly from their previous iterates. A convergence criterion, which can be the norm of the mathematical difference between the most recent and the past values of the waveform  $\mathbf{x}_{1\mathrm{w}}$  is compared with threshold  $\varepsilon$  as shown in (1.7). If it is smaller than the threshold, the system is assumed to have converged.

$$\left\|\mathbf{x}_{1\mathbf{w}}^{k+1} - \mathbf{x}_{1\mathbf{w}}^{k}\right\| < \epsilon \tag{1.7}$$

Figure 1-4. GS-WR method for solving a set of two ordinary differential equations.

The waveform norm can be defined for example as (1.8).

$$\|\mathbf{x}_{1w}^{k+1} - \mathbf{x}_{1w}^{k}\| = \max_{m=1,\dots,N} |\mathbf{x}_{1w}^{k+1}(m\Delta t) - \mathbf{x}_{1w}^{k}(m\Delta t)|$$

(1.8)

If the convergence criterion in (1.7) is satisfied, the algorithm ends; otherwise, the updated  $\mathbf{x}_{2w}$  is fed back into the first equation and the next iteration of the GS-WR is started and the iterations continue until the convergence condition is satisfied.

The ODEs of (1.6), when the GS-WR applied, can be rewritten as (1.9) [17].

$$\begin{cases} \frac{dx_1^{k+1}}{dt} = f_1(x_1^{k+1}, x_2^k, t); \\ \frac{dx_2^{k+1}}{dt} = f_2(x_1^{k+1}, x_2^{k+1}, t); \end{cases}$$

(1.9)

#### 1.2.2 Gauss-Jacobi WR

In Gauss-Jacobi Waveform Relaxation, GJ-WR, [17] all the subsystems are solved in parallel. This means that, for example, in the WR iteration k+1, the input waveforms to all subsystems are from the simulation results from the iteration k.

Figure 1-5. GJ-WR method for solving a set of two ordinary differential equations.

This method is popular in parallel simulation of the subsystems as the decoupled subsystems can be distributed on multiple processing units for parallel simulation. This algorithm is presented in Figure 1-5.

The ODEs of (1.6) can be rewritten as (1.10) [17], when the GJ-WR applied.

$$\begin{cases} \frac{dx_1^{k+1}}{dt} = f_1(x_1^{k+1}, x_2^k, t); \\ \frac{dx_2^{k+1}}{dt} = f_2(x_1^k, x_2^{k+1}, t); \end{cases}$$

(1.10)

## 1.2.3 Advantages of Waveform Relaxation

The standard circuit simulators use *standard time-stepping schemes*, i.e. they employ numerical integration methods to discretize the nonlinear DAEs in time. Then, the extracted systems of algebraic equations are solved at each time-step [19]. Usually, calculation of the inverse of the resultant Jacobian matrix of the linearized system is expensive (large memory size and powerful processor units are required) and time consuming especially in cases where the matrix elements change in time (e.g. switching actions in a power electronic circuit). On the other hand, consider the nonlinear DAE problem as shown in (1.5). The rate of change of each variable can be different from the others depending on the structure of the original system. The appropriate simulation time-step is generally determined by the variable whose rate of change in time is the fastest among other variables. By choosing an adequately small time-step for the fastest variables, slow changing variables will also be calculated with the small time-step, which leads to redundant high resolution of the solution for the slow variables.

The WR methods could be applied to overcome some of the issues mentioned above. In this scheme, the circuit model is decomposed into smaller subsystems. In classical applications of the WR method, the partitioning can be done carefully to increase the convergence rate of the simulation. A proper partitioning decomposes weakly connected groups in a circuit, while each group consists of strongly connected elements. A simulation time-step is assigned to each subsystem based on the rate of change of the fastest mode. The generated subsystems are thus solved separately using a suitable numerical integration method for the entire simulation time. One loop of the WR algorithm is accomplished after all the subsystems are simulated for the time interval of interest sequentially (Gauss-Seidel WR), or in parallel (Gauss-Jacobi WR). In cases where the rate of change of signals for different variables is different, the WR method can significantly decrease the time consumed for the simulation of the system in comparison to direct solutions.

The main drawback of the WR algorithms is the high memory usage since the WR waveforms resulting from simulation of all subsystems are recorded to be used in the current or the next WR iterations. Also, a weak partitioning (i.e. partitioning a system within strongly connected points) may dramatically increase the number of iterations required for the WR to converge. It also should be noted that the classical WR methods have lost their popularity for circuits simulation recently because of the advanced technology in manufacturing powerful and cost-effective processor units and cheap memory. In this thesis, the WR method is used to create a new cost-effective HIL simulation method, which is a different approach than its classical use.

## 1.2.4 Classical WR Acceleration techniques

Without any special speed-up method, GS-WR and GJ-WR can be excessively slow in convergence especially when there are strong feedback loops in the circuits being modeled [6]. Significant research has been conducted to propose new acceleration methods for WR algorithms. A selection of popular acceleration techniques suitable for waveform relaxation based circuits simulation are briefly discussed here.

Partitioning refers to the decomposition of the system into two or more subsystems such that each subsystem shares a common characteristic among its members [28-32]. Multi-rate simulation of the generated subsystems, i.e., simulating subsystems using different time-steps, may accelerate the WR algorithm by solving the slow changing variables with larger time-steps and vice versa. Multi-rate simulation has been used in conventional fixed time-step programs by splitting the larger system into smaller blocks, each running with a different fixed time-step and interfacing them [33].

Time Windowing breaks down the entire simulation time interval into smaller time segments in order to avoid solving the subsystems within sections of time in which the solution is already converged. By applying this technique appropriately, the time spent for the WR convergence can be reduced. However, determination of the size of the time segments whether fixed or variable, statically (before starting the simulation) or dynamically (during the simulation), in a simulation case could be a challenge [25, 28, 34, 35].

Scheduling occurs after partitioning the original system, where the order of solving the subsystems may affect the WR convergence speed. For instance, it is recommended in [28] to solve subsystems with slow changing variables first and then those with fast

changing rates, especially when the windowing technique is applied. For instance, in a current time window, the slow subsystem is first analyzed based on the response of the fast subsystem from the previous time window. Then, the results obtained from the slow subsystem are applied to the fast subsystem in the current time window. The response of the fast subsystem is once again used in the slow subsystem to refine the results acquired in the previous iteration. Specifically, for short time windows, for many applications, these results are accurate enough and no more iterations would be necessary [28].

With *Time-step Acceleration* technique, the subsystems are initially solved with a large simulation time-step for a sufficiently large number of iterations, i.e. until a convergence criterion is satisfied, where that convergence criterion needs not be too small. The resulting low-resolution waveforms are used as inputs for further simulation of the subsystems with the precise time-steps. In this way, only a few iterations may be required to achieve the high-resolution simulation results after changing the time-steps from large to small values [36, 37]. This method can reduce the WR convergence time because the simulation of the subsystems with larger time-steps in the earlier iterations is fast.

Successive Overrelaxation (SOR) manipulates the resulted output waveform from the simulation of a subsystem which will be then fed back as input into another subsystem. This is done by adding a multiple of the "error waveform" to the waveform from the previous iteration [19, 38, 39]. Here, the "error waveform" is the subtraction of the two waveforms recorded from the last two WR iterations for a system variable. For example, once  $\mathbf{x}_{1\mathrm{w}}^{k+1}$  is obtained from the simulation of the first equation in (1.9), the manipulated waveform  $\mathbf{x}_{1\mathrm{w}}^{k+1} = \mathbf{x}_{1\mathrm{w}}^k + K(\mathbf{x}_{1\mathrm{w}}^{k+1} - \mathbf{x}_{1\mathrm{w}}^k)$  is provided as the input to the second equation,

where K is a constant. Similarly,  $\mathbf{x}'_{2\mathbf{w}}^{k+1}$  is calculated and fed as input to the first equation in the next WR iteration. In order to gain the fastest convergence, some analysis needs to be conducted to optimize the constant K to obtain the fastest rate of WR convergence [19]. In this work, for solving algebraic-differential equations generated by partitioning a circuit,  $K\approx0.9$  resulted in adequate acceleration of the WR methods in most of the cases.

### 1.3 Thesis Outline

Chapter 2 gives an overview for the simulation of electric circuits using the classical waveform relaxation method. Further in this chapter, the waveform relaxation based hardware-in-the-loop (WR-HIL) simulation as a new application for the waveform relaxation method is introduced.

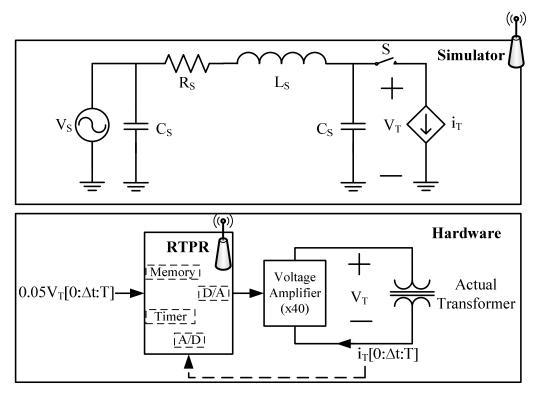

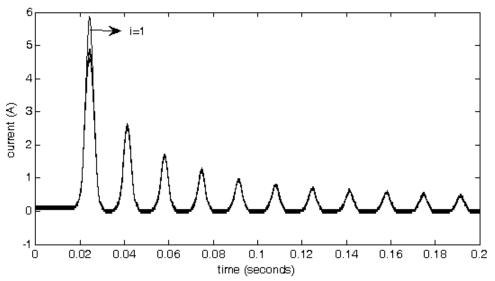

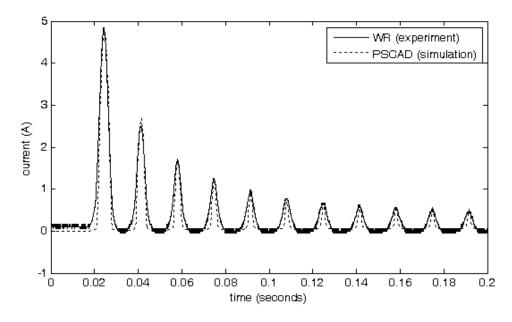

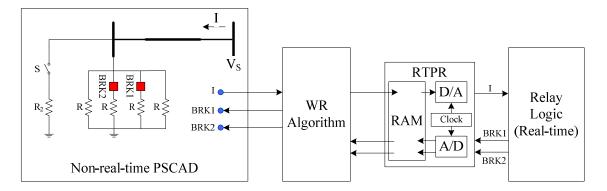

The WR-HIL method is implemented in hardware by means of a specialized Real-Time Player/Recorder (RTPR) device designed and presented in Chapter 3. The device receives the waveforms generated from the off-line EMT simulation and plays them back in real-time to the actual hardware under test (HUT). The RTPR also samples, digitizes, and records the HUT's output response waveforms and makes them available to the EMT simulation in each WR iteration. Two simple examples of the WR-HIL simulation using the designed RTPR are given. In one example, the WR-HIL simulation technique is used to conduct a Power Hardware-in-the-Loop (PHIL) simulation, where the connection of a 120V transformer to the off-line PSCAD/EMTDC simulation program is simulated. In the second example, the approach is used to test two coordinated instantaneous overcur-

rent protective relays. In this example also, the power system model is simulated in the off-line PSCAD/EMTDC program.

The application of the WR method for performing HIL simulation as described above is not straight-forward. The use of real hardware creates many challenges for convergence of the WR method not reported in its classical, purely software-based use. In classical WR, for a simulated system the partitioning points between subsystems can be carefully selected to ensure fast convergence of the WR method. This luxury is not available in WR-HIL, as the interface point must of course be the point at which the physical device would connect to the remainder of system, making convergence more difficult. Also existence of noise (including quantization errors in analog-digital conversion) can cause the WR to diverge. Chapter 4 discusses such practical and theoretical issues. Furthermore, an analytical study for the stability of the WR based Power Hardware-in-the-Loop (WR-PHIL) simulation is given. It will be shown that the WR may face instability under certain conditions just as in the traditional HIL simulation technique.

In Chapter 5, the convergence problems reported in Chapter 4 are solved by several proposed solutions. Also a stabilization technique is proposed to stabilize the WR-HIL simulation for the cases where the stability criteria found in Chapter 4 are not met.

Chapter 6 extends the WR-HIL simulation approach to enable the optimization of parameters of power system controllers. The proposed algorithm is validated by optimal tuning of two physical controller HIL systems. In these examples, the power system models are simulated in the off-line PSCAD/EMTDC simulation program and the RTPR device is used as the interface to exchange the waveforms between the simulator and the

controllers. The examples include the optimization of the parameters of High Voltage Direct Current (HVDC) and Static Compensator (STATCOM) controllers.

Chapter 7 proposes some potential industrial applications in which the proposed WR-HIL simulation could be applied. In the end of the thesis, conclusions are given and a number of suggestions for the future work are presented.

# Chapter 2

# Circuit Simulation Using WR

The traditional Waveform Relaxation method has been used in the past to iteratively solve a set of coupled differential equations. This method was later used to speed up the simulation of electric circuits including power systems by partitioning the original circuit into two or more subsystems. In this chapter, this kind of WR application is explained and further the method is extended to perform Hardware-in-the-Loop simulation, which is the principal contribution of this thesis.

### 2.1 WR Applications in Circuit Simulation

The Waveform Relaxation method has been used for the simulation of electric circuits such as Very Large Scale Integration (VLSI) circuits [25], power systems transient stability studies [34, 35, 40, 41, 42], power electronics simulation [28], and closed loop simulation of wide-area control systems in power networks [43]. These applications of the WR method are briefly discussed in this section.

#### 2.1.1 Application in transient stability

The Waveform Relaxation method has been applied in the past to study the transient stability of typical power systems. In [34], the sets of coherent generators were partitioned into separate equation sets for applying the WR method. In this way, the generators in the power system that are strongly coupled to each other but weakly coupled to the rest of the system are clustered as one group. The fastest mode, i.e., the variable with highest rate of change, in each group determines the largest possible simulation time-step for that group. Power systems are stiff systems, i.e., the difference between the rates of change of the fastest and the slowest modes are significant; and partitioning is the most efficient acceleration technique [34] as was mentioned in Section 1.2.4.

The application of the WR in the simulation of power systems for transient stability studies is also investigated in [35]. It is shown in [35] that the WR methods always converge when applied for the transient stability analysis of the power systems if the coupling between the subsystems (groups of electric machines) is weak. For a typical multimachine power system, the simulation results in [35] show approximately 50% reduction in the WR convergence time when windowing and coherence based partitioning techniques were applied [19].

#### 2.1.2 Application in power electronics

The application of the WR method for fast time-domain simulation of power electronic systems is investigated in [28]. A typical power electronic circuit is first decomposed into slow and fast subsystems. The main energy storage elements, input sources, and con-

trollers in feedback loops are chosen as the elements of the slow subsystem. On the other hand, the fast subsystem consists of power electronic switches, resonant circuits, snubber circuits, and parasitic elements. "Time windowing" is mentioned as the most suitable acceleration technique for the WR based simulation of such power electronic circuits. In [28], the size of the windows is set equal to the switching period of the converter, which could be either fixed or variable.

#### 2.1.3 Extension of WR to perform HIL simulation

Hardware-in-the-Loop (HIL) simulation is a commonly used approach for testing physical hardware and controllers connected to a power system. In this approach, the power system is represented using a real-time simulated model, to which the physical controller is connected. Nevertheless, in some cases, the use of such simulators is either expensive or even infeasible [43]. The latter might be the case when the hardware under the test is located geographically away from the simulation station. System-level testing of protective relays distributed in a large, geographically vast power system and Wide Area Power System Stabilizer (WA-PSS) controllers are such examples [43]. It is suggested in [43] that the classical WR method may be used to tackle the above issue and this thesis follows up on this suggestion. This thesis shows by experimental results that the classical WR methods may at times exhibit non-convergence when one or more of the subsystems are physical hardware. Noise and analog-digital converter errors and other hardware distortions can cause the classical WR methods to diverge in HIL application. Several convergence techniques are proposed and tested in this thesis to modify the classical WR to make it feasible to conduct HIL simulations.

### 2.2 WR Based Circuit Simulation Example

In this section, a buck converter, a typical power electronic circuit, is simulated. The circuit is split into two subsystems and the Gauss-Seidel WR method, as described in Section 1.2.1, is applied to attain the closed loop response of the two subsystems and the converged result is compared to the direct simulation of the original circuit. Additionally, an acceleration technique (Time Windowing) is applied and the results are presented and discussed.

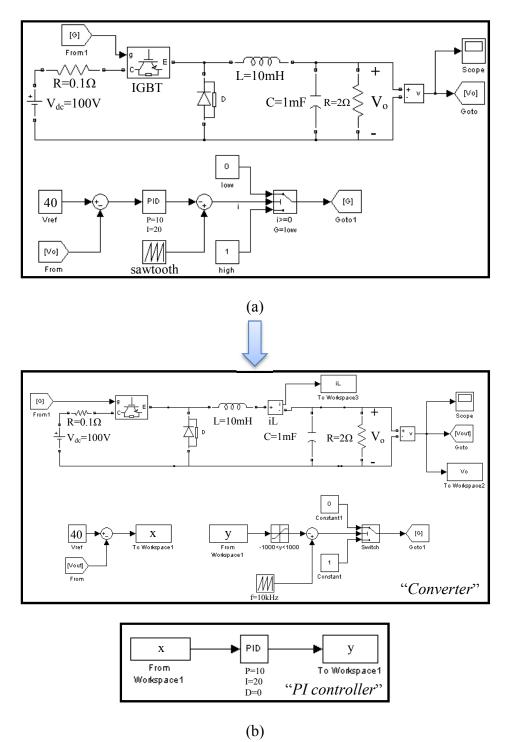

Figure 2-1 displays a pulse width modulated (PWM) buck converter circuit with the control loop consisting of a Proportional-Integral (PI) controller simulated in Matlab/Simulink. The PI controller regulates the output voltage ( $V_o$ ) by changing the duty cycle of the switching pulses applied to the series switch (IGBT). In this way, the difference between the output voltage ( $V_o$ ) and the reference voltage ( $V_{ref}$ ) is fed back into the PI controller as the error signal and the PI controller outputs the firing angle order for the pulse generator. The input voltage source is 100 V and the reference output voltage is 40 V in the example. The frequency of the saw-tooth waveform used to generate the switching pulses is 10 kHz.

The circuit in Figure 2-1(a) is divided into two subsystems labeled "converter" and "PI controller" as shown in Figure 2-1(b). The simulation time-step for both subsystems is set to  $\Delta t = 1 \mu S$ , due to the high switching frequency of 10 kHz in the PWM converter. The total simulation time is T=0.02 seconds.

The voltage error (x), which is the difference between the output voltage and the reference voltage, and the PI controller's output (y) are the WR interface variables. The

Gauss-Seidel WR method for solving the two subsystems of Figure 2-1 is presented in Figure 2-2.

Figure 2-1. (a) A buck converter, (b) partitioning of the system of (a) into two subsystems.

Figure 2-2. Flow chart for WR implementation of Figure 2-1.

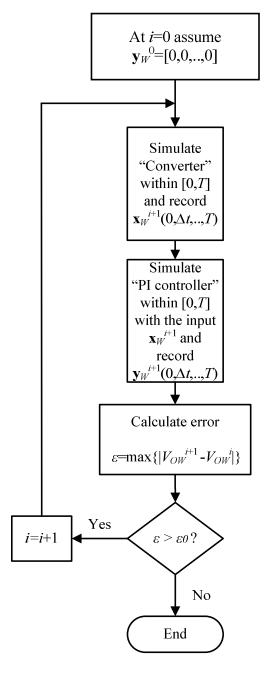

An initial guess waveform of  $\mathbf{y}_w^0$ =[0,0,..,0] is generated for the algorithm. The "converter" subsystem is simulated for T=0.02 seconds and the value of the variable x is sampled and recorded at every simulation time-step. This waveform ( $\mathbf{x}_w$ ) is then fed to the "PI controller" subsystem, which is simulated for 0.02 seconds and the output variable y

is sampled and recorded at every simulation time-step. The convergence criterion is checked by comparing a convergence threshold ( $\varepsilon_0$ ) with the largest value in the waveform difference between the most recently updated output voltage waveform  $\mathbf{V}_{ow}$  and the previous WR iteration, i.e.,  $\varepsilon_0 = \max\{|\mathbf{V}_{OW}^{i+1} - \mathbf{V}_{OW}^i|\}$ . If the error is less than the threshold value, then the simulation is assumed to have converged; otherwise, the next WR iteration is started.

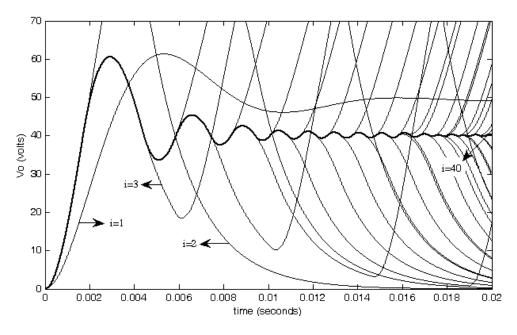

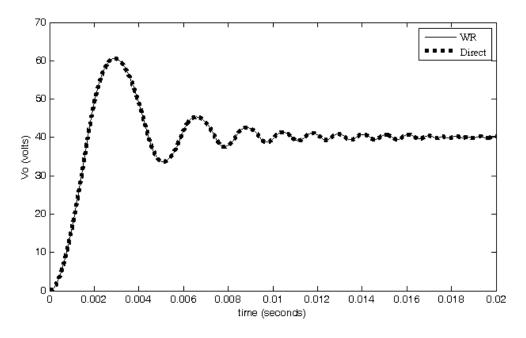

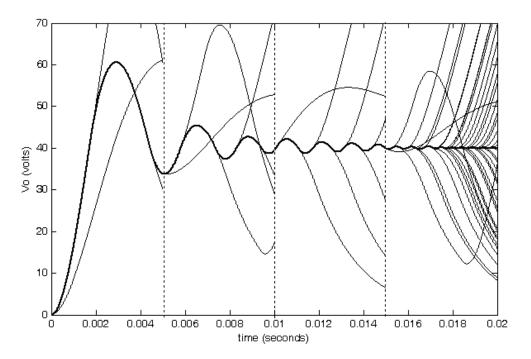

The GS-WR based simulation results for the output voltage of the circuit of Figure 2-1 are presented for each WR iteration in Figure 2-3. The WR converged in 40 iterations with  $\varepsilon_0$ =1. The total GS-WR simulation time was 23 seconds with a 2.8 GHz Intel<sup>®</sup> processor. The converged GS-WR response for the output voltage is compared to the direct simulation results in Figure 2-4. The agreement between the WR simulation result at convergence and the direct simulation result of the circuit shows that the post-convergence WR method results are accurate.

Figure 2-3. Output voltage response in each WR iteration.

Figure 2-4. Comparison of output voltage responses from WR and direct simulation.

#### Application of Time Windowing [25, 28, 33, 34]:

WR convergence is piecewise, i.e. as iterations continue, the initial portion of the waveform begins to converge first; and the later portions of the waveform converge in later iterations, without affecting the earlier converged part. This means that the converged parts of the waveforms are repeated in each WR iteration until the rest of the waveform also converges. Hence, the time spent to repeat the converged parts is wasted. In order to prevent such redundant time consumption, time windowing can be applied [25, 28, 33, 34].

Fixed time-window sizes are applied to the example of Figure 2-1 to investigate the effect of this technique on the total number of iterations to achieve the convergence as well as the total simulation elapsed time. The total simulation time T=0.02 seconds is divided into four windows, each 0.005 seconds duration. WR is iterated within the first

time window, and the convergence criterion is checked till satisfied. The converged result for the output voltage waveform within the first window ( $V_{OW}[0, \Delta t, 2\Delta t,..., 0.005]$ ) is recorded. Additionally, the converged values of the inductor's current and the capacitor's voltage at the last time point of the first window, here,  $\frac{T}{4} = \frac{0.02}{4} = 0.005$  seconds, are recorded to be used at the next time window as new initial conditions. Ultimately, if the waveform relaxation converges in all four time windows, four pieces of converged output voltages are available. This can be seen in Figure 2-5. Note that here both subsystems are purely digitally simulated models and therefore are re-initializable at the start of each time window, i.e. the initial values for the inductor current and the capacitance voltage can be set to desired values. This luxury is not available in the WR-HIL simulation if the physical hardware is not re-initializable, which is often true.

Figure 2-5. Output voltage response for each iteration in case of 4 time windows.

The simulation results show an increase in the total number of iterations. However, there is an overall reduction in the total simulation time. This is because the total simulation time for each window is only 1/4<sup>th</sup> of the time required for an undivided window. The time windowing technique for different number of windows was examined for this example and a summary of results for two cases of four and ten time windows are given in Table 2-1.

Table 2-1. Summary of WR simulation results with time windowing acceleration technique.

| Number of    | Number of  | Total elapsed   |

|--------------|------------|-----------------|

| Time windows | iterations | Time in seconds |

| 1            | 40         | 23.0            |

|              |            |                 |

| 4            | 65         | 18.1            |

| 10           | 89         | 10.5            |

| 10           | 89         | 19.5            |

|              |            |                 |

Table 2-1 shows that the total simulation time for 4 windows is decreased by 21.2 %, even though the total number of iterations is increased by 62.5%, as each iteration covers a smaller interval. This might be acceptable in simulation studies, however for the HIL simulation, it is found that the substantial portion of the elapsed time is the communication between the hardware and the simulator computer in exchanging the recorded waveforms. As a result, increased elapsed time of data communication caused by the increased number of iterations is very likely to more than offset the total time saved by the time windowing technique. It is also deduced from Table 2-1 that further increasing of the number of the time windows may lead to less time savings. In this example, application of four windows was more efficient than ten windows. It was observed that, in order to

achieve convergence is a certain time window, many of the iterations took place at the ending portions of the waveforms. This is acceptable because the convergence improves from left to right in the time axis. With 10 time windows, although the duration of the simulation for each window is shorter than that of 4 time windows, the large number of iterations for each time window needed to satisfy the convergence criterion, especially in the ending portions of the waveforms, led to larger total simulation time than 4 windows. This clearly shows that there is always an optimal number of time windows to achieve the fastest convergence.

As mentioned before, it is possible to reinitialize the energy storage elements in simulation models; however, if the actual hardware under test consists of such memories, then it may be impractical to apply the time windowing technique. So in general, time windowing is not suited for WR-HIL simulation.

### 2.3 WR Based HIL Simulation

#### 2.3.1 WR-HIL method

So far, the classical Waveform Relaxation methods for solving purely simulated computer models were briefly discussed. In this section, the application of WR for conducting HIL simulation is introduced. In this scheme, one of the subsystems in the WR simulation is physical hardware under test (HUT).

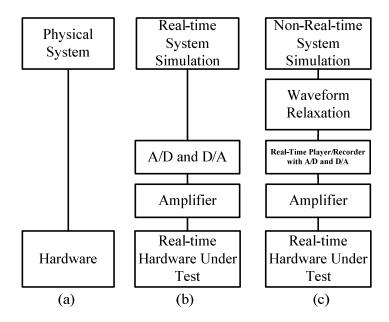

Figure 2-5 shows a general block diagram of the actual hardware connection in a real system and two different simulation approaches. Figure 2-5(a) displays the physical

hardware connected to the actual power system. The hardware may be an analog or digital controller. In this case, the simulation is referred to as controller hardware in the loop (CHIL) simulation. It could also represent actual power hardware such as a transformer, generator, or an HVDC converter interfaced to the simulation using high power amplifiers. In this case the simulation is referred to as power hardware in the loop simulation (PHIL).

Figure 2-5. (a) Hardware connected to the physical system, (b) testing the hardware using real-time simulators, (c) testing hardware using WR-HIL technique.

Figure 2-5(b) shows the traditional HIL simulation methods where the computer model of the physical system is simulated in real-time by means of a real-time digital simulator. The digital output of the simulator is converted to analog using a D/A converter and amplified if necessary to match the voltage/current levels of the equipment under test. Likewise, the feedback signal from the equipment is sampled and converted to digital for sending to the simulator. Thus, the HUT is connected to the simulation system as

though it is connected to the actual physical system if the model of the system is accurate. In this scheme, the exchange of information between the simulator and the HUT occurs in every time-step.

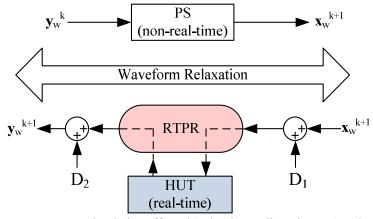

Figure 2-5(c) shows the classical WR-HIL simulation scheme proposed in [43]. The model of the power system is simulated in an off-line Electromagnetic Transient (EMT) simulation program. The WR method (GS-WR) is used to obtain the closed loop response of the non-real-time system simulation and the real-time HUT. The EMT Simulation results are stored and played back in real-time to the HUT, using D/A converters and amplifiers as needed. The HUT response is sampled and recorded using A/D converters and made available to the EMT for the next iteration. This process is continued to convergence. The method is potentially cost-effective as it permits testing of the HUT without the use of a real-time digital simulator. Also note that unlike the case of Figure 2-5(b), the exchange of information only occurs at the end of the simulation time window and not in each time-step; hence, there is no issue with any time-step delay as would be the case in the traditional HIL simulator. It is declared in [43] that the classical WR fails to converge in many practical applications due to noise and other hardware errors when used in HIL simulation. These issues are further discussed in Chapter 4. In Chapter 5, the classical WR is modified to include three new convergence techniques proposed in this thesis in order to successfully implement for the first time, the WR-HIL technique for practical use. The WR-HIL simulation scheme is described in more detail below. Figure 2-6 shows a device connected to a power system (PS).

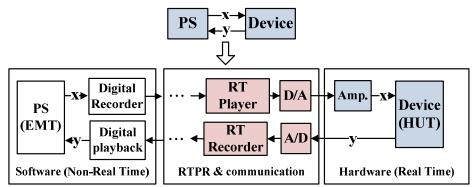

The device is a real piece of hardware and PS is simulated on an off-line EMT program. The output waveforms from PS that form the inputs to the device (HUT) are la-

belled "x", and the HUT inputs to PS are labelled "y". The PS simulation time-step is  $\Delta t_1$ . The HUT may be analog or digital (such as a digital controller or relay), and if it is the latter, its real-time time-step is referred to as  $\Delta t_2$ . Generally, x and y may be multi-dimensional. A voltage or current amplifier should be used with sufficient power rating if the HUT requires input "x" with magnitudes greater than the waveform player's D/A output level.

Figure 2-6. Hardware-in-the-Loop simulation using the WR method.

Figure 2-7. Iterative WR-HIL simulation algorithm.

The classical WR algorithm is described in Figure 2-7. The total simulation time is T seconds. An arbitrary initial (digitized) waveform  $\mathbf{y}_{w}^{0} = \{y^{0}(0), y^{0}(\Delta t_{1}), y^{0}(2\Delta t_{1})...y^{0}(T)\}$  is applied to the PS via the "Digital Playback" unit.

In the first WR iteration, the PS is simulated over T seconds and the waveform at the interface is recorded in the "Digital Recorder" as  $\mathbf{x}_w^1 = \{x^1(0), x^1(\Delta t_1), ..., x^1(T)\}$ . The RTPR receives and plays  $\mathbf{x}_w^1$  in real-time as an analog waveform to the HUT. This would be similar to what the device would see in the field, as its input would be measurements in the system. Depending on the available facilities, the RTPR could interface to high power current or voltage amplifiers to give full levels and then measurement transducers (e.g., real current transformers) to make the environment for the HUT as realistic as possible. The waveform is received by the A/D converter of the HUT and sampled with the HUT time-step  $\Delta t_2$  to yield  $\mathbf{x}_w^{1c} = \{x^{1c}(0), x^{1c}(\Delta t_2), ... x^{1c}(T)\}$ . The RTPR samples and records the HUT's response over the period T to the input  $\mathbf{x}^{1c}$  as  $\mathbf{y}_w^{1c} = \{y^{1c}(0), y^{1c}(\Delta t_2), ... y^{1c}(T)\}$ . Again, this is resampled (with time-step  $\Delta t_1$ ) as  $\mathbf{y}_w^1 = \{y^1(0), y^1(\Delta t_1), ... y^1(T)\}$  and applied to the off-line PS simulation as its input for the next iteration. This process is repeated until a convergence criterion, such as (2.1), is satisfied, where  $\delta$  is the convergence threshold.

$$\max_{t=0, \Delta t_2, \dots, T} \left( \left| \mathbf{y}_w^{k+1}(t) - \mathbf{y}_w^k(t) \right| \right) < \delta$$

(2.1)

#### 2.3.2 Advantages of WR-HIL method

<u>Cost-effective</u>: In WR-HIL, the simulation and hardware subsystems are decoupled and an ordinary personal computer can be used as the simulation processor regardless of