# **DESIGN AND IMPLEMENTATION**

# OF AN ATM

# TRAFFIC GENERATION AND CAPTURE CARD

BY

# JEFF GIESBRECHT

A Thesis Submitted to the Faculty of Graduate Studies in Partial Fulfillment of the Requirements for the Degree of

# MASTER OF SCIENCE

Department of Electrical and Computer Engineering University of Manitoba Winnipeg, Manitoba

(c) January, 2000

# National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-51712-8

# THE UNIVERSITY OF MANITOBA

### FACULTY OF GRADUATE STUDIES \*\*\*\*\* COPYRIGHT PERMISSION PAGE

### Design and Implementation of an ATM Traffic Generation and Capture Card

BY

Jeff Giesbrecht

### A Thesis/Practicum submitted to the Faculty of Graduate Studies of The University

### of Manitoba in partial fulfillment of the requirements of the degree

of

**Master of Science**

# **JEFF GIESBRECHT © 2000**

Permission has been granted to the Library of The University of Manitoba to lend or sell copies of this thesis/practicum, to the National Library of Canada to microfilm this thesis/practicum and to lend or sell copies of the film, and to Dissertations Abstracts International to publish an abstract of this thesis/practicum.

The author reserves other publication rights, and neither this thesis/practicum nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

# Abstract

As a result of recent increases in demand for network bandwidth, it is becoming more important that high-speed telecommunication networks be installed, managed, and used as efficiently as possible. In order for these objectives to be realized, it is essential that network operation be studied and accurate models of its behavior developed. Unfortunately, the data acquired from testing with network equipment is often less than ideal due to the cost and capabilities of test equipment currently available commercially. Testing suffers as a result of the equipment's high cost, inability to generate network traffic with certain types of properties, and the limited amount of traffic which can be recorded for analysis. A network interface card designed specifically to overcome the limitations of commercial test equipment is one solution for improving the results of current network testing. This card would not duplicate all of the capabilities of existing test equipment. Instead, it would only strive to improve the traffic generation capabilities to allow all possible types of network traffic sources to be simulated, extend network traffic capture periods to provide a sufficient amount of data for analysis, and be built at a low-enough cost to be a viable alternative to commercial equipment. This thesis will describe the development of a card designed for generating and capturing ATM network traffic at OC-3 rates.

# Acknowledgements

Several people deserve to be acknowledged for their role in helping to realize a working prototype of the ATM traffic generation and capture card discussed in this thesis. I would like to begin by thanking my advisor, Professor Bob McLeod, and Yair Bourlas for developing the concept of the card. Thanks also go to Hung Nguyen, who designed the card's architecture, as well as to Kent Felske and Dan Reader for their part in getting prototype boards fabricated.

Thanks should also go to the staff at TRLabs. In particular, Dan Erickson and Andy Parker for their help in overcoming the many technical hurdles that were encountered during the card's development and Dr. Jose Rueda for managing the project at TRLabs.

I would also like to acknowledge the assistance provided by TRLabs, Nortel Networks, and the Canadian Microelectronics Corporation in terms of personnel, equipment, and other resources. Finally, I would like to thank my family for their encouragement and support.

# **Table of Contents**

| ABSTRACT                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTS iii                                                                                                                                                                                                                    |

| LIST OF FIGURES                                                                                                                                                                                                                         |

| LIST OF TABLES                                                                                                                                                                                                                          |

| LIST OF ABBREVIATIONS ix                                                                                                                                                                                                                |

| 1 INTRODUCTION                                                                                                                                                                                                                          |

| 2 ASYNCHRONOUS TRANSFER MODE                                                                                                                                                                                                            |

| 2.6 ATM Reference Model.22Physical Layer.22ATM Layer.24ATM Adaptation Layer.25Higher Layers.27Planes in the ATM reference model.28                                                                                                      |

| 3 DESIGN SPECIFICATION.       .29         3.1 Required Features and Functionality       .29         3.2 Host Interface.       .31         3.3 ATM Traffic Stream Representation.       .32                                              |

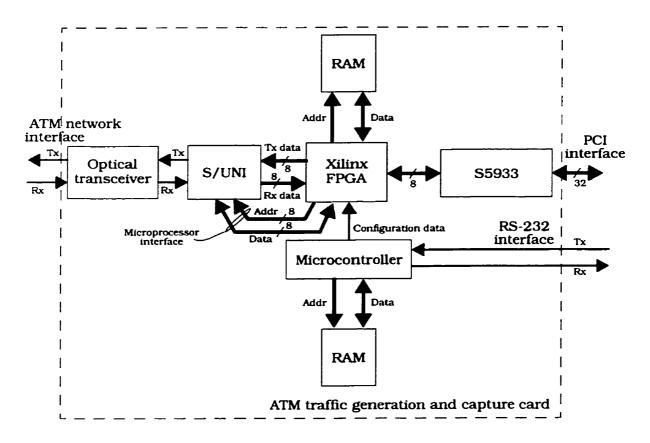

| 4 CARD DESIGN AND IMPLEMENTATION       .34         4.1 Basic Architecture       .34         ATM Network Interface       .35         Host PC Interface       .35         Traffic Stream Translator       .35         Data Flow       .36 |

| 4.2 Component Selection and Complete Architecture                                                                                                                                                                                       |

| Traffic Stream Translator                         | .42 |

|---------------------------------------------------|-----|

| FPGA Configuration                                | .46 |

| Complete Architecture                             | .47 |

| 4.3 System Clock                                  |     |

| 4.4 PCB Design                                    |     |

| 4.4 1 00 Design                                   |     |

| 5 SUPPORT SOFTWARE FOR THE ATM TRAFFIC GENERATION | .52 |

| AND CAPTURE CARD                                  |     |

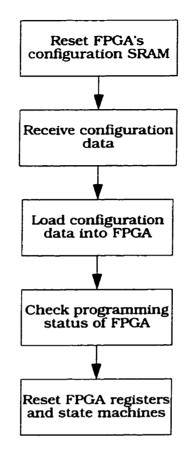

| 5.1 FPGA Configuration                            | 52  |

|                                                   |     |

| 5.2 Host-Card Communication                       |     |

| Transfer Mechanism                                |     |

| Host-Card Relationship                            |     |

| Signalling                                        |     |

| 5.3 Low-Level PCI Communication Functions         |     |

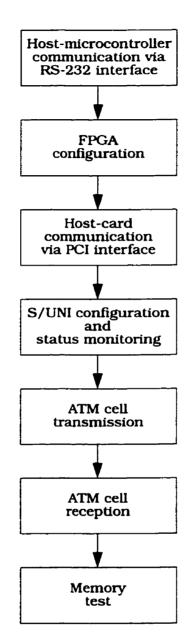

| 5.4 Card Initialization                           |     |

| 5.5 Traffic Stream Transfer                       | .64 |

|                                                   |     |

| 6 TESTING AND VERIFICATION                        |     |

| 6.1 Component Testing                             | .66 |

| FPGA Configuration                                |     |

| PCI Interface.                                    |     |

| S/UNI                                             | .69 |

| RAM                                               |     |

| 6.2 System testing                                | .71 |

| Traffic Capture                                   | .71 |

| Traffic Generation                                | .77 |

|                                                   |     |

| 7 DISCUSSION                                      | .85 |

|                                                   |     |

| 8 RECOMMENDATIONS AND FUTURE WORK                 | .95 |

|                                                   |     |

| 9 CONCLUSION                                      | 00  |

|                                                   |     |

| 10 REFERENCES                                     | 03  |

|                                                   |     |

# List of Figures

| Figure 1.1 | Switch load test                                                                                                |

|------------|-----------------------------------------------------------------------------------------------------------------|

| Figure 1.2 | Capturing network traffic for analysis and characterization5                                                    |

| Figure 1.3 | Applications of the ATM traffic generation and capture card 6                                                   |

| Figure 2.1 | ATM cell structure                                                                                              |

| Figure 2.2 | ATM cell header formats                                                                                         |

| Figure 2.3 | Relationship between VCs, VPs, and transmission paths12                                                         |

| Figure 2.4 | SONET OC-1 frame structure                                                                                      |

| Figure 2.5 | Mapping of ATM cells to an OC-1 frame                                                                           |

| Figure 2.6 | SONET OC-3 frame structure                                                                                      |

| Figure 2.7 | ATM reference model ([13])                                                                                      |

| Figure 2.8 | Sublayers within the physical layer ([13])                                                                      |

| Figure 2.9 | Sublayers within the ATM adaptation layer ([13])                                                                |

| Figure 3.1 | Operating environment of the ATM traffic generation                                                             |

| Figure 4.1 | Basic architecture of the ATM traffic generation and capture 36 card                                            |

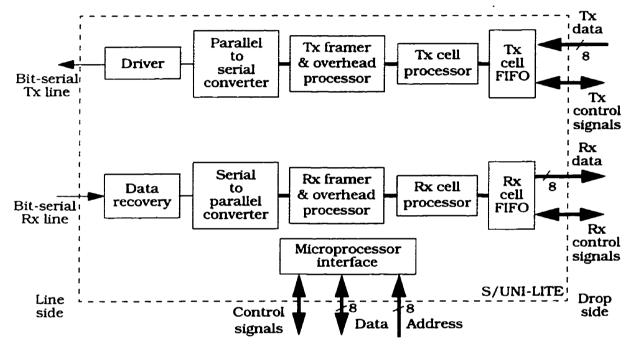

| Figure 4.2 | Internal architecture of the S/UNI-LITE                                                                         |

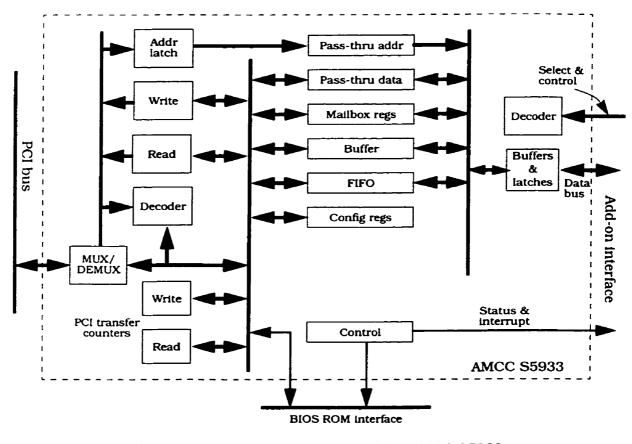

| Figure 4.3 | Internal architecture of the AMCC S593341                                                                       |

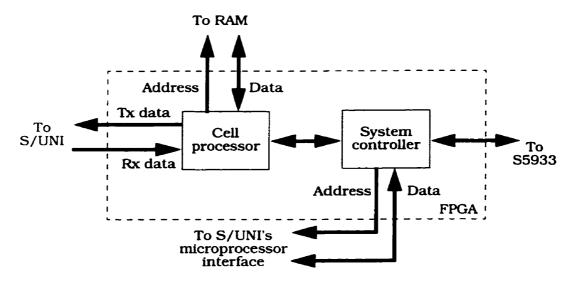

| Figure 4.4 | Internal architecture of the traffic stream translator                                                          |

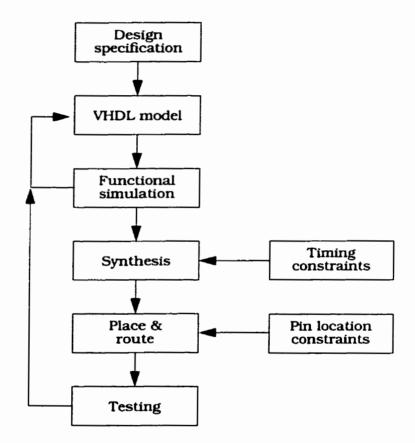

| Figure 4.5 | Traffic stream translator development                                                                           |

| Figure 4.6 | Complete architecture of the ATM traffic generation                                                             |

| Figure 4.7 | Photographs of prototype ATM traffic generation                                                                 |

| Figure 5.1 | Operations performed by microcontroller used for configuring 56 the FPGA for ATM traffic generation and capture |

| Figure 5.2 | Command/response structure                                                                               |

|------------|----------------------------------------------------------------------------------------------------------|

| Figure 6.1 | Component testing flowchart                                                                              |

| Figure 6.2 | Environment used for testing ATM traffic capture                                                         |

| Figure 6.3 | Cell sequences used in testing card's ATM traffic capture                                                |

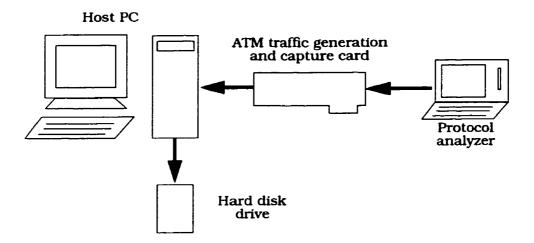

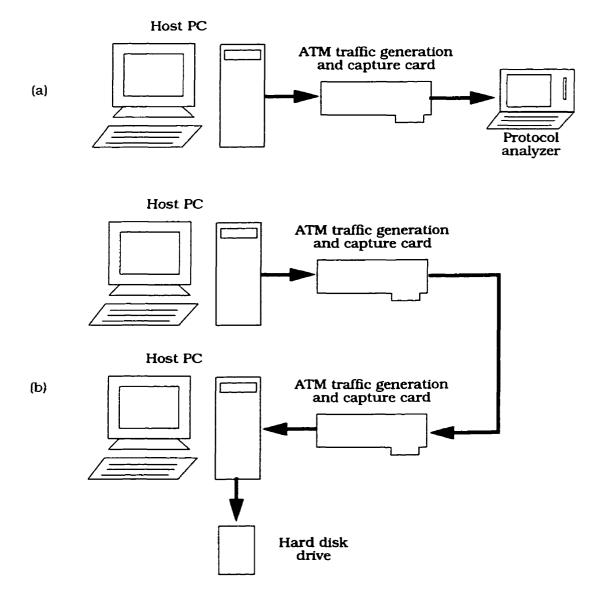

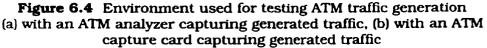

| Figure 6.4 | Environment used for testing ATM traffic generation                                                      |

| Figure 6.5 | Cell sequences used in testing card's ATM traffic generation81 capability                                |

| Figure 6.6 | Preferred approach for performing ATM traffic generation testing84                                       |

| Figure 7.1 | Approximate material cost of ATM traffic generation and                                                  |

| Figure 8.1 | External FIFOs on the ATM traffic generation and capture card98 for buffering data for PCI bus transfers |

# List of Tables

| Table 2.1 | Common SONET/SDH transports                                |

|-----------|------------------------------------------------------------|

| Table 5.1 | Commands defined for host-microcontroller communication 53 |

| Table 5.2 | Responses defined for host-microcontroller communication54 |

| Table 5.3 | Commands defined for host-card communication               |

| Table 5.4 | Responses defined for host-card communication              |

# List of Abbreviations

| AAL    | ATM adaptation layer                                                 |

|--------|----------------------------------------------------------------------|

| ABR    | available bit rate                                                   |

| ANSI   | American National Standards Institute                                |

| API    | application programming interface                                    |

| ASIC   | application-specific integrated circuit                              |

| ATM    | asynchronous transfer mode                                           |

| B-ISDN | broadband-ISDN                                                       |

| CBR    | constant bit rate                                                    |

| CLB    | configurable logic block                                             |

| CLP    | cell loss priority                                                   |

| CS.    | convergence sublayer                                                 |

| FIFO   | first-in, first-out                                                  |

| FPGA   | field-programmable gate array                                        |

| GFC    | generic flow control                                                 |

| HEC    | header error control                                                 |

| 1/0    | input/output                                                         |

| ISDN   | integrated services digital network                                  |

| ITU-T  | International Telecommunications Union, Telecommunications Standard- |

|        | ization Sector                                                       |

| LAN    | local area network                                                   |

| LED    | light-emitting diode                                                 |

| LOH    | line overhead                                                        |

| Mbps   | mega-bits per second                                                 |

| NNI    | network-node interface                                               |

| NRT    | non-real-time                                                        |

| OC     | optical carrier                                                      |

| OS     | operating system                                                     |

| PC     | personal computer                                                    |

| PCB    | printed circuit board                                                |

| PCI    | peripheral component interconnect                                    |

| PHY    | physical layer                                                       |

| PMD    | physical medium dependent                                            |

| POH    | path overhead                                                        |

| PROM   | programmable read-only memory                                        |

| PT     | payload type                                                         |

| PVC    | permanent virtual connection                                         |

| QoS    | quality of service                                                   |

| RAM    | random access memory                                                 |

| RT     | real-time                                                            |

| RTL    | register transfer level                                              |

| SAR    | segmentation and reassembly                                          |

| SDH    | synchronous digital hierarchy                                        |

| SOH    | section overhead                                                     |

| SONET  | synchronous optical network                                          |

| SPE   | synchronous payload envelope        |

|-------|-------------------------------------|

| STM   | synchronous transport module        |

| STS   | synchronous transport signal        |

| SVC   | switched virtual connection         |

| TC    | transmission convergence            |

| ТОН   | transport overhead                  |

| UBR   | unspecified bit rate                |

| UNI   | user-network interface              |

| VBR   | variable bit rate                   |

| VC    | virtual channel                     |

| VCI   | virtual channel identifier          |

| VHDL  | VHSIC hardware description language |

| VHSIC | very high speed integrated circuit  |

| VP    | virtual path                        |

| VPI   | virtual path identifier             |

# Chapter 1 Introduction

# **1.1 Motivation**

In recent months, there has been increased installation and use of high-speed digital telecommunication networks based on technologies such as asynchronous transfer mode (ATM). This additional demand for network resources can be attributed partly to the popularity of applications such as the Internet, video conferencing, distance education, and interactive multimedia as well as to the availability of computer and networking equipment able to support such applications. As a result of this increased need for bandwidth, the importance of efficient installation, use, and management of network resources has never been greater. In order to realize these objectives, a thorough understanding and accurate models of network operation and behavior must be obtained. This can be accomplished through software simulations or by testing with actual network equipment. Testing with physical hardware is the preferred approach for studying network operation as it is inherently more accurate than software models which may not capture all details of the network's behavior.

Unfortunately, there are several problems with the current methods of performing network testing. Rather than attempting to acquire, configure, and operate a variety of common network equipment (e.g. computer terminals, video cameras, telephones,

#### **Chapter 1 - Introduction**

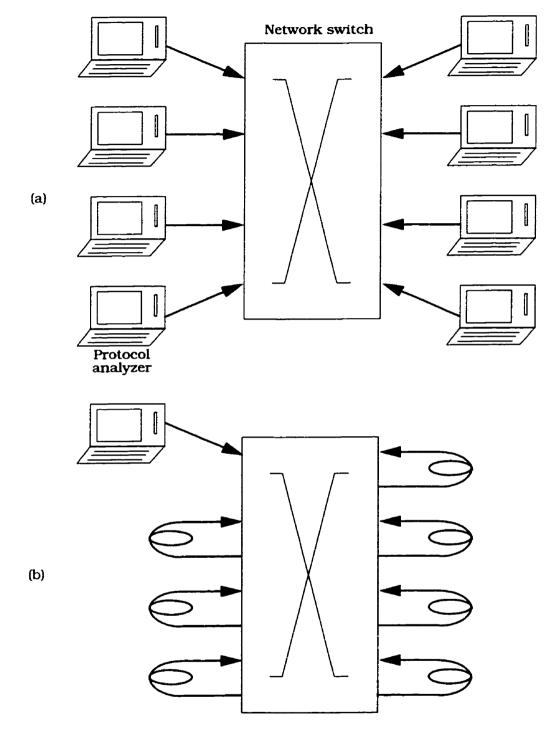

etc.) to provide traffic for testing, what is typically done instead is to configure test equipment such as network protocol analyzers to act as traffic sources for loading the equipment or network being studied. Figure 1.1(a) illustrates such a set-up, where protocol analyzers are being used to drive the inputs of a network switch for the purpose of performing a switch load test. In this test, the behavior of the switch is studied under a variety of realistic as well as some not-so-realistic traffic loading conditions. With protocol analyzers costing hundreds of thousands of dollars each and with switches or networks having many ports to populate, it is often not possible to have each of the inputs of a switch or network receive traffic from its own network analyzer. What is done instead is to have a single protocol analyzer drive one of the inputs to a switch and to supply the other input ports with traffic looped-back from the outputs of the same switch using an arrangement like that shown in Figure 1.1(b). While this approach to providing data traffic to each of the inputs of a switch is certainly less expensive in terms of the amount of test equipment required, it creates an unrealistic test environment as there is no independence in the traffic streams arriving at each of the switch inputs; the properties of the data traffic arriving at one of the switch inputs may be similar to that appearing at other ports. The timing of the traffic stream may also become distorted as it is looped through the switch. Protocol analyzers are also limited in the types of network traffic that they are capable of generating; it is quite difficult to configure a network analyzer to provide a stream of traffic with the long-range dependence and self-similarity properties that have been found to occur in some types of network traffic ([5], [17]).

Figure 1.1 Switch load test: (a) with protocol analyzers driving individual input ports. (b) with input ports connected in loop-back

#### **Chapter 1 - Introduction**

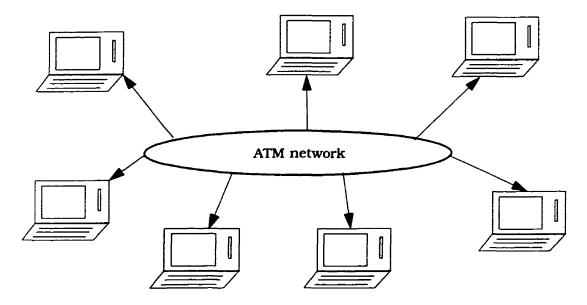

Characterization of network behavior and that of individual traffic sources suffers as a result of the capabilities of currently-available commercial network test equipment. In an environment like that shown in Figure 1.2, protocol analyzers are used to capture traffic leaving the output ports of a network. Traffic recorded at each of the outputs is analyzed in an attempt to characterize properties of the traffic sources and examine how data transfers across a network are affected by various network loading conditions. In order to develop models that can accurately describe and predict network behavior, it is essential that these capture intervals last for durations as long as possible. This is necessary for observing the long-range dependence tendencies which have been found to occur with various types of data traffic in analysis performed over periods of hours, days, and weeks. Commercial test equipment typically<sup>1</sup> permits only a few seconds of OC-3 ATM network traffic to be captured. This is not a sufficient amount of data from which accurate models of network behavior can be developed. Also, the expense of the network analyzers limits the number of ports from which traffic can be captured.

<sup>1.</sup> GN Nettest has recently introduced an option for its ATM network analyzers which would allow approximately 81 million cells, or up to 4 minutes of OC-3 traffic, to be captured. Unfortunately, only a fraction of the bandwidth in an OC-3 stream can be captured.

Figure 1.2 Capturing network traffic for analysis and characterization

A network interface card designed specifically for the purpose of generating and capturing network traffic and available at a low cost is one possible approach to overcoming the limitations of performing network testing and analysis with current commercial test equipment. The intent of this traffic generation and capture card would not be to duplicate the protocol checking and error injection and analysis capabilities of network protocol analyzers. Rather, the card would extend the traffic generation and traffic capture capabilities of these devices. The traffic generation capability would be enhanced to allow a larger variety of network traffic sources to be simulated including those that exhibit properties of self-similarity. Extended traffic capture capabilities would permit network traffic to be logged for periods of time long enough for accurate characterization and modelling of traffic sources and network behavior to be realized. The objective of maintaining a low cost is crucial for making this traffic generation and capture card an economically-viable alternative to using protocol analyzers for generating and capturing network traffic. An inexpensive implementation of the card would

```

Chapter 1 - Introduction

```

permit more input and output ports to be populated when performing switch load tests or capturing network traffic. As Figure 1.3 shows, this traffic generation and capture card could find application in testing typically performed with network protocol analyzers.

Figure 1.3 Applications of the ATM traffic generation and capture card: (a) in a switch load test, (b) for network traffic capture

# **1.2 Report Structure**

The purpose of this thesis is to describe the design and implementation of a traffic generation and capture card developed for testing ATM networks. The next chapter will provide a brief introduction to ATM and background for the remainder of the discussion on the card's development. A discussion of the features and functionality required of the ATM traffic generation and capture card will be presented in Chapter 3. Chapter 4 of this thesis will describe the design and implementation of the generation and capture card while Chapter 5 will discuss the software developed to support the card's operation. Testing of these hardware and software modules will be described in Chapter 6. Chapter 7 will discuss the card's design and Chapter 8 will provide suggestions for future work and development on the card in terms of extensions and improvements. Chapter 9 will conclude the thesis and summarize the results achieved.

The ATM traffic generation and capture card discussed in this thesis was developed in partnership with TR*Labs*. As a result, certain aspects of the card's design and operation are proprietary and cannot be discussed in detail.

# **Chapter 2**

# **Asynchronous Transfer Mode**

Asynchronous transfer mode (ATM) is a high-speed, digital telecommunications technology which was designed for the purpose of integrating a variety of services and applications on a common network. Applications for which ATM was designed to support range from low bandwidth, constant bit rate telephony to bursty, high-bandwidth video and data transfers. ATM is the transport used in the implementation of B-ISDN (broadband-integrated services digital network).

This chapter will describe the basic features and operation of ATM networks. Specifically, the chapter will discuss asynchronous transfer mode as it relates to the ATM traffic generation and capture card implemented in this thesis project.

# 2.1 Supported Traffic Types

ATM is designed to be capable of supporting a variety of network traffic types including:

- traffic generated at constant bit rates and at variable bit rates in large or small bursts

- traffic originating from source applications that require a connection to be established with the destination application prior to the transmission of data and traffic

from applications that transfer data without a connection present

- traffic from applications which are sensitive to any loss of data caused by mis-routing or corruption during the transfer and traffic from applications which are more tolerant to the occurrence of data loss

- traffic from applications that require data to be transferred in real-time with minimal delay and jitter as well as traffic from applications having less-stringent requirements in the delays encountered during the data transfer

Each of these ATM network traffic types can be classified as belonging to one of several service categories defined by the Telecommunications Standardization Sector of the International Telecommunications Union (ITU-T). A constant bit rate (CBR) service class is defined for traffic sources which generate data at fixed bit rates and require data to be transported in real-time but without any error checking, flow control, or other processing applied to the traffic stream. Uncompressed audio and video streams are typical applications which would be classified as belonging to the CBR service category. The variable bit rate (VBR) service class is one which serves applications which generate data traffic at a variable rate. This service class is divided into a real time (RT) sub-class, where stringent requirements are placed on the transfer delay and the amount of jitter experienced, and a non-real time (NRT) sub-class, where the timing of the data transfer is less critical. Compressed video traffic in a video-conferencing environment would fall into the RT-VBR service class while e-mail with a video attachment would belong to the NRT-VBR class. The available bit rate (ABR) service class is defined for bursty traffic sources which have known minimum levels of bandwidth requirements. For the ABR service class, the network guarantees to support this minimum data transfer rate and may provide additional bandwidth, if resources become available. Web browsers are one example of an application belonging to the ABR class. The unspecified bit rate (UBR) service class is for applications which place no minimum bandwidth requirements on

the network, but will accept and utilize whatever level of bandwidth that the network is able to provide at any given time. File transfers and e-mail messages fall into this service class.

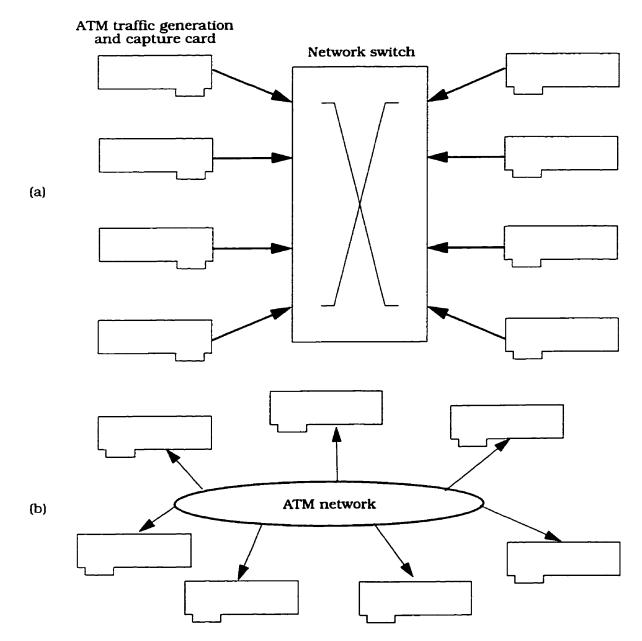

# 2.2 Cell Structure

All data is transferred across an ATM network in the form of a fixed-length block called a cell. As Figure 2.1 illustrates, ATM cells are 53 bytes in size and are comprised of a 5-byte header and a 48-byte payload. The header portion of a cell contains the information needed to ensure that the cell is correctly transferred across a network from a source node to one or more destinations. The payload portion of a cell contains the data that is to be transferred. The cell payload can contain user data, control signalling, or operation and administration information.

Figure 2.1 ATM cell structure

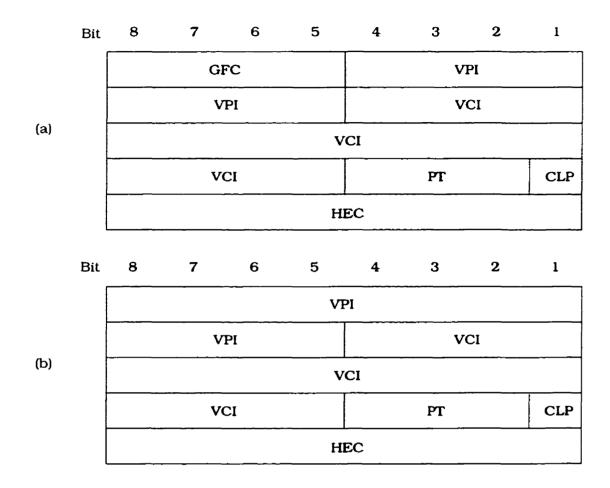

There are two header formats defined for ATM cells. The user-network interface (UNI) header structure is the format used for cells transferred between a user application and an ATM network while the network-node interface (NNI) header format is used for cells transferred between nodes within the network. The UNI and NNI header formats, shown in Figure 2.2, differ only in the generic flow control and virtual path identifier fields.

The 4-bit generic flow control (GFC) field is present only in the UNI cell header format. This field was intended to implement flow control between a user and a network.

but its use is presently not defined in ATM standards ([3]). As a result, the GFC field in a UNI cell header is typically set to zero and ignored by ATM switches in a network.

Figure 2.2 ATM cell header formats: (a) user-network interface style, (b) network-node interface style

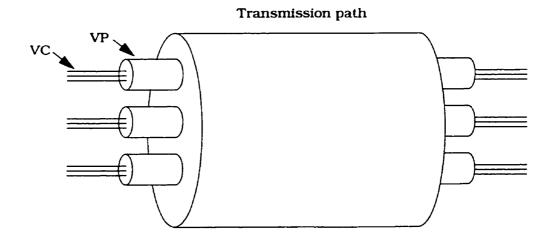

The virtual path identifier (VPI) and virtual channel identifier (VCI) fields contain the address information necessary for switching a cell during its transfer across an ATM network. The VPI field is 8 bits in length in the UNI header format and 12 bits in the NNI header format. The VCI field is 16 bits long in both the UNI and NNI header formats. The VCI field allows for differentiation of cells from a number of virtual channels (VCs) sent over a common virtual path (VP). The VPI field identifies a particular VP in a transmission path. Figure 2.3 illustrates the relationship between virtual channels, virtual paths, and transmission paths.

Figure 2.3 Relationship between VCs, VPs, and transmission paths

The 3-bit payload type (PT) field is used to describe the type of data being carried in the cell payload. This field indicates whether the payload is carrying user data or network management information. When the payload contains user data, the PT field can also indicate whether a cell has experienced congestion in its transfer across a network.

The cell loss priority (CLP) field is a single bit used to indicate the priority of an ATM cell. When traffic congestion occurs in a network, ATM switches in the network can drop cells in an attempt to reduce the level of congestion. The CLP bit allows a network switch to differentiate between the two priority levels assigned to cells; low priority cells are discarded by a switch before those with a high priority are dropped.

The last field in the cell header is an 8-bit header error control (HEC). The HEC field is a checksum applied to the first four bytes of the cell header in order to prevent the mis-routing of cells with errored headers. This field makes it possible to correct all single-bit errors and detect most multi-bit errors that can occur in the cell header. The HEC is not applied to the cell payload.

Cell transmission begins with the most-significant bit of the first byte of the cell header and ends with the least-significant bit of the last (or forty-eighth) byte in the cell payload.

# 2.3 Connections

ATM networks are connection-oriented. Before data can be transferred between a source and a destination, a connection with the network must first be established. A connection is a set of links which define the path across the network that all cells transferred between these two entities will follow. Connection establishment reserves network resources for data transfer between a particular source and destination or destinations, in the event that data is to be broadcast. As a result of the connection-oriented nature of ATM networks, cells will be received at the destination node in the same order that they were sent by the source, provided that no cells are discarded or mis-routed while in transit across the network.

A connection with an ATM network can be established as one of two types: as a permanent virtual connection or as a switched virtual connection. A permanent virtual connection (PVC) is a connection that is created and released manually by the network provider's personnel. A switched virtual connection (SVC), on the other hand, is a connection which is created and released through meta-signalling exchanged between network switches and equipment at the source and destination nodes. SVCs are established without human intervention by hardware and/or software within the network switches and user equipment. SVCs are dynamically established and released, typically existing only for the duration that data needs to be transferred, while PVCs tend to be maintained for longer periods before and after a data transfer is completed. SVCs have the advantage of making more-efficient usage of network resources than

PVCs.

Regardless of whether a connection is established as an SVC or as a PVC, the connection set up procedure involves negotiation between a data source and the ATM network to which it is attached. During connection set up, the data source indicates to the network its quality of service (QoS) requirements for the connection using parameters which include its tolerance for cell loss, delay in the cell transfer, and variation in the cell transfer delay. The data source also specifies the peak, average (sustained), and minimum rates that it requires for cells being transferred across the network. The network evaluates these requirements and determines whether or not it has sufficient resources to be able to meet the source's goS requirements. The connection request is accepted only if the network is able to support the source's QoS requirements for the connection and if the QoS requirements of existing connections are not compromised as a result of accepting the connection. The request is refused if either of these two conditions is not satisfied. In the event that a network refuses a source's connection request, the source can resubmit its request if it is willing to accept a lower GoS for the connection. The values of the QoS parameters that finally get agreed upon by the two entities become what is known as the traffic contract.

Once a connection has been established, the data source is informed of the values that it must assign to the VPI and VCI fields of all data cells that it sends to the network. The specific values of the VPI and VCI fields allow cells associated with one connection to be distinguished from cells sent on other connections by other data sources.

When a data source begins transmitting cells on an established connection, it is the responsibility of the switches in the network to police the traffic on the connection through a mechanism known as usage parameter control. This policing of a source is necessary to ensure that it does not violate the terms agreed upon in the traffic contract, ultimately causing network congestion or compromising the QoS of other connections. Cells which are found to be in violation of the traffic contract can be marked to be discarded immediately or at some later point in time.

# 2.4 Payload Formatting

As discussed earlier, data is transferred across an ATM network in the payload of cells. The sending application must therefore format the data that it wishes to transfer to fit within the cell payload. The application at the destination node must extract the data from the payload of the cells it receives and reformat the data to meet its usage requirements. Formatting of the data being transferred to the payload of an ATM cell involves more than just simply chopping the data into blocks of 48 bytes. In order to meet the QoS requirements of each of the service classes, additional control information is inserted into the cell payload along with the data. The control information that is added can include:

- a payload sequence number

- an indication of the relative position of the payload within the frame from which it originated

- the length of the frame from which the cell payload was extracted

- an identifier for differentiating between multiple sessions multiplexed over a common connection

- error correction/detection applied to the entire cell payload or only the control information included in the payload

The specific type, format, and amount of control information inserted in the payload is dependent upon the service class of the connection

### 2.5 Cell Transmission

ATM transfers cells across a network asynchronously, as cells become available from source applications. Rather than assigning a dedicated time slot during which cells from a particular connection are to be transferred, cells are transmitted to an ATM network as they are created by a source. Cells on different connections are multiplexed to form a single stream of cells which are transferred across a network. The order that cells from different connections are multiplexed into a single stream is dependent upon their order of arrival and, possibly, the QoS requirements of the individual connections involved. This asynchronous approach to cell transfer makes most-optimal use of network resources by allowing bandwidth which is freed-up by a source which temporarily does not have any data to send to be shared by other sources which have an immediate need for data to be transferred. In the absence of cells carrying user or control information (also referred to as assigned cells), idle/unassigned cells are inserted into the stream transferred to the network as a means of cell rate decoupling.

At switches within an ATM network, cells arriving on an incoming link are queued to allow the VPI and VCI fields in the header to be examined. These fields are decoded to select the switch's output port to which the cell should be routed. ATM switches may also examine the HEC field to detect and correct errors in the cell headers, translate the VPI and VCI fields for transfer further across the network, or drop cells in an attempt to control network congestion. Cells leaving an output port of a switch are multiplexed to form a single cell stream to be transferred to other nodes in the network.

There are a number of physical transport mechanisms which can be used to transfer ATM cells across the transmission paths between nodes in an ATM network. Cells can be transferred using framed transports such as the synchronous optical network (SONET) and synchronous digital hierarchy (SDH) or even in their raw form with-

out any additional transport overhead. Some of the physical transports for transferring ATM cells, as defined by organizations such as the ATM Forum, the ITU-T, and the American National Standards Institute (ANSI), include:

- 44.736 Mbps DS-3/T-3 transport over coaxial cable

- 51.84 Mbps SONET STS-1 over category 3 unshielded twister pair

- a 100 Mbps data rate over a fiber optic medium using the FDDI/TAXI (fiber distribute data interface/transparent asynchronous exchange interface) architecture

- 155.52 Mbps SONET STS-3c/SDH STM-1 over fiber optic cable or coaxial cable

- a 155.52 Mbps data rate over fiber or category 5 unshielded twisted pair using the Fiber Channel architecture

- 622.08 Mbps SONET STS-12c/SDH STM-4 over a fiber optic medium

- and a number of low-speed transports which provide data transfer rates of a few mega-bits per second over shielded and unshielded twisted pair and coaxial cable

At the output port of a source node, ATM cells are mapped to one of these transports for transfer across the physical links between nodes in a network. At switches in the network, cells are extracted from the physical transport, are switched and multiplexed with cells from other sources, and are mapped again to a physical transport for transfer further through the network. When the destination node is reached, the cells are extracted from the transport and sent to the receiving application.

One physical transport that is commonly used, and the one that will be important in this thesis, is the SONET hierarchy. The remainder of this section will describe the basics of this transport mechanism.

### SONET

The SONET hierarchy is an optical communications interface standard maintained by ANSI. It is a framed transport which allows direct, synchronous multiplexing

of traffic streams to be used to realize high data transfer rates. In addition to being a transport for data, SONET provides network management and maintenance capabilities.

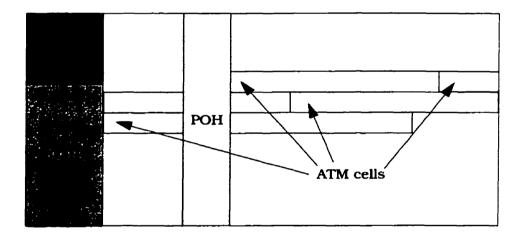

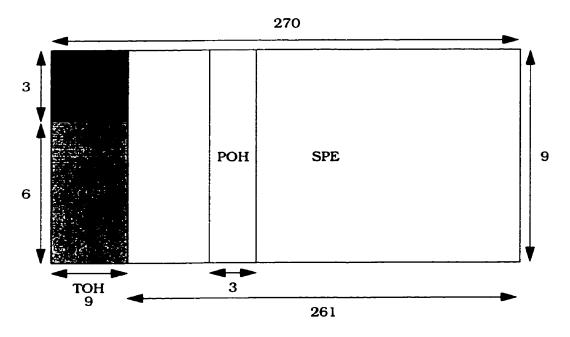

The basic structure used for data transfer in the SONET hierarchy is the level 1 optical carrier (OC-1) frame as shown in Figure 2.4. The OC-1 frame is 9 rows by 90 columns in size, with the intersection of a row and a column representing one byte of data. Three columns in the frame contain transport overhead (TOH) consisting of 9 bytes of section overhead (SOH) and 18 bytes of line overhead (LOH). The remaining 87 columns in the frame form the synchronous payload envelope (SPE). The SPE contains one column of path overhead (POH) data and 86 columns of user information in which services such as ATM are mapped. The section, line, and path overhead together provide such transport management and diagnostic information as frame alignment detection, performance monitoring, fault isolation, a pointer to the start of the SPE in the frame, and a voice channel for network maintenance personnel. The equivalent electrical version of an OC-1 frame is referred to as a level 1 synchronous transport signal (STS-1).

SONET frames are transferred beginning with the byte at the left-most column and top-most row of the frame, proceeding rightward across the row towards the last column, and continuing in a similar manner with the second and subsequent rows until all the bytes in the frame have been transmitted; the cycle begins again with the next frame. Frames at an OC-1 rate, as well as at all other optical carrier levels, are generated and transmitted across a link at a rate of 8000 frames per second. This frame size and transmission rate allows a data transfer rate of 51.84 Mbps to be realized. Of this 51.84 Mbps, 49.536 Mbps is available for transferring user information.

As mentioned previously, the user information that is to be transferred is mapped into the SPE portion of a SONET frame. In the case where SONET is used as the transport for ATM, cells are mapped head to tail into the SPE in a manner like that

shown in Figure 2.5. The SPE can begin at any location in the payload of a frame and can, consequently, extend across the boundary of one frame and into a second frame. A pointer in the line overhead part of the transport overhead indicates where the SPE begins and facilitates the demapping of the payload from the frame when it reaches the destination node in a network.

Figure 2.4 SONET OC-1 frame structure

Data transfer rates higher than 50 Mbps are achieved by multiplexing a number of OC-1 signals together to form a new signal in the SONET transport hierarchy. An OCn signal is created when n OC-1 signals are multiplexed, with the OC-n frame being ntimes larger and having n times the data transfer capacity of an OC-1 signal. In the OCn frame, the SOH, LOH, and POH sections of the frame also increase n times in size from the OC-1 frame. As an example, Figure 2.6 illustrates the OC-3 frame that is formed when three OC-1 frames are multiplexed; an OC-3 frame is 9 rows by 270 columns in size and contains 9 columns of TOH and 3 columns of POH. In general, an OC-m signal

is formed when k OC-l signals are multiplexed, where k, l, and m are integers and m is the product of k and l. An OC-m signal is k times larger and has k times the data transfer rate of an OC-l signal. The SONET hierarchy allows signals which have already been multiplexed to be multiplexed further to achieve yet higher data transfer rates. Four OC-3 signals, for example, can be multiplexed to create an OC-l2 signal; this is also equivalent to multiplexing l2 OC-l signals. Lower-level signals in a multiplexed stream can be recovered through demultiplexing of the higher-level signal. Table 2.1 lists some of the transport signals defined in the SONET hierarchy, the resulting data transfer rates, and the equivalent level of the synchronous transport module (STM) signal in the synchronous digital hierarchy (SDH).

Figure 2.5 Mapping of ATM cells to an OC-1 frame

Higher-level signals in the SONET hierarchy are formed through synchronous, byte-interleaved multiplexing of lower-level signals. Using the notation from the previous paragraph, an OC-m signal is created by taking a single byte sequentially from each of the k OC-l frames. This creates an arrangement where the first group of k bytes in the OC-m frame is the first byte of each of the k OC-l frames, the second group of k bytes in the OC-m frame is the second byte of each of the k OC-l frames, etc. As the multiplexing is synchronous, bytes which were adjacent to each other in the lower-level OC-l signal are always only k bytes apart in the OC-m signal.

Figure 2.6 SONET OC-3 frame structure

The SONET hierarchy also defines transport signals which allow higher data transfer rates to be realized without using the byte-interleaved scheme of multiplexing lower-level signals described previously. These signals are differentiated from the optical carrier signals described earlier by appending a letter 'c' designator to the optical carrier level value (OC-3c, for example). OC-nc signals have a frame size and data transfer rate which is identical to that of an OC-n signal. The frame structure of an OC-nc signal is identical to that of an OC-n with the exception of the POH portion of the frame; the POH in an OC-n signal is n columns wide, but is only a single column wide in an OC-nc frame. Data is mapped to the SPE of OC-nc signal in a manner similar to what was described previously for an OC-1 signal. Because an OC-nc signal is not created from multiplexing of lower-level signals, a byte-interleaved multiplexing scheme is not used to

map data into the SPE of these frames. Consequently, an OC-nc signal cannot be demultiplexed.

| Data transfer<br>rate<br>(Mbps) | SONET optical carrier | SONET<br>electrical<br>carrier | SDH<br>carrier |

|---------------------------------|-----------------------|--------------------------------|----------------|

| 51.84                           | OC-1                  | STS-1                          | -              |

| 155.52                          | OC-3                  | STS-3                          | STM-1          |

| 622.08                          | OC-12                 | STS-12                         | STM-4          |

| 2488.32                         | OC-48                 | STS-48                         | STM-16         |

| 9953.28                         | OC-192                | STS-192                        | STM-64         |

Table 2.1 Common SONET/SDH transports

# 2.6 ATM Reference Model

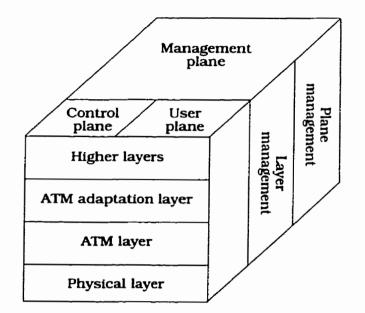

Figure 2.7 shows the protocol reference model defined for ATM. This section will briefly describe the function of each of the layers and planes in this reference model and relate them to the discussion earlier in the chapter.

### Physical Layer

The lowest layer in the ATM protocol reference model is the physical layer (PHY). The purpose of this layer is to ensure accurate transmission and reception of ATM cells across the links that connect nodes in an ATM network. It serves as an interface between the physical transmission medium used for data transfer between network nodes and the next-higher layer in the reference model, the ATM layer. The physical layer is further sub-divided into two sublayers, the transmission convergence (TC) and physical medium dependent (PMD) sublayers, as illustrated in Figure 2.8.

Figure 2.7 ATM reference model ([13])

The transmission convergence sublayer looks after the mapping and demapping of ATM cells to and from one of the physical transport mechanisms listed earlier. The specific functions performed by the TC sublayer include transmission frame generation and recovery, transmission frame adaptation, cell delineation, cell rate decoupling, and HEC field generation and verification. At the source node in an ATM network, the TC sublayer calculates the value inserted in a cell's HEC field, creates the frame used by the physical transport mechanism, and maps cells to the data payload portion of the frame. The TC sublayer also inserts idle cells into the frame's payload as a means of cell rate decoupling in the event that the total data transfer requirements are less than the transport mechanism's data transfer capacity. The TC sublayer at the destination node processes the received data stream to locate the start of the transport mechanism frame structure as well as the beginning of ATM cells so that they can be demapped from the frame's payload. The TC sublayer at the destination node discards idle cells that were

inserted at the source for cell rate decoupling. Also at the destination, the TC sublayer recalculates a cell's HEC and compares it to the HEC field that was received in the header for the purposing of detecting, and possibly correcting, errors that have occurred in the cell header. The TC sublayer typically does not pass cells with errored headers (that cannot be corrected) up to the ATM layer.

Transmission convergence sublayer

Physical medium dependent sublayer

Figure 2.8 Sublayers within the physical layer ([13])

The physical medium dependent sublayer of the physical layer handles the coding of transmission frames for the purpose of transmission across links in a network. At a source node, the PMD sublayer converts individual bits in the transmission frame received from the TC sublayer into electrical or optical signals (depending on the transmission medium used) with the appropriate voltage or light intensity levels and bit timing. At a destination node, the PMD sublayer forms the transmission frame from the signal levels received on the transmission media.

### **ATM Layer**

The next-higher layer in the reference model is the ATM layer. This layer interfaces with the physical layer and the ATM adaptation layer. The ATM layer exchanges ATM cells with the physical layer, passing down ATM cells that it wishes to transmit to the physical layer and receiving cells that the physical layer has demapped from the physical transport mechanism. The payload portion of a cell is passed between the ATM layer and the ATM adaptation layer.

Some of the responsibilities of the ATM layer in the protocol reference model

#### Chapter 2 - Asynchronous Transfer Mode

include:

- attaching a cell header to payload information received from the ATM adaptation layer at the source node where the cell begins it transfer through network

- removal of the header from the cell and passing of the payload up to the ATM adaptation layer when the cell reaches its destination

- multiplexing and demultiplexing of cells from different traffic streams

- switching and address (VPI/VCI) translation of cells at intermediate nodes in a network

- cell rate decoupling through insertion and removal of idle/unassigned cells in the traffic stream

- connection establishment and release using connection admission control procedures

- processing of a header's CLP bit for the purpose of congestion control in a network

- traffic policing (usage parameter control), shaping, and accounting (for billing purposes) of data originating from individual sources

- processing of cell headers to identify reserved meta-signalling or network management cells

- all cell processing and management tasks necessary for proper network operation and for meeting a variety of QoS requirements

# **ATM Adaptation Layer**

The layer above the ATM layer in the reference model is the ATM adaptation layer (AAL). The AAL acts as an interface between the ATM layer and higher layers in the model. This layer operates to map the services required by user applications to the services provided by the ATM layer. In addition to translating between the data format used by sending and receiving applications and the ATM cell structure which is used for transferring data across a network, the AAL is also responsible for the overhead informa-

#### **Chapter 2 - Asynchronous Transfer Mode**

tion included in the payload for the purpose of meeting applications' GoS requirements. This overhead serves as a mechanism for handling variations in cell transfer delays, the occurrence of transfer errors, the mis-insertion or loss of cells during transport, and the recovery of source timing information at destination nodes. The AAL deals with ATM cell payloads only and does not have access to the cell headers.

A number of types of ATM adaptation layers are defined to meet the differing requirements of each of the available service classes. ATM adaptation layer type 1 (AAL-1) is defined for the CBR service class which requires data generated at a constant bit rate to be transferred in real-time and with a connection to be established. Included with the user data in the payload of AAL-1 cells are fields for a sequence number and a checksum for detecting errors in the sequence number. AAL-2 is for the NRT-VBR service class which transfers variable bit rate data in real-time with a connection present. This AAL includes sequence number, information type identifier, and length indication fields with the user data as well as a field which serves as a checksum over the entire cell payload. AAL-3/4 is for connection-oriented or connectionless applications which require data, generated a variable bit rate, to be transferred without loss, but not necessarily in real-time. This AAL includes a length field, frame sequence numbers, a location identifier (for the position of the cell in the frame from which it originated), a multiplexing identifier field, and an indication of the type of data in the payload of the cell. Like AAL-3/4, AAL-5 is for connection-oriented or connectionless applications. It attaches a field for the length of frame from which the cell was extracted and a checksum. ITU-T specifications ([14]) describe the operation and function of each of the ATM adaptation layers in more detail.

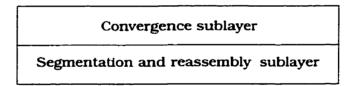

Each of the AAL types share a common sublayer structure: the AAL layer is subdivided into the convergence sublayer (CS) and the segmentation and reassembly (SAR)

#### Chapter 2 - Asynchronous Transfer Mode

sublayer as shown in Figure 2.9. The function of the convergence sublayer is to interface with the sending and receiving applications and to provide the mechanism for supporting each of the defined service classes. This sublayer attaches the AAL-type-specific overhead information to the application data at a source node and removes and processes this overhead at a destination node. The purpose of the SAR sublayer is to do the transformation between the sending and receiving applications' data format and the 48byte ATM cell payload. At a source node, the SAR sublayer segments the data (received from the convergence sublayer above) into 48-byte blocks to fit within the cell payload. The SAR sublayer at a destination node reassembles the original data structure by joining together each of the cell payloads received from the network, ultimately passing the recovered data up to the CS.

Figure 2.9 Sublayers within the ATM adaptation layer ([13])

# Higher Layers

The higher layers in the ATM reference model represent the sending and receiving applications which use the network to transfer data. Among the applications that can be included in this layer are file transfer software, audio and video teleconferencing tools, and world wide web servers and browsers. At a source node, the sending application passes the data that it wishes to transfer across the network to the AAL. When the data has reached the destination node, the receiving application gets the data from the network via the AAL.

## Planes in the ATM reference model

The user plane in the ATM reference model handles the transfer of application data from source to destination across a network. The tasks performed by the user plane include data transport, flow and congestion control, and error detection and correction functions.

The purpose of the control plane in the ATM reference model is to support the services that the user plane provides. The control plane looks after connection set up through call admission control, connection tear-down, addressing and switching of data during transfer, traffic policing, and other connection management tasks.

The management plane is concerned with the management of resources and the performance of the network. This plane is subdivided into layer and plane management functions. Layer management is concerned with the operation, administration, and performance of each of the layers in the reference model individually. Plane management looks after the operation and management of the entire system including intercommunication between individual layers and planes in the ATM reference model.

As discussed in the introduction to this thesis, the purpose of the ATM traffic generation and capture card was to provide an economical means of generating and capturing ATM traffic in order to improve the approach currently used for studying network operation and behavior as well as the characterization of network traffic. This chapter will describe the features and functionality that were required for the implementation of the ATM traffic generation and capture card.

# 3.1 Required Features and Functionality

The design specification for the ATM traffic generation and capture card required that the card be capable of performing the complementary traffic processing operations of ATM traffic generation and ATM traffic capture. Each of these two traffic processing operations was to be performed by a single network interface card. Under traffic generation, the card was to act as a source of network traffic by providing a stream of ATM cells. This stream was to be used to drive the input of a network (or a switch) so that the behavior of the network could be studied under a range of traffic loading conditions. Among the types of network traffic that the card had to be capable of generating were those streams that exhibited characteristics of self-similarity and long range depen-

dence. When capturing traffic, the card was required to record the timing information of an ATM traffic stream that it received from an output port of a switch or a node in a network. The network traffic information that the card captured was to be used for developing models of network operation and network traffic behavior. Although the design requirements specified that the card be capable of both ATM traffic generation and capture, the card was not required to perform both traffic processing operations simultaneously. The card was also not required to perform any connection establishment tasks: rather, it was to generate and capture ATM traffic on connections which had been created ahead of time as PVCs.

The design requirement suggested the duration of the traffic processing interval for which the card had to be capable of operating. In order to improve upon the accuracy of the models that are developed to describe network behavior and to characterize network traffic, the ATM traffic generation and capture card implemented in this project had to extend the traffic processing intervals of conventional network test equipment. This was necessary so that the rare events which occur infrequently during network operation, but which are essential for proper network modelling, could be specified in the generated ATM traffic streams and could be recorded in the captured traffic streams. A target traffic processing interval of a few hours in length was recommended by the design specification.

The ATM traffic generation and capture card's physical layer interface to an ATM network was also determined by the design specification. The card had to process cells using the UNI cell header format and was required to interface to an ATM network through a 155.52 Mbps OC-3c physical transport.

Cost was another aspect of the ATM traffic generation and capture card's implementation that was defined in the design specification. In order for the card to be a via-

ble alternative to testing with commercial network test equipment, the design specification required that the card be built at a low cost. A target cost of a few thousand dollars was placed on the hardware needed for the card's fabrication.

In order to achieve a low hardware cost, the design specification recommended that commercially-available components be used whenever possible in the design of the ATM traffic generation and capture card. This suggestion was made in an attempt to avoid the high fabrication costs associated with the development of an application-specific integrated circuit (ASIC). In the event that no commercial part was available to realize a particular operation, the specification recommended that a field-programmable gate array (FPGA) be used to implement the required functionality.

# 3.2 Host Interface

The design specification required that the ATM traffic generation and capture card have an interface to a host computer. This interface was required for several purposes. First, it was necessary to allow a host to configure and control the operation of the card. The host had to be able to select whether the card was to perform traffic generation or traffic capture. The host also had to be able to perform any initialization or run-time management tasks as necessary for either traffic processing operation. The interface was required to transfer the ATM traffic stream between the card and the host. During traffic generation, the interface was to be used by the host to supply the card with the ATM traffic stream to "generate" to the network. This traffic stream could be one which the host creates in real time or one which it has read from a pre-computed traffic log file stored on disk. When capturing traffic, the interface was needed by the host to read the ATM traffic stream which the card has received from a network. This allows the host to analyze the traffic stream as it received from the network or to store to

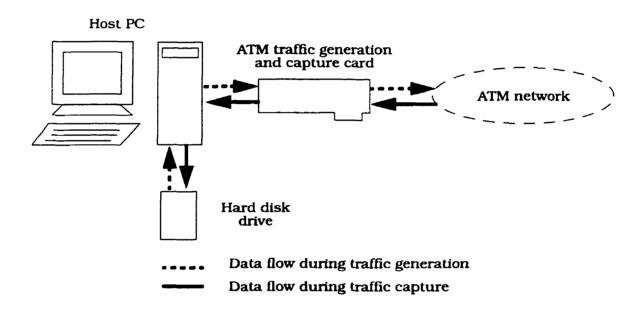

disk for processing off-line. Figure 3.1 illustrates the operating environment of the ATM traffic generation and capture card and the orientation of the ATM traffic stream flow during each of its two modes of operation.

In keeping with the requirement that the ATM traffic generation and capture card be a low-cost alternative to conventional network test equipment, the design specification stipulated that an IBM-compatible personal computer (PC) be employed as a host for supervising the operation of the card. A PC was selected as the host because of its popularity and relatively low cost.

Figure 3.1 Operating environment of the ATM traffic generation and capture card

# 3.3 ATM Traffic Stream Representation

As a result of the combined requirements for long traffic generation and capture periods and the high bandwidth of the traffic generation and capture card's ATM network interface, large amounts of data storage space would have been needed for storing raw ATM cells in the traffic log files. For instance, capturing one hour of ATM network traffic at an OC-3c rate requires approximately 67 giga-bytes of disk space on a host PC,

counting storage of the ATM cells only and neglecting any storage overhead that may be needed. A similar amount of storage space would be required for the ATM traffic stream that the card is to supply to the network during traffic generation.

In order to realize the required network transfer rates and traffic processing intervals without any specialized and expensive hardware, it was necessary to apply some of type of compression to the ATM traffic streams. The design specification defined a traffic encoding scheme<sup>2</sup> that made substantial reductions to the amount of storage space required for representing the ATM traffic streams. This encoding scheme recorded the timing data of an ATM traffic stream while maintaining sufficient information such that an encoded traffic stream could be expanded into a stream of ATM cells. This can then be sent to a network during traffic generation and a captured stream of ATM cells could be characterized once encoded. The specific variation of the encoding implemented by the card reduced the storage requirements for the ATM traffic streams to less than one giga-byte per hour.

The design specification required that the ATM traffic stream translation tasks be performed by the ATM traffic generation and capture card rather than by the host PC supervising the card's operation. This requirement was made in order to reduce the amount of data transferred between the host and the card and the amount of ATM traffic stream processing performed by a host during traffic generation or capture. By localizing the traffic stream translation to the card, a host might then be capable of supporting the concurrent operation of a number of cards; a host may be able to supply encoded ATM traffic streams to cards configured for traffic generation and/or to receive encoded traffic streams from cards capturing ATM traffic.

<sup>2.</sup> This encoding scheme is currently being patented by TRLabs and will not be defined in this thesis.

Design of the ATM traffic generation and capture card began with identification of the individual tasks necessary for performing generation and capture of ATM traffic. This served to define the major functional elements and establish the card's basic architecture. Completion of this initial design step led to the selection of components to implement these functions and the design and fabrication of prototype cards. Discussion of the card's development in this chapter will follow this structure and will also include a description of other details of its implementation.

# 4.1 Basic Architecture

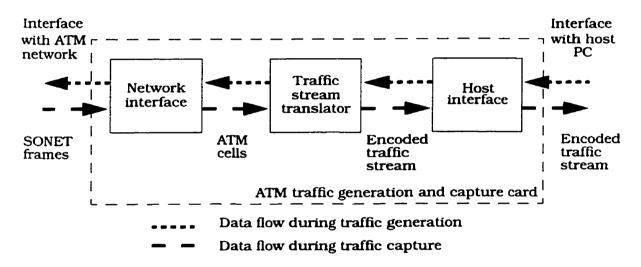

Three modules form the basic architecture of the ATM traffic generation and capture card. These modules include an ATM network interface, an interface to a host PC, and a traffic stream translator. This section will define the purpose of each of these modules and will describe how they interact to realize ATM traffic generation and capture.

## **ATM Network Interface**

In order for the card to be able to generate traffic to an ATM network as well as for it to capture traffic from a network, an interface to the ATM network is required. The network interface has to perform the functions of the ATM reference model's physical layer by completing the mapping between ATM cells and the signalling used to transfer cells across a network. The design requirements for the card specified that it be able to interface to a network using an OC-3c physical transport. During traffic generation, the network interface is required to insert cells generated by the card into the SPE of outgoing SONET frames transmitted to a network. When performing traffic capture, the network interface has to extract ATM cells from the SPE of incoming SONET frames received from a network.

# Host PC Interface

The design specification also required that the ATM traffic generation and capture card have an interface to a host PC. In addition to providing a host with the means of controlling and configuring the operation of the card, this interface is necessary for transferring the encoded ATM traffic stream between the card and the host. When generating traffic, the host supplies the card with the ATM traffic stream to send to the network. During traffic capture, the interface is used by the host to receive the ATM traffic stream captured by the card.

# **Traffic Stream Translator**

The traffic stream translator module is needed for performing the translation between a stream of ATM cells transported by a network and an encoded traffic stream processed by a host PC. During traffic generation, the traffic stream translator expands an encoded traffic stream into a stream of ATM cells which can be transmitted to the network. During traffic capture, the translator encodes the ATM traffic stream received from the network.

## Data Flow

Figure 4.1 illustrates how the network interface, host interface, and traffic stream translator modules are interconnected to form the basic architecture of the ATM traffic generation and capture card. This figure also shows the orientation and type of data flow during each of the card's two traffic processing operations.

Figure 4.1 Basic architecture of the ATM traffic generation and capture card

During traffic generation, a host supplies, via the host interface module, an encoded traffic stream to the traffic stream translator. The translator converts the encoded traffic stream into a stream of ATM cells which it transfers to the network interface. The network interface module inserts these cells into the SPEs of SONET frames sent to the network.

The direction of data flow during ATM traffic capture is opposite that during traffic generation. The network interface extracts ATM cells from the SONET SPEs received from a network and transfers these cells to the traffic stream translator. The translator converts the stream of ATM cells into an encoded traffic stream which it then sends to a host PC via the host interface.

# 4.2 Component Selection and Complete Architecture

Having defined the function of each of the modules in the card's basic architecture, the next step in the design of the ATM traffic generation and capture card was selection of components to perform these functions. This section will describe the components chosen and the complete architecture developed for the card's implementation.

# ATM Network Interface

A physical layer chip from PMC-Sierra called the S/UNI-LITE was selected to implement the card's ATM network interface. The S/UNI performs the ATM cell mapping and demapping and SONET/SDH processing functions at line rates of 51.84 Mbit/s (STS-1) and 155.52 Mbit/s (STS-3c/STM-1) and at ATM Forum mid-range PHY sub-rates of 12.96 Mbit/s and 25.92 Mbit/s<sup>3</sup>. The S/UNI conforms to the ATM Forum UNI Specification ([3]) and the ATM physical layer specification for B-ISDN as described in ITU-T Recommendation I.432 ([15]).

Like the ATM reference model's physical layer, the S/UNI is characterized as having two sides (or interfaces). The line side of the S/UNI interfaces to an ATM network through two independent bit-serial signal lines; one line is used to transmit data to the network and the other receives data from the network. The unit of transfer on the line side of the S/UNI is the SONET/SDH frame.

The side of the S/UNI opposite the line side is the drop side. The drop side of the S/UNI interfaces with ATM layer devices and uses the ATM cell as the unit of transfer.

<sup>3.</sup> Only the 155.52 Mbit/s STS-3c line rate is required for the current implementation of the ATM traffic generation and capture card.

Similar to the line side, the drop side features two independent interfaces; the transmit interface is used to load the S/UNI with the stream of ATM cells that it will send to the network while the receive interface is used to read the ATM cells that the S/UNI has received from the network. Both the transmit and receive drop side interfaces are implemented as synchronous, byte-wide buses which conform to the ATM Forum's UTOPIA Level-1 standard for interfacing ATM layer and physical layer devices ([4]). A total of 53 clock periods are required for a complete cell to be written to or read from the S/UNI; these transfers can be done at a maximum clock frequency of 33 MHz.

The transmit and receive interfaces access separate FIFOs within the S/UNI. Each of the FIFOs can be configured to a maximum depth of four ATM cells. The S/UNI takes cells which have been loaded into the transmit FIFO and maps them into the SPE of SONET/SDH frames sent to the network. When the transmit FIFO reaches an empty condition or less than a complete cell is available in the FIFO, the S/UNI inserts idle/ unassigned cells into the SPE. As ATM traffic is received from the network, the S/UNI loads the receive FIFO with the cells that are extracted from the SPE of incoming SONET/SDH frames. A simplified view of the internal architecture of the S/UNI is shown in Figure 4.2.

Also shown in Figure 4.2 is the S/UNI's microprocessor interface. The purpose of this interface is to allow devices external to the S/UNI to monitor and control its operation during ATM cell transmission and reception. The microprocessor interface consists of byte-wide address and data buses which access status and configuration registers within the S/UNI. This allows the S/UNI to be configured to perform such operations as cell filtering on received traffic and statistics such as the number of errored and uncorrectable cell headers received and the total number of cells transmitted to be monitored.

An optical transceiver on the line side of the S/UNI is necessary to complete the

implementation of the card's ATM network interface. This transceiver performs the conversion between the electrical signals processed by the S/UNI and the optical signals used to interface with the network. The particular optical transceiver selected enables the card to connect to a network through multi-mode fiber and optical signals with a 1300 nanometer wavelength.

Figure 4.2 Internal architecture of the S/UNI-LITE (after [23])

# Host PC Interface

The ATM traffic generation and capture card implements two interfaces to a host PC. One of these interfaces - the PCI Local Bus - was intended to be used to initialize the card for the traffic generation and capture operations and for transferring the encoded ATM traffic stream between a host PC and the card. The card's second interface (an RS-232 interface) to a host will be discussed later.

PCI Interface. The PCI (peripheral component interconnect) Local Bus interface

was selected as an interface to the host PC because of its capability for high data transfer rates. Although the current implementation of the card only requires a fraction (a few hundred kilo-bytes per second) of the 132 mega-bytes per second peak data transfer rate that the PCI bus is capable of providing, use of this interface was expected to ensure that the correct operation of the card is not sacrificed as a result of insufficient transfer rates between the host and the card. During traffic capture, for instance, this extra bandwidth prevents the card's captured traffic buffer from overflowing and traffic loss in the captured traffic log files from ultimately occurring.

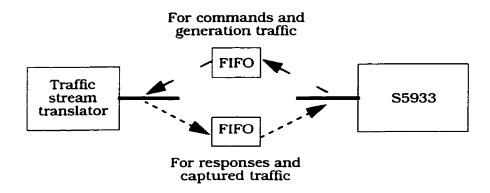

The AMCC S5933 PCI controller chip was chosen to implement the card's interface to the PCI Local Bus. The S5933 is a general purpose PCI interface chip capable of functioning as a PCI bus master or as a target device. The PCI bus side of the S5933 implements the 32 bit, 33 MHz, 5 volt version of the bus as defined in Revision 2.1 of PCI Local Bus Specification ([20]). The add-on, or expansion, side of the S5933 features a 32 bit data path and is capable of asynchronous operation or synchronous operation at clock rates up to 33 MHz.