# Minimum Power Operation of Cascade Inverter Based Dynamic Voltage Restorer for Power Quality Improvement

By

#### Husam Al-Hadidi

#### A Thesis

submitted to the Faculty of Graduate Studies in partial fulfillment of the requirements for the Degree of **Doctor of Philosophy**

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg, Manitoba, CANADA

#### THE UNIVERSITY OF MANITOBA

# FACULTY OF GRADUATE STUDIES

\*\*\*\*

#### **COPYRIGHT PERMISSION**

Minimum Power Operation of Cascade Inverter Based Dynamic Voltage Restorer for Power Quality Improvement

by

#### Husam Al-Hadidi

A Thesis/Practicum submitted to the Faculty of Graduate Studies of The University of

Manitoba in partial fulfillment of the requirement of the degree

of

**Doctor of Philosophy**

#### Husam Al-Hadidi © 2006

Permission has been granted to the Library of the University of Manitoba to lend or sell copies of this thesis/practicum, to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film, and to University Microfilms Inc. to publish an abstract of this thesis/practicum.

This reproduction or copy of this thesis has been made available by authority of the copyright owner solely for the purpose of private study and research, and may only be reproduced and copied as permitted by copyright laws or with express written authorization from the copyright owner.

# Acknowledgements

The encouragement, guide, support and incredible enthusiasm provided by Prof. A. M. Gole have been very crucial in making this thesis a reality. Thanks are due to the HVDC Centre for providing me a space and equipment during the experimental phase of this thesis and their staff members Mr. Randy Wachal, P.Eng. and Mr. Paul Wilson P. Eng. I would also like to thank my University colleague and fellow Ph.D student Mr. F. Mosallat. To all staff and colleagues of the Power Group for their kindness and friendship which have made this period a memorable and enlightening experience. I also thank my family back home, especially my parents who have devoted most of their time and energy for the well being of their children.

Finally, I express my deep appreciation to my beloved wife whose love, understand and support, were the essential ingredients in completing this work. To my two kids Samer and Sally, the tremendous joy of your presence has certainly given me an insparation.

# Abstract

This thesis introduces an enhanced implementation of a dynamic voltage restorer (DVR) based on a Voltage Sourced Converter (VSC) topology, for power quality improvement in a power network. Building on earlier research that has shown that sag compensation ability is greatly enhanced by permitting energy storage on the dc side of the VSC, a new control method is introduced which mitigates sag with minimum real power injection. This technique requires a much smaller energy reservoir on the dc side. It also permits the energy reservoir to be a capacitor instead of higher capacity reservoir such as a battery. A modular H-bridge mulilevel cascade converter topology is used which has the benefits of one-phase compensation as well as transformerless operation.

The thesis also introduces a modified new topology and the corresponding control system where the capacitor energy storage can be even further reduced by active modulation of the power factor during a sag. The thesis also demonstrates that the auxiliary function of harmonic compensation can be easily integrated into the control of the DVR.

The operational limits and the component selection of the circuit parameters is conducted from simplified analytical formulation of the circuit equations.

Extensive analysis of the dynamic performance is conducted using electromagnetic transients simulation on the PSCAD/EMTDC program.

Finally, all key conclusions are supported by small scale physical implementation in the laboratory.

| Acknowledgments       | i    |

|-----------------------|------|

| Abstract              | ii   |

| Contents              | iii  |

| List of Figures       | xii  |

| List of Tables        | xx   |

| List of Abbreviations | xxii |

| List of Symbols       | xxiv |

# Chapter 1 - Introduction

| 1.1 Introduction                                | 1  |

|-------------------------------------------------|----|

| 1.2 Conventional Dynamic Voltage Restorer (DVR) | 2  |

| 1.2.1 Major Conventional DVR Components         | 3  |

| 1.3 Research Objectives                         | 7  |

| 1.4 Digital Simulations                         | 8  |

| 1.5 Thesis Organization                         | 8  |

| Chapter 2- Power Quality Problems               |    |

| 2.1 Introduction                                | 9  |

| 2.2 Transients                                  | 9  |

| 2.3 Short-duration variations                   | 10 |

| 2.3.1 Interruption                              | 10 |

| 2.3.2 Voltage Sags                              | 11 |

| 2.3.3 Swells                                    | 11 |

| 2.4 Long duration variations                    | 12 |

| 2.4.1 Overvoltages                                         | 12 |  |  |  |

|------------------------------------------------------------|----|--|--|--|

| 2.4.2 Undervoltage                                         | 13 |  |  |  |

| 2.5 Sustained interruptions                                | 13 |  |  |  |

| 2.6 Voltage imbalance                                      | 13 |  |  |  |

| 2.7 Waveform distortion                                    | 14 |  |  |  |

| 2.7.1 Harmonics                                            | 14 |  |  |  |

| 2.8 Power quality standards                                | 16 |  |  |  |

| 2.9 Mitigation Methods Currently in Use                    | 18 |  |  |  |

| 2.9.1 Transient Voltage Surge Suppression (TVSS)           | 18 |  |  |  |

| 2.9.2 Uninterruptible Power Supplies (UPS)                 | 19 |  |  |  |

| 2.9.3 Dynamic Voltage Correction or Restoration (DVC, DVR) | 19 |  |  |  |

| Chapter 3 - Analysis of a Multilevel Inverter              |    |  |  |  |

| 3.1 Introduction                                           | 20 |  |  |  |

| 3.2 Diode-Clamped Multilevel Inverter                      | 21 |  |  |  |

| 3.3 Cascade Multilevel Inverters                           | 23 |  |  |  |

| 3.3.1 Circuitand Working Principle                              | 23 |

|-----------------------------------------------------------------|----|

| 3.3.2 The Advantage Of Cascade Multilevel Inverter              | 25 |

| 3.3.3 The Output Voltage Control of Cascade Multilevel Inverter | 26 |

| 3.4 Fundamental Frequency Switching (FFS) Of GTO'S              | 27 |

| 3.5 Pulse Width Modulation (PWM) Switching Techniques           | 33 |

| 3.5.1 Subharmonics Pulse Width Modulation (SHPWM)               | 34 |

| 3.5.2 Triangular Carrier Phase Shifting PWM Technique .         | 36 |

| 3.5.3 Switch Frequency Optimal PWM                              | 37 |

| 3.6 Comment on Different Techniques of PWM                      | 39 |

| 3.7 Comparison Between FFS Method And PWM Techniques            | 40 |

| 3.7.1 Total Harmonic Distortion                                 | 40 |

| 3.7.2 Power Losses                                              | 43 |

| 3.8 Summary                                                     | 43 |

# Chaper 4 - SYSTEM MODELING AND CONTROL STRATEGIES

| 4.1 Introduction                                           | 45 |

|------------------------------------------------------------|----|

| 4.2 A dynamic voltage restorer (DVR)                       | 46 |

| 4.2.1 Major Conventional DVR Components                    | 47 |

| 4.3 DVR Operation                                          | 53 |

| 4.4 Voltage sag Correction By DVR                          | 55 |

| 4.4.1 Minimum injected voltage method                      | 56 |

| 4.4.2 Compensation with Zero Active Power                  | 57 |

| 4.5 Proposed Minimal Active Power Mitigation Strategy      |    |

| 4.5.1 Sag smaller than that limiting value from (14)       | 60 |

| 4.2.2 Sag larger than the limiting value from (14)         | 60 |

| 4.5.3 Sag compensation when DVR voltage rating is breached | 61 |

| 4.6 Comparison between the above methods of sag mitigation | 63 |

| 4.7 Control Strategies                                     | 67 |

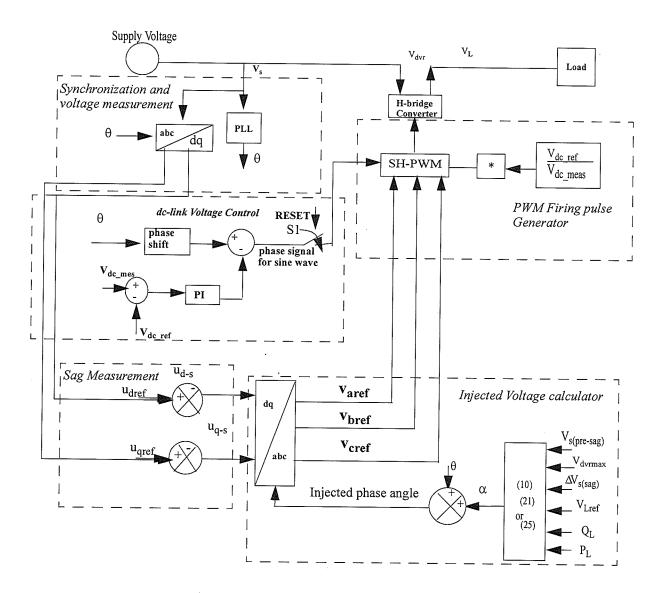

| 4.7.1 Synchronization and voltage measurement              | 68 |

| 4.7.2 Sag Measurement                                                                | 69 |  |  |

|--------------------------------------------------------------------------------------|----|--|--|

| 4.7.3 Injected Voltage Calculation                                                   | 70 |  |  |

| 4.7.4 Dc-link Voltage Control                                                        | 70 |  |  |

| 4.7.5 PWM Based Firing Pulse Generators                                              | 70 |  |  |

| 4.8 Current methods to detect voltage sags                                           | 72 |  |  |

| 4.8.1 Monitoring the peak values of the supply                                       | 72 |  |  |

| 4.8.2 Monitoring of $\sqrt{V_d^2 + V_q^2}$ or Vd in a vector controller              | 73 |  |  |

| 4.8.3 Locking a narrow band-pass filter or Phase Locked-<br>Loop (PLL) to each phase | 75 |  |  |

| 4.8.4 Applying the Fourier Transform (FFT) to each phase.                            | 75 |  |  |

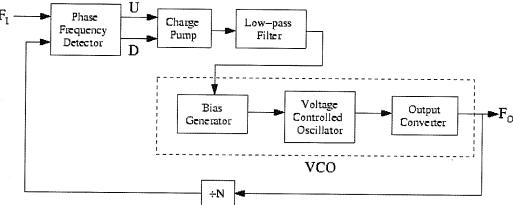

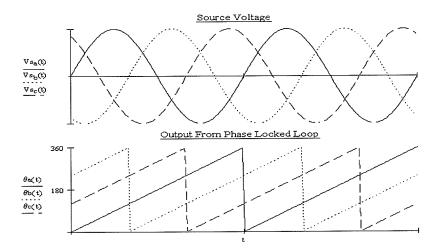

| 4.9 Phase-Locked-Loop                                                                | 76 |  |  |

| 4.10 Method Of Pre-Charging The Inverter                                             | 77 |  |  |

| Chapter 5- Sag Mitigation Simulation Results                                         |    |  |  |

| 5.1 Introduction                                                                     | 78 |  |  |

| 5.2 Test System                                                                      | 78 |  |  |

| 5.3 Results of Simulations                                                                                    | 80  |  |  |

|---------------------------------------------------------------------------------------------------------------|-----|--|--|

| 5.4 Effect of Filter                                                                                          | 84  |  |  |

| 5.5 Voltage Stability                                                                                         | 86  |  |  |

| 5.6 dc-Link voltage                                                                                           | 86  |  |  |

| Chapter 6- A New Configuration for a Cascade Inverter Based<br>DVR with Reduced Energy Storage<br>Requirement |     |  |  |

| 6.1 Introduction                                                                                              | 88  |  |  |

| 6.2 The New Proposed DVR Circuit Configuration                                                                | 89  |  |  |

| 6.2.1 Voltage Sag Correction by Proposed DVR                                                                  | 91  |  |  |

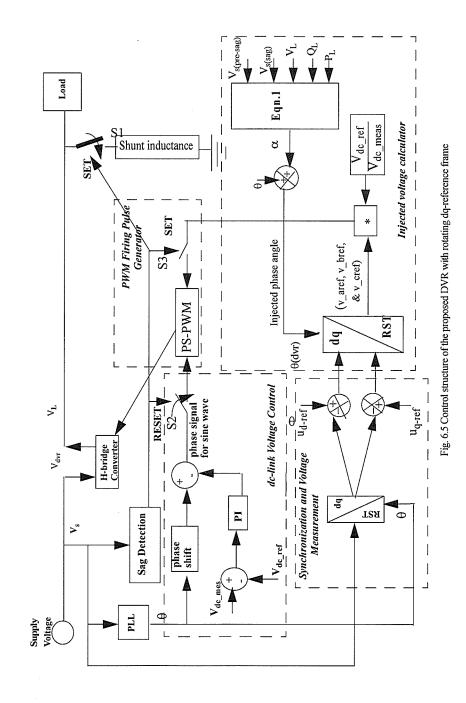

| 6.3 Control Method                                                                                            | 94  |  |  |

| 6.3.1 Sag detection                                                                                           | 94  |  |  |

| 6.4 Simulation Results                                                                                        | 96  |  |  |

| 6.5 Summary                                                                                                   | 103 |  |  |

| Chapter 7- Harmonics Compensation                                                                             |     |  |  |

| 7.1 Introduction                                                                                              | 104 |  |  |

| 7.2 Application considerations of parallel active filters           | 105 |  |  |  |

|---------------------------------------------------------------------|-----|--|--|--|

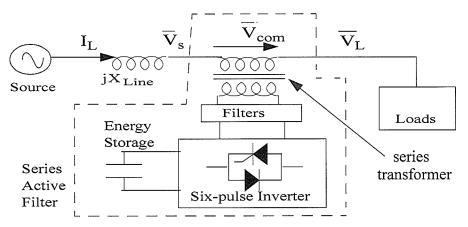

| 7.3 Series Active Filters                                           | 107 |  |  |  |

| 7.4 Comparison of Parallel Active Filters and Series Active filters | 108 |  |  |  |

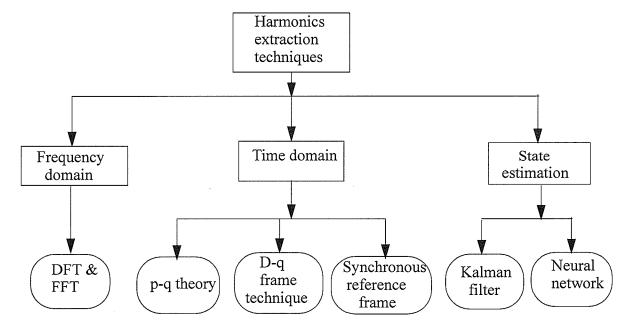

| 7.5 Harmonics Measurement Techniques                                | 109 |  |  |  |

| 7.5.1 DFT and FFT                                                   | 110 |  |  |  |

| 7.5.2 D-q Orthogonal Rotating Frame                                 | 111 |  |  |  |

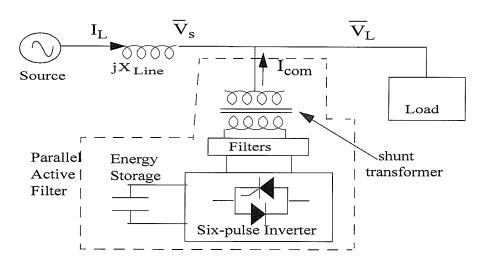

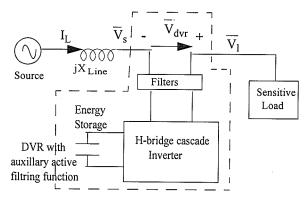

| 7.6 Proposed Harmonics Compensation Topology                        | 112 |  |  |  |

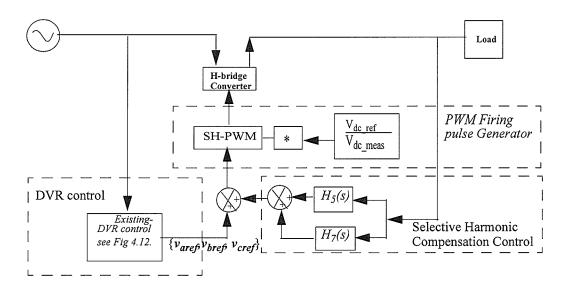

| 7.6.1 Proposed Selective Harmonic Compensation Control              | 113 |  |  |  |

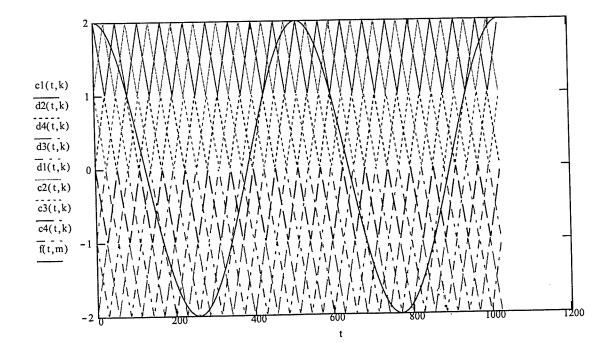

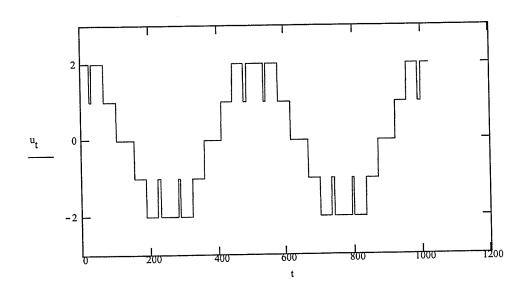

| 7.6.2 PWM Based Firing Pulse Generators                             | 117 |  |  |  |

| 7.7 Validation of Proposed Method by Simulation                     | 120 |  |  |  |

| 7.8 Summary                                                         | 123 |  |  |  |

| Chapter 8- Experimental Setup and Results                           |     |  |  |  |

| 8.1 Introduction                                                    | 124 |  |  |  |

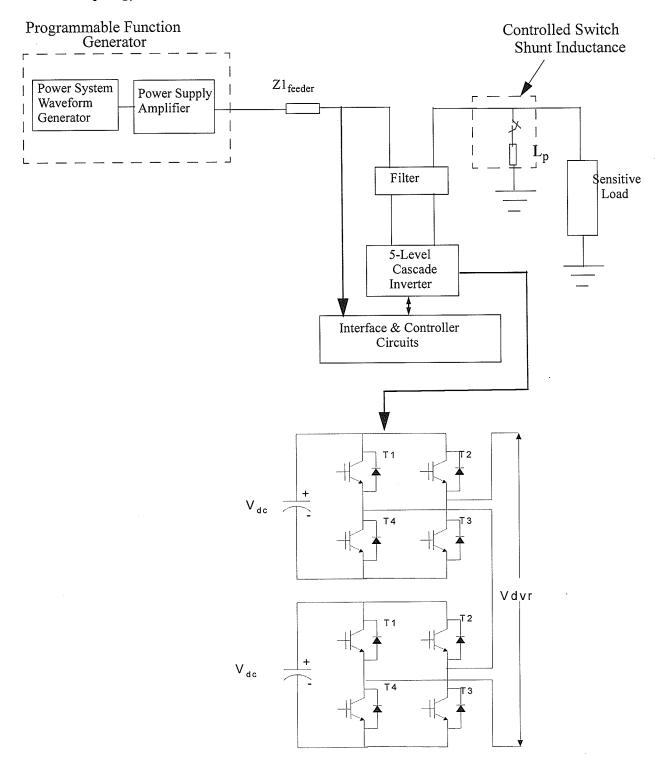

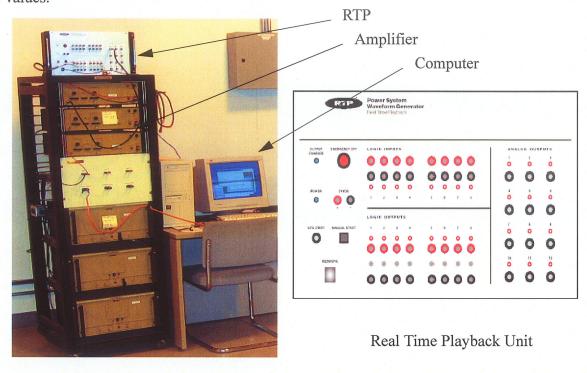

| 8.2 Experimental Setup                                              | 125 |  |  |  |

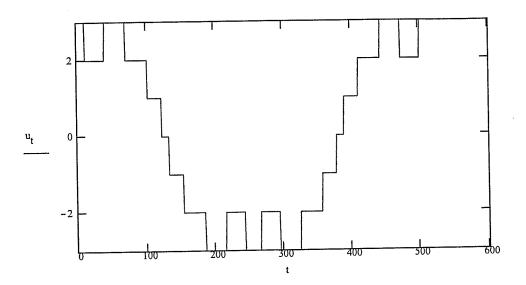

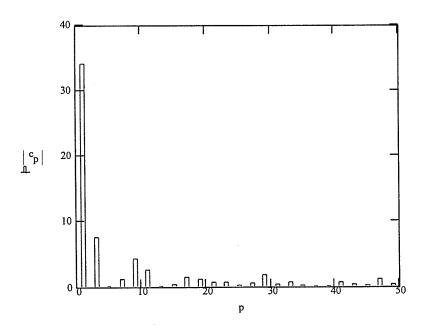

| 8.2.1 Programmable Function Generator (PFG)                         | 126 |  |  |  |

| 8.2.2 The Filter Circuit                          | 127 |  |  |  |

|---------------------------------------------------|-----|--|--|--|

| 8.2.3 The 5-Level Cascade Inverter                | 128 |  |  |  |

| 8.2.4 The Loads                                   | 129 |  |  |  |

| 8.2.5 Interface Circuits and Controllers          | 129 |  |  |  |

| 8.3 Experimental Results                          | 132 |  |  |  |

| 8.3.1 Voltage Sage and Swell Mitigation           | 132 |  |  |  |

| 8.3.2 Voltage Harmonic compensation               | 140 |  |  |  |

| 8.4 Summary                                       | 143 |  |  |  |

| Chapter 9- Contributions and Future Research Work |     |  |  |  |

| 9.1 Conclusions and Contributions                 | 144 |  |  |  |

| 9.2 Future Research Work                          | 147 |  |  |  |

| References                                        | 149 |  |  |  |

| Appendix A                                        |     |  |  |  |

| LC Filter Design                                  |     |  |  |  |

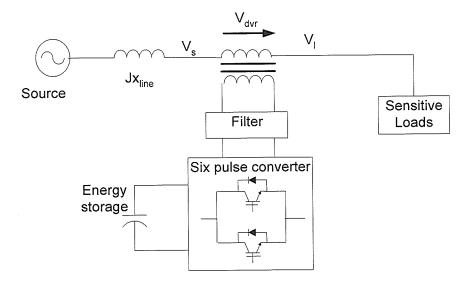

| 1.1 | Schematic diagram of a conventional DVR            | 3  |

|-----|----------------------------------------------------|----|

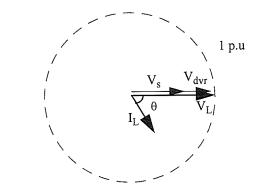

| 1.2 | Phasor diagram for compensation of sag             | 3  |

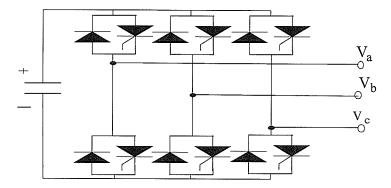

| 1.3 | Six-Pulse GTO voltage source inverter              | 6  |

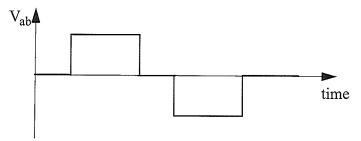

| 1.4 | Inverter output line-to-line voltage waveform      | 6  |

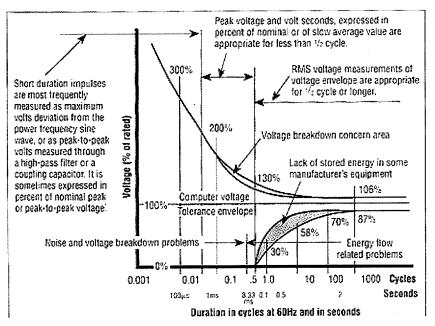

| 2.1 | The CMEBA plot for voltage tolerance               | 16 |

| 2.2 | Flicker limit curve of 519-1992 and 141-1993       | 18 |

| 3.1 | One phase of diode-clamped N-level inverter        | 22 |

| 3.2 | Five level Diode-clamped Inverter Waveform Voltage | 23 |

|     |                                                    |    |

| 3.3  | The three phase Y-structure 7-level cascade inverter                                                           | 24 |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 3.4  | The H-bridge inverter and its three level output voltage waveform                                              | 25 |

| 3.5  | One phase of a 7-Level cascaded multi-level inverter                                                           | 28 |

| 3.6  | The output voltage waveform for each H-bridge                                                                  | 29 |

| 3.7  | The 7-Level Stepped-waveformt                                                                                  | 30 |

| 3.8  | Line-to-neutral output voltage waveform of 7-level cascaded 33 inverter using the FFS method                   | 33 |

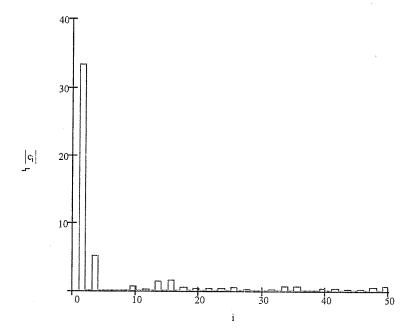

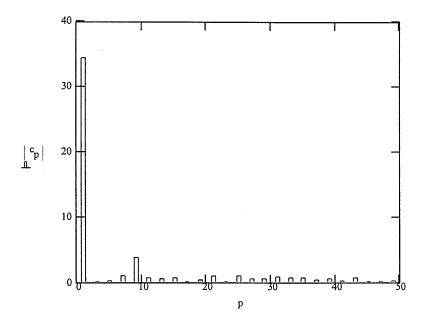

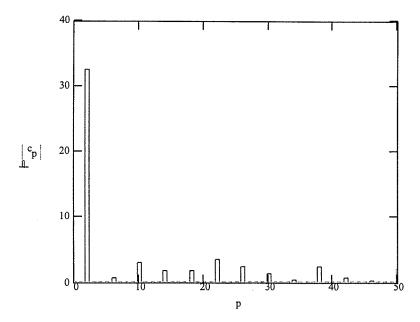

| 3.9  | Harmonic spectra for line-to-neutral output voltage waveform of 7-level cascaded inverter using the FFS method | 33 |

| 3.10 | The Principle of the SHPWM for n=5, k=7 and MI=1.0                                                             | 35 |

| 3.11 | The Principle of the PS-PWM for n=5, k=9 and MI=1.0                                                            | 36 |

| 3.12 | The Principle of the SOF PWM for n=5, k=7 and MI=1.0                                                           | 38 |

| 4.1  | Schematic diagram of a DVR                                                                                     | 46 |

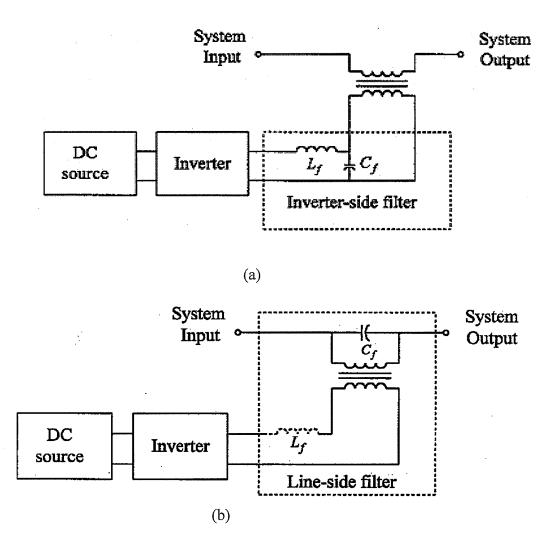

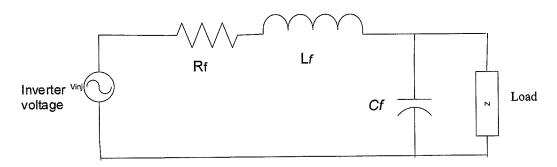

| 4.2: | Filtering scheme of the conventional DVR                                                                       | 48 |

| 4.3  | One phase of a 5-level cascaded multi-level inverter                                                           | 53 |

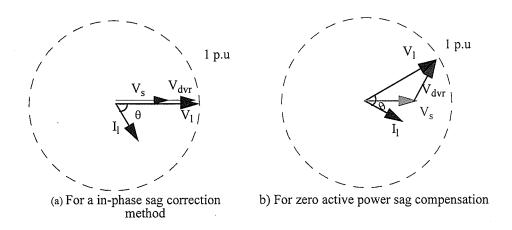

| 4.4  | Phasor diagram for compensation of sag                                                                         | 55 |

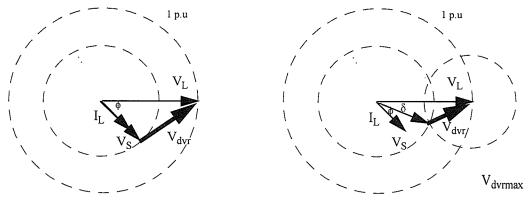

| 4.5  | Phasor diagram proposed method for sag compensation                                                            | 62 |

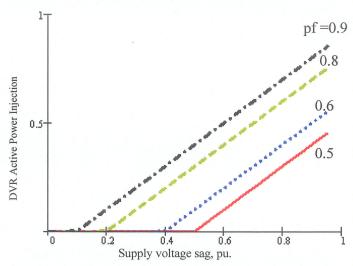

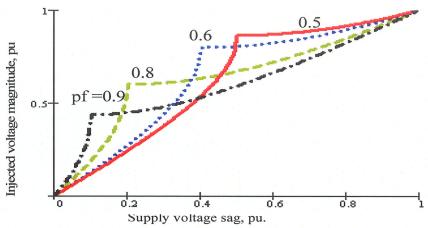

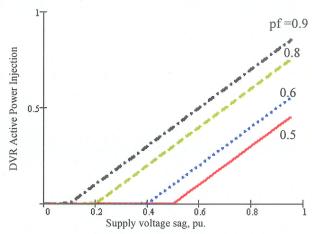

| 4.6  | Injected DVR active power verses the voltage sag for four different power factor                                     | 65 |

|------|----------------------------------------------------------------------------------------------------------------------|----|

| 4.7  | Injected voltage magnitude of DVR versrs the voltage sag for four-different power factors                            | 65 |

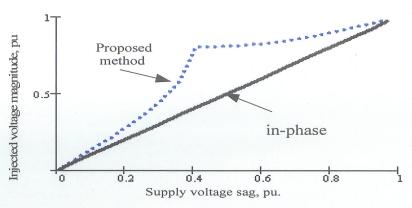

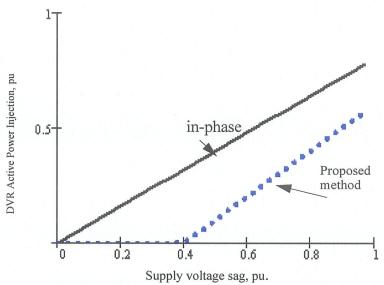

| 4.8  | Comparison between in-phase with minimum active power injected method based on the voltage magnitude injected by DVR | 66 |

| 4.9  | Comparison between in-phase with minimum active power injection based on active power injected by DVR                | 66 |

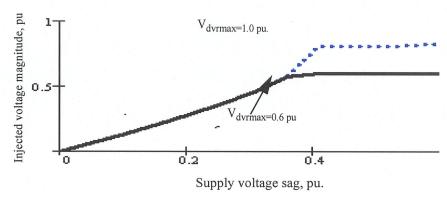

| 4.10 | The injected voltage magnitude for the proposed compensation method with two different ceiling rating $(V_{dvrmax})$ | 67 |

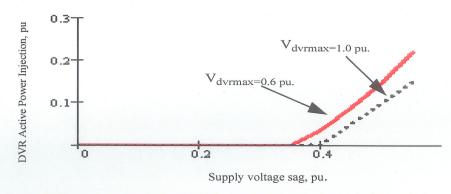

| 4.11 | The active power injection for the proposed compensation method with two different ceiling rating $(V_{dvrmax})$     | 67 |

| 4.12 | Control structure of DVR with rotating dq-reference frame                                                            | 68 |

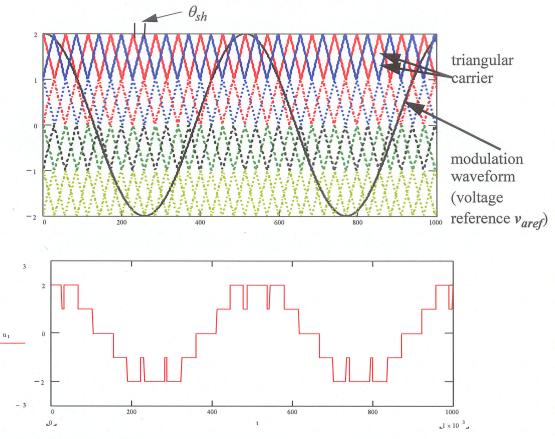

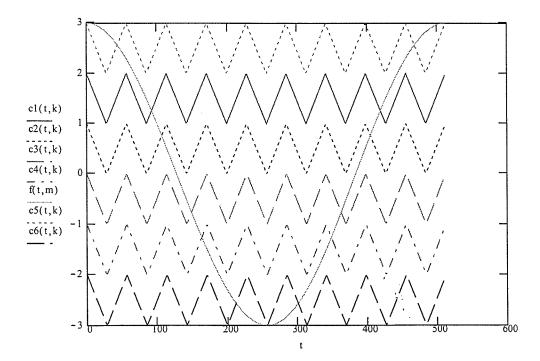

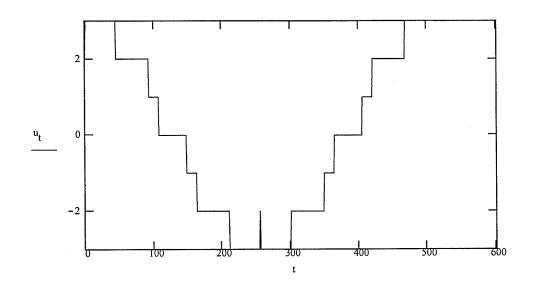

| 4.13 | The Principle of the PS-PWM for n=5, k=9 and MI=1.0                                                                  | 71 |

| 4.14 | Basic Phase Locked Loop                                                                                              | 76 |

| 4.15 | Output Signals from Phase Locked Loop                                                                                | 76 |

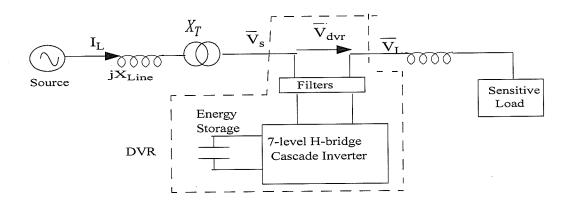

| 5.1  | Schematic diagram of the simulation test system                                                                      | 79 |

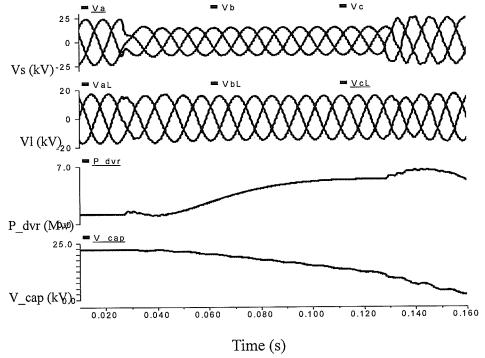

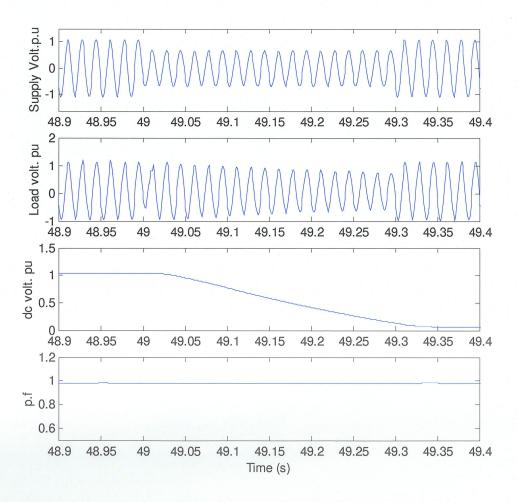

| 5.2  | Simulation results by using in-phase DVR                                                                             | 80 |

| 5.3  | Simulation results by using in-phase DVR for long duration sag                                                  | 81 |

|------|-----------------------------------------------------------------------------------------------------------------|----|

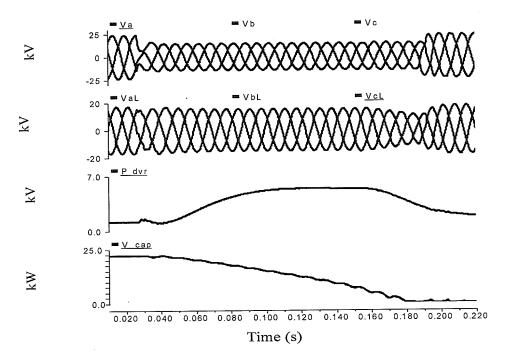

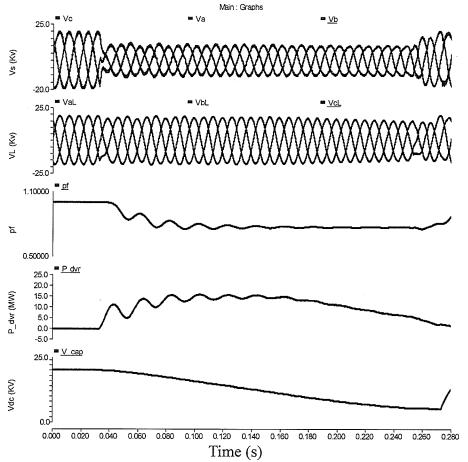

| 5.4  | Sag Correction by Minimum Power Injection for a 5 cycle sag                                                     | 82 |

| 5.5  | Sag correction by minimum power injection for a 8 cycle sag                                                     | 83 |

| 5.6  | Unbalance sag correction by minimum power injection                                                             | 84 |

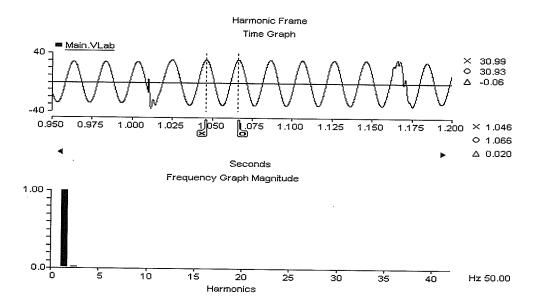

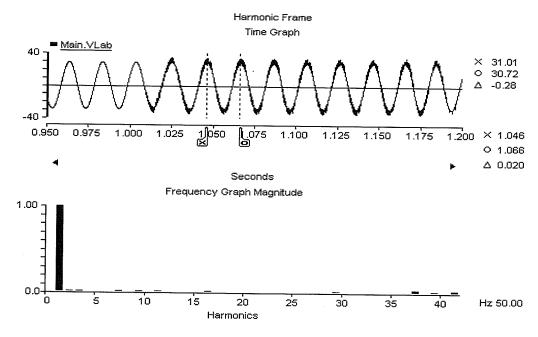

| 5.7  | DVR output line-to-line voltage waveform after the filter and its harmonic spectrum                             | 85 |

| 5.8  | DVR Output Line-to-line voltage waveform before the filter and its harmonic spectrum                            | 85 |

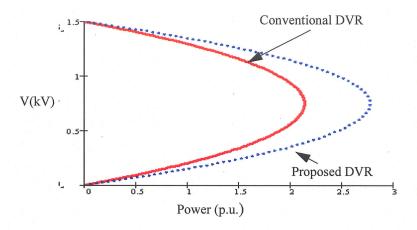

| 5.9  | PV curves for system with typical DVR configuration and proposed configuration                                  | 86 |

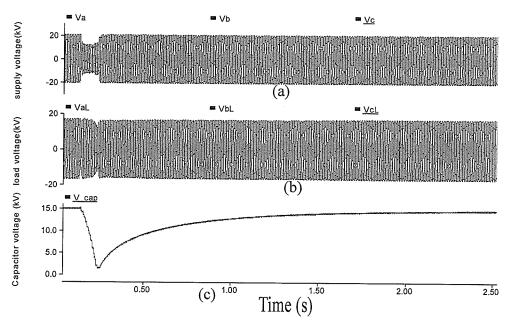

| 5.10 | Charging of the dc-link voltage                                                                                 | 87 |

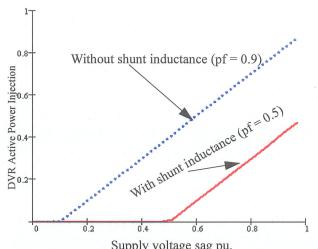

| 6.1  | Injected DVR active power verses the voltage sag for four different power factors                               | 89 |

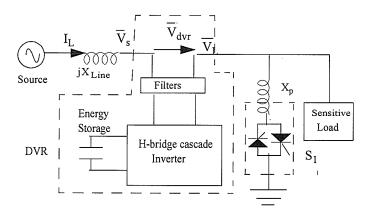

| 6.2  | Schematic diagram of proposed new DVR                                                                           | 91 |

| 6.3  | Injected DVR active power verses the voltage sag for system without series inductance and with shunt inductance | 92 |

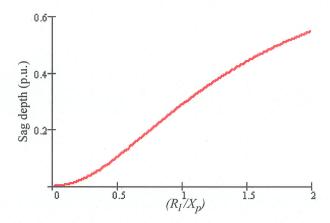

| 6.4  | Shows the sag depth which can be mitigated without injecting real power for different $(R_l/X_p)$ ratio         | 93 |

| 6.5  | Control structure of the proposed DVR with rotating dq-reference frame                             | 95  |

|------|----------------------------------------------------------------------------------------------------|-----|

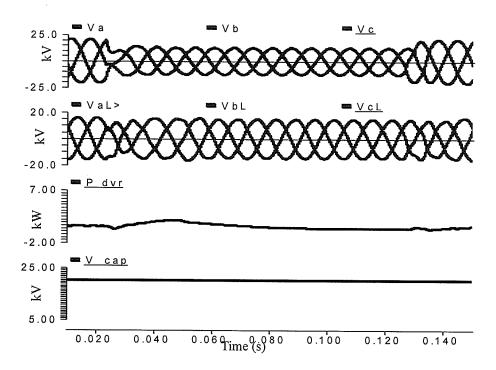

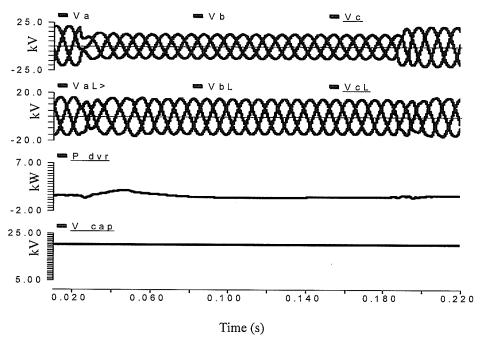

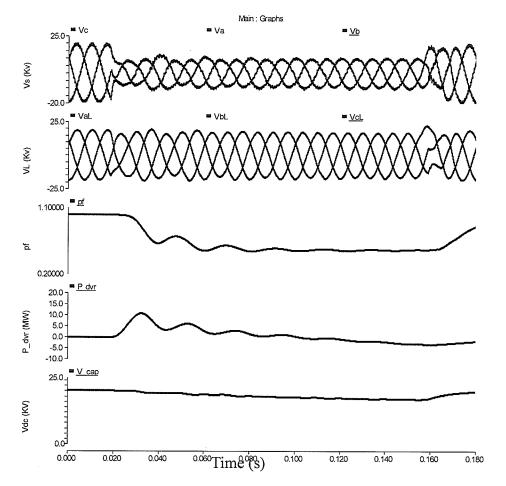

| 6.6  | Simulation results without shunt inductance in the circuit                                         | 97  |

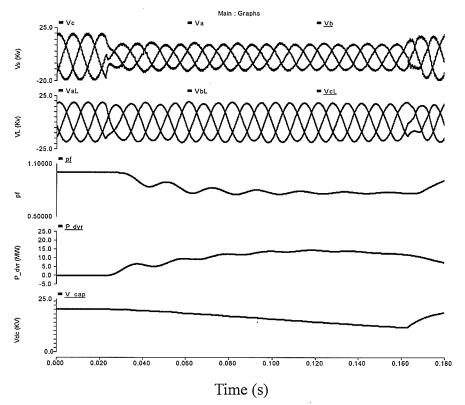

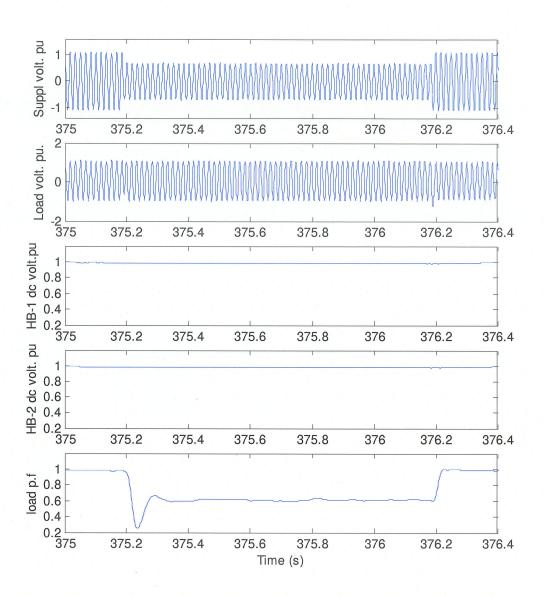

| 6.7  | Simulation results for the proposed DVR configuration for 7 cycles 40% sag with $(R_l/X_p) = 0.8$  | 99  |

| 6.8  | Simulation results for the proposed DVR configuration for 14 cycles 40% sag with $(R_1/X_p) = 0.8$ | 100 |

| 6.9  | Simulation results for the proposed DVR configuration for 7 cycles 40% sag with $(R_1/X_p) = 1.3$  | 101 |

| 6.10 | Simulation results for the proposed DVR configuration for 14 cycles 40% sag with $(R_l/X_p)$ =1.3  | 102 |

| 7.1  | Schematic diagram of a parallel active filter                                                      | 106 |

| 7.2  | Schematic diagram of a series active filter                                                        | 107 |

| 7.3  | Harmonics extraction and estimation techniques                                                     | 109 |

| 7.4  | Schematic diagram of a proposed DVR for sags and harmonics mitigation                              | 113 |

| 7.5  | Control structure of DVR with harmonic compensation                                                | 115 |

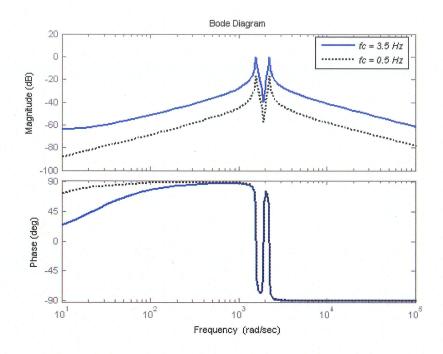

| 7.6  | Open loop frequency response of the voltage harmonic controllers                                   | 117 |

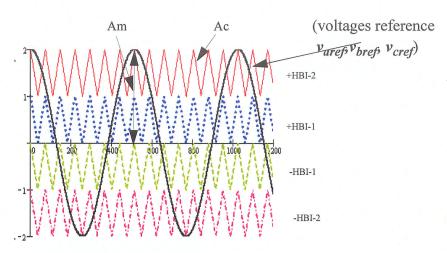

| 7.7  | SHPWM for five-level cascade inverter (during the sag)                                             | 118 |

| 7.8  | SHPWM for five-level cascade inverter (during the harmonics)                                                        | 118 |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

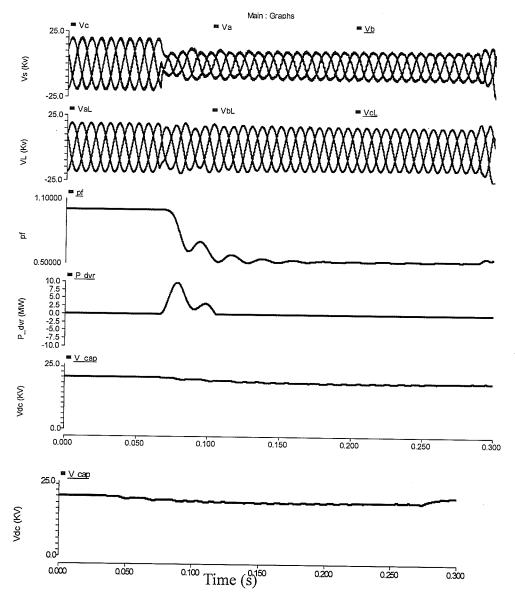

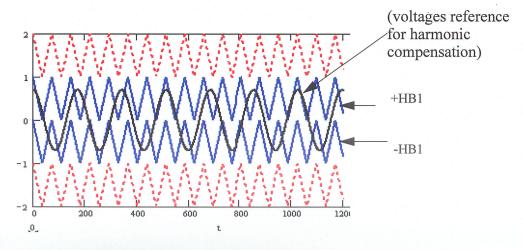

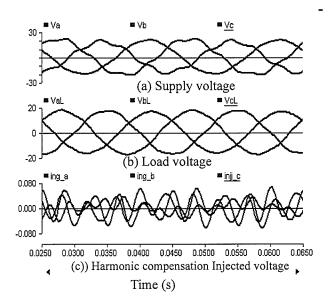

| 7.9  | Selective harmonic compensation for System with balanced supply voltage THD of 20%                                  | 121 |

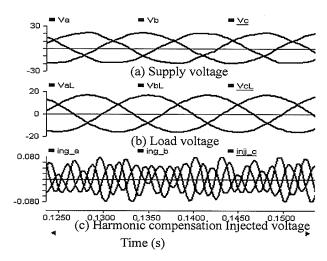

| 7.10 | Selective harmonic compensation for System with balanced supply voltage THD of 6.5%                                 | 122 |

| 7.11 | System with unbalanced supply voltage (phase with THD of 0.5%, phase b with THD of 6.5%, and phase c with THD of 9% | 123 |

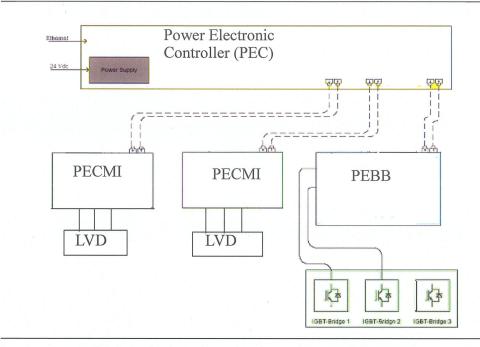

| 8.1  | Experimental Setup for Voltage Sags, Swells and Harmonics Mitigation                                                | 125 |

| 8.2  | Programmable Function Generator (PFG)                                                                               | 127 |

| 8.3  | 5-Level cascade inverter                                                                                            | 128 |

| 8.4  | The interface circuits and controllers                                                                              | 130 |

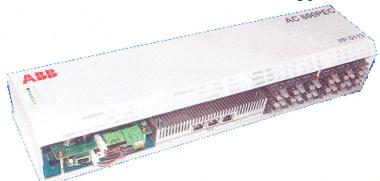

| 8.5  | A Power electronic controller (PEC)                                                                                 | 130 |

| 8.6  | The hardware of the experimental setup                                                                              | 131 |

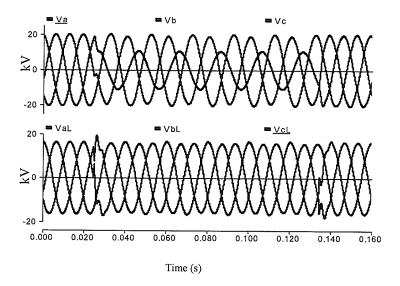

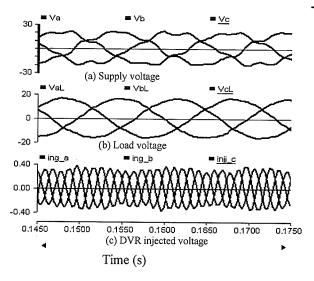

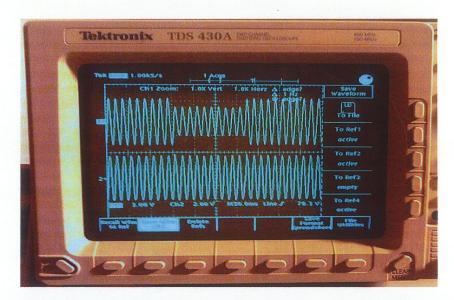

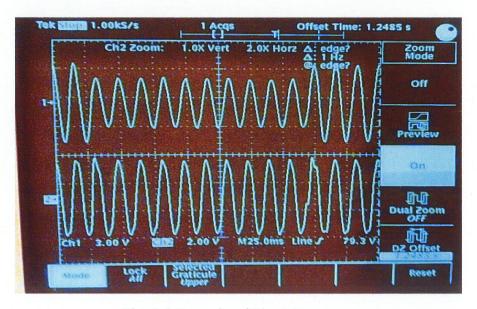

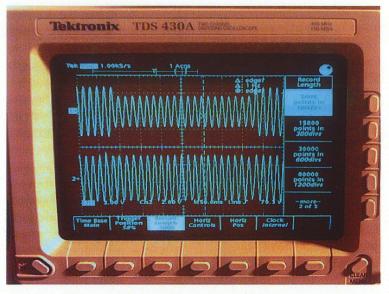

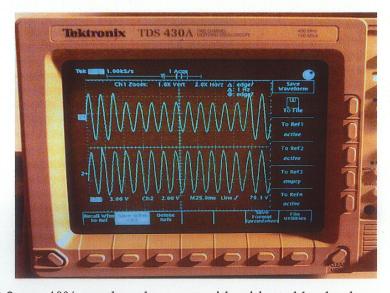

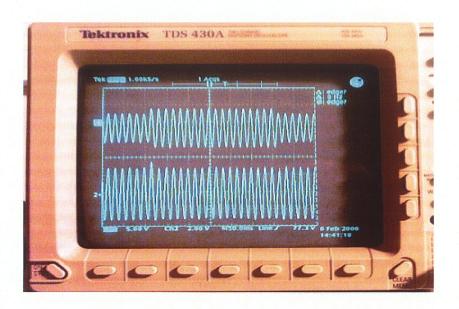

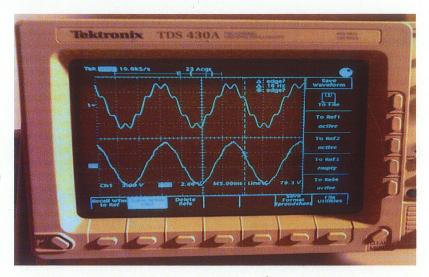

| 8.7  | 40% supply voltage sag with mitigated load voltage waveforms                                                        | 133 |

| 8.8  | Zoom in of Fig. 8.7                                                                                                 | 133 |

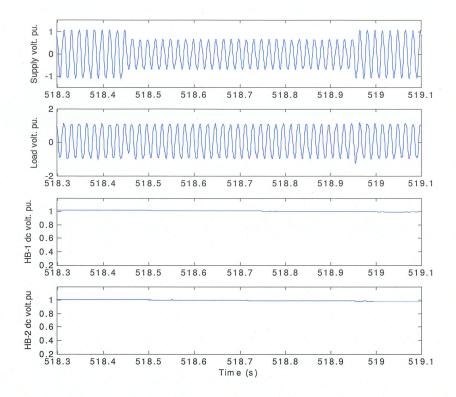

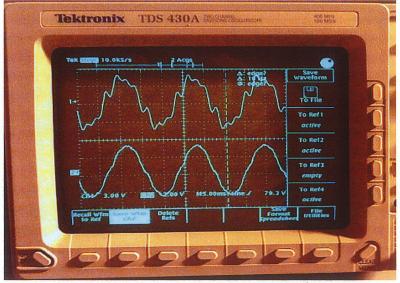

| 8.9  | Supply voltage with 0.5 sec. 40% sag, load voltage, HB-1 dc voltage and HB-2 dc voltage Waveforms respectively                  | 134 |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

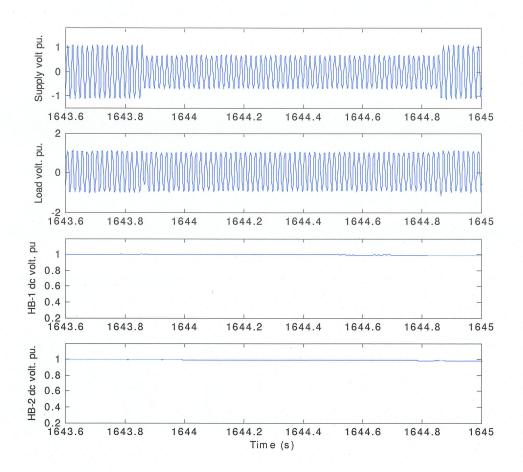

| 8.10 | Supply voltage with 1 sec. 40% sag, load voltage, HB-1 dc voltage and HB-2 dc voltage Waveforms respectively                    | 135 |

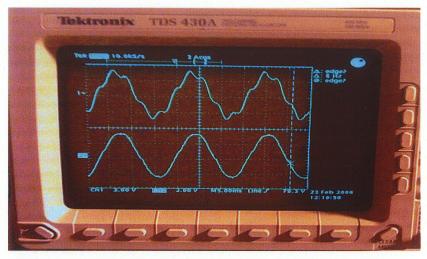

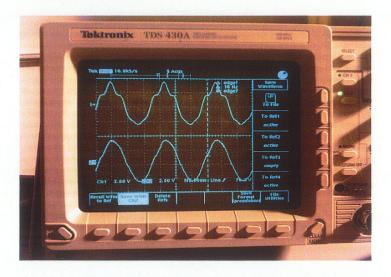

| 8.11 | 0.4 sec. 40% supply voltage sag with mitigated load voltage waveforms                                                           | 136 |

| 8.12 | 0.2 sec. 40% supply voltage sag with mitigated load voltage waveforms                                                           | 136 |

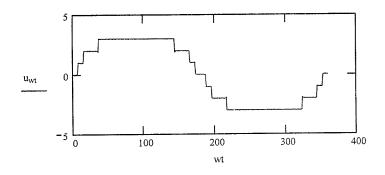

| 8.13 | Sag voltage mitigation without the control switch inductance                                                                    | 137 |

| 8.14 | Sag voltage mitigation with the control switch inductance                                                                       | 139 |

| 8.15 | 0.4 sec. 30% supply voltage swell with mitigated load voltage waveforms                                                         | 140 |

| 8.16 | Distorted supply voltage with 15% 5 <sup>th</sup> harmonic with 90 degree phase shift and the compensated load voltage          | 141 |

| 8.17 | Distorted supply voltage with 15% 7 <sup>th</sup> harmonic with 90 degree phase shift and the compensated load voltage waveform | 142 |

| 8.18 | Distorted supply voltage with 15% 5 <sup>th</sup> and 15% 7 <sup>th</sup> harmonics and the compensated load voltage waveform | 142 |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----|

|      | Distorted supply voltage with 10% 4 <sup>th</sup> and 10% 5 <sup>th</sup> harmonics and the compensated load voltage waveform | 143 |

# List of Tables

| 2.1 | Categories of Power quanty variation-TEEE Std. 1139-19993       | 13  |

|-----|-----------------------------------------------------------------|-----|

| 3.1 | The Gate Logic for Five-level Diode-clamped Inverter            | 22  |

| 3.2 | Calculated Switching Angles for Different MI                    | 32  |

| 3.3 | Typical Calculation Results Using FFS                           | 40  |

| 3.4 | Typical Calculation Results Using SH-PWM                        | 41  |

| 3.5 | Typical Calculation Results Using SFO-PWM                       | 41  |

| 5.1 | Main test system parameters                                     | 79  |

| 7.1 | Comparison of Parallel Active Filters and Series Active filters | 108 |

| 7.2 | D-q disturbance extraction table | 111 |

|-----|----------------------------------|-----|

| 8.1 | Main test system parameters      | 126 |

# List of Abbreviations

**DFT** Discrete Fourier Transform

**FFT** Fast Fourier Transform

VSC Voltage Sourced Converter

**PWM** Pulse Width Modulation

**PS-PWM** Phase Shift Pulse Width Modulation

**SHPWM** SubHarmonic Pulse Width Modulation

**SFOPWM** Switch Frequency Optimal PWM

PLL Phase 1

**UPS** Uninterruptible Power Supplies

**FFS** Fundamental Frequency Switching

**DVR** Dynamic Voltage Restorer

PLL Phase Locked-Loop

**PFG** Programmable Function Generator

**RTP** Real Time Playback

TVSS Transient Voltage Surge Suppression

**UPS** Uninterruptible Power Supplies

**THD** Total Harmonic Distortion

**IGBT** Insulated Gate Bipolar Transistors

GTO Gate Turnoff Thyristor

**HBI** H-bridge Inverter

SMES Superconductive Magnetic Energy Storage

# List of Symbols

ac Alternating current

$\mathbf{A_m}$  Amplitude of the modulation waveform

$\mathbf{A_c}$  Amplitude of carrier waveform

dc Direct current

$\mathbf{f_c}$  Frequency of the carrier

$\mathbf{f_m}$  Frequency of the modulation waveform

**K** Frequency ratio

kA Kiloampere

kV Kilovolt

**m** Modulation index

**p.f** Load power factor

$V_s$  Supply voltage

$V_l$  Load voltage

V<sub>dvr</sub> Dynamic Voltage Restorer voltage

$I_l$  Load current

$\Delta \mathbf{V_{s\_sag}}$  Sag voltage

α Dynamic Voltage Restorer injection angle

$\theta$  Phase Locked-Loop angle

φ Load power factor angle

**Xp** Shunt inductance

R<sub>l</sub> Load resistor

L<sub>f</sub> Filter inductance

$\mathbf{C_f}$  Filter capacitor

#### **CHAPTER 1**

# Introduction

#### 1.1 Introduction

This chapter introduces the definition of power quality and the importance of maintaining power quality. The basic dynamic voltage restorer (DVR) and the research objectives will be presented in this chapter.

The term power quality has come into the vocabulary of many industrial and commercial electricity end-users in recent years has many definitions and terminologies, which vary according to IEEE and IEC standards, utilities, and consumers [1-4]. However it may be defined as the degree to which both the utilization and delivery of electric power affect the performance of electrical equipment [5].

Power quality is an issue that is becoming increasingly important to electricity consumers at all levels of usage. Sensitive equipment and non-linear loads are now more common place in both the industrial sectors and the domestic environment. Because of this a heightened awareness of power quality is developing amongst electricity users. Occur-

rences affecting the electricity supply that were once considered acceptable by electricity companies and users are now often considered a problem to the users of everyday equipment. Voltage sag, swell and harmonics can cause equipment to fail, or shutdown, as well as create a large current unbalance that could blow fuses or trip breakers. These effects can be very expensive for the customer, ranging from minor quality variations to production downtime and equipment damage [6]. With the dawn of a competitive environment, the utility company has much more interest in power quality. Utilities are interested in keeping their customers satisfied, as well as keeping them on-line and drawing kilowatts, creating more revenue for the utility. All of this interest has resulted in a variety of devices designed for mitigating power disturbances such as voltage sags [1]. One class of these devices is the DVR, which has been developed and applied to the critical loads such as found in semiconductor or chemical plants.

# 1.2 Conventional Dynamic Voltage Restorer (DVR)

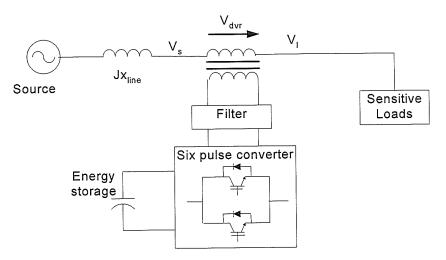

A conventional dynamic voltage restorer (DVR)[7, 10], with its excellent dynamic capabilities, when installed between the supply and a critical load feeder, can compensate for voltage sags, restoring line voltage to its nominal value within a few milliseconds and hence avoiding any power disruption to that load. Fig. 1.1 shows the schematic diagram of a typical DVR used for voltage correction. When the supply voltage  $V_S$  changes, the DVR injects a voltage  $V_{dvr}$  in series with the supply voltage as shown in Fig. 1.2 so that the desired load voltage magnitude can be maintained. The DVR is simply a voltage source inverter that produces an ac output voltage and injects in series with the supply voltage through a booster transformer.

Fig. 1.1: Schematic diagram of a Conventional DVR

Fig. 1.2: Phasor diagram for compensation of sag

# 1.2.1 Major Components of a Conventional DVR

From Fig 1.1 the major conventional DVR components and their function can be listed as follows:

• Injection / Booster transformer:

It's main tasks are connects the DVR to the distribution network via the HV-windings and transforms and couples the injected compensating voltages generated by the volt-

age source converters to the incoming supply voltage. It is one unit three phase construction.

#### • Harmonic filter:

The main tasks of harmonic filter is to keep the harmonic voltage content generated by the voltage source converters to the permissible level. It has a small rating approximately 2% of the load MVA connected to delta-connected tertiary winding of the injection transformer.

• Energy source e.g. storage capacitor bank.

The purpose is to supply the necessary energy to the VSC via a dc link for the generation of injected voltages. Different kinds of energy storage devices exist like superconductive magnetic energy storage (SMES), batteries, and capacitance. In fact, the capacity of the stored energy directly determines the ride-through capability; therefore it can affect the duration of the sag which can be mitigated by the DVR. The focus of this research is not to give a justification for selection of energy storage device, but to develop a control algorithm to minimize the amount of energy required to mitigate a voltage sag. Essential control aspects are considered in Chapter 4 and Chapter 6.

# • DC charging circuit:

The main tasks of the dc charging circuit are to charge the energy source after a sag compensation event and maintain dc link voltage at the nominal dc link voltage.

Control and protection system.

# • Voltage source converters

The main task of the voltage source converter is to generate the required injected voltage to compensate for the supply voltage sags. A six-pulse voltage source converter with its ac output connected to the low voltage windings of the injection transformer is the simplest implementation of such a converter, as shown in Fig. 1.3. In normal operation, a 6-pulse bridge voltage source inverter with a charged dc capacitor will give a balanced set of three quasi-square waveforms of the voltages at the output terminal, as shown in Fig. 1.4 [9]. This simple form is usually not adequate for utility application as it has harmonics, needs a series transformer and has a single dc storage for all three phases. This research proposes cascade multilevel inverter based DVR. The proposed configuration will be discuss in detail in Chapter 3.

Fig. 1.3: Six-Pulse GTO voltage source inverter

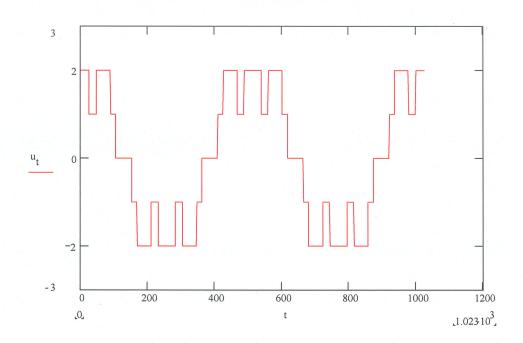

Fig.1.4: Inverter output line-to-line voltage waveform

The customer's requirements dictate the design and performance of the DVR. In the third chapter; the considerations that must be taken into account for the design of the DVR in order to fulfil the required specifications will be investigated. Design considerations that influence the rating and performance of the DVR such as the load MVA, power factor, magnitudes of single and three phase voltage sags and fault duration, three phase fault level at the incoming bus, etc. are discussed in detail in Chapter 4. In Fig. 1.3 the switching device is shown as a Gate Turnoff Thyristor (GTO). However, for ratings typical for distribution system application the Insulated Gate Bipolar Transistors (IGBT) device is adequate. Individual IGBT ratings are now upto 4.5kV, 2.0kA [44].

## 1.3 Research Objectives

The main objective of this research is to develop a new cascade multi-level based topology and control strategy for compensating and mitigating voltage disturbances and improving the power quality in distribution systems while optimizing the dc-side energy storage. To achieve the above objective the following tasks were carried out:

- Investigation of different topologies of multilevel inverters

- Identification and development of PSCAD/EMTDC models for the prototype network configurations. The converter devices will be tested on these network configurations.

- Development of suitable control strategies which will be aimed at:

- 1- Maintaining individual capacitor voltages at desired levels.

- 2- Optimizing the dc-side energy storage requirements by controlling the amount of active power injected to the system.

- 3- Obtaining adequate dynamic performances with high control stability.

- 4- Charging ability of the capacitors with energy drawn from the system without any connection on the dc side of the DVR.

- Investigation of the switching methods. Both the fundamental frequency switching (FFS) and pulse width modulation (PWM) techniques will be studied.

- Develop DVR circuit topology, which has the ability to mitigate severe and long duration voltage sags with comparatively small energy storage capacitors.

- Develop a novel control strategy to add a harmonic elimination ability to the DVR

- Additional Considerations.

- 1. Implications of additional capacitor sizing for energy storage.

- 2. Using PWM for harmonic quality improvement.

## 1.4 Digital Simulations

The models for the prototype network configurations were further evaluated and analyzed by using the electromagnetic transient simulation program PSCAD/EMTDC.

#### 1.5 Thesis Organization

This thesis includes nine chapters. Chapter 2 discusses some of the power quality problems and their definitions according to IEEE Standards. In Chapter 3, there is a full analysis of multilevel inverters with a focus on cascade multilevel inverters and their operating principles and control strategies. Chapter 4 introduces the DVR operating principle, mathematical analysis of the required active and reactive power needed by the DVR to mitigate a certain sag and a proposed control strategy to optimize the dc energy storage of the DVR. Chapter 5 provides the simulation results for the mitigation of balance and unbalanced voltage sags. Chapter 6 presents a proposed novel DVR configuration and compares it with the existing configuration to demonstrate the superiority of the proposed configuration. Chapter 7 presents an extensive study about harmonic compensation techniques and there suitability for integrating into DVR configurations. The hardware and the software for the experimental work and results are presented in Chapter 8. Finally, Chapter 9 summarizes and concludes the contribution of this thesis, and suggests some topics for future research.

#### **CHAPTER 2**

# Power Quality Problems

#### 2.1 Introduction

Power quality is an issue that is becoming increasingly important to electricity consumers at all levels of usage. Sensitive equipment and non-linear loads are now more commonplace in both the industrial/commercial sectors and the domestic environment. Hence, a heightened awareness of power quality is developing amongst electricity users. Occurrences affecting the electricity supply that were once considered acceptable by electricity companies and users are now often considered a problem to the users of everyday equipment [4-6].

#### 2.2 Transients

"The term transients has been used in the analysis of power system variations for a long time. Its name immediately conjures up the notion of an event that is undesirable but momentary in nature" [1]. The IEEE Std. 100-1992 definition of transient reflects this understanding. The primary definition uses the word "rapid" and talks of frequencies up to

3 MHz when defining the transient in the context of evaluating cable systems in substations. Other definitions in IEEE Std. 100-1992 are broader in scope and simply state that a transient is that part of the change in a variable that disappears during transition from one steady-state operating condition to another. Unfortunately, this definition could be used to describe just about anything unusual that happens on the power system.

#### 2.3 Short-duration variations

"This category encompasses the IEC category of voltage dips and short interruptions as well as the antithesis of dip, or swell" [1]. Each type of variation can be designated as instantaneous, momentary, or temporary, depending on its duration as defined in Table 2.1. Short-duration voltage variations are almost always caused by fault conditions, the energizing of large loads that require high starting currents, or intermittent loose connections in power wiring. Depending on the fault location and the system conditions, the fault can cause either temporary voltage rises (swells) or voltage drops (sags), or a complete loss of voltage (interruptions).

#### 2.3.1 Interruption

An interruption occurs when the supply voltage or load current decreases to less than 0.1 pu for a period of time not exceeding 1 min. Interruptions can be the result of power system faults, equipment failures, and control malfunctions[1, 5]. The interruptions are measured by their duration since the voltage magnitude is always less than 10% of nominal. The duration of an interruption due to a fault on the utility system is determined by utility protective devices and the particular event that is causing the fault. The duration

of an interruption due to equipment malfunctions or loose connections can be irregular. Some interruptions may be preceded by voltage sag when these interruptions are due to faults on the source system. The voltage sag occurs between the time a fault initiates and the protective device operates. On the faulted feeder, loads will experience a voltage sag followed immediately by an interruption.

#### 2.3.2 Voltage Sags

A momentary voltage dip that lasts for a few seconds or less is classified as a voltage sag. Voltage sags may be caused by faults on the transmission or distribution system or by the switching of loads with large amounts of initial starting/ inrush current (motors, transformers, large dc power supplies). Voltage sags may be sufficiently severe, especially in the case of faults, to cause sensitive loads (computers, VCRs, clocks, etc.) to reset [8]. The term sag has been used in the power quality community for many years to describe a specific type of power quality disturbance; a short duration voltage decrease. Clearly, the notion is directly borrowed from the literal definition of the word sag. The IEC definition for this phenomenon is called dip.

#### **2.3.3** Swells

A swell is defined "as an increase in rms voltage or current at the power frequency for durations from 0.5 cycles to 1 min. Typical magnitudes are between 1.1 and 1.8 pu" [1]. As with sags, swells are usually associated with system fault conditions, but they are much less common than voltage sags. A swell can occur due to a single line-to-ground fault on the system resulting in a temporary voltage rise on the unfaulted phases. Swells

can also be caused by switching off a large load or switching on a large capacitor bank. A formal definition of swell in IEEE Std. C62.41-1991 is a momentary increase in the power-frequency voltage delivered by the mains, outside of the normal tolerances, with duration of more than one cycle and less than a few seconds [6].

# 2.4 Long duration variations

Long duration variations encompass rms deviations at power frequencies for longer than 1 min. The steady-state voltage tolerances expected on a power system are specified. These magnitudes are reflected in Table 2.1. Long duration variations are considered to be present when the ANSI limits are exceeded for greater than 1 min. Long duration variations can be either overvoltages or undervoltages, depending on the cause of the variation. Overvoltages and undervoltages generally are not the result of system faults. They are caused by load variations on the system and system switching operations. These variations are characterized by plots of rms voltage versus time.

#### 2.4.1 Overvoltages

Overvoltages can be the result of load switching (e.g., switching off a large load), or variations in the reactive compensation on the system (e.g., switching on a capacitor bank). Poor system voltage regulation capabilities or controls result in overvoltages. Incorrect tap settings on transformers can also result in system overvoltages.

#### 2.4.2 Undervoltage

Undervoltages are the result of the events that are the reverse of the events that cause overvoltages. A load switching on, or a capacitor bank switching off, can cause an undervoltage until voltage regulation equipment on the system can bring the voltage back to within tolerances. Overloaded circuits can result in undervoltages also.

# 2.5 Sustained interruptions

The decrease to zero of the supply voltage for a period of time in excess of 1 min is considered to be a sustained interruption. Voltage interruptions longer than 1 min. are often permanent in nature and require manual intervention for restoration. Sustained interruptions are specific power system phenomena and have no relation to the usage of the term outage. Outage, as defined in IEEE Std. 100-1992, does not refer to a specific phenomenon, but rather to the state of a component in a system that has failed to function as expected. Also, use of the term interruption in the context of power quality monitoring has no relation to reliability or other continuity of service statistics.

# 2.6 Voltage imbalance

Voltage imbalance (or unbalance) is defined as the ratio of the negative or zero sequence component to the positive sequence component. The negative or zero sequence voltages in a power system generally results from unbalanced loads causing negative or zero sequence currents to flow. Imbalance can be estimated as the maximum deviation from the average of the three-phase voltages or currents, divided by the average of the

three-phase voltages or currents, expressed in percent. In equation form voltage imbalance = 100 ' (max deviation from average voltage)/average voltage [6].

#### 2.7 Waveform distortion

Waveform distortion is a steady-state deviation from an ideal sine wave of power frequency principally characterized by the spectral content of the deviation. There are five primary types of waveform distortion as follows:

- DC offset

- Harmonics

- Interharmonics

- Notching

- Noise

#### 2.7.1 Harmonics

Harmonics are sinusoidal voltages or currents having frequencies that are integer multiples of the frequency at which the supply system is designed to operate (termed the fundamental frequency; usually 50 Hz or 60 Hz) [IEC 1000-2-1 (1990)]. Harmonics combine with the fundamental voltage or current, and produce waveform distortion. Harmonic distortion exists due to the nonlinear characteristics of devices and loads on the power system. These devices can usually be modeled as current sources that inject harmonic currents into the power system. Voltage distortion results as these currents cause nonlinear voltage drops across the system impedance. Harmonic distortion is a growing concern for many customers and for the overall power system due to the increasing application of

power electronic equipment. Harmonic distortion levels can be characterized by the complete harmonic spectrum with magnitudes and phase angles of each individual harmonic component. It is also common to use a single quantity, the Total Harmonic Distortion (THD), as a measure of the magnitude of harmonic distortion. Harmonic currents result from the normal operation of nonlinear devices on the power system.

Table 2.1. Categories of Power quality variation- IEEE Std. 1159-19995

|    | Categories                       | Typical<br>Duration | Typical<br>Magnitudes |

|----|----------------------------------|---------------------|-----------------------|

| 1. | Transients                       |                     |                       |

|    | 1.1 Impulsive                    | < 200 μs            |                       |

|    | 1.2 Oscillatory                  | < 30 cycles         |                       |

| 2. | <b>Short-Duration Variations</b> |                     |                       |

|    | 2.1 Sag                          |                     |                       |

|    | 2.1.1 Instantaneous              | 0.5-30 cycles       | 0.1-1.0 pu            |

|    | 2.1.2 Momentary                  | 30-120 cycles       | 0.1-1.0 pu            |

|    | 2.1.3 Temporary                  | 2 sec2 min.         | 0.1-1.0 pu            |

|    | 2.2 Swells                       |                     |                       |

|    | 2.2.1 Instantaneous              | 0.5-30 cycles       | 0.1-1.8 pu            |

|    | 2.2.2 Momentary                  | 30-120 cycles       | 0.1-1.8 pu            |

|    | 2.2.3 Temporary                  | 2 sec2 min.         | 0.1-1.8 pu            |

|    |                                  |                     |                       |

| 3. | <b>Long-Duration Variations</b>  |                     |                       |

|    | 3.1 Overvoltages                 | > 2 min.            | 0.1-1.2 pu            |

|    | 3.2 Undervoltages                | > 2 min.            | 0.8-1.0 pu            |

| 4. | Interruptions                    |                     |                       |

|    | 4.1 Momentary                    | < 2 sec.            | 0                     |

|    | 4.2 Temporary                    | 2 sec 2 min.        | 0                     |

|    | 4.3 Long-Term                    | > 2 min.            | 0                     |

| 5. | Waveform Distortion              |                     |                       |

|    | 5.1 Voltage                      | steady-state        | 0-20%                 |

|    | 5.2 Current                      | steady-state        | 0-100%                |

| 6. | Waveform Notching                | steady-state        |                       |

|    | Flicker                          | intermittent        | 0.1-7%                |

| •• |                                  |                     | 0.1 //0               |

### 2.8 Power quality standards

IEEE attempts to fix a set of standards to accurately define and quantify the quality of power supplied to the customer. But these standards vary with the type of load and the magnitude of the disturbance. The most important voltage quality indices are listed as follows:

The CBEMA Curve: In the early 1980's, the Computer Business Manufacturers Association (CBEMA, and now the ITI Council) established a susceptibility profile curve as shown in Fig. 2.1 to aid manufacturers in the design of power supply protection circuits. This curve has since become a standard reference within the industry. It describes an AC input voltage boundary, which typically can be tolerated (no interruption in function) by most Information Technology Equipment (ITE).

Fig. 2.1 The CMEBA plot for voltage tolerance

Total Harmonic Distortion (THD): Total Harmonics Distortion factor, which was defined as the ratio of the root-mean-square of the harmonic content to the root-mean-square of the fundamental quantity [6], which is expressed as a percent of the fundamental, that is

$$THD = 100 \sqrt{\sum_{n \neq 1, 3n} \left(\frac{V_n}{V_1}\right)^2}$$

(2.1)

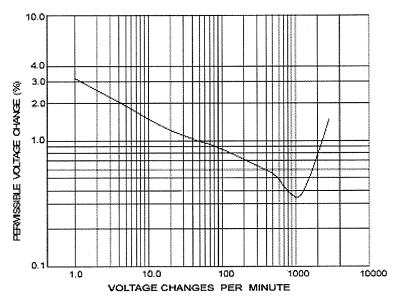

**Flicker Limit Curve**: This is used to assess the visibility that is produced by the voltage fluctuations, based on the voltage fluctuations definition. IEEE publishes this curve in the IEEE standards 519-1992 and 141-1993 as shown in Fig 2.2.

Short-term flicker indicator,  $P_{st}$ : The flicker severity evaluated over a short period (in minutes); Pst = 1 is the conventional threshold of irritability. A Pst value is obtained every 10 min. There are 144 Pst samples each day [3].

**Long-term flicker indicator,**  $P_{lt}$ : The flicker severity evaluated over a long period (a few hours) using successive Pst values [3]. Each  $P_{lt}$  value is calculated from 12 successive Pst values using this formula:

$$P_{lt} = \sqrt[3]{\frac{1}{12} \sum_{j}^{12} P_{stj}}$$

(2.2)

Fig. 2.2 Flicker limit curve of 519-1992 and 141-1993

## 2.9 Mitigation Methods Currently in Use

The remainder of this chapter provides an overview of each of the current mitigation technologies.

# 2.9.1 Transient Voltage Surge Suppression (TVSS)

TVSS devices are used to protect other equipment from the dangers of brief but potentially harmful voltage surges, which can be caused by lightning and the switching of inductive or capacitive devices [9]. TVSS devices are best understood as high-voltage, high-power semiconductors. At normal voltages, they conduct little or no electrical current. As voltage climbs, they begin conducting current. For example, a surge arrester designed for a 3 kV system may conduct 1 milliamp at 5 kV and 10,000 amps at 10 kV—a 7-fold increase in current magnitude after a mere doubling of applied voltage.

## 2.9.2 Uninterruptible Power Supplies (UPS)

UPSs use energy storage, usually in the form of lead-acid batteries, to store energy in the event that utility power is interrupted. Some newer UPS topologies use alternative energy storage such as flywheels, super conducting inductance ultracapacitors, or advanced chemical batteries. There are basically three different types of devices that are commonly referred to as UPSs: offline (standby), line-interactive, and online.

# 2.9.3 Dynamic Voltage Correction or Restoration (DVC, DVR)

Dynamic voltage restorers as shown in Fig. 1.1 augment voltage during voltage sags by adding missing voltage at critical times[7]. The theory is that because end users suffer many more voltage sags than outages, having a device that mitigates only sags can become cost-effective than conventional technologies. These devices can have different configuration and the focus of this research is to investigate one promising topology that achieves sags/swells compensation with minimum stored energy. Different kinds of energy storage devices are exist like superconductive magnetic energy storage (SMES), batteries, and capacitance. In fact, the capacity of the stored energy directly determines the ride-through capability therefore it can effect the duration of the sag which can be mitigate by the DVR.

## **CHAPTER 3**

# **Multilevel Inverter Topologies**

## 3.1 Introduction

Multilevel power conversion has been receiving increased attention in the past few years for high-power applications [8]. Numerous topologies and modulation strategies have been introduced and studied extensively for utility and drive applications in the recent literature [9]. These converters are suitable in high-voltage and high-power applications due to their ability to synthesize waveforms with an improved harmonic spectrum and attain higher voltages with a limited maximum device rating. In this multilevel Voltage Source Inverter (VSI) based dynamic voltage restorer (DVR) category, there are mainly two different system configurations. They are 1) diode-clamped converter configuration [11], and 2) cascading converter configuration [14]. In this chapter will analyze the first configuration in brief and focus will be given to the second configuration to develop DVR system.

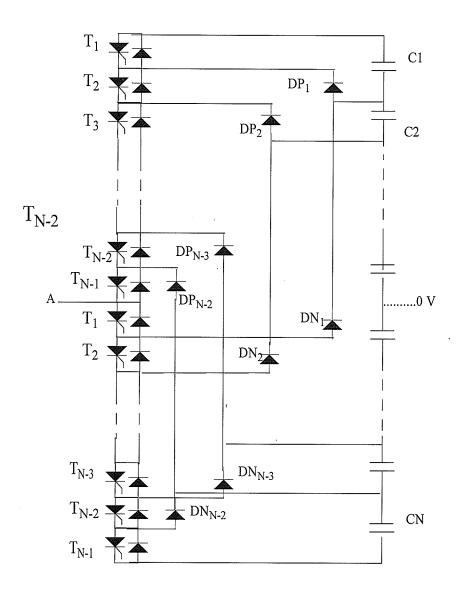

# 3.2 Diode-Clamped Multilevel Inverter

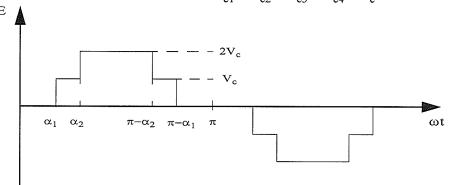

The diode-clamped multilevel inverter uses one DC bus subdivided into a number of voltage levels by a series string of capacitors [11]. A generalized structure of one phase of a 5-level inverter with a gate turnoff switch (GTO) is shown in Fig. 3.1. The dc capacitors are shared by the other phases, and possibly by the other bridges in higher pulse number designs. In a three-phase bridge configuration the number of levels in the line-to-line voltage will be 2N+1. The advantages of such a structure are each thyristor voltage stress will be limited to one capacitor voltage level, Vdc/(N-1), through clamping diodes. Furthermore, each GTO thyristor is well protected against overvoltage by the clamping action of the dc capacitors. There are N-1 complementary switch pairs in each phase, i.e., T<sub>1</sub>-T'<sub>1</sub>,  $T_2$ - $T'_2$ , ...,  $T_{N-1}$ - $T'_{N-1}$ . It should be mentioned that for each voltage step only one GTO thyristor must turn on and one GTO thyristor must turn off. For example, if  $T_1$  is off, then  $T_2, T_3, \dots, T_{N-1}$  and  $T_1$  are on, and the terminal voltage  $V_1$  is connected to the output terminal through  $Dp_1, T_2, T_3, \dots, T_{N-1}$  for positive current, or through  $T'_1$  and  $DN_1$  for negative currents. As described above, take one single phase into account, the five voltage levels could be achieved at the output terminal if the gate logic in Table 3.1 is followed, a stepped output voltage of the five level inverter shown in Fig. 3.2, which is a simple sum of the two rectangular waveforms. It should be noted that the clamping diodes are required to block different voltages, e.g. DP1 must block the voltage of a single dc level, V, while  $DP_{N-2}$  must block (N-2)Vc, assuming that all the capacitor voltages are equal to Vc.

Fig. 3.1 One phase of diode-clamped N-level inverter

| <b>Table 3.1.</b> The | Gate Logic for Five-level I | Diode-clamped Inverter |

|-----------------------|-----------------------------|------------------------|

|                       |                             |                        |

| output           | The state of GTO thyristors |       |                       |       |                 |     |                 |     |

|------------------|-----------------------------|-------|-----------------------|-------|-----------------|-----|-----------------|-----|

| $(E_a)$          | $T_1$                       | $T_2$ | <b>T</b> <sub>3</sub> | $T_4$ | T' <sub>1</sub> | T'2 | T' <sub>3</sub> | T'4 |

| $+2V_{c}$        | 1                           | 1     | 1                     | 1     | 0               | 0   | 0               | 0   |

| $+V_c$           | 0                           | 1     | 1                     | 1     | 1               | 0   | 0               | 0   |

| 0                | 0                           | 0     | 1                     | 1     | 1               | 1   | 0               | 0   |

| $-V_c$           | 0                           | 0     | 0                     | 1     | 1               | 1   | 1               | 0   |

| -2V <sub>c</sub> | 0                           | 0     | 0                     | 0     | 1               | 1   | 1               | 1   |

In the above Table we assumed that  $V_{c1} = V_{c2} = V_{c3} = V_{c4} = V_c$ .

Fig. 3.2 Five level Diode-clamped Inverter Waveform Voltage

## 3.3 Cascade Multilevel Inverters

## 3.3.1 Circuit and Working Principle

The cascade inverter is made up from series connected single phase full bridge inverters, each with their own isolated dc bus [12, 13]. Fig. 3.3 illustrates the connection diagram for a wye connection 7-level inverters using the cascade voltage source H-bridge inverters. It is clear from Fig. 3.3 that to have M-level cascade multilevel inverters we need  $\left(\frac{M-1}{2}\right)$  H-bridge units in each phase. Each H-bridge inverter can generate three level outputs,  $V_{dc}$ , 0, and  $-V_{dc}$ . Fig. 3.4 shows the structure of one unit of H-bridge inverter and

its three level output voltage waveform. And the output voltage of M-level inverter is a simple sum of the M-rectangular waveforms from each H-bridge inverter for each phase. There are many switching techniques possible to control the output voltage of the H-bridge inverter. Four of them will be discussed in a later section: the Fundamental Frequency Switching (FFS) method and three different Pulse Width Modulation (PWM) techniques.

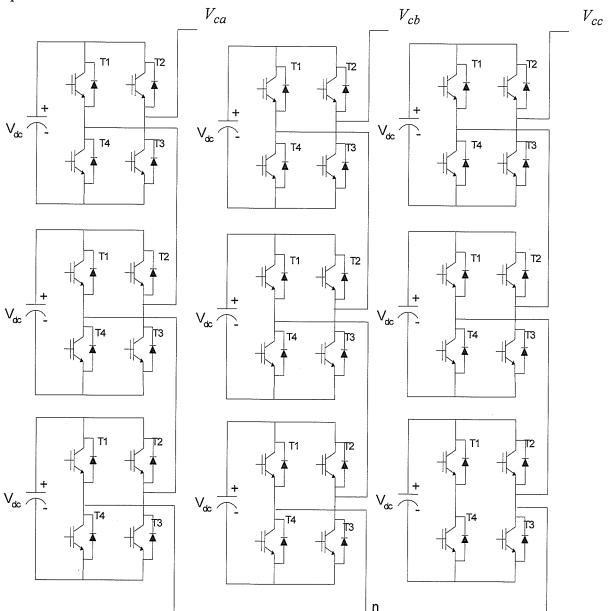

Fig. 3.3 The Three Phase Y-structure 7-level Cascade Inverter

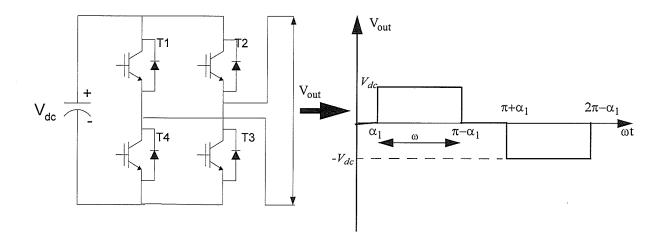

Fig. 3.4. The H-bridge Inverter and its Three Level Output Voltage Waveform

## 3.3.2 The Advantage of Cascade Multilevel Inverter

There are mainly three types of multilevel inverters, the two most common being the Cascade type and the Diode-clamped type. Listed below are some of the advantages of the cascade type

- 1- The diode-clamped configuration requires a very large number of clamping diodes whereas the cascade configuration requires a smaller number of diodes.

- 2- In case of cascade configuration packaging and physical layout is very simple in comparison with diode-clamped configuration due to its modular structure. It is constructed by cascading several voltage source H-bridge inverters.

3-The dc voltage unbalancing between the capacitors can be more severe in the case of the diode-clamped configuration in comparison with the cascade configuration. This is because in the cascade topology, each H-bridge can be controlled independently.

# 3.3.3 Output Voltage Control of the Cascade Multilevel Inverter

It is clear by examining the cascade inverter structure as described in Section 3.3.1 that the H-bridge inverter forms the building block of the cascade multilevel inverter, therefore by controlling the voltage of each individual H-bridge, the total output voltage of the cascade inverter can be regulated. There are mainly three methods to control the output voltage of the H-bridge inverter as in Fig. 3.4. These are listed below:

- 1- Controlling the output voltage pulse width  $(\omega)$  by Fundamental Frequency Switching (FFS) method or PWM technique while keeping the dc voltage fixed. This can be done by controlling the firing angle value of the IGBT or by controlling the modulation index in case of PWM is used as will be discussed later.

- 2- Controlling the dc voltage ( $V_{dc}$ ) while keeping the output voltage pulse width ( $\omega$ ) fixed.

- 3- Controlling both the dc voltage ( $V_{dc}$ ) and the output voltage pulse width ( $\omega$ ).

In this thesis the first method is used because one objective of the proposed method is to maintain the dc voltage  $(V_{dc})$  across each H-bridge fixed.

#### 3.4 Fundamental Frequency Switching (FFS) of IGBT'S

Using the fundamental frequency switching (FFS) method [14], each IGBT thyristor is switched on and off once during a power frequency (60 Hz) cycle.

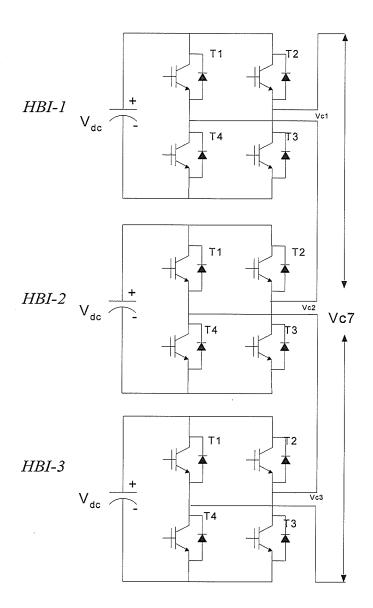

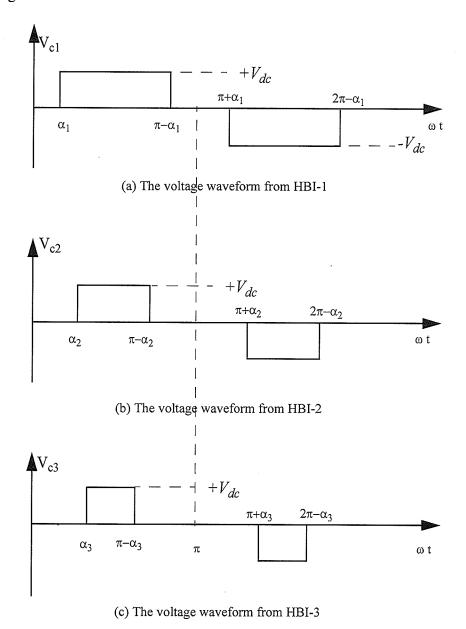

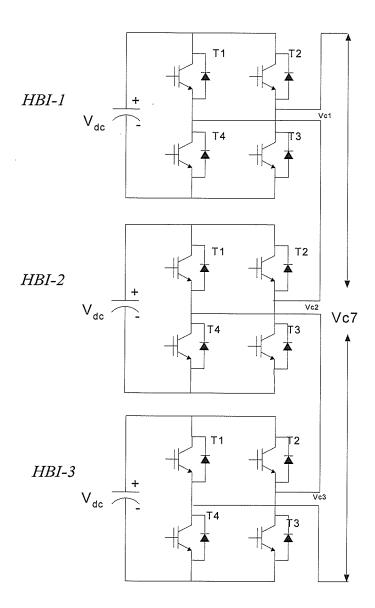

As mentioned earlier, the H-bridge inverter forms the building block of the cascade multilevel inverters. For simplification let us consider one phase 7-level cascade multilevel inverter as shown in Fig. 3.5, which consists of three H-bridge inverters [(7-1)/2)) =3] called HBI-1, HBI-2 and HBI-3.

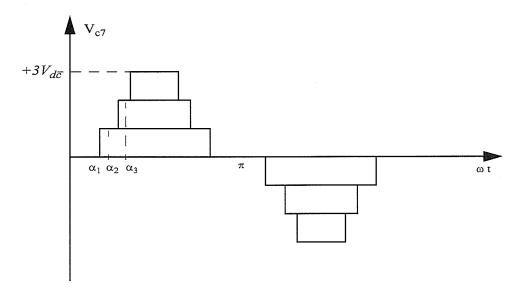

A 7-level voltage waveform can be generated at the output terminal of the 7-level, single phase cascade inverter shown in Fig. 3.5, by applying FFS technique to each H-bridge inverter. Let us start by examining the first H-bridge inverter (HBI-1). It can be seen that the main switching devices  $T_1$ ,  $T_2$ ,  $T_3$  and  $T_4$  can be any self-commutated devices such as a Gate-Turn-Off thyristors (IGTO) or an IGBT transistors (for lower rating). In one period T, each switch must be turned on for a half period [0,T/2] and turned off for the remaining period [T/2,T]. For each H-bridge, consider a half cycle duration( $\pi$  radian). The switching sequence is as follows: Turnon  $T_1$  at  $-\alpha_1$ ,  $T_4$  at  $(\pi-\alpha_1)$ ,  $T_3$  at  $\alpha_1$  and  $T_2$  at  $(\pi+\alpha_1)$ . Turnoff  $T_1$  at  $(\pi-\alpha_1)$ ,  $T_4$  at  $(2\pi-\alpha_1)$ ,  $T_3$  at  $(\pi+\alpha_1)$ , and  $T_2$  at  $(2\pi+\alpha_1)$ . By this way three level outputs +  $V_{dc}$ , 0, and -  $V_{dc}$  can be generated, as shown in Fig. 3.6(a). If the same role is applied to other two H-bridge inverters HBI-2 and HBI-3 but with different firing angles  $\alpha_2$  and  $\alpha_3$ , where  $\alpha_1 < \alpha_2 < \alpha_3 < \frac{\pi}{2}$ , then

Fig. 3.5: One Phase of a 7-Level Cascaded Multi-level Inverter

an output voltage can be generated from each H-bridge as shown in Fig. 3.6 (b & c). The sum of the three rectangular waveforms generated from HBI-1, HBI-2 and HBI-3 is then

the total output voltage  $V_{c7}$  of Fig. 3.5. The 7-level voltage waveform can be achieved as shown in Fig. 3.7.

Fig. 3.6 The Output Voltage Waveform for Each H-bridge

Fig. 3.7 The 7-level Stepped-waveform

Performing the Fourier Transform for this waveform, the total output voltage can be obtained as follow:

$$E(\omega t) = V_c(\alpha_1, \omega t) + V_c(\alpha_2, \omega t) + V_c(\alpha_3, \omega t)$$

Where

$$V_c(\alpha_x, \omega t) = \frac{4V_c}{\pi} \sum_n \frac{1}{n} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{2} - n\alpha_x\right) \sin(n\omega t)$$

Where

$$x = 1, 2 \text{ or } 3$$

$n = 1, 3, 5, 7, \dots$

$$E(\omega t) = \frac{4V_c}{\pi} \sum_{n} \frac{1}{n} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{2} - n\alpha_1\right) \sin(n\omega t) + \frac{4V_c}{\pi} \sum_{n} \frac{1}{n} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{2} - n\alpha_2\right) \sin(n\omega t)$$

$$\frac{4V_c}{\pi} \sum_{n} \frac{1}{n} \sin\left(\frac{n\pi}{2}\right) \sin\left(\frac{n\pi}{2} - n\alpha_3\right) \sin(n\omega t)$$

$$E(\omega t) = \frac{4V_c}{\pi} \sum_{n} \frac{1}{n} [\cos(n\alpha_1) + \cos(n\alpha_2) + \cos(n\alpha_3)] \sin(n\omega t)$$

Where n = 1, 3, 5, 7,...........

From the formula (3.1), the magnitude of the Fourier coefficients can be obtained, which is equal to the magnitude of the  $n^{th}$  harmonic normalized to  $V_c$  as follows:

$$H(n) = \frac{4}{\pi n} [\cos(n\alpha_1) + \cos(n\alpha_2) + \cos(n\alpha_3)]$$

(3.2)

Where n = 1, 3, 5, 7,...

As mentioned before the angles  $\alpha_1$ ,  $\alpha_2$ , and  $\alpha_3$  can be chosen arbitrarily subject to the constraint of  $\alpha_1 < \alpha_2 < \alpha_3 < \frac{\pi}{2}$ . If suitably selected, these degrees of freedom can be used to obtain a lower harmonic content or a larger fundamental voltage. The degrees of freedom, in choosing the switching angle are equal to ((M-1)/2), where M is the level of the multilevel inverter. In the present case with M=7, the system has three degrees of freedom. Therefore  $\alpha_1$ ,  $\alpha_2$ , and  $\alpha_3$  can be selected at such values to control the magnitude values of any three harmonics. To entirely eliminate the  $n^{th}$  harmonic Equation (3.2) is set to zero for that particular value of n. For example, if it is decided to eliminate the  $5^{th}$ ,  $7^{th}$  and the  $11^{th}$  harmonics, three equations can be written, by substituting n=5, 7, 11 in Equation (3.2):

$$\cos(5\alpha_1) + \cos(5\alpha_2) + \cos(5\alpha_3) = 0$$

$$\cos(7\alpha_1) + \cos(7\alpha_2) + \cos(7\alpha_3) = 0$$

$$\cos(11\alpha_1) + \cos(11\alpha_2) + \cos(11\alpha_3) = 0$$

(3.3)

The Equations (3.3) are nonlinear transcendental equations which can be solved by an iterative method. By using Newton-Raphson method to solve these equations, different sets of solutions can be obtained. It is obvious that the magnitude of the fundamental component and the harmonic content in the inverter output voltage will change with these switching angles as listed in Table 3.2. In other words, the inverter waveform can be optimized to achieve the larger fundamental component and / or best Total Harmonics Distortion (THD) factor which was defined as the ratio of the root-mean-square of the harmonic content to the root-mean-square of the fundamental quantity [12], which is expressed as a percent of the fundamental, that is:

$$THD = 100 \sqrt{\sum_{n \neq 1, 3n} \left(\frac{V_n}{V_1}\right)^2}$$

(3.4)

Table 3.2. Calculated Switching Angles for Different modulation index

| $\alpha_1$ (degree) | $\alpha_2$ (degree) | $\alpha_3$ (degree) | Fundamental component pu | THD  |

|---------------------|---------------------|---------------------|--------------------------|------|

| 7.09                | 15.68               | 36.17               | 0.9                      | 5.9% |

| 22.77               | 49.38               | 64.57               | 0.85                     | 9%   |

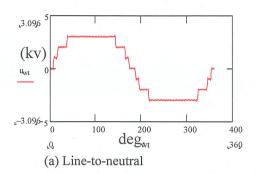

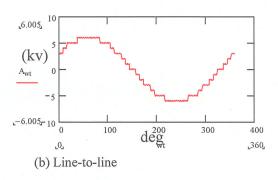

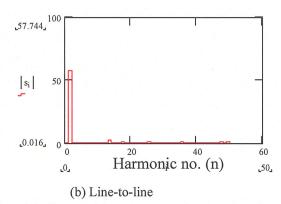

Fig. 3.8 shows the line-to-neutral output voltage waveform of 7-level cascaded inverter using the FFS method with  $\alpha_1$ = 7.09 degrees,  $\alpha_2$ = 15.68 degrees, and  $\alpha_3$ = 36.17 degrees. Fig.3.9 illustrates the Fourier analysis of the obtained waveforms. From Fig.3.8(a), it can be seen that the 5, 7, and 11 harmonic orders can be eliminated. The triplen order harmonics, such as third, and ninth, in the line-to-neutral voltage waveform are allowed to exist in

the line-to-neutral waveforms as they will automatically be cancelled in the line-to-line waveform as shown in the spectrum of Fig. 3.9 b.

Fig. 3.8: line-to-neutral& line-to-line output voltage waveform of 7-level cascaded inverter using the FFS method

Fig. 3.9: Harmonic spectra for line-to-neutral & line-to-line output voltage waveform of 7-level cascaded inverter using the FFS method

# 3.5 Pulse Width Modulation (PWM) Switching Techniques

Many multilevel PWM techniques [14] have been studied and investigated during the past two decades. Generally, these techniques are the extensions of the traditional two-level PWM strategies. The PWM techniques can be classified into the two categories: the triangle intersection techniques and the direct digital techniques. Recently, with the development of digital technology, the space vector PWM is widely used, due to not only it's relatively easy hardware implementation, but also due to its features of good dc-link voltage utilization and low current

ripple. But this method has a very significant drawback that if the voltage level is more than five, the control algorithm becomes too complex to implement. So it is reasonable to adapt the triangle intersection techniques in applications with a higher number of levels. In this section the principles and the features of three kinds of triangle intersection PWM techniques applied to the cascade multilevel inverter will be described.

# 3.5.1 Subharmonic Pulse Width Modulation (SHPWM)

The SHPWM [13] method is an extensions of the traditional two-level PWM strategies, but instead of using one triangular carrier signal it use several triangular carrier signals with only one modulation waveform per phase. For an n-level inverter, n-1 triangular carriers of the same frequency  $f_c$  and peak-to-peak amplitude  $A_c$ , are arranged so that they fully occupy are contiguous bands in the range of +Vdc and -Vdc. A modulation waveform centered in the middle of the carrier set is then compared with each carrier to determine the voltage level that the converter should switch to. In n-level inverters, the amplitude modulation index (m) and the frequency index (K) are defined as:

$$m = \frac{A_m}{(n-1)A_c}$$

$$K = \frac{f_c}{f_m}$$

(3.5)

Where  $A_m$ : The amplitude of the modulation wave

A<sub>c</sub>: The amplitude of the carrier wave

$f_m$ : The frequency of the modulation wave

f<sub>c</sub>: The frequency of the carrier wave

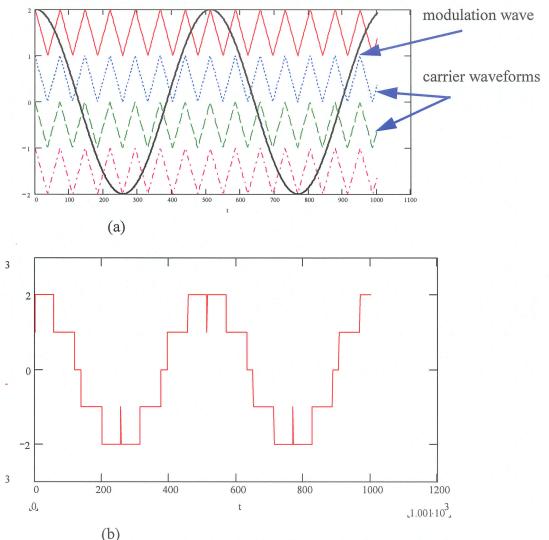

Fig. 3.10(a) shows the principle of the SHPWM for n=5, k=7, and m=1.0 from the Fig.. It can be seen that there are 4 carrier waveforms, the two carrier which are above the zero reference controlling the switching of the HB-1 and HB-2 during the positive period of the fundamental cycle, while the other two carrier which are below the zero reference take care of the negative period as shown in Fig. 3.10(a).

Fig. 3.10 The Principle of the SHPWM for n=5, k=7 and m =1.0

Note that for small m, HB-2 may never switch however, to make sure each H-bridge faces equal stress, the switching patterns are rotated every cycle.

# 3.5.2 Triangular Carrier Phase Shifting PWM Technique (PS PWM)

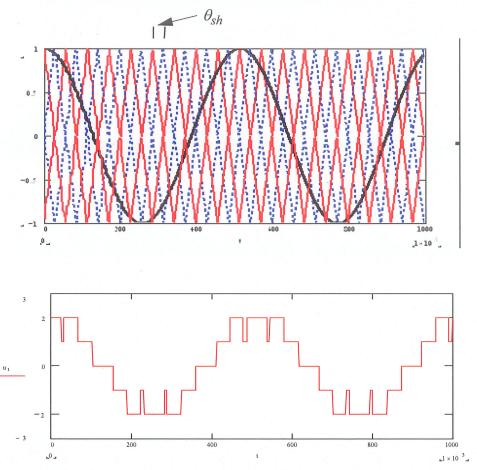

For the cascaded inverters, phase-shifted carrier PWM (PSPWM) is the most common strategy. The PS PWM can be considered as a generalization of the traditional pulse width modulation principles, but The PS PWM technique uses 2(n-1) carrier signals of the same amplitude and frequency which are phase shifted by  $\theta_{sh} = \frac{\pi}{n}$  to one another to generate the n-level inverter output voltage (n is the number of H-bridge inverters in a multilevel phase leg). This strategy leads to cancellation of all carrier and associated sideband harmonics up to the 2nth carrier group. This effective increase of sampling frequency is highly interesting, since it can be used effectively to reduce the switching frequency in each switching leg. Fig. 3.11 illustrates the carrier and reference arrangements for a single multilevel phase leg of a five level cascaded structure.

Fig. 3.11 The Principle of the PS-PWM for n=5, k=9 and m =1.0

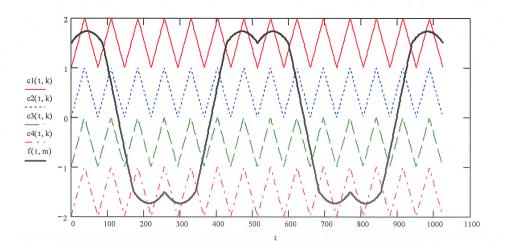

# 3.5.3 Switch Frequency Optimal PWM

Switch Frequency Optimal PWM (SFO PWM) [14] is something like the SHPWM, except that the modulation waveform for each phase are obtained by subtracting the means instantaneous average of the maximum and minimum of the three reference voltage (V<sub>a</sub>, V<sub>b</sub>, V<sub>c</sub>) as shown in (3.6) from each of the individual reference as shown in (3.7). The addition of the zero sequence (triplen harmonic) voltage continuously centers all of the three reference waveforms in the carrier band. This method can only be used for three

phase system, and it has the advantage of increasing the modulation index by 15% before over modulation occurs.

$$V_{zero} = \frac{max(V_{a}, V_{b}, V_{c}) + min(V_{a}, V_{b}, V_{c})}{2}$$

$$V_{a}^{"} = V_{a} - V_{zero}$$

$$V_{b}^{"} = V_{b} - V_{zero}$$

$$V_{c}^{"} = V_{c} - V_{zero}$$

(3.6)

The algorithm above is convenient for microprocessor implementation and also analog implementation. The principle of SFO PWM is illustrated in Fig. 3.12.

Fig. 3.12 The Principle of the SOF PWM for n=5, k=7 and m=1.0

# 3.6 Comment on Different Techniques of PWM

- SHPWM and PS PWM are extensions of traditional triangle carrier two-level

SPWM strategies to multilevel.

- PS PWM is superior to SHPWM, this is due to it's higher effective carrier frequency,

which is n times of carrier frequency of the SHPWM for n-level multilevel converter. That means the harmonics of PS PWM are the lowest.

- The modulation index SFO-PWM method can be increased by about 15% before over modulation due to its modified modulation waveform.

- PS PWM especially suitable for cascaded multilevel inverters. It has better control effect as each phase can be controlled independently.

• In general it can be concluded that in multilevel triangular carrier PWM strategies, there are at least three control degrees of freedom in triangular carrier: frequency, phase and amplitude and also at least three control degrees of freedom in modulation waveform: amplitude, frequency and zero sequence. Composite of some of these control degrees of freedom can generate a good number of PWM strategies.

# 3.7 Comparison between FFS Method and PWM Techniques

In this section FFS method will be compared with other two types of PWM methods the SHPWM method and SFO PWM method as the PS PWM is special case of the SHPWM, our comparison are based on reducing Total Harmonic Distortion (THD), power loses, and transient response. Off course, the best control strategy is the one which has the lowest harmonic distortion, lowest power loses, and the faster transient response.

#### 3.7.1 Total Harmonic Distortion (THD)

THD is a measure of voltage quality. It is important to a voltage waveform with a low THD. To show the performance of the various techniques FFS method, the SH-PWM and SFO-PWM techniques with respect to the Total Harmonics Distortion (THD) of the output line voltage, the sample Mathcad programs are listed in Appendix A. By running the above mention programs for 5-level inverters, and 7-level inverters, the THD was calculated with different modulation index for each switching technique. The results are sum-

marized as shown: Table 3.3 for FFS method, Table 3.4 for SH-PWM technique, and Table 3.5 for SFO-PWM technique.

Table 3.3: Typical Calculation Results Using FFS

| Waveform level | THD   |

|----------------|-------|

| 5              | 10.9% |

| 7              | 7.6%  |

Table 3.4: Typical Calculation Results Using SH-PWM

| Waveform level | Frequency ratio (k) | Modulation<br>Index (m) | THD   |

|----------------|---------------------|-------------------------|-------|

|                |                     | 1                       | 12.1% |

|                |                     | 0.9                     | 14%   |

|                |                     | 0.85                    | 15.2% |

| 5              | 9                   | 0.8                     | 15.7% |

|                |                     | 0.7                     | 19.6% |

|                |                     | 0.6                     | 20.3% |

|                |                     | 0.5                     | 33.0% |

|                |                     | 0.4                     | 37.6% |

|                |                     | 1                       | 6.8%  |

|                |                     | 0.9                     | 10.1% |

|                |                     | 0.85                    | 11.6% |

| 7              | 9                   | 0.8                     | 9.5%  |

|                |                     | 0.7                     | 14.5% |

|                |                     | 0.6                     | 14%   |

|                |                     | 0.5                     | 11.6% |

|                |                     | 0.4                     | 16.6% |

Table 3.5: Typical Calculation Results Using SFO-PWM

| Waveform level | Frequency ratio (k) | Modulation<br>Index (m) | THD   |

|----------------|---------------------|-------------------------|-------|

|                |                     | 1                       | 13.1% |

|                |                     | 0.9                     | 13.4% |

|                |                     | 0.85                    | 16%   |

| 5              | 9                   | 0.8                     | 18.4% |

|                | -                   | 0.7                     | 19.2% |

|                |                     | 0.6                     | 27%   |

|                |                     | 0.5                     | 35.6% |