# A VHSIC HARDWARE DESCRIPTION LANGUAGE COMPILER FOR LOGIC CELL ARRAYS

by

Bing Liu

#### A thesis

presented to the University of Manitoba

in partial fulfillment of the

requirements of the degree of

Master of Science

in Electrical and Computer Engineering

Winnipeg, Manitoba, Canada © Bing Liu, January 1990

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

> The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

> The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada-de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-71751-3

# A VHSIC HARDWARE DESCRIPTION LANGUAGE COMPILER FOR LOGIC CELL ARRAYS

BY

BING LIU

A thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements of the degree of

MASTER OF SCIENCE

#### © 1990

Permission has been granted to the LIBRARY OF THE UNIVER-SITY OF MANITOBA to lend or sell copies of this thesis. to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

#### **ABSTRACT**

This thesis presents a development of a VHSIC Hardware Description Language (VHDL) compiler for Logic Cell Arrays (LCAs). First, the concept of electronic circuit engineering and the electronic circuit development cycle using computer aided engineering (CAE) tools are reviewed; and the motivation of this research work is provided. Then, the architecture, design methodology and the significance of LCA are described. Thirdly, the VHDL is briefly reviewed and a VHDL architectural description subset for LCA is defined as the input of the compiler; the Xilinx Netlist Format (XNF) is chosen as the target of the compiler. Finally, the development, testing and verification of the VHDL compiler for LCA is described. Two of the examples implemented from the VHDL descriptions are presented to demonstrate the compiler.

#### **ACKNOWLEDGEMENTS**

I wish to express my sincere thanks to Dr. Witold Kinsner, my advisor, and Dr. Robert D. McLeod for their excellent guidance, endurable motivation and consistent support throughout the course of this research.

My thanks go to Dr. William L. Kocay for his comments and suggestions on my thesis. I am also grateful to Mr. J. Dickson, who helped me to simulate one of the examples, and all the other fellow students for their help.

I would also like to thank my wife who helped me a great deal during my writing of this thesis, my parents, and family for their encouragement.

The financial support of this research work provided by the National Science and Engineering Research Council (NSERC) of Canada through Dr. Kinsner's grant and Dr. McLeod's grant, Canadian Microelectronics Corporation, and the University of Manitoba is gratefully acknowledged. The LCA Xilinx Netlist Format Specification and the LCA External Netlist Tool Kit provided by Xilinx Inc. is also acknowledged.

# TABLE OF CONTENTS

|                                                    | Page |

|----------------------------------------------------|------|

| ABSTRACT                                           | ii   |

| ACKNOWLEDGEMENT                                    | iii  |

| TABLE OF CONTENTS                                  | iv   |

| LIST OF FIGURES                                    | vi   |

| LIST OF TABLES                                     | viii |

| LIST OF ABBREVIATIONS                              | ix   |

| CHAPTER 1: INTRODUCTION                            | 1    |

| 1.1. Electronic Circuit Engineering                | 3    |

| 1.1.1. Electronic Circuit Design                   |      |

| 1.1.2. Programmable Logic Devices                  |      |

| 1 1 3 Prototyping                                  | 0    |

| 1.9 Mativation                                     | 9    |

| 1.3. Thesis Objectives ·····                       | 10   |

| 1.4. Thesis Structure                              | 11   |

| CHAPTER 2: XILINX LOGIC CELL ARRAYS                | 12   |

| 2.1 Architecture of Xilinx Logic Cell Attays       | 13   |

| 2.1.1 Configurable Logic Blocks                    | 10   |

| 2.1.2 Input/Output Blocks                          | 10   |

| 2.1.3 Programmable Interconnections                | 10   |

| 2.2 Villar I CA Davidae                            | 19   |

| 2.3 I CA Design Methodology                        | 21   |

| 2.3.1 Design Entries                               | . 22 |

| 2.3.2. Design Implementation                       | . 24 |

| 2.3.5 Design Verification                          | • 23 |

| 2.4. Summary ·····                                 | · 26 |

| THE PARTY WAS THE PRIVATE DESCRIPTION I ANCHAG     | E 27 |

| CHAPTER 3: THE VHSIC HARDWARE DESCRIPTION LANGUAGE | . 28 |

| 3.1. Features of VHDL                              | . 29 |

| 3.1.1. Design Entity                               |      |

|                                                           | 29       |

|-----------------------------------------------------------|----------|

| 3.1.2. Interface Description                              | 30       |

| 3.1.3. Body Description                                   | 30       |

| 3.1.3.1. Architectural Description                        | 31       |

| 3.1.3.2. Dataflow Description                             | 32       |

| 3.1.3.3. Behavioural Description ······                   | 34       |

| 3.1.4. Types                                              |          |

| 3.1.5. Signals                                            | 35<br>36 |

| 3.1.6. Packages ·····                                     | 37       |

| 3.2. Supported VHDL Subset                                |          |

| 3.2.1. Input/Output Pin Description                       | 37<br>38 |

| 3.2.2. Predefined Types for LCA                           | 38       |

| 3.3. Summary                                              | 20       |

| CHAPTER 4: A VHDL COMPILER FOR LCA DESIGN                 | 40       |

| 4.1. Lavigal Analysis                                     | 44       |

| 4 1 1 FX — A Lexical Analyzer Generator ······            | 45       |

| 4.2 Parcing                                               | 47       |

| 4.2.1 VACC — Yet Another Compiler Compiler                | 47       |

| 4.2 Stack Machine                                         | 49       |

| 4.2.1 Stack Machine Instructions                          | 50       |

| 4.3.2. Internal VHDL Representation (IVHDL)               | 53       |

| 4.4 Yiling Netlist Format Generation                      | 54       |

| 4.4.1. Internal Xilinx Netlist Format (IXNF) and WriteNet | 54       |

| 4.5 Flattening                                            | 54       |

| CHAPTER 5: IMPLEMENTATION, TESTING AND VERIFICATION       | 56       |

| 5.1 Test 1. 16 bit I iner Feedback Shift Register         | 57       |

| 5.2. Test 2: 4-bit ALU                                    | 61       |

| J.Z. 168t Z. 4-0it ALO                                    |          |

| CHAPTER 6: CONCLUSIONS AND RECOMMENDATIONS                | 67       |

| REFERENCES                                                | 70       |

|                                                           |          |

| APPENDIX A: EXAMPLES AND SIMULATION RESULTS               | 74       |

| APPENDIX B: VHDL USER'S GUIDE                             | 97       |

|                                                           |          |

| APPENDIX C: KEYWORD LIST                                  | 111      |

| APPENDIX D: GRAMMAR OF SUPPORTED VHDL SUBSET              | 112      |

| APPENDIX E: STANDARD XNF LIBRARIES LIST                   | 116      |

| ADDENDIY F. PROGRAM LIST                                  | 120      |

| A C C M (W 1 1 2 M 1 M 1 M 1 M 1 M 1 M 1 M 1 M 1 M        |          |

# LIST OF FIGURES

| Figur | e                                                                     | Page |

|-------|-----------------------------------------------------------------------|------|

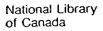

| 1.1.  | Electronic circuit design process                                     | 4    |

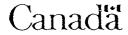

| 1.2.  | Electronic circuit development cycle using CAE tools                  | 6    |

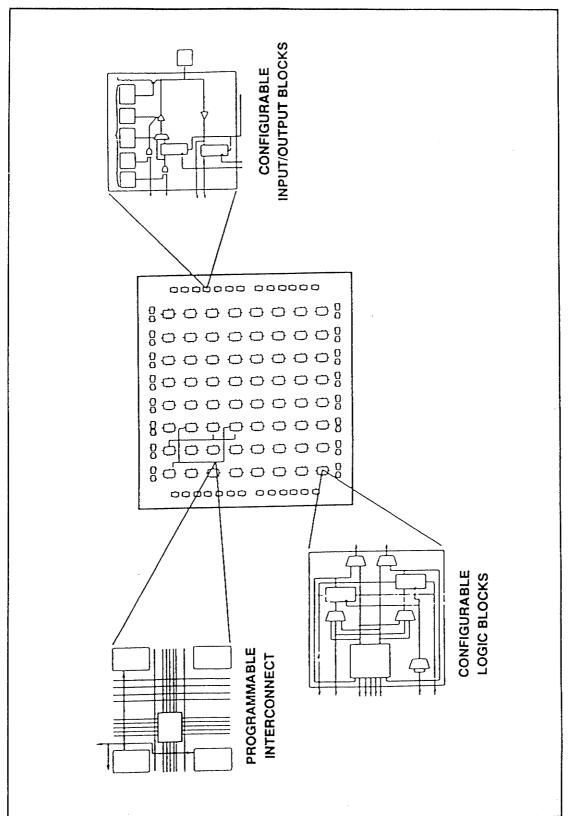

| 2.1.  | The architecture of Logic Cell Arrays                                 | 14   |

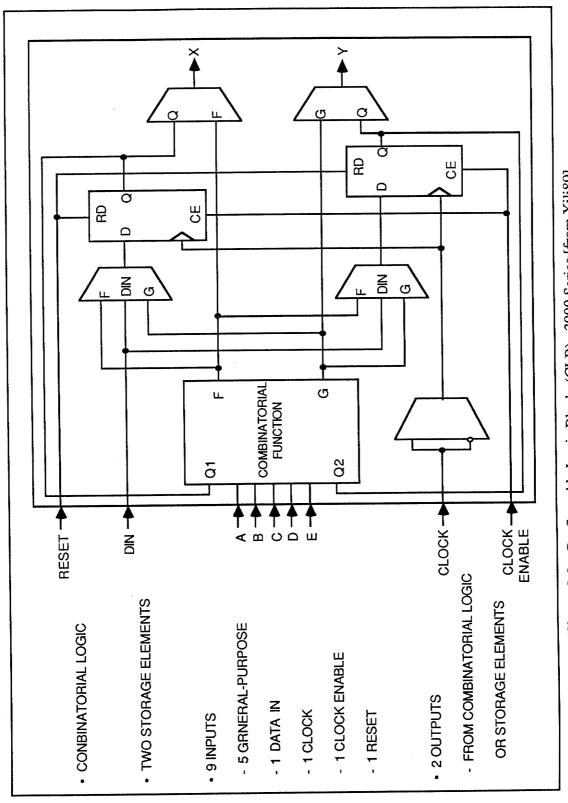

| 2.2.  | Configurable Logic Block (CLB): 3000 Series                           | 15   |

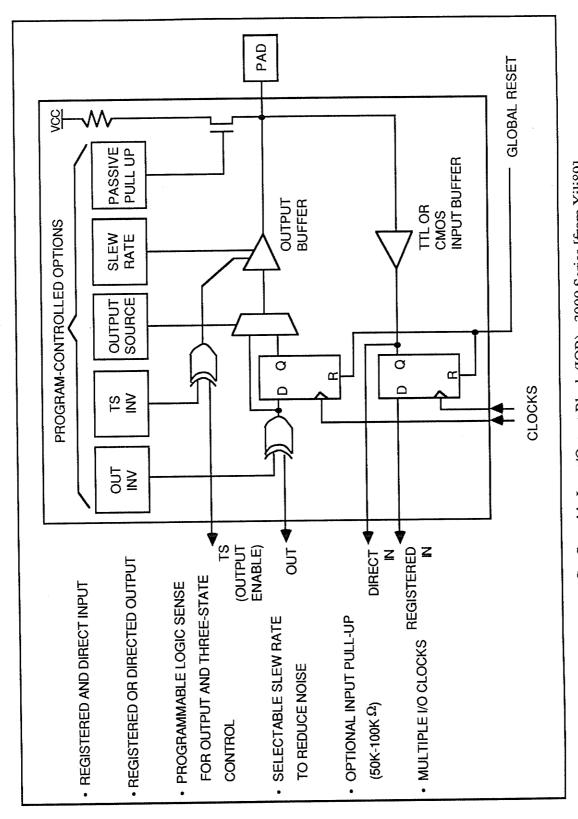

| 2.3.  | Configurable Input/Output Block (IOB): 3000 Series ······             | 16   |

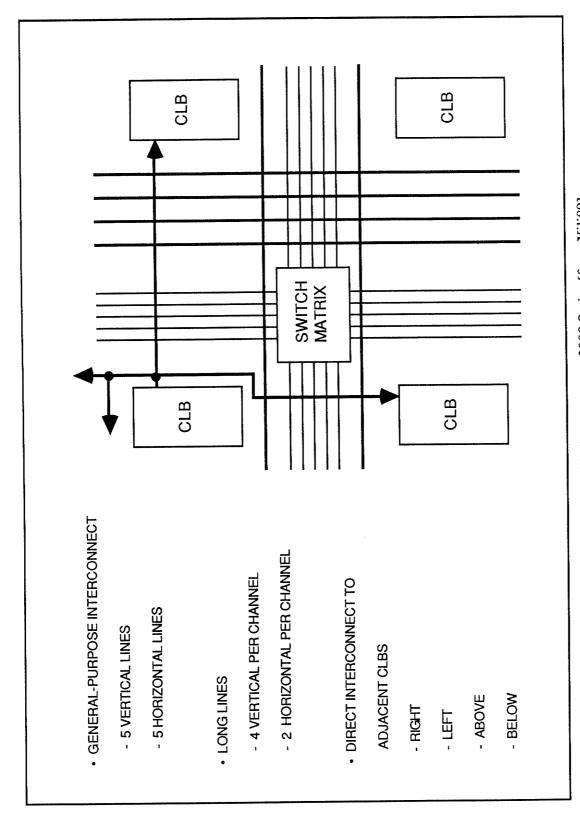

| 2.4.  | Programmable Interconnections: 3000 Series                            | 17   |

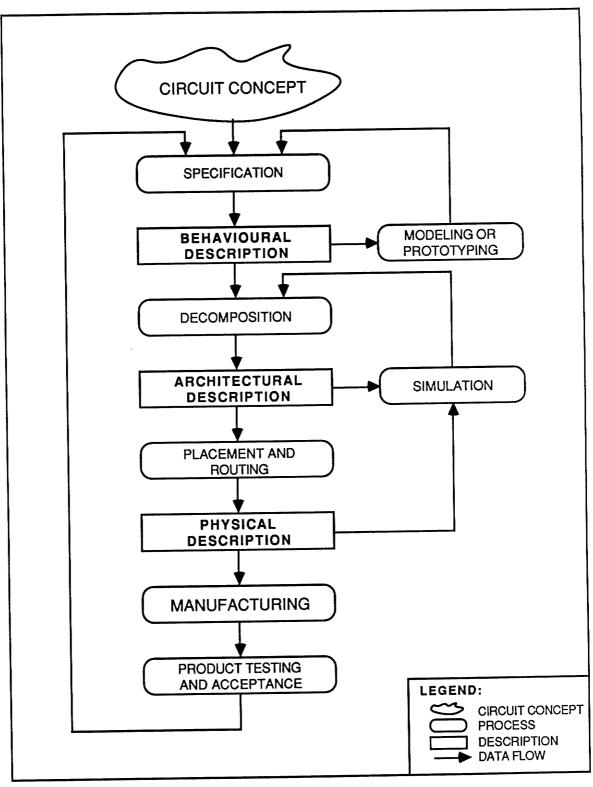

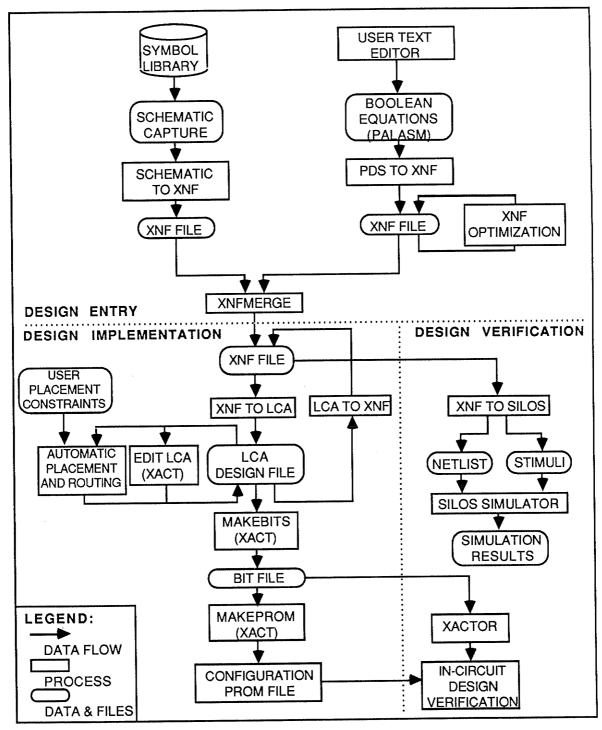

| 2.5.  | LCA design process ·····                                              | 23   |

| 3.1.  | Interface description of a full adder                                 | 30   |

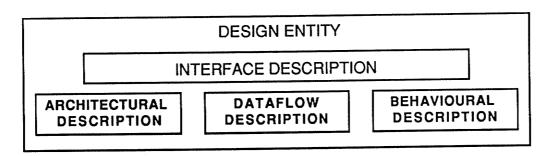

| 3.2.  | Body descriptions of design entity                                    | 30   |

| 3.3.  | Architectural body description of a full adder                        | 31   |

| 3.4.  | Dataflow body descriptions of a full adder                            | 32   |

| 3.5.  | Behavioural body description of a AND gate with interface description | 33   |

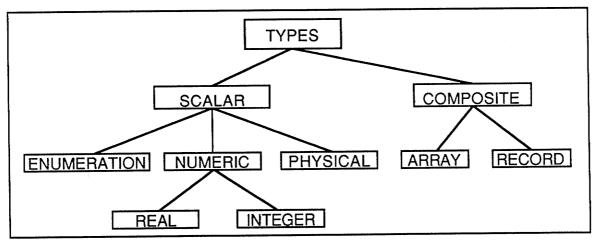

| 3.6.  | VHDL type classification tree                                         | 34   |

| 3.7.  | Type declaration                                                      | 35   |

| 3.8.  | Signal declaration                                                    | 36   |

| 3.9.  | Package declaration                                                   | 36   |

| 3.10. | Interface description of a full adder with pin association            | 38   |

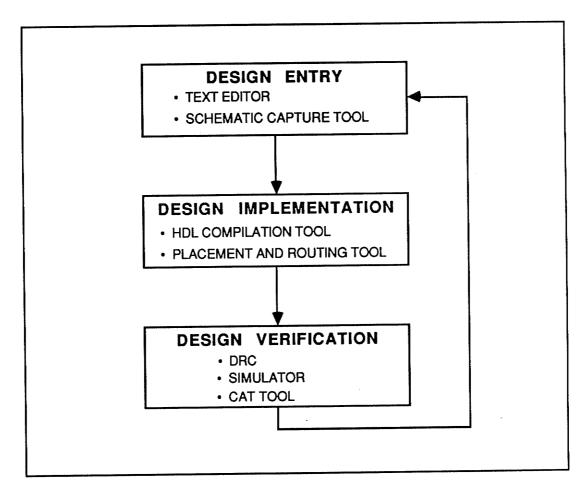

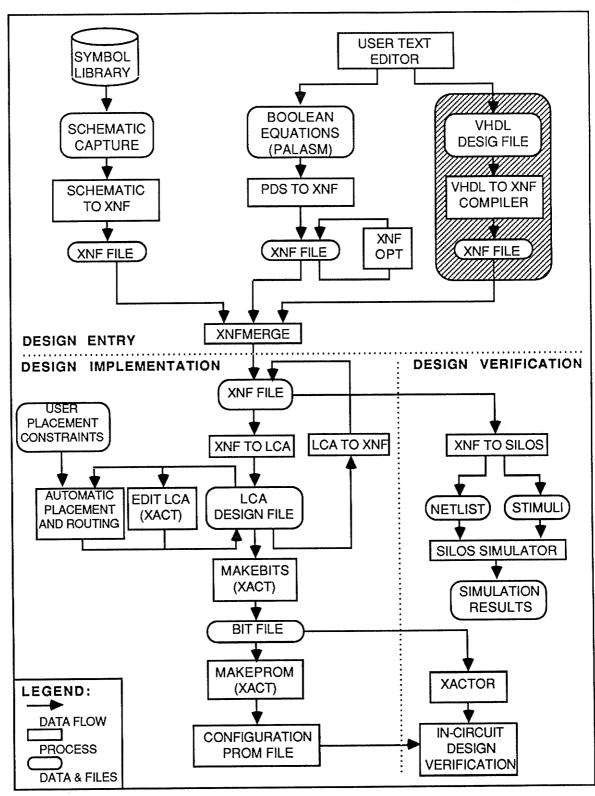

| 4.1   | The position of the VHDL compiler in the LCA design process           | 41   |

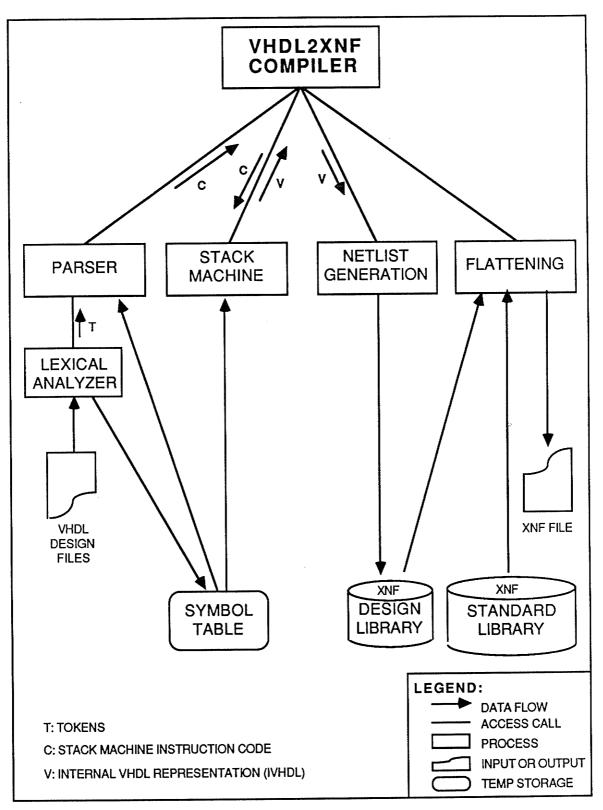

| 4.2   | The structure of the VHDL compiler for LCA design                     | 43   |

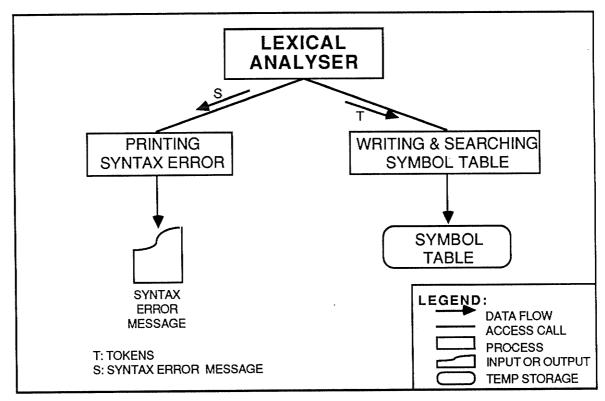

| 4.3   | The lexical analyzer of the VHDL compiler                             | 45   |

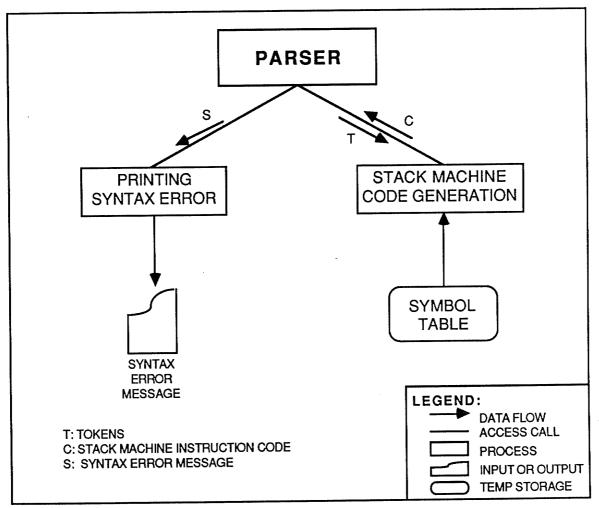

| 4.4   | The parser of the VHDL compiler                                       | 48   |

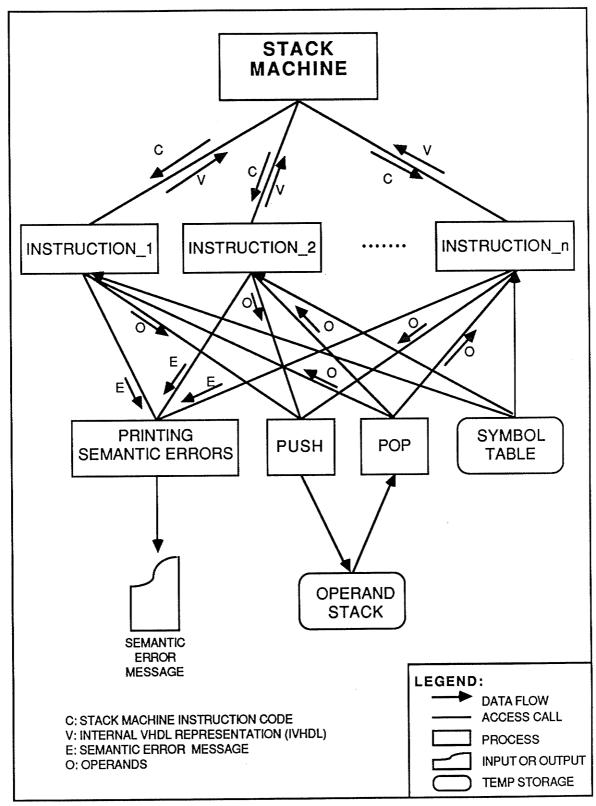

| 4.5   | The stack machine of the VHDL compiler                                | 51   |

| 4.6   | Internal VHDL representation                                          | 53   |

| 4.7   | Xilinx Netlist Format generation                                      | 56   |

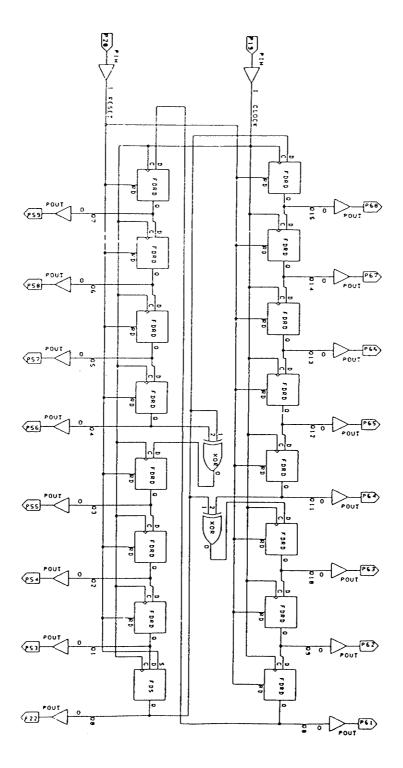

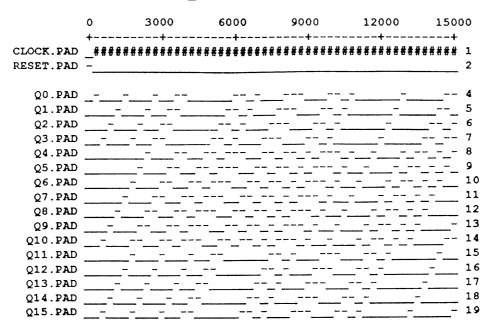

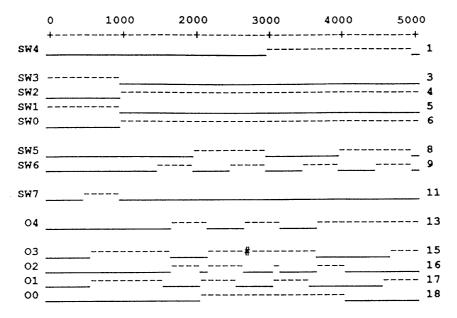

| 5.1 | The schematic of the 16-bit LFSR                                    | 58 |

|-----|---------------------------------------------------------------------|----|

| 5.2 | The graphic output of the simulation the 16-bit LFSR                |    |

|     | implemented from the schematic                                      | 59 |

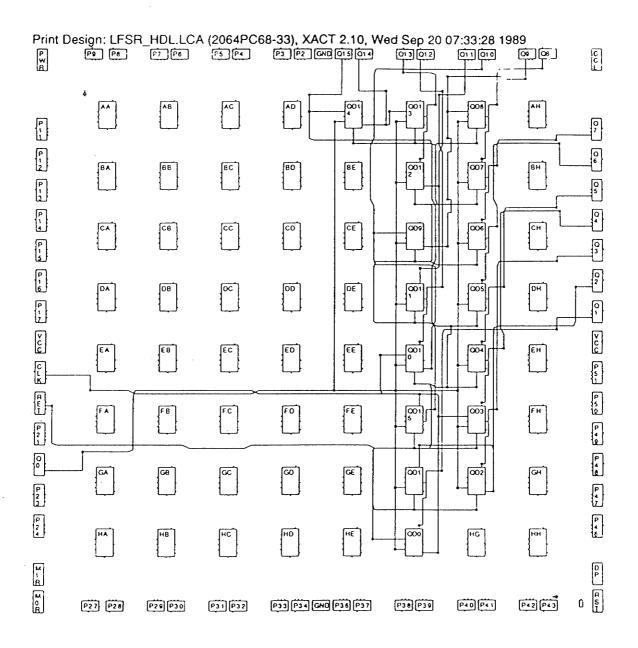

| 5.3 | The layout of the 16-bit LFSR implemented from the VHDL description | 60 |

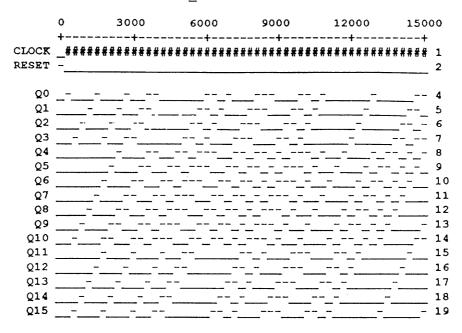

| 5.4 | The graphic output of the simulation of 16-bit LFSR                 |    |

|     | implemented from the VHDL description                               | 61 |

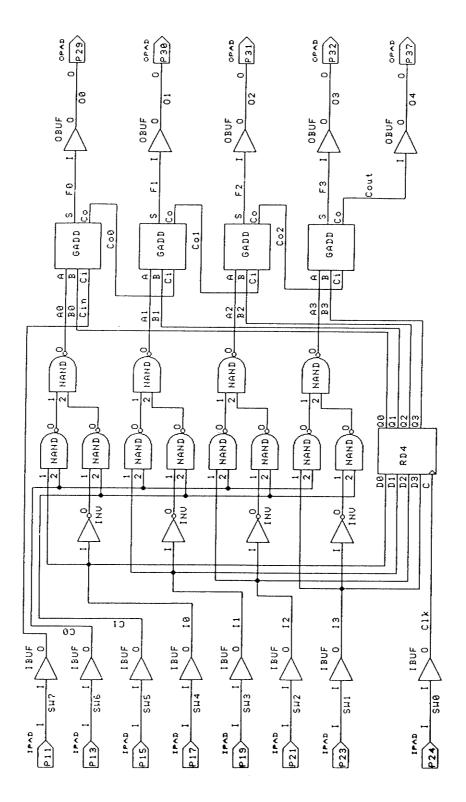

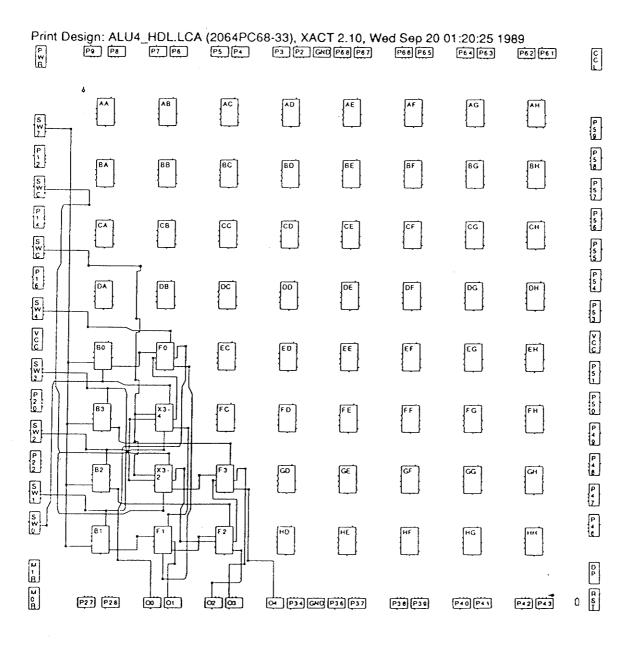

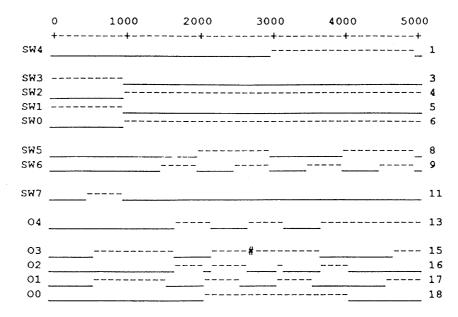

| 5.5 | The schematic of the 4-bit ALU                                      | 63 |

| 5.6 | The graphic output of the simulation of the 4-bit ALU               |    |

|     | implemented from the schematic                                      | 64 |

| 5.7 | The layout of the 4-bit ALU implemented from the VHDL description   | 65 |

| 5.8 | The graphic output of the simulation of 4-bit ALU                   |    |

|     | implemented from the VHDL description                               | 66 |

# LIST OF TABLES

| Table                                    | Page |

|------------------------------------------|------|

| 2.1 Xilinx Logic Cell Array device table | 21   |

| 4.1 Stack machine instruction table      | 52   |

| 5.1 The operation of the 4-bit ALU       | 62   |

#### LIST OF ABBREVIATIONS

ASIC Application Specific Integrated Circuit.

**CAD** Computer Aided Design

CAE Computer Aided Engineering

CAT Computer Aided Testing

CAV Computer Aided Verification

CLB Configurable Logic Block.

DRC Design Rule Checker

IC Integrated Circuit

IOB Input/Output Block

IVHDL Internal VHDL representation

IXNF Internal Xilinx Netlist Format

HDL Hardware Description Language

LCA Logic Cell™ Array

LFSR Linear Feedback Shift Register.

PAL Programmable Array Logic

PCB Printed Circuit Board

PLD Programmable Logic Device

SMB Surface Mount Board

VHSIC Very High Speed Integrated Circuit

VHDL VHSIC Hardware Description Language

VLSI Very Large Scale Integration

XNF Xilinx Netlist Format

#### **CHAPTER 1**

#### INTRODUCTION

The design of electronic systems always involves the design of electronic circuits, often in the form of either integrated circuits (ICs) using very large scale integration (VLSI) or very high speed ICs (VHSIC), or printed circuit boards (PCBs). The design process of electronic circuits can be considered as a transformation of a behavioural description of the circuit concepts into a physical description of the circuits suitable for implementation. A behavioural description is the highest level of abstraction, providing only the functional characteristics of circuits with no specified way of implementing them. For example, the behavioural description of a subtraction unit simply states that the output be the difference of the two inputs. For complex circuits, the transformation is achieved by a hierarchical decomposition from behavioural description to architectural description, then to physical description.

The architectural description is closer to the final implementation because it provides the necessary building blocks and the connections among the blocks with or without the information of how to implement the circuit. The architectural description defines the architecture of the circuit and its organization if the implementation information is contained. An architecture may be implemented in different approaches. For example, the architecture of the processor SPARC has two organizations implemented by two companies

respectively [RISC89]. The architectural description of a subtraction unit would show the negation modules, the summation modules, the carry lines, and the connections among them. The architectural description may have many different levels. The lower the level, the more the detailed building blocks and their connections become. The architectural description at the lowest level is used for placement and routing to generate physical descriptions.

The physical descriptions are the lowest level of circuit description, in which the geometrical representation of the circuits is provided. The physical description is also called circuit layout. At this stage, the circuits are ready to be implemented. Depending on the target technologies of circuit implementation, many different forms of physical description are possible. Common technologies include the use of standard components mounted on PCBs, or surface mount boards (SMBs), and semi-custom or full-custom integrated circuit (IC) fabricated on silicon dies, and programmable logic devices (PLDs).

While the behavioural description is textual, architectural and physical descriptions may be textual or graphical. Textual descriptions specify circuits in the forms of hardware description languages (HDLs) that are formalized modular languages. The graphic description is called schematic, which requires sketching programs that allow the user to physically place circuitry on a display screen.

As the circuit technology develops, the complexity of a circuit increases exponentially. This ever increasing circuit complexity has rendered manual intervention tedious, error-prone and time consuming. On the other hand, the demand for application specific IC (ASIC) is also increasing. As a result, computer-aided tools have been

developed to help implement and verify circuit designs. Electronic circuit engineering now utilizes computer-aided engineering (CAE) tools, including computer-aided design (CAD) tools, computer-aided verification (CAV) tools, and computer-aided test (CAT) tools, to reduce the design effort, turnaround time and design error, and at the same time to improve the design quality.

## 1.1. Electronic Circuit Engineering

The design process of electronic circuit is shown in Fig. 1.1. The concept of a circuit is first studied to establish the behaviour of the circuit. The behaviour is specified in behavioural description, which is used for modeling and prototyping to verify the specification, and for decomposition into architectural description [Kins86].

The architectural description is used for functional simulation to verify the circuit design at early stage. The building blocks are placed and the connections among the blocks are routed towards the target technology of implementing the circuits. Placement and routing generates the physical description of the circuit, i.e. the circuit layout.

The physical description is also used for simulation to verify the function and timing delay of the circuit. The circuit is manufactured using the circuit layout if the simulation is passed. The product must be tested before the acceptance.

# 1.1.1. Electronic Circuit Design

The CAE tools are used throughout the design process. The circuit design development cycle using CAE tools includes three stages: design entry, design

Fig. 1.1. Electronic circuit design process [after Kins86].

implementation and design verification. The CAE tools used at different stages are shown in Fig. 1.2.

The CAD tools include three groups: (i) schematic capture; (ii) HDL compilation; and (iii) placement and routing. Schematic capture tools are the sketching programs that users can place the building blocks on a display screen and draw the connections among the blocks. The schematics are converted to an architectural description. HDL compilation tools accept textual circuit descriptions. At the highest level the compiler decomposes the behavioural descriptions into architectural descriptions, and converts the architectural descriptions to a level for placement and routing. Placement and routing tools accept the architectural description at the lowest level, and generate the circuit layout.

The CAV tools include design rule checkers (DRCs) and simulators. Simulators accept textual descriptions and simulate the functions and timing delay of the circuits.

The circuit descriptions have to be formed into machine understandable formats, and entered into the computers in order to use CAE tools. This is the design entry stage. The CAE tools may accept the descriptions at the behavioural, architectural, or physical level in text using a text editor, or graphic using a schematic capture tool.

The CAE tools may perform decompositions, conversions, and placement and routing at the design implementation stage. If the design entries are at the behavioural level, HDL compilers decompose them into an architectural description. As design entries, architectural descriptions may be in textual or graphical forms. If graphical descriptions are entered into the computers, the schematic capture tools extract the circuit descriptions into a textual format. The architectural descriptions at high level must be converted into a lower

level suitable for placement and routing. The circuit designs can be implemented after the physical descriptions are generated by placement and routing.

Fig 1.2. Electronic circuit development cycle using CAE tools.

While behavioural descriptions provide a great promise for the future, the decomposition from a behavioural description to an architecture that matches the function specification still remains difficult [Sang86]. More research is needed in this area. In general, it is also very difficult to obtain optimized layouts from automatic placement and routing due to the complexity of this problem. However, acceptable layouts may be obtained for the Programmable Logic Device (PLD) target technology because its regular

architecture provides constraints, thereby reducing complexity of the problem.

At the design verification stage, the DRC checks the design according to the design rules and reports design rule violations. Simulations must then be carried out at different levels to verify the functions of the designs. Design verification helps the designers to find out design faults at early design stages. Simulations provide design modelling at the behavioural description level, and worst-case analysis at the physical description level.

# 1.1.2. Programmable Logic Devices [Kins89]

The first PLD device, the Field-Programmable Logic Array (FPLA), was introduced by Signetics in the early 1970s. In 1975, Monolithic Memories followed with their Programmable Array Logic (PAL) devices [BiCo81, MoMe81]. Both PLDs were based on fusible-link technology. In the early 80s, the devices were used extensively in different practical industrial and experimental applications, requiring moderate random logic and small sequencers with high reliability. Later, implementation of more complex circuits demanded more complex PLDs, a number of which were introduced by Advanced Micro Devices, Fairchild Semiconductor, GE/Intersil, Harris Semiconductor, Intel, National Semiconductor, Texas Instruments, and newer companies such as Actel, Altera, Cypress Semiconductor, Exel Microelectronics, Lattice Semiconductor, and VLSI Technology [Marr86, Coll86a, Coll86b, Coll87, Meye87, Smit88, Free88, Actel88]. Many of those devices have advanced from the old fusible-link technology to floating-gate-based ultraviolet-erasable PLDs (UVEPLDs or simply EPLDs) and electrically erasable PLDs (EEPLDs) [Goet86], as well as from the old bipolar to CMOS technologies. A recent example of such devices is the CMOS electrically-configurable gate arrays

[AGGC88] which combine the flexibility of mask-programmable gate arrays and convenience of user-programmable PLDs. Notice that while the EPLDs cannot be reprogrammed *in situ*, the EEPLDs can be reprogrammed in place at the expense of slow programming times and high programming voltages.

The Logic Cell Array (LCA), introduced by Xilinx in 1985 [Land85b, CDFH86, Wynn86, Coll86a, Land87, Xili86a to Xili88] is a CMOS static-memory-based user programmable gate arrays. The LCA devices combine the flexibility of gate arrays with the instant (literally) availability of PLDs. The connections of the gate arrays are controlled by the memory cells so that LCAs are reprogrammable. Its density is between 1200 and 9000 gates with a 20,000 gate part announced for 1990.

#### 1.1.3. Prototyping

Simulation verifies that the functions of the circuit according to the circuit definition. It also provides the worst-case analysis and verification of the critical timing path. However, simulation is limited to subsystem level [Shae87]. Prototyping can enhance simulation as the essential part of the circuit design process.

On the other hand, prototyping allows the circuit to be tested in the target system that it is intended for, and facilitates debugging of the circuit in real time, including the unpredictable timing of asynchronous events. Nevertheless, prototype implementations of complex electronic circuits are difficult. The task of building such prototypes can be simplified significantly by the use of electronic breadboarding.

An alternative implementation methodology has been provided by the Logic Cell

Array (LCA) technology, in which the wiring is done electrically rather than mechanically. Furthermore, once the system has been developed by using computer-aided tools, it can then be verified and modified easily, thus permitting the desired concept of analysis-by-implementation to be a realistic goal.

#### 1.2. Motivation

PLDs have been used extensively to reduce the design complexity and turn around time. However, the flexibility of PLDs is limited because of their AND-OR plane architectures. Full-custom ICs can provide design flexibility, speed, reliability, small size, and security of designs, but they are very costly and time consuming. Gate arrays have higher flexibility and density than PLDs, and less design cost and turn around time than full-custom ICs. However, the design cost and turn around time of gate arrays are still much higher than those of PLDs.

LCAs have a great potential by combining the advantages of both PLDs and gate arrays. The density of LCA is up to 9000 or higher equivalent gates. Xilinx provides a development system supporting various schematic capture tools and logic synthesis tools such as PALASM. Although it is useful, PALASM has its limitation in general circuit design. At present, a general HDL is not available as a design entry option for LCA design.

Schematic capture tools have the direct visual representation. However, as the size of the design increases, graphical specifications become more difficult to create and modify. Hardware description languages are becoming increasingly popular as more

programmers become interested in hardware design and more designers become interested in software design. Textual descriptions can be created using a standard text editor, are easy to store and modify, and also serve as written documentation.

The VHSIC Hardware Description Language (VHDL) is an emerging standard for hardware description languages [Arms89]. The VHDL has the ability to describe circuits from as simple as a gate to as complex as a microprocessor. The VHDL is also able to describe the circuits in both behavioural and architectural description. The aim of this thesis is to develop a VHDL compiler integrated with the front end of the Xilinx development system in order to (i) facilitate the LCA design, and (ii) model an electronic circuit design using VHDL and prototype it using LCA instantaneously. This approach merges the advantages of both VHDL and LCA technologies.

#### 1.3. Thesis Objectives

The objectives of this research work are:

- To study Xilinx Logic Cell Arrays methodology, and its importance in the circuit design process.

- 2. To study hardware description languages (HDLs) and to select an HDL for LCA.

- 3. To design a VHDL compiler for LCA design.

- 4. To implement, test and verify the compiler.

Xilinx provides a circuit-layout tool. Its input language is described by the Xilinx Netlist Format (XNF). The exact format of XNF is proprietary and cannot be described in this thesis, but it is freely available from Xilinx to interested people.

The VHDL compiler developed in this thesis translates an architectural description subset of VHDL into the Xilinx netlist format, which is used by Xilinx circuit-layout tool. The design of the parser of the compiler is accomplished by using parser generation tools in Unix environment, which accept regular expressions of the grammar and produce the parser.

This compiler enables the designer to use hardware description language as the design entry option. Compared with the traditional graphical design entry approach, hardware description languages are easy to create and modify, and serve as documentation of the design. This compiler can also provide an interface with other VLSI design systems so that the LCA can be used for prototyping of the VLSI design. In addition, we anticipate that graphical design system will be unable handle the increasingly complexity of sophisticated system design. For this reason, the VHDL tool developed here will directly contribute to our efforts in promoting system level design space exploration in our laboratory.

#### 1.4. Thesis Structure

Chapter 2 reviews the architecture of Xilinx LCAs, and the methodology of circuit design in LCAs. Chapter 3 gives an overview of VHDL. An architectural description subset of VHDL is defined as the input of the compiler. The output of the VHDL compiler is the Xilinx Netlist Format. Chapter 4 describes the design of the compiling algorithm. Chapter 5 represents the implementation, testing and verification result with two examples. Chapter 6 draws the conclusions of this research work and describes the possible further development and recommendations.

#### **CHAPTER 2**

#### XILINX LOGIC CELL ARRAY

Programmable gate arrays (PGAs) have become increasingly prominent in the past two years, and the signs are that this trend is set to continue [Micr89]. Programmable logic technology has been dominated by devices based on the PLA architecture for the last ten years. As IC technology has advanced, it has become possible to produce larger and larger PLAs. However, the efficiency of PLA utilization decreases as PLA size increases, and the fixed allocation of device pins to array and flip-flop outputs reduces the flexibility of the PLDs. The architecture of gate arrays is being adopted to large programmable devices to solve the problems.

Gate arrays are semi-custom devices based on any array of simple cells surrounded by an interconnection network. In standard gate arrays technology, the interconnection pattern is defined by metallization layers applied at the final stage of manufacture. PGAs dispense with this final stage by possessing a fixed interconnection network which includes programmable crosspoints or switches. The logic cell array (LCA) introduced by Xilinx in 1985 is one of the PGA families. This chapter provides a brief review of the architecture of the LCA, the devices of LCA, the LCA design methodology and the LCA development system.

# 2.1 Architecture of Xilinx Logic Cell Arrays

The logic cell array family is a group of high-density, high-performance, user-programmable gate arrays [CDFH86, HDKN87, Micr89, Xili89]. The LCA architecture is similar to that of other gate arrays, with an interior matrix of configurable logic blocks (CLBs) and surrounding ring of I/O interface blocks (IOBs). Interconnect resources with programmable routing sources occupy the channels between the rows and columns of logic blocks, and between the logic blocks and the I/O blocks. The architecture is shown in Fig. 2.1. Like a microprocessor, the LCA is a program-driven logic device. The functions of the configurable logic blocks and I/O blocks, and their interconnections, are controlled by a configuration program stored in the on-chip static memory. The crosspoints of the programmable routing sources are turned on or off by memory cells controlled switches.

There are three stages of utilizing an LCA device: i) configuration program generation, ii) configuration, and iii) operation. First, a configuration program is generated from the circuit design. Then, the configuration program is loaded either automatically from an external memory on power-up, or by a microprocessor on command as a part of system initialization. The methods of loading the configuration program are determined by logic levels applied to configuration mode selection pins at the time of configuration. The form of the data may be either serial or parallel, depending on the configuration mode. The programming data are independent of configuration mode selected. Finally, the configured LCA device functions just like an ASIC chip. The LCA device can be reconfigured by loading a new configuration program, since the configuration program is stored in an on-chip RAM like memory.

Fig. 2.1. The architecture of Logic Cell Arrays [from Xili89].

Fig. 2.2. Configurable Logic Block (CLB): 3000 Series [from Xili89].

Fig. 2.3. Configurable Input/Output Block (IOB): 3000 Series [from Xili89].

Fig. 2.4. Programmable Interconnect: 3000 Series [from Xili89].

#### 2.1.1. Configurable Logic Blocks

The core of the LCA is a matrix of identical Configurable Logic Block (CLBs). Each CLB contains programmable combinatorial logic and storage registers as shown in Fig. 2.2. The combinatorial logic section of the block is capable of implementing any Boolean function of its input variables. The registers can be loaded from the combinatorial logic or directly from a CLB input. The register outputs can be inputs to the combinatorial logic via an internal feedback path.

#### 2.1.2. Configurable Input/Output Blocks

The periphery of the LCA is made up of user programmable Input/Output Blocks (IOBs). Each block can be programmed independently to be an input, an output, or a bidirectional pin with three-state control as shown in Fig. 2.3. Inputs can be programmed to recognize either TTL or CMOS. Each IOB also includes flip-flops that can be used to buffer inputs and outputs.

# 2.1.3. Programmable Interconnections

The flexibility of the LCA is due to resources that permit program control of the interconnection of any two points on the chip, as shown in Fig. 2.4. Like gate arrays, the interconnection resources of LCA include a two-layer metal network of general purpose lines that run horizontally and vertically in the rows and columns between the CLBs. Programmable switches connect the inputs and outputs of IOBs and CLBs to nearby metal

lines. Crosspoint switches and interchanges at the intersections of row and columns allow signals to be switched from one path to another. Long lines run the entire length or width of the chip, bypassing interchanges to provide distribution of critical signals with minimum delay or skew. Adjacent CLBs can be connected by direct interconnections.

#### 2.2. Xilinx LCA Devices

The first generation of LCAs introduced in 1985 has been incorporated as two devices in the XC2000 series in density ranging from 1200 to 1800 gates [CDFH86, Micr89, Xili89]. Each XC2000 CLB contains combinational logic and a signal storage element. The combinatorial logic of the block is capable of implementing any Boolean function of up to four variables, or any two independent functions of up to three variables in each. The storage element in the CLB can be configured as an edge-triggered flip-flop or a transparent latch. The XC2000 series IOBs include a register in the input path and a three-state buffer in the output path. The programmable interconnections include direct interconnects, five general purpose lines and two long lines per vertical channel and four general purpose lines and one long lines per horizontal channel.

The second generation of LCA introduced in 1987 is embodied in the XC3000 family [HDKN87, Micr89, Xili89]. It consists of five compatible devices ranging 2000 to 9000 gates densities. The XC3000-series CLB includes a wider combinatorial logic circuit, two storage elements, and dedicated logic that implements clock, reset, and I/O selection functions as shown in Fig 2.2. The nine inputs of the CLB include five general-purpose inputs to the combinatorial logic, and clock, clock enable, reset, and direct data

inputs to the register. The two outputs of the CLB can be driven by the combinatorial logic or the the Q output of the registers. Each combinatorial logic of the CLB can be configured in any one of the three modes. Any single Boolean function of five input variables can be implemented. A second option offers any two independent functions of four variables in each. The third option is to create two independent functions of four variables in each, multiplexed into a single function by the E input to the block. The two registers of the CLB are edge-triggered D-type flip-flops. Clocking is provided by the dedicated clock input of the block; the clock path has an option invert, allowing the flip-flops to be leading or falling-edge triggered at each block. Asynchronous reset and clock-enable inputs are also provided at each CLB. The D input to each flip-flop can be driven by the output of either of the two logic functions that can be generated in the combinatorial circuit, or by a direct data input to the block that bypasses the combinatorial logic.

Each IOB of XC3000 controls one pin. There are two registers in each IOB — one in the input path and one in the output path as shown in Fig. 2.3. Input signals pass through an input buffer to the D input of a register. The input register of the IOB can be configured as an edgetriggered flip-flop or a transparent latch. The output path includes a programmable invert for determining the polarity of the output signal. The signal then goes to the D input of the output register. This register is always an edgetriggered flip-flop. The direct or registered output signal can be sent to the output buffer, which is a three-state buffer.

The programmable interconnections of XC3000 include direct interconnects, five general purpose lines and four long lines per vertical channel and five general purpose lines

and two long lines per horizontal channel as shown in Fig. 2.4.

The XC4000 series, the third generation of LCA announced for 1990, are twice as fast as prior devices, and feature densities as high as 20,000 gates, on-chip static RAM and greatly improved utilization [Goer89, Wils89]. The devices of XC2000 series and XC3000 series are listed in Table 2.1.

Table 2.1. Xilinx Logic Cell Array device list.

| DEVICES             | XC2064                   | XC2018                    | XC3020                    | XC3030           | XC3042                    | XC3064           | XC3090           |

|---------------------|--------------------------|---------------------------|---------------------------|------------------|---------------------------|------------------|------------------|

| EQUIVALENT GATES    | 1200                     | 1800                      | 2000                      | 3000             | 4200                      | 6400             | 9000             |

| CLBS<br>(ROW X COL) | 64<br>(8 X 8)            | 100<br>(10 X 10)          | 64<br>(8 X 8)             | 100<br>(10 X 10) | 144<br>(12 X 12)          | 224<br>(16 X 14) | 320<br>(20 X 16) |

| CLFS                | 128                      | 200                       | 128                       | 200              | 288                       | 448              | 640              |

| FLIP-FLOPS          | 122                      | 174                       | 256                       | 360              | 480                       | 688              | 928              |

| IOBS                | 58                       | 74                        | 64                        | 80               | 96                        | 120              | 144              |

| PACKAGES            | 48DIP<br>68PLCC<br>68PGA | 68PLCC<br>84PLCC<br>84PGA | 68PLCC<br>84PLCC<br>84PGA | 84PLCC<br>84PGA  | 84PLCC<br>84PGA<br>132PGA | 132PGA           | 132PGA<br>175PGA |

| PROM SIZE (BITS)*   | 11,404                   | 17,096                    | 14,819                    | 22,216           | 30,824                    | 46,104           | 64,200           |

| MEMORY (KBYTES)**   | 2,048                    | 2,048                     | 2,048                     | 2,186            | 3,584                     | 4,846            | 6,144            |

<sup>\*</sup> The PROM size required to store the configuration program for the devices.

### 2.3. LCA Design Methodology

Integrated circuits of the LCA complexity need advanced CAE tools if they are to be used effectively. Like electronic circuit design using CAE tools, the LCA design process is partitioned into three main steps: entry, implementation, and verification [Micr89, Xili89]. The design process for LCA is shown in Fig. 2.5. An integrated development

<sup>\*\*</sup> The RAM of the CAD station required to design the devices using the LCA development system.

system for design and implementation of LCA is provided by Xilinx. This provides the user with an effective, convenient, low risk method of logic design entry, simulation, configuration program generation and verification for single chip logic design.

The LCA development system is an open system — the designer can choose from among several popular CAE programs and workstations, allowing the use of existing familiar tools to develop LCA-based design. The development system is available for PC-AT and PS/2 personal computers, and their fully compatible clones. In addition, tools are also available for Sun, Apollo, and Vax/VMS workstations.

Many different schematic editors and simulators are available for entering and verifying circuit designs. To provide a bridge to existing CAE tools, Xilinx has defined an intermediate design description format called the Xilinx Netlist Format (XNF) [Xili88e]. Any design entry tools can be used to enter LCA designs if the output of the design entry can be translated into XNF file [Xili88f]. Similarly, any simulator can be used to verify LCA designs if the XNF file can be translated into the netlist format of that simulator.

#### 2.3.1. Design Entry

An LCA design can be entered by using schematic capture, Boolean equations, or state machine equations in PALASM format. Xilinx supports various schematic capture tools, such as FutureNet DASH, Dasiy AIE or EED II, Mentor IDEA and OrCAD SDT. The design entry is translated into an XNF file. Other design entry methods can be supported with an appropriate XNF translator.

Fig. 2.5. LCA design process[after Xilinx].

Designers typically enter the designs hierarchically, by first creating a top-level description that defines the application in terms of major functional blocks. Lower-level descriptions decreasing the logic in each of the larger blocks are then entered, using marcos defined by the designer or supplied in the standard library. There is no limit to the number of levels within the hierarchical design. Two design examples will be seen later in Chapter 5.

#### 2.3.2. Design Implementation

Implementing designs in LCA entails mapping the desired logic into the CLBs and IOBs of the LCA architecture. The automatic LCA implementation tools include logic reduction and logic partitioning, placement and routing, and design editor and configuration program generation [Micr89, Xili89]. Once a design has been translated into an XNF file, the design is mapped into the programmable resources of the LCA by a program called XNF2LCA. The XNF2LCA program performs two operations: logic reduction and logic partitioning. Logic reduction is the process of deleting unused logic from the design, permitting liberal use of the library, without any penalty when a macro has unused functions. The remaining logic is automatically partitioned into pieces that can be implemented within individual CLBs and IOBs. As much logic as possible is grouped into each block. The result is a design file called LCA.

Each CLB and IOB of the design is "placed" by assigning it to one of the discrete blocks within an LCA and is "routed" by specifying the programmable interconnection paths used to implement the connections among the blocks. Placement and routing can be

performed automatically with placement and routing software, interactively with graphic based design editor, or combination of the two. The automatic placement and routing (APR) program searches for the optimum placement by using the simulated annealing algorithm and then routes the nets that interconnect the blocks.

The core of the development system is the LCA design editor XACT. The XACT provides the designer with the ability to graphically enter, place, route, and manipulate LCA designs, and to generate the LCA configuration program data after the placement and routing. The generated configuration program data can be download through the download cable, which provides a convenient approach to program a breadboard or prototype unit.

#### 2.3.3 Design Verification

After the implementation of the design, its operation must be verified. Both APR and XACT calculate the worst-case delays through both the logic block and the routing resources. A simulator PC-SILOS is also available from Xilinx with a converter that converts the XNF to the SILOS simulation netlist and a dummy simulation stimulus file. The stimulus file is tailored to define the input pattern and which signals to be examined and with what timing. The XNF file may come from the design entry or form an implemented design by converting the design to XNF file. Designs which have not been routed can be simulated with unit delay data. Routed designs include worst-case timing of functional blocks and their interconnections.

The verification can also be done by in-circuit testing tools such as Xilinx

XACTOR, or by IC testing devices such as AXIC tester.

### 2.4. Summary

The LCA technology provides a fast turn around time and high flexibility, and allows users to implement ASIC design easily and quickly. It also provides a practical approach for ASIC breadboarding. For educational purposes, the Xilinx development system demonstrates the whole process of digital system design. In this environment, an HDL should be available as an option for design entry. Since the development system is an open system with XNF as the interface, an HDL compiler can be developed to generate the XNF file.

#### **CHAPTER 3**

# THE VHSIC HARDWARE DESCRIPTION LANGUAGE

The VHSIC Hardware Description Language (VHDL) is a newly-adopted IEEE standard hardware description language that supports architectural, dataflow and behavioural styles of design and documentation for digital systems. A number of CAE tools have been developed to support VHDL [AAIR88, LCAC88, Saun87]. The motivation for the development of the VHDL CAE tools has been the need for a standard medium of communication for transmitting hardware design data from one organization to another [DeGa86]. Such communication is necessary for the following four reasons [Shah86]: (i) from the viewpoint of the hardware component vendor, it allows formal specification of the behaviour of the component; (ii) from the viewpoint of a component user, it allows formal specification of the functionality required of the component for procurement purposes; (iii) from the viewpoint of the hardware design engineer, it provides a standard for sharing information within a design team, even among designers working at different levels of abstraction; and (iv) from the viewpoint of the CAE tool developer, it provides a wider user-base for tools, thereby creating a better return on investment.

Beginning in 1983, the U.S. Department of Defense sponsored the development of the VHSIC Hardware Description Language (VHDL). The original

intent of the language was to serve as a means of communicating designs from one contractor to another in the Very High Speed Integrated Circuit (VHSIC) program. However, the design of the language has received input from many individuals in computer industry and thus reflects a consensus of option as to what characteristics a hardware description language should have [Arms89].

In August 1985, Version 7.2 of the language was released by the Department of Defense, representing the completion of the first major stage of the language development. The IEEE sponsored a further development of VHDL, with the goal to establish a standard version of the language. In June 1987, eligible IEEE members voted to accept Version 7.2 as the standard version and in December 1987, it was officially so designated by the IEEE [VHDL88]. This chapter gives a brief overview of IEEE standard VHDL as well as a subset of VHDL for LCA design.

#### 3.1. Features of VHDL

VHDL allows design and documentation of digital circuits from the system level to the gate level, and supports bottom-up as well as top-down design methodologies [Meye89]. Although designed to be independent of any underlying technology, design methodology, or environment tool, the language is extendible to various hardware technologies, design methodologies, and the varying information needs of design automation tools. In VHDL, not only the architecture of a circuit is defined, but its organization can be defined as well. The integration and unification of architecture and organization information is provided in VHDL.

VHDL describes the functionality and organization of hardware system at various levels of abstraction. The concept of *design entity* is the primary abstraction mechanism of the language [LMSh86]. Starting with design entity, we discuss the basic features of VHDL in this section.

# 3.1.1. Design Entities

One of the characteristics of hardware devices is that their functionality can be defined for the most part independent of the environment in which they operate. This characteristic allows components from various sources to be wired together to create new and more complex designs. VHDL reflects this characteristic in its overall organization, by emphasizing the ability to describe isolated components, called design entities, which can then be combined with other component descriptions to form more complex descriptions. In VHDL, a design entity consists of an interface description and one or more alternative body descriptions.

# 3.1.2. Interface Description

The interface contains a set of definitions common to alternative bodies. Such definitions capture the external view of hardware entity and specify communication channels between the design entity and the outside world. An example of interface description for a full adder is shown in Fig. 3.1. The interface description names the entity and describes its inputs and outputs. The port description of interface declares signals visible externally, including the mode of the signals (e.g., in or out) and the

type of the signals (e.g., BIT). BIT is a predefined signal type in VHDL.

Fig. 3.1. Interface description of a full adder.

## 3.1.3. Body Descriptions

After the interface description, the specification of the behaviour of the entity is required. In VHDL, three styles of body descriptions are possible: architectural, dataflow, and behavioural, as shown in Fig. 3.2. The three styles can be combined within an architectural body description. In general, the three styles are used separately as alternative body descriptions for a design entity.

Fig. 3.2. Body descriptions of design entity.

# 3.1.3.1. Architectural Description

The architectural description captures the schematic view of hardware and consists primarily of interconnected components. The behaviour of the components is

externally defined. The architectural description involves (i) component declaration, which defines interface to components used in a design, and (ii) component instantiations, which create one or more instances of a declared component. An example of the architectural description of the full adder is shown in Fig. 3.3. Note that each instantiation has a unique label associate with it as well as a port map. The port map creates an association between the inputs and outputs of the components declared and the instantiation components by positions.

### architecture Structure of FullAdder is

```

component XOR2 port (Ain, Bin, Output);

end component;

component AND2 port (Ain, Bin, Output);

end component;

component OR2 port (Ain, Bin, Output);

end component;

```

signal A, B, C: Bit;

#### begin

ADD0: XOR2 port map (X, Y, A);

ADD1: XOR2 port map (A, Cin, Sum);

CARRY0: AND2 port map (A, Cin, B);

CARRY1: AND2 port map (X, Y, C);

CARRY3: OR2 port map (B, C, Cout);

end Structure;

Fig. 3.3. Architectural body description of a full adder.

# 3.1.3.2. Dataflow Description

The dataflow description specifies data transforms being performed in terms of concurrently executing register transfer level statements. It is more abstract than the architectural description.

One advantage of the architectural description is the ability to express the parallelism inherent in hardware operation. In contrast, purely architectural description cannot express what each component actually does, since component behaviour is externally defined. However, the dataflow description allows the simultaneous expression of parallelism and behaviour. For example, AHPL is a register transfer level language which has been used widely in industrial and educational area [HiPe87].

#### architecture Dataflow of FullAdder is

signal A, B: Bit;

begin

A <= X or Y; B <= A and Cin; Sum <= A xor Cin; Cout <= B or (X and Y); end Dataflow;

Fig. 3.4. Dataflow description of a full adder body.

An example of dataflow description for the full adder is shown in Fig. 3.4. Dataflow descriptions are created through the use of concurrent signal assignment statements. Such statements execute in response to event or changes in signal values referenced within the statements.

# 3.1.3.3. Behavioural Description

The behavioural description, the most abstract style, specifies data transforms in terms of algorithms for computing output responses to input changes. Component networks modeled with concurrent signal assignment statements represent both design

architecture (in terms of component interconnection) and design behaviour (in terms of data transforms performed). However, it is sometimes necessary to describe behaviour without biasing that description toward a particular implementation. A pure behavioural description, entailing little or no architectural information, is more appropriate in such situations. For example, Mentor has developed the Behavioural Language [Ment84]. In VHDL behavioural description can be written by using process statement. An example of a behavioural description for an AND gate with its interface description is shown in Fig. 3.5.

```

entity AndGate is

port ( inputs: in Bit_Vector(1 to 2);

Result: out Bit);

end AndGate;

architecture Behaviour of AndGate is

begin

process (Inputs)

variable Temp: Bit;

begin

Temp := '1';

for i in Inputs' Range loop

if Inputs(i) = '0' then

Temp := '0';

exit:

end if:

end loop;

Result <= Temp after 10ns;

end process;

end Behaviour;

```

Fig. 3.5. Behavioural description of an AND gate with interface description.

A process statement contains a declarative part and a statement part. However, only sequential statements such as if, case, and loop statements can be written in its statement part. Such statements describe algorithms that specify how a component will respond to changes on input signals by causing changes on output signals.

A process statement is initially sensitive to an associated list of signals. An event on any of those signals will cause the process to execute, and will potentially cause the process to modify certain output signals.

#### 3.1.4. Types

VHDL is strongly typed and supports a variety of data types. The data type classification is shown in Fig. 3.6. VHDL also allows the designer to define new data types as they are needed. For example, two new types BYTE and WORD can be created using type declaration as shown in Fig. 3.7.

Fig. 3.6. VHDL type classification tree [after Arms87].

# type BYTE is array (0 to 7) of BIT; type WORD is array (0 to 15) of BIT;

Fig. 3.7. Type declaration.

INTEGER and REAL are two predefined numeric types with the standard numeric operation defined upon them; designers may define additional numeric types by specifying their range of values. Enumeration types include values that are either character literals or identifiers. VHDL predefines several enumeration types including type BOOLEAN, type BIT, and type CHARACTER. Standard logic operations are available on BOOLEAN or BIT objects. Designers may also define their own enumeration types. Physical types allow expression of measurements. A physical type declaration specifies a set of units, all defined in terms of some based unit, and all measuring the same quantity.

The two classes of composite types in VHDL are array and record types; elements of an array type must be the same, whereas elements of record type may differ. Predefined array types BIT\_VECTOR and STRING represent arrays of bits and arrays of characters respectively. Logic operations defined on BITs are defined on BIT\_VECTORs as well.

#### **3.1.5.** Signals

VHDL supports architectural and dataflow descriptions through the use of signals. Signals can be used to represent wires or buses in a architectural description or to represent data transmissions in a dataflow description. Signals may retain state and

as such may be used to represent memory elements such as flip-flops and registers.

Signals may have different types. Before their use, signals must be declared to define their names and the types associated with them. As shown in Fig. 3.8, an example of signal declaration signals RESET and CLOCK with type BIT, INPUTS and OUTPUTS with type BYTE, and ADDRESS\_LINES with type WORD.

signal RESET, CLOCK: BIT;

signal INPUTS, OUTPUTS: BYTE;

signal ADDRESS\_LINES: WORD;

Fig. 3.8. Signal declaration.

## 3.1.6. Packages

For frequently used declarations, a package may be created to avoid writing declarations repeatedly when they are needed. The package has a name associated with it. A package can be used to share declarations among many other design units, or collect declarations relating to a particular abstraction. Declarations in a package may be made visible by referring to the package. A package declaration example is shown in Fig. 3.9.

package BYTE\_WORD is

type BYTE is array (0 to 7) of BIT;

type WORD is array (0 to 15) of BIT;

end;

Fig. 3.9. Package declaration.

## 3.2. Supported Subset

VHDL is a very complicated language. It is very difficult to develop a compiler which is able to accept the whole set of VHDL, especially for the decomposition from behavioural description to architectural description. It is a better approach to divide the task into several stages. We choose to develop a compiler that accepts a VHDL architectural description subset as the first step. Further development can be built up on this stage.

The VHDL subset supports the interface and architectural body description. Package declaration is also supported so that a group of type declarations can be referred by more than one entity. Pin declarations and several predefined signal types are added into the subset to support the LCA design. A User's Guide and the Backus–Naur (BN) form syntax description of the supported subset can be found in Appendix B and Appendix C.

# 3.2.1. Input/Output Pin Descriptions

In standard VHDL, the physical positions of interface ports cannot be specified. However, the I/O pin numbers of a design in LCA have to be explicitly defined for implementation using the LCA development system. If a I/O signal is not connected with a IOB or pin of the LCA, the logic partitioning and reduction program considers this signal no source. Thus, the signal and its loads are reduced. For this purpose, a pin description clause is added into interface description after the port description. For example, the full adder interface with its pin association description is

shown in Fig. 3.10.

Fig. 3.10. Interface description of a full adder.

## 3.2.2. Types for LCA Design

Signals can have flags in an LCA design. The flags are used to control the automatic placement and routing (APR) process [Xili88f, Xili89]. "L" is used to tell the APR to route a signal through a long line across the row or column of the array. "C" tells APR that it is a critical route so that APR gives this signal the highest priority. "N" tells APR that it is a non-critical route so that APR gives it the lowest priority. "X" assures that this signal stays outside of CLBs. To cope with those flags, four predefined types BIT\_L, BIT\_C, BIT\_N, and BIT\_X are added into VHDL, corresponding to the flags L, C, N, and X.

## 3.3. Summary

This Chapter describes a sophisticated hardware description language, capable of supporting architectural, dataflow, and behavioural styles design and documentation for digital circuits from a single gate to a complex system. It is too

difficult to develop a compiler for the whole set of the language. A subset of VHDL needs to be adopted for a class of circuits design such as LCAs. As the first step, A VHDL architectural description subset is chosen for LCA design.

#### **CHAPTER 4**

## A VHDL COMPILER FOR LCA DESIGN

Various VHDL design systems have been implemented to support the design of digital systems. There are basically two approaches to implement such a VHDL design system [Gilm86, Mars88]: i) a full-scale VHDL design system [Saun87], including VHDL analysis to compile the VHDL design files into a design library, synthesis to create the hardware layout and simulation to verify the design; and ii) an embedded VHDL design system in which the VHDL compiler is combined with an existing CAE system [AAIR88]. In this system, VHDL is used as an approach for design entry, with the compiler generating a description format acceptable by the CAE system, while the CAE tools are used to implement and verify the design originally described in VHDL.

The second approach has several advantages, such as the availability of simulation model library, schematic capture and fault simulation, and a large existing user base. Since we have a dedicated CAE system for LCA design, the second approach is selected in which the VHDL compiler for LCA design is embedded within the existing CAE tools.

The position of the compiler in the LCA design process as shown in Fig. 2.5. is shown by the shadowed area in Fig. 4.1. As we described in Chapter 2, the LCA development system supported by Xilinx has an interface with the high level entry and the

Fig. 4.1. The position of the VHDL compiler in the LCA design process.

simulation tools. The Xilinx Netlist Format (XNF) is accepted by the LCA development system as an interface for implementation and is generated by the LCA development system for simulation.

The VHDL compiler for LCA design is a one-pass compiler supporting a subset of standard VHDL for hierarchical architectural descriptions. It accepts VHDL design files and compiles the design files into the XNF files. Then, the design implementation and simulation are accommodated using the existing LCA development system. The structure of the compiler is shown in Fig. 4.2. The compiler consists of the following five components: a lexical analyzer, parser, stack machine, netlist generator and flattener.

VHDL design files are typed in and edited using a standard text editor such as VI in UNIX system. The lexical analyzer reads the VHDL design files and converts them into meaningful lexical chunks called tokens. The parser calls lexical analyzer to obtain the tokens and checks the syntax of the VHDL design files. If there are any syntax errors, they are reported by the parser. Otherwise, the parser generates a code for the stack machine. The code executed on the stack machine is a linear array of the instructions of the stack machine and parameters for the instructions. The stack machine generates an internal VHDL representation (IVHDL), and also reports any semantic errors. In the netlist generation stage, first the IVHDL is converted into an internal XNF (IXNF) representation which is subsequently translated to XNF file. Both IXNF and XNF are formats supported by Xilinx [Xili88e, Xili88f]. The XNF files in different hierarchical levels are stored in the design library. Each design entity in VHDL results in an XNF file in the design library. A standard library can also be established by adding the XNF files which are proved to

Fig. 4.2. The structure of the VHDL compiler for LCA design.

be eligible designs. Current standard libraries are provided by Xilinx. The library list is included in Appendix E. A program supported by Xilinx flattens the hierarchical XNF files. The flattening program reads the XNF files in the design library and the XNF files of the standard components in standard library, checks the syntax of the NXF files, and generates a flattened XNF file, which is used for implementation of the design.

#### 4.1. Lexical Analysis

The lexical analysis is the first phase of the compiler. The lexical analyzer is a subroutine of the parser as shown in Fig. 4.2. Its main task is to read the VHDL design files and produce as output a sequence of tokens that the parser uses for syntax analysis. Each token represents a logically cohesive sequence of characters or string, such as an identifier, a keyword, a punctuation character, or an operator. In general, there is a set of strings in the input for which the same token is produced as output. This set of strings is described by a rule called a *pattern* associated with the token. The pattern is said to match each string in the set. The string forming a token is called the lexeme for the token. The lexemes are stored in a symbol table for later use. The lexical analysis uses the patterns to identify the tokens. Upon receiving a "get next token" request from the parser, the lexical analyzer reads the input files until it can identify the next token, and then passes the token to the parser.

The secondary task of the lexical analyzer includes stripping out comments and white spaces in the form of blanks, tabs, and newline characters from the VHDL design files, as well as counting line numbers which can be used in association with error

messages. The structure of the lexical analyzer is shown in Fig. 4.3.

There are tools for constructing lexical analyzer from special-purpose notations based on regular expressions. LEX [LEX86], a lexical analyzed generator tool is used to generate the lexical analyzer of the VHDL compiler.

Fig. 4.3. The lexical analyzer of the VHDL compiler.

# 4.1.1. LEX — A Lexical Analysis Generator

LEX is used in the following manner. First, a specification of the lexical analysis is prepared by creating a program using regular expressions to describe all the patterns and fragments of C programs to be executed when a matching string is found. Then, the program is run through the LEX to produce a C program lex.yy.c. The program lex.yy.c

is the pattern-matching algorithm of the lexical analyzer.

The specification of the lexical analysis consists of three parts:

declarations

%%

patterns and actions

%%

auxiliary procedures

The declarations section includes declarations of variables, constants, and definitions.

The patterns and actions are statements of the form:

$p_1$  {action<sub>1</sub>}  $p_2$  {action<sub>2</sub>} ...  $p_n$  {action<sub>n</sub>}

where each  $p_i$  is a regular expression and each  $action_i$  is a program fragment describing what action the lexical analyzer should take when pattern  $p_i$  matches a lexeme. In LEX, the actions are written in C; in general, however, they can be any implementation languages. The third section holds whatever auxiliary procedures are needed by the actions. The specification of the lexical analyzer can be found in Appendix F.

When called by the parser, the lexical analyzer begins reading its remaining input, one character at a time, until it has found the longest prefix of the input that is matched by one of the regular expressions  $p_i$ . Then, it executes  $action_i$ . Typically,  $action_i$  will return the control and the token to the parser. If the token is an identifier, the  $action_i$  also

searches the symbol table and writes the identifier into the symbol table if it is not in the table.

#### 4.2. Parsing

The second phase of the compiler is syntax analysis or parsing. The parser obtains a string of tokens from the lexical analyzer, as shown in Fig. 4.2, and verifies that the string can be generated by the grammar for the source language. After the tokens pass the syntax checking, they are used to generate the output of the parser. The output of the parser of the VHDL compiler is a sample stack machine code which is a list of instructions and the parameters for the instructions. The tokens are used as the parameters in the code. The parser is also expected to report any syntax errors. The structure of the parser is shown in Fig. 4.4.

There are many different algorithms for syntax analysis and tools to generate parsers. Every programming language has rules that prescribe the syntactic structure of the well-formed programs. The syntax of programming language constructs can be described by context-free grammar or Backus-Naur Form (BNF) notation. YACC [YACC86], a parser generator that accepts a context-free grammar description and generates an LALR parser, is used to generate the parser of the VHDL compiler.

# 4.2.1. YACC — Yet Another Compiler Compiler

A parser can be constructed using YACC by creating a file containing a

specification of the parser first. Then, YACC transforms the file into a C program called y.tab.c using the LALR method [ASU186]. The program y.tab.c is a representation of an LALR parser, along with other C routines.

Fig. 4.4. The parser of the VHDL compiler.

A specification of the parser has three parts:

%{

C language declarations

YACC declaration: lexical tokens, grammar variables, precedence and associativity information

%%

grammar and actions

%%

supporting C routines

The specification of the parser of the VHDL compiler can be found in Appendix E.

Alternate rules are separated by "I". Any grammar rule can have an associated action, which will be performed when an instance of that rule is recognized in the input. An action is a sequence of C statements enclosed in braces  $\{$  and  $\}$ . Within an action, \$n (that is, \$1, \$2, etc.) refers to the value returned by the n-th component of the rule, and \$\$ is the value to be returned as the value of the whole rule.

The parser of the VHDL compiler has basically one kind of action which is to add new instructions and tokens as parameters in the code for the stack machine. Different grammar rule recognition result in different instructions added to the stack machine code.

#### 4.3. Stack Machine

After the parser process, the result is a list of instructions for a stack machine. The stack machine is a simple computer. When an operand is encountered, it is pushed onto a stack; most operators operate on items on the top of the stack.

A stack machine results in simple compiler. It is just an array containing operators

and operands. The operators are the machine instructions; each is a function call with its arguments, if any, following the instructions. Other operands may already be on the stack. A stack machine is also easy to modify and expand by changing the instruction functions, or adding new instructions.

The structure of the stack machine is shown in Fig. 4.5. For example, to handle a signal declaration

COMMENTS

signal X: BIT;

the following code is generated by the parser:

CODE

idpush

Push symbol table pointer onto stack;

X

..... identifier X;

idpush

Push symbol table pointer onto stack;

EIT

.....predefined type BIT;

scode

Create a Signal record to store the declaration.

In the code, the boldface strings are stack machine instructions and the others are the parameters for the instructions. When this code is executed on the stack machine, the result is an internal VHDL representation of the signal declaration.

### 4.3.1. Stack Machine Instructions

The stack machine of the VHDL compiler has 46 instructions. When the VHDL subset is to be expanded, new instructions can be easily added into the existing instruction set. The instructions and their brief function descriptions are shown in Table 4.1.

Fig. 4.5. The stack machine of the VHDL compiler.

**Table 4.1.** The stack machine instructions.

| INSTRUCTION | FUNCTION                   | INSTRUCTION | FUNCTION           |

|-------------|----------------------------|-------------|--------------------|

| INTPUSH     | PUSH INTEGER ONTO STACK    | AND         | LOGIC AND          |

| IDPUSH      | PUSH IDENTIFIER ONTO STACK | NAND        | LOGIC NAND         |

| POP         | POP ID OR INT FROM STACK   | OR          | LOGIC OR           |

| PCODE       | PROCESS PACKAGE            | NOR         | LOGIC NOR          |

| CHKPL       | CHECK PACKAGE NEME         | XOR         | LOGIC XOR          |

| UCODE       | PROCESS USE-CLAUSE         | EQ          | EQUAL              |

| ECODE       | PROCESS ENTITY             | NE          | NOT EQUAL          |

| CHKE        | CHECK ENTITY NAME          | GT          | GREATER THAN       |

| PPCODE      | PROCESS PINS               | GE          | GREATER OR EQUAL   |

| ACODE       | PROCESS BODY               | LT          | LESS THAN          |

| CHKA        | CHECK BODY NAME            | LE          | LESS OR EQUAL      |

| TCODE       | PROCESS TYPE               | NEGATE      | NEGATIVE           |

| CDCODE      | PROCESS COMPONENT DECLA.   | ADD         | ADDITION           |

| FPCODE      | PROCESS FORMAL PORT        | SUB         | SUBTRACTION        |

| IDFIRST     | PROCESS IDENTIFIER         | MUL         | MULTIPLICATION     |

| IDLIST      | PROCESS IDENTIFIER LIST    | DIV         | DIVISION           |

| SCODE       | PROCESS SIGNAL             | MOD         | MODEL              |

| CICODE      | PROCESS COMPONENT INST.    | REM         | REMAININGG         |

| CHKCL       | CHECK COMPONENT LABEL      | POEWR       | POWER              |

| SIMNAME     | PROCESS SIMPLE NAME        | ABSL        | ABSOLUTE           |

| FORCODE     | PROCESS FOR STATEMNET      | NOT         | LOGIC NOT          |

| IFCODE      | PROCESS IF STATEMENT       | EVAL        | EVALUATE VARIABLE  |

| CHKGL       | CHECK GENERATE LABEL       | STOP        | STOP STACK MACHINE |

INTPUSH, IDPUSH and POP are the three instructions that manipulate the operands stack. STOP halts the stack machine. The other instructions generate the IVHDL using the symbol table. The instructions on the left side of Table 4.1. process the declarations and statements, check the semantic of the VHDL design file. The instructions on the right side of Table 4.1. process the logic, relational and mathematical operations.

When the stack machine code generated by the parser is executed, the result is a group of records that contain the information from the VHDL design files. These records are denoted as Internal VHDL representations (IVHDL).

# 4.3.2. Internal VHDL Representation (IVHDL)

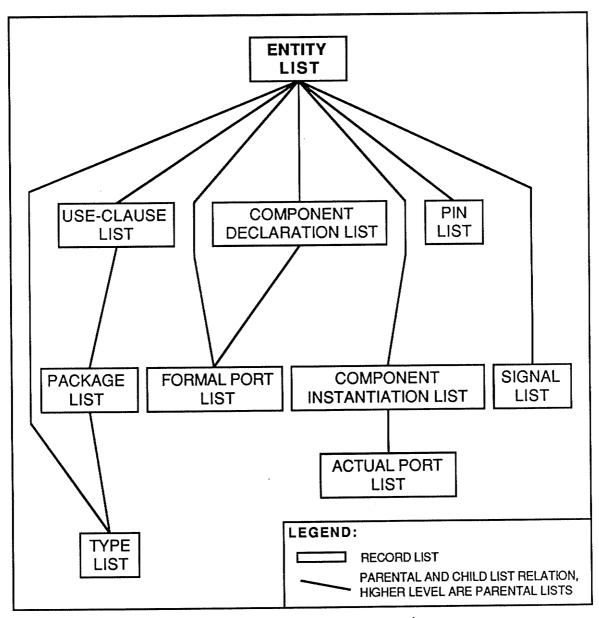

The Internal VHDL Representation (IVHDL) is a list of records called entity list. Some items in the records are sublists which are lists of some other records. The relation of the lists is shown in Fig. 4.6.

Fig. 4.6. Internal VHDL representation.

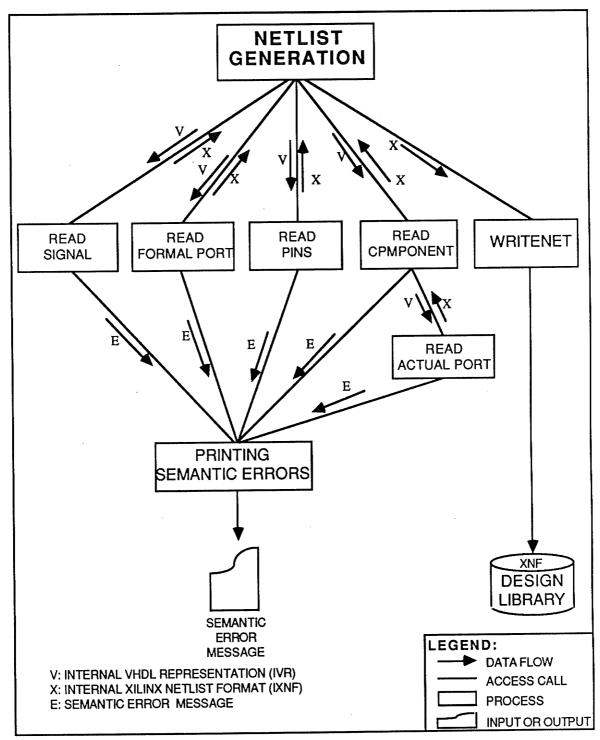

#### 4.4. Xilinx Netlist Format Generation

After the IVHDL is obtained, it has to be converted into the internal Xilinx Netlist Format (IXNF) in order to generate the XNF files. Xilinx provides a program for the generation of the XNF file from IXNF.

The conversion starts from the entity list, since each design entity results in an XNF file. Then, the sublists in entity list are read, such as signal list, formal port list, pin list and component instantiation list. The actual port list is read when component instantiation is read. While the IVHDL is read, the corresponding IXNF is generated. The structure of the netlist generator is shown in Fig. 4.7.

## 4.4.1. Internal Xilinx Netlist Format

Xilinx provides the internal Xilinx Netlist Format (IXNF) and a program to generate the XNF files from the IXNF. The IXNF is also a group of record list that represents the XNF. WRITENET reads the lists and creates XNF files.

#### 4.5. Flattening

The XNF files generated by WRITENET are still hierarchical files. Some XNF files are the components in the higher XNF files. The XNF files need to be flattened before the design can be implemented. Xilinx also provides the flattening program which reads all the XNF files in the design library and the used XNF files in standard libraries,

also checks the syntax of the XNF files and reports any XNF syntax errors.

Fig. 4.7. Xilinx Netlist Format generation.

#### **CHAPTER 5**

# IMPLEMENTATION, TESTING AND VERIFICATION

The VHDL compiler is implemented on a SUN workstation in the C language. The C program code has a total of 1371 lines. The LEX and YACC tools in the UNIX system are used to generate the lexical analyzer and the parser. The LEX specification has 75 lines, which results in 537 lines of C program code generated by LEX. The YACC specification has 285 lines, which results in 651 lines of C program code generated by YACC. The total 2559 lines of C code are compiled together with C program code provided by Xilinx for writing and flattening the XNF files. The sizes of the VHDL compiler for LCA are 98304 KBYTE for SUN3 and 106496 KBYTE for SUN4. The program lists can be found in Appendix E.

An IBM PC/AT compatible computer is used for the Xilinx LCA Development System. The PC and the SUN workstation communicate through Ethernet. The XNF files generated by the VHDL compiler can be transmitted from the SUN workstation to the PC for implementation.