## DESIGN AND AN ANALYSIS OF THE STACKED MULTICELL CONVERTER WITH COMPARISON TO THE NEUTRAL POINT CLAMPED CONVERTER

Ву

#### LIJUAN WANG

A Thesis

Submitted to the Faculty of Graduate Studies

In Partial Fulfillment of the Requirements

For the Degree of

Master of Science

Department of Electrical and Computer Engineering University of Manitoba, Winnipeg, Manitoba

© Copyright by Lijuan Wang 2003

#### THE UNIVERSITY OF MANITOBA

#### **FACULTY OF GRADUATE STUDIES**

\*\*\*\*

#### **COPYRIGHT PERMISSION**

Design and an Analysis of the Stacked Multicell Converter with Comparison to the Neutral Point Clamped Converter

BY

#### Lijuan Wang

A Thesis/Practicum submitted to the Faculty of Graduate Studies of The University of Manitoba in partial fulfillment of the requirement of the degree

Of

Master of Science

Lijuan Wang © 2003

Permission has been granted to the Library of the University of Manitoba to lend or sell copies of this thesis/practicum, to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film, and to University Microfilms Inc. to publish an abstract of this thesis/practicum.

This reproduction or copy of this thesis has been made available by authority of the copyright owner solely for the purpose of private study and research, and may only be reproduced and copied as permitted by copyright laws or with express written authorization from the copyright owner.

# The author Want to express her respect and appreciate to her beloved parents

Her father, Wang Renyu

Her mother, Peng Suhu

### Acknowledgements

The author would like to express her deep appreciation to Professor R.W.Menzies, the author's advisor, for his valuable guidance and discussions, useful suggestions, and great encouragement throughout this project, especially his kindness and friendship making this period a happy and memorable experience.

Thanks to Professor Ani M.Gole for his kindly help and helpful discussions of the work.

The author also wishes to thank Professor R.W.Menzies for financial support for this project.

Finally, the author wants to express her heartfelt thanks to her beloved husband whose love, understanding and endless heart care were the important ingredients during the period of the project.

#### Abstract

This study is the comparison of the design and analysis of the Stacked Multicell Converter (SMC) with the Neutral Point Clamped (NPC) converter. Multilevel converters are becoming increasingly popular for high power applications, because they can considerably reduce the output voltage and current harmonics by using several voltage levels while still switching the devices at the same frequency. The diode clamped converter (DCC) and the SMC converter are two types of multilevel converters which both use one DC bus subdivided into a number of voltage levels by a series string of capacitors. This kind of structure can reduce the blocking voltage requirement of each switching device. The three-level DCC converter, which is also called the NPC converter, has been put into practical use for large capacity ac motor drives in industry. Due to the voltage limitations of the switching devices, series connection of the devices is required in high-voltage and high-power applications with the NPC structure. Higher level DCC can solve this problem, but another problem of voltage unbalance between the outer dc capacitors and inner dc capacitors occurs. Although methods have been proposed to balance the capacitor voltage, they have not been put into practice by the industry.

In this thesis we present a new topology called the SMC which allows increasing input voltage level, while not increasing the switching device stresses by the use of floating capacitors. This thesis gives the design of the SMC including a method of pre-charging the floating capacitors, selection of the floating capacitors, and analysis of the commutation requirements. Both the converters are simulated using EMTDC and PWM techniques and compared in theory and experiment.

#### **Table of Contents**

| CHAPTER 1 INTRODUCTION                                        | j        |

|---------------------------------------------------------------|----------|

| 1.1 Background                                                | · ]      |

| 1.2 Purpose                                                   | · 3      |

| 1.3 Thesis Outline                                            | 4        |

| CHAPTER 2 BASIC ANALYSIS OF THE VOLTAGE SOURCE INVERTER       | <i>t</i> |

| 2.1 Basic Operation for the VSI                               | 7        |

| 2.2 Basic Control for the VSI                                 | 9        |

| 2.3 PWM Switching Techniques for the VSI                      | 11       |

| 2.3.1 Carrier Based PWM Technique                             | 11       |

| 2.3.2 Optimal Pulse Pattern (OPP) Technique                   | 15       |

| 2.3.3 Comparison of Carrier-based PWM and OPP Techniques      |          |

| 2.4 Chapter Summary                                           | 17       |

| CHAPTER 3 BASIC THEORY OF MULTILEVEL CONVERTER                | 19       |

| 3.1 Description of Diode Clamped Converter                    | 20       |

| 3.1.1 Neutral Point Clamped Converter                         | 20       |

| 3.1.2 Multilevel Diode Clamped Converter (DCC)                | 22       |

| 3.1.3 Switching Technique for the DCC Converter               | 26       |

| 3.2 Description of Stacked Multicell Converter                | 30       |

| 3.2.1 Five-level 2x2 SMC Converter                            | 30       |

| 3.2.2 Multilevel SMC Converter                                | 32       |

| 3.2.3 Switching Technique for the SMC converter               | 34       |

| 3.3 Chapter Summary                                           | 37       |

| CHAPTER 4 COMMUTATION STUDY OF THREE-LEVEL NPC AND FIVE-LEVEL | L SMC    |

| CONVERTER                                                     |          |

| 4.1 Common Specifications for NPC and SMC converter                | 39        |

|--------------------------------------------------------------------|-----------|

| 4.2 Basic Design Principle for the Current Limiting Circuit        | 41        |

| 4.3 Steady Analysis of Three-level NPC                             | 42        |

| 4.3.1 Voltage Stress                                               |           |

| 4.3.2 Current Stress                                               |           |

| 4.4 Steady Analysis of Five-level SMC                              | 45        |

| 4.4.1 Voltage Stress                                               | 45        |

| 4.4.2 Current Stress                                               | 46        |

| 4.5 Converter Output Analysis                                      | 48        |

| 4.6 Chapter Summary                                                | 50        |

| CHAPTER 5 PERFORMANCE OF DC CAPACITORS AND FLOATING CAPACITORS     | 52        |

| 5.1 Basic Ripple Analysis on the Capacitor                         | 52        |

| 5.2 Voltage Unbalance Analysis                                     | 55        |

| 5.2.1 Voltage unbalance on the floating capacitor                  | 55        |

| 5.2.2 Principle of Voltage Balance Control                         | 59        |

| 5.3 Size Selection of DC Capacitors and Floating Capacitors        | 61        |

| 5.4 Chapter Summary                                                | 64        |

| CHAPTER 6 CONTROL SYSTEM ANALYSIS                                  | 65        |

| 6.1 Mathematical Model and Main Control Loop of the Control System | 66        |

| 6.2 Floating Capacitor Voltage Control Loop                        | 70        |

| 6.3 Start-up of the Converters                                     | 71        |

| 6.4 Test Study for the Control System                              | 72        |

| 6.4.1 Start-up of the Converter                                    | <i>73</i> |

| 6.4.3 Steady State Operation                                       | 76        |

| 6.4.4 Transient Operation                                          |           |

| 6.5 Chapter Summary                                                | 79        |

| CHAPTER 7 EXPERIMENTAL COMPARISON OF SMC TO NPC                    | 81        |

| 7.1 Voltage and Current Spectrum Comparison | 82  |

|---------------------------------------------|-----|

| 7.2 Device Stresses Comparison              | 87  |

| 7.3 Chapter Summary                         | 92  |

| CHAPTER 8 CONCLUSIONS AND FUTURE WORK       | 93  |

| 8.1 Conclusions                             | 93  |

| 8.2 Future work                             | 95  |

| REFERENCES                                  | 96  |

| APPENDIX A                                  | 98  |

| APPENDIX B                                  |     |

| APPENDIX C                                  |     |

| APPENDIX D                                  | 104 |

## **List of Figures**

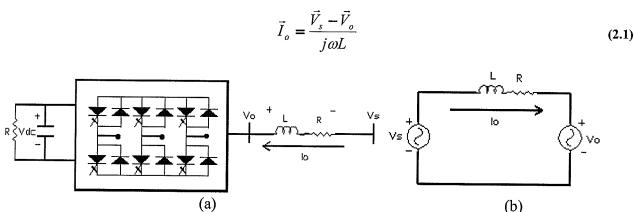

| Figure 2.1 Circuit Diagram and Simplified Model of a Three Phase Converter                                                                           | 7        |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

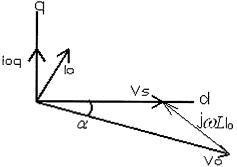

| Figure 2.2 Phasor Diagram of the VSI                                                                                                                 | 9        |

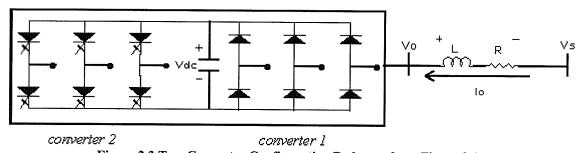

| Figure 2.3 Two Converter Configuration Redrawn from Figure 2.1a                                                                                      | 9        |

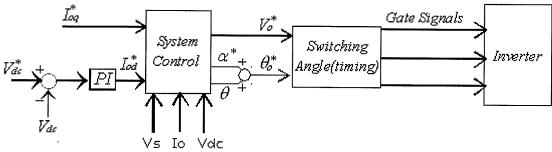

| Figure 2.4 The Basic Control Diagram for VSI                                                                                                         | 10       |

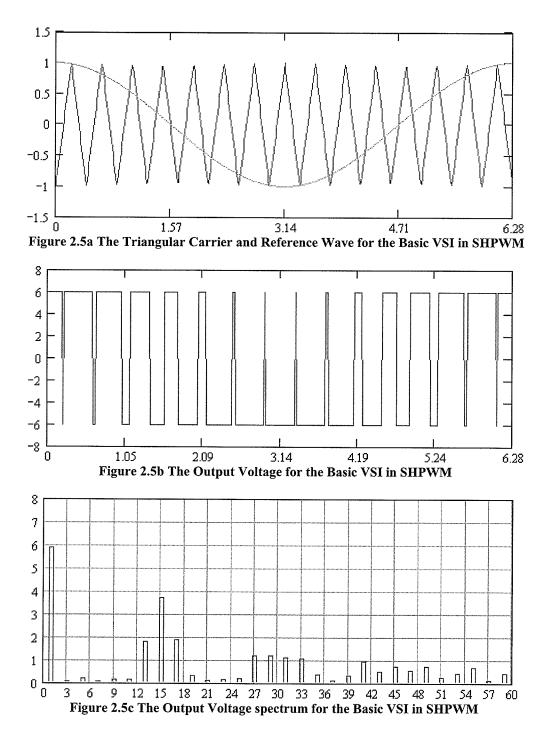

| Figure 2.5a The Triangular Carrier and Reference Wave for the Basic VSI in SHPWM                                                                     | 13       |

| Figure 2.5b The Output Voltage for the Basic VSI in SHPWM                                                                                            | 13       |

| Figure 2.5c The Output Voltage spectrum for the Basic VSI in SHPWM                                                                                   | 13       |

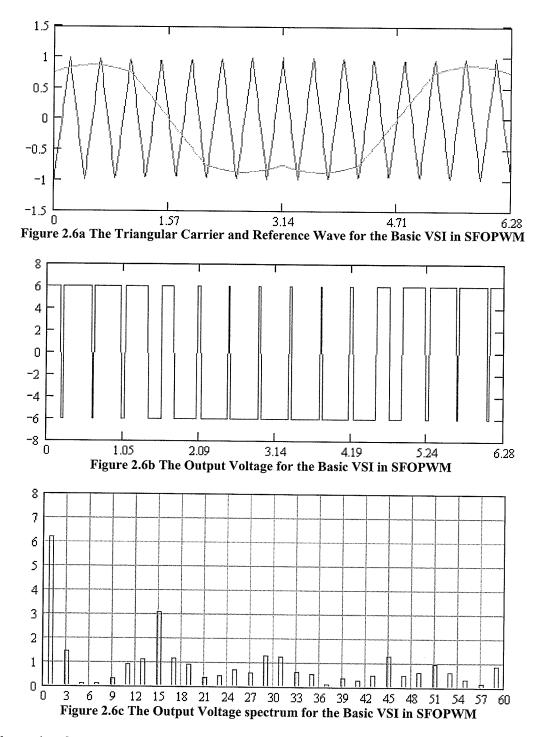

| Figure 2.6a The Triangular Carrier and Reference Wave for the Basic VSI in SFOPWM                                                                    | 14       |

| Figure 2.6b The Output Voltage for the Basic VSI in SFOPWM                                                                                           | 14       |

| Figure 2.6c The Output Voltage spectrum for the Basic VSI in SFOPWM                                                                                  | 14       |

| Figure 2.7 A Two Level PWM Waveform with Odd and Half-wave Symmetries                                                                                | 16       |

| Figure 3.1 Three-level NPC Converter circuit                                                                                                         | 21       |

| Figure 3.2 A Typical Voltage Waveform for the NPC                                                                                                    | 21       |

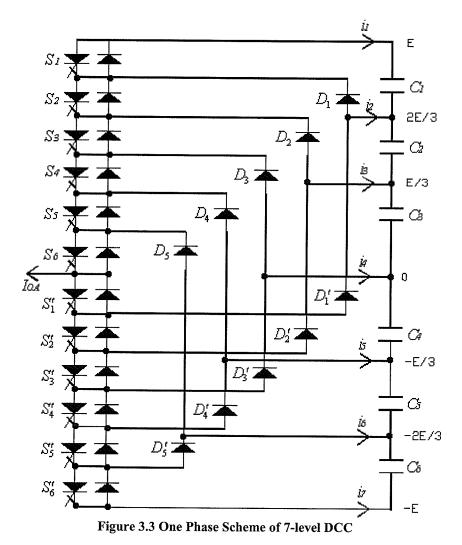

| Figure 3.3 One Phase Scheme of 7-level DCC                                                                                                           | 23       |

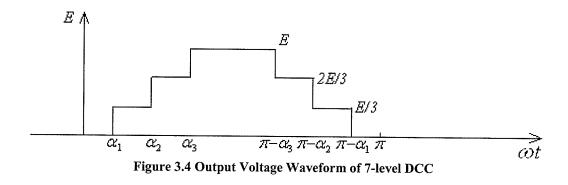

| Figure 3.4 Output Voltage Waveform of 7-level DCC                                                                                                    | 24       |

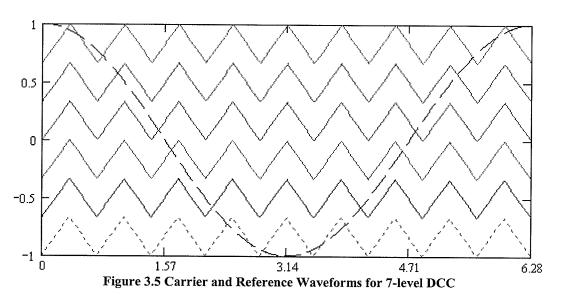

| Figure 3.5 Carries and Reference Waveforms for 7-level DCC                                                                                           | 27       |

| Figure 3.6a The Triangular Carriers and Modulation Wave for Three-level NPC Using SHPWM                                                              | 29       |

| Figure 3.6b The Three-level Output Voltage for NPC Using SHPWM                                                                                       | 29       |

| Figure 3.7a The Triangular Carriers and Modulation Wave for Three-level NPC Using SFOPWM                                                             | 29       |

| Figure 3.7b The Three-level Output Voltage for NPC Using SFOPWM                                                                                      | 30       |

| Figure 3.8 Topology of a 2x2 Stacked Multicell Converter                                                                                             | 30       |

| Figure 3.9 Voltage Constraints on Switches                                                                                                           | 31       |

| Figure 3.10 A Generalized Structure of One Phase for an N-level nxp SMC                                                                              |          |

| Figure 3.11a The Triangular Carriers and Modulation Wave for Five-level SMC Using SHPWM                                                              | 32       |

| Figure 3.11b The Five-level Output Voltage for SMC Using SHPWM                                                                                       | 35       |

| Figure 3.12a The Triangular Carriers and Modulation Wave for Five-level SMC Using SFOPWM                                                             | 35       |

| Figure 3.12b The Five-level Output Voltage for SMC Using SFOPWM                                                                                      | 36       |

| Figure 4.1 The Current Limiting circuit                                                                                                              | 36       |

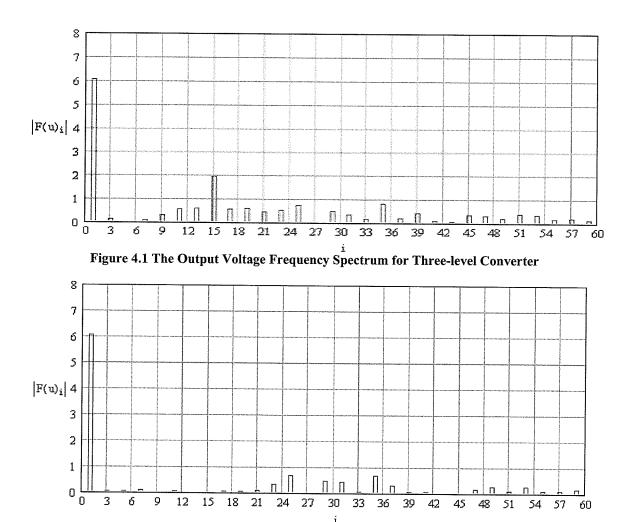

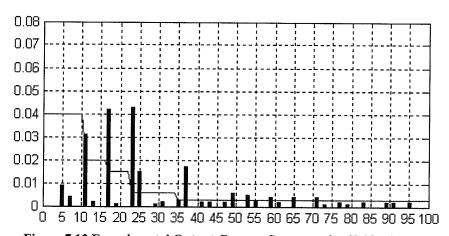

| Figure 4.1 The Output Voltage Frequency Spectrum for Three-level Converter                                                                           | 42       |

| Figure 4.1 The Output Voltage Frequency Spectrum for Five-level Converter  Figure 4.2 The Output Voltage Frequency Spectrum for Five-level Converter | 50<br>50 |

| Figure 5.1 Basic Voltage Pulse of the Converter                                                                                                      | 50<br>53 |

| Figure 5.2 Simple model of 2-cell Multicell Converter                                                                                                | 53       |

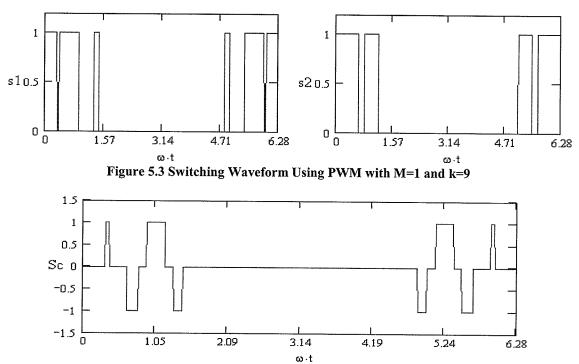

| Figure 5.3 Switching Waveform Using PWM with M=1 and k=9                                                                                             | 55<br>57 |

| Figure 5.4 Switching Waveform for the Floating Capacitor Current                                                                                     | 57<br>57 |

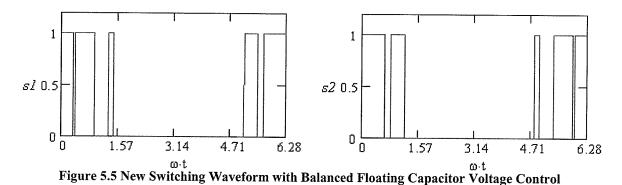

| Figure 5.5 New Switching Waveform with Balanced Floating Capacitor Voltage                                                                           | 57       |

|                                                                                                                                                      | 59       |

| Figure 5.6 New Switching Waveform for the Floating Capacitor Current                                                                                 | 60       |

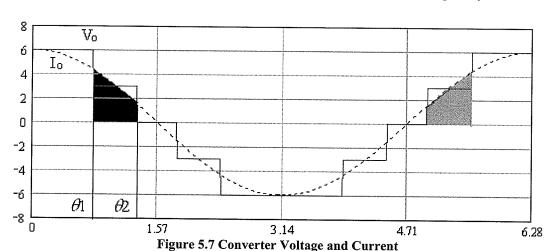

| Figure 5.7 Converter Voltage and Current                                                                                                             | 63       |

| Figure 6.1 Equivalent Circuit of the System                                                                                                          | 66       |

| Figure 6.2 The Vector Diagram in $dq\omega$ Coordinates                                                                                              | 68       |

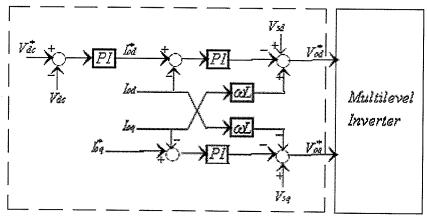

| Figure 6.3 Detail Diagram for the Main System Control                                                                                                | 69       |

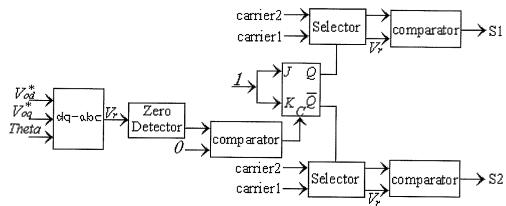

| Figure 6.4 The Floating Capacitor Voltage Control Loop                                                                                               | 71       |

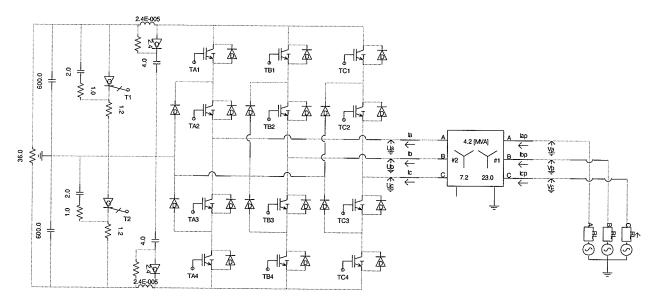

| Figure 6.5 Configuration of the Three-level NPC                                                                                                      | 72       |

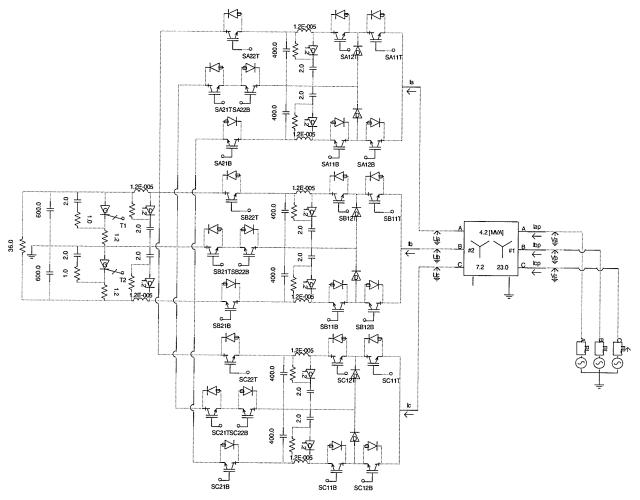

| Figure 6.6 Configuration of the Five-level SMC                                                                                                       | 73       |

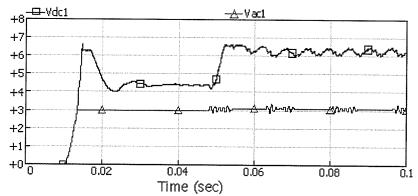

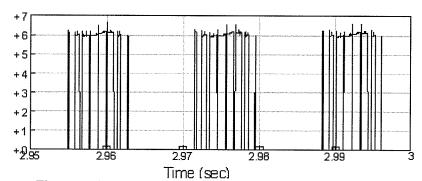

| Figure 6.8 The Primary Current and Voltage During the Start-up                                                                                       | 74       |

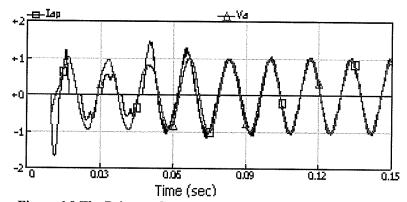

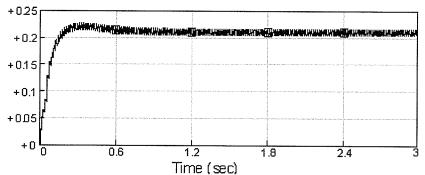

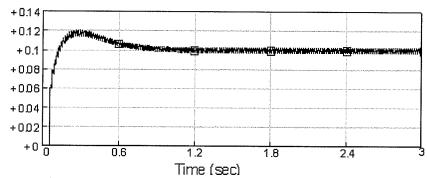

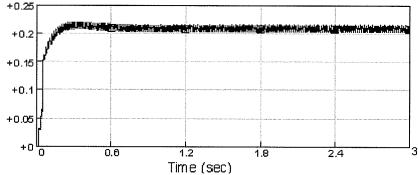

| Figure 6.9 The Floating Capacitors Voltage Without the Balance Control                                                                               | 75       |

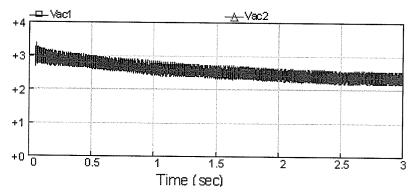

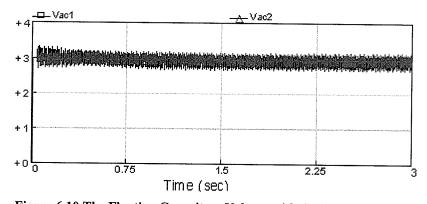

| Figure 6.10 The Floating Capacitors Voltage With the Balance Control                                                                                 | 75       |

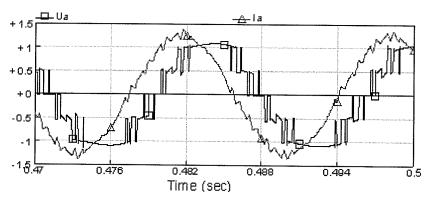

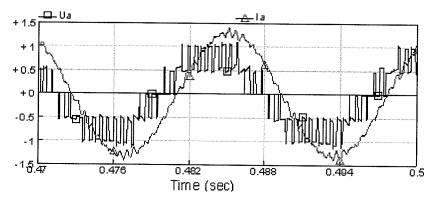

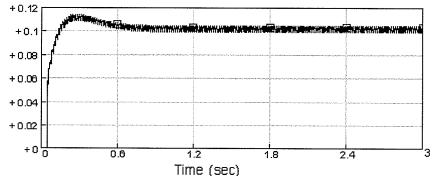

| Figure 6.11 The Output Voltage and Current of the 2x2 SMC Using PWM in Capacitive Mode                                                               | 77       |

| Figure 6.12 The Output Voltage and Current of the 2x2 SMC Using PWM in Inductive Mode                                                                | 77       |

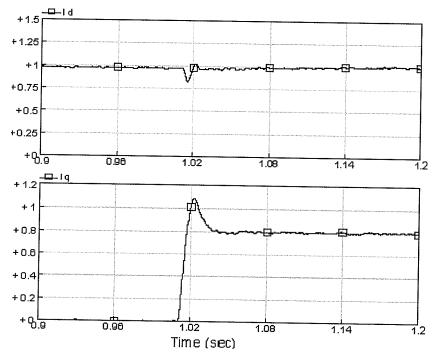

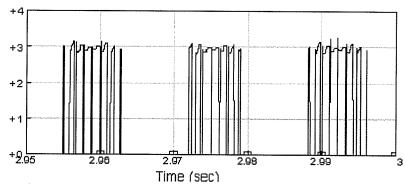

| Figure 6.13 Transient Response of the SMC                                                                                                            | 78       |

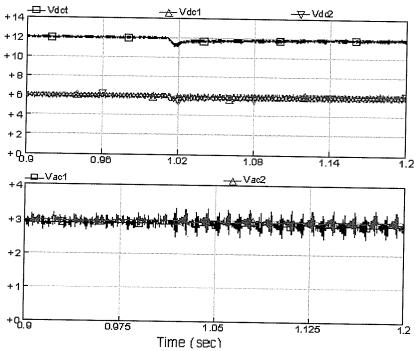

| Figure 6.14 Voltage Variations on the dc and Floating Capacitors during Transient Operation                                                          | 78       |

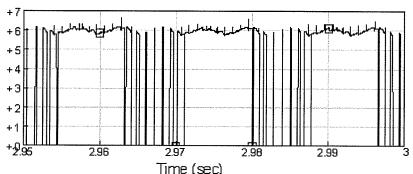

| Figure 6.15 The Output Voltage and Current of the SMC during Transient Operation                                                                     | 79       |

| τ | 7 | Y |

|---|---|---|

| ١ | / | ı |

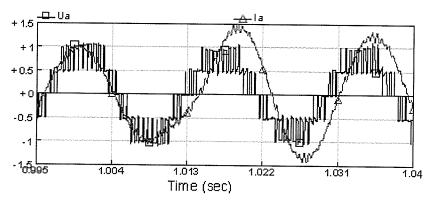

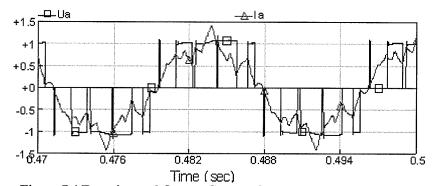

| Figure 7.1 Experimental Output Voltage and Current for NPC with k=15     | 83 |

|--------------------------------------------------------------------------|----|

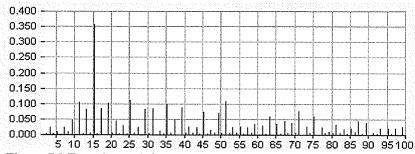

| Figure 7.2 Experimental Output Voltage Spectrum for NPC with k=15        | 84 |

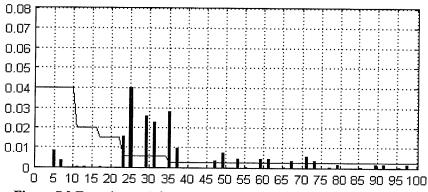

| Figure 7.3 Experimental Output Current Spectrum for NPC with k=15        | 84 |

| Figure 7.4 Experimental Output Current Spectrum for NPC with k=9         | 84 |

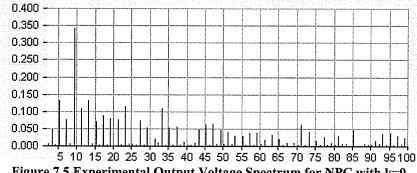

| Figure 7.5 Experimental Output Voltage Spectrum for NPC with k=9         | 84 |

| Figure 7.6 Experimental Output Current Spectrum for NPC with k=9         | 85 |

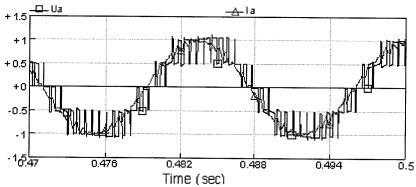

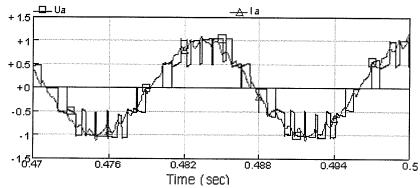

| Figure 7.7 Experimental Output Voltage and Current for SMC with k=15     | 85 |

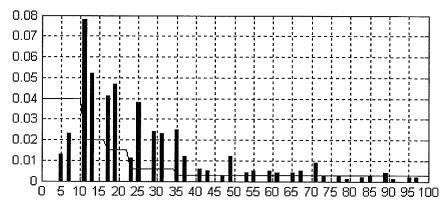

| Figure 7.8 Experimental Output Voltage Spectrum for SMC with k=15        | 85 |

| Figure 7.9 Experimental Output Current Spectrum for SMC with k=15        | 85 |

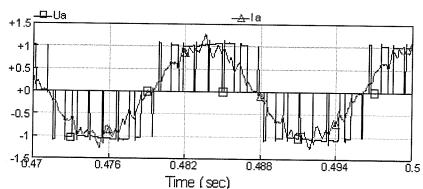

| Figure 7.10 Experimental Output Voltage and Current for SMC with k=9     | 86 |

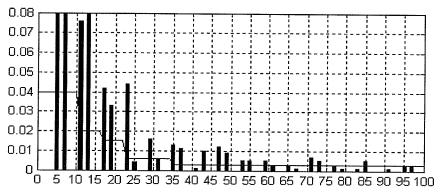

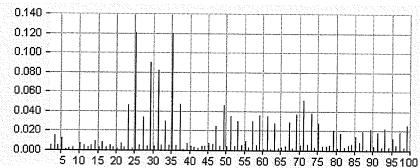

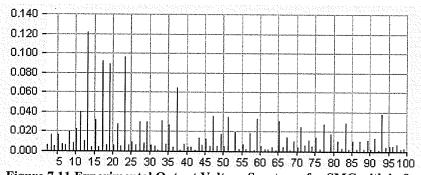

| Figure 7.11 Experimental Output Voltage Spectrum for SMC with k=9        | 86 |

| Figure 7.12 Experimental Output Current Spectrum for SMC with k=9        | 86 |

| Figure 7.13 Experimental RMS Current on Diode of T1 of NPC Circuit       | 88 |

| Figure 7.14 Experimental RMS Current on T3 of NPC Circuit                | 88 |

| Figure 7.15 Experimental Voltage Stress on T1 of NPC Circuit             | 89 |

| Figure 7.16 Experimental Voltage Stress on T2 of NPC Circuit             | 89 |

| Figure 7.17 Experimental RMS Current on Diode of S11T in SMC Circuit     | 90 |

| Figure 7.18 Experimental RMS Current on Thyristor of S12B in SMC Circuit | 90 |

| Figure 7.19 Experimental Voltage Stress on S11T of SMC Circuit           | 91 |

| Figure 7.20 Experimental Voltage Stress on S12T of SMC Circuit           | 91 |

| Figure 7.21 Experimental Voltage Stress on S21T of SMC Circuit           | 91 |

| Figure 7.22 Experimental Voltage Stress on S22T of SMC Circuit           | 91 |

## List of Tables

| Table 2.1 Calculated Percent Harmonic Voltage Content using Carrier-based PWM for Basic VSI | 15 |

|---------------------------------------------------------------------------------------------|----|

| Table 3.1 The Switching Logic for 7-level NPC                                               | 24 |

| Table 3.2 The Switching Logic for Three-level NPC                                           | 27 |

| Table 3.3 Typical Calculation Results for the NPC Converter                                 | 28 |

| Table 3.4 The Switching Logic for N-level SMC                                               | 33 |

| Table 3.5 The Switching Logic for Five-level 2x2 SMC                                        | 35 |

| Table 3.6 Typical Calculation Results for the SMC Converter                                 | 37 |

| Table 4.1 Similarity between NPC and SMC                                                    | 48 |

| Table 4.2 Typical Results Using SHPWM Method (M=1)                                          | 49 |

| Table 5.1 The Required Capacitance in the Worst case                                        | 64 |

| Table 6.1 Voltage and Current Spectrum Comparison without and with Balance Control          | 76 |

| Table 7.1 Voltage Spectrum Comparison between NPC and SMC                                   | 82 |

| Table 7.2 Current Spectrum Comparison between NPC and SMC                                   | 83 |

Introduction

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Background

Power converters make use of a configuration of power semiconductor devices that function as switches. They have shown rapid development in recent years, primarily because of the development of semiconductor power devices that can switch larger currents at higher voltages, and so can be used for the conversion and control of electrical energy at higher power levels. The electrical energy is converted to make it suitable for various applications such as regulated power supplies, active power filters, heating and lighting control [1], dc and ac motor drive application, welding control, static VAR compensation and HVDC transmission.

During the past few decades of power electronic device and circuit development a number of concepts have been examined. Low blocking voltage (50V-500V) and medium voltage (500V-1800V) applications have found a number of satisfactory candidates, but at high voltage (2500V-9000V) compromises still seem to dominate and development work is necessary. Gate Turn Off Thyristors (GTO), Integrated Gate Commutated Thyristors (IGCT) and Insulated Gate Bipolar Transistors (IGBT) are the high power semiconductors currently available on the market which can be turned off actively. A short background review of the field's history may help to understand the root of this thesis work [2].

Introduced in the late 1950's, thyristors have been the only choice for power electronic applications requiring ≥2.5kV blocking for more than 20 years. With these elements only the moment of turn-on could be influenced by the gate drive, while turn-off had to be initiated by a reversal of the device current. As a consequence, realization of circuits transferring energy from AC sources to AC or DC loads was much easier at that time than realization of circuits with DC sources or DC voltage links.

The GTO thyristor, adding forced gate commutation to control the turn-off, was invented in 1960, but it was not developed for high power applications until the late 70's. At that time, the voltage source converter (VSI) topology entered the field, leading to a drastic increase in performance of important application areas like traction converters and industrial drives.

At the same time a number of innovations and changes were observed close to the GTO's domain at blocking voltages below 2000V. Before the GTOs really could establish themselves in that area, bipolar transistors entered, and were soon followed by the IGBT. Although the IGBTs suffered from a loss of control by undesired latching for many years, device development was continued to finally overcome that constraint. Then, the IGBT began its success in improving

Introduction 3

current and voltage handling capability and switching performance step by step. But the IGBTs are still limited to medium power applications.

The quest in last ten years for high-power snubberless semiconductor switches to replace the conventional GTO has led to the IGCT technology. Currently the IGCT is the optimum combination of the proven, low-cost thyristor technology and the snubberless, cost-effective gate turn-off capability for demanding medium and high-voltage power electronic application [3]. The introduction of the IGCTs has substantially advanced the development of high power hard switching Pulse Width Modulation (PWM) Voltage Source Converters for industrial and traction applications. The switching frequencies are typically limited to about 500 to 1000Hz by the switching losses with snubberless operation.

The development of power semiconductor technology indicates a tradeoff in the selection of power devices in terms of switching frequency and voltage-sustaining capability [4]. Normally, the voltage-blocking capability of faster devices such as the IGBT, and the switching speed of high-voltage IGCT, are found limited.

#### 1.2 Purpose

With respect to the design of the voltage source converter topology, the conventional two-level converter can not satisfy the market requirements of harmonic distortion and dynamic control. This leads to increasing interest in the multilevel power converter. These converters are suitable in high-voltage and high-power applications due to their ability to synthesize waveforms with better spectrum and attain higher voltages with a limited maximum device rating. To date the industry appears to have settled on the three-level NPC converter as the best compromise.

There are many possible circuit configurations for realizing a practical multilevel converter. This thesis will compare a five-level Stacked Multicell Converter (SMC) against a benchmark three-

level Neutral Point Clamped Converter (NPC) of similar ratings that are connected between an ac system and a dc load. The focal point of the investigation will be the number of switches, the device stresses, the harmonic performance of the output voltages and currents in the two types of converter. Along with this, the switching method and the capacitor performance are to be analyzed. The control system will be designed to regulate the dc voltage, as well as the reactive power production or absorption. The main tool used in this investigation is the electromagnetic transient simulation program called PSCAD/EMTDC<sup>TM</sup>.

#### 1.3 Thesis Outline

Chapter 2 of this thesis gives a general introduction to the voltage source inverter. The operating principle and the four-quadrant operating characteristic of the VSI is explained. The general control idea is introduced based on the basic two-level VSI, which can be also applied to the multilevel converters. Two types of pulse width modulation (PWM) are compared based on the basic VSI and carrier-based PWM is chosen as the switching method in later chapters.

In Chapter 3, a general introduction to multilevel converters is given. The detail configurations of the three-level NPC and the five-level 2x2 SMC are presented and extended to higher level. The advantages and constraints for both converter circuits are analyzed. The switching methods for the NPC and SMC converter are presented respectively and analyzed using MATHCAD software.

Chapter 4 describes the common specification for the three-level NPC and five-level SMC from the aspects of DC side capacitor, number of switches and device stresses. The output voltage spectrum of the two different structures are analyzed and compared. The advantages and disadvantages of each design are discussed.

Introduction 5

Chapter 5 explains the performance of capacitors in the converters. First a basic theory about the capacitors is given. Then the voltage unbalance existing in the capacitors is analyzed and the design principle of voltage balance control is developed. Finally the principle to choose the size of the capacitors is presented.

Chapter 6 develops a mathematical model for the control system and pre-charging method for the converter. Simulation study for the control system are carried out using EMTDC which include test of start-up of the SMC, the voltage balance control for capacitors, steady state operation and transient operation.

Chapter 7 gives detailed simulation results for the three-level NPC and five-level SMC using EMTDC. The output voltage and current waveforms are presented and the harmonics are analyzed using LIVEWIRE software for both types of converter. The simulation results for the NPC and the SMC are compared with respect to the voltage level, harmonics in the supply voltage and current, and device voltage and current stresses.

#### **CHAPTER 2**

#### BASIC ANALYSIS OF THE VOLTAGE SOURCE INVERTER

Voltage source inverters (VSI) are commonly used to transfer real power from a dc source voltage to an ac load such as an ac motor [5]. The output current waveforms of the inverter must be as close as possible to a sinusoidal wave and therefore reducing the current harmonics is a major concern. The output voltage can be controlled by either the fundamental frequency switching (FFS) or PWM switching techniques, which controls the output voltage by altering the switching pattern with a constant dc voltage, or by varying the dc voltage with a fixed switching pattern. In this thesis, the focus is on the case with a constant dc capacitor voltage. This means the real component of the current flowing into the converter must be controlled. This is

accomplished by controlling the magnitude and phase of the converter ac voltage as will be discussed later.

The FFS technique has a limited switching pattern and hence a high harmonic content over much of the operating ranges. PWM techniques are simple to apply and are able to control harmonics over a wider operating range. Therefore, this thesis will restrict the switching methods to PWM techniques in this thesis.

#### 2.1 Basic Operation for the VSI

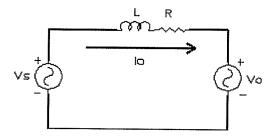

The operating principle of the VSI can be best explained with the aid of the simplified model of the three-phase circuit shown in Figure 2.1a, which consists of a basic two-level VSI. Figure 2.1b shows the per-phase fundamental equivalent circuit of the system. An equivalent voltage source  $\vec{V}_o$ , which is the fundamental component of the converter output voltage, is connected to the ac main system through a reactor. The inductance L represents any series inductance between the inverter ac voltage and the ac system voltage and the resistance R represents any resistance associated with the converter and the supply as a lumped value as shown in figure 2.1b. Usually, R is small so that we can ignore it. From this simplified model, the output current  $\vec{I}_o$  can be expressed as follow:

Figure 2.1 Circuit Diagram and Simplified Model of a Three-Phase Converter

The ac system voltage is assumed as the reference with a zero phase angle. It can easily be seen from Equation 2.1 that the magnitude and direction of the output current  $\vec{I}_o$  can be regulated by the amplitude and phase angle of the variable converter output voltage  $\vec{V}_o$ . In general, we assume the converter output voltage  $\vec{V}_o$  with a magnitude  $V_o$  and phase shift angle  $\alpha$  with respect to  $V_s$ . Then the reactive component of the output current can be given as:

$$I_{oq} = \frac{-V_s + V_o \cdot \cos \alpha}{\omega L} \tag{2.2}$$

thus the corresponding reactive power is:

$$Q = \frac{-V_s^2 + V_o \cdot V_s \cdot \cos \alpha}{\omega L}$$

Similarly, the active component of the output current can be given as:

$$I_{od} = \frac{-V_o \cdot \sin \alpha}{\omega L} \tag{2.3}$$

The corresponding active power is:

$$P = \frac{-V_o \cdot V_s \cdot \sin \alpha}{\omega L}$$

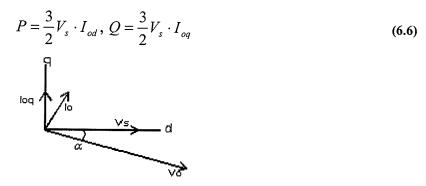

From Equation (2.2) and (2.3), we can easily see that both reactive and active current can be positive or negative. When  $V_o \cdot \cos \alpha$  is larger than  $V_s$ ,  $I_{oq}$  is positive. This means  $-90^\circ < \alpha < 90^\circ$ . In this operating region,  $I_{od}$  is positive for  $-90^\circ < \alpha < 0^\circ$  and negative for  $0^\circ < \alpha < 90^\circ$ . When  $V_o \cdot \cos \alpha$  is smaller than  $V_s$ ,  $I_{oq}$  is negative. In this operating region,  $\alpha$  can be any value between  $0^\circ$  and  $360^\circ$  and therefore  $I_{od}$  can also be positive or negative. Generally speaking, the VSI can operate in all the four quadrants. The phasor diagram of the VSI is shown in Figure 2.2.

Figure 2.2 Phasor Diagram of the VSI

#### 2.2 Basic Control for the VSI

The converter shown in Figure 2.1a is inherently two converters connected in inverse parallel and can be redrawn as Figure 2.3. Converter 1 acts as an uncontrolled rectifier to allow the real power flowing from the ac side to the dc side. Converter 2 operates in the converter mode, where the polarity of the voltage across the dc capacitor  $V_{dc}$  remains the same but the direction of the dc side current  $I_d$  is reversed. Initially, when converter 2 is not conducting, capacitor charges up to the peak value of the supply voltage through converter1. This characteristic of the VSI provides the possibility to pre-charge the dc capacitors directly through the ac system. Providing no real power transfer occurring between the circuit and the supply, the capacitor voltage remains at its initial charged voltage and acts as a constant dc source.

Figure 2.3 Two Converter Configuration Redrawn from Figure 2.1a

The control strategy adopted in this investigation is based on the PWM switching technique. As described in Section 2.1, both reactive power and active power should be controlled and the dc capacitor voltage should remain constant. Then, there are two main tasks that the control scheme

has to achieve. One is to control the converter input power factor or the reactive component of the current, and the other is to control the real power flowing into the dc load to maintain a constant voltage across the dc capacitors. Figure 2.4 shows the basic control diagram that was designed to perform the above tasks.

Figure 2.4 The Basic Control Diagram for VSI

Where  $V_{dc}^{\phantom{\dagger}}$  is the reference dc voltage and  $V_{dc}$  is the measured voltage,  $I_{od}^{\phantom{\dagger}}$  and  $I_{oq}^{\phantom{\dagger}}$  are the reference active and reactive current respectively,  $V_o^{\phantom{\dagger}}$  and  $\alpha^*$  is the magnitude and phase angle of the reference output voltage respectively.  $\theta$  comes from a phase locked loop (PLL) locked to the system frequency which is used to obtain the phase angle,  $\alpha$ , the angle difference between converter output and ac system voltage.

Given a certain reactive and active current, from Equation 2.2 and 2.3, the magnitude and phase angle of the reference output voltage could be expressed as:

$$V_o^* = \sqrt{(I_{oq}^* \cdot \omega L + V_s)^2 + (I_{od}^* \cdot \omega L)^2}$$

(2.4)

$$\alpha^* = -\arctan(\frac{I_{od}^* \cdot \omega L}{I_{oq}^* \cdot \omega L + V_s})$$

(2.5)

The control loop to maintain the constant capacitor voltage is implemented by comparing the actual dc voltage and the reference dc voltage. The error of the two signals passes through a PI controller and thus obtains the required real power to the dc capacitor. This real power divided

by the constant supply voltage provides the reference real component of the supply current. The reactive current component  $I_{oq}^{\phantom{oq}}$  does not affect the dc voltage but does affect the power factor of the VSI as seen from the ac system. This component is normally set to zero, but may vary if some form of power factor control is required. These two reference currents are compared to the measured real and reactive current components of the input current, and the magnitude and phase of the converter voltage is adjusted according to Equations 2.4 and 2.5. This reference output voltage can then be used to calculate the switching signals of the converter by using PWM techniques. With above control, both the magnitude and phase angle of the output voltage can be continuously controlled to maintain a constant dc voltage and constant reactive current component. The detail mathematical model for the system control block will be presented in Chapter 6.

#### 2.3 PWM Switching Techniques for the VSI

The PWM switching technique is the most common method to control output voltages of a voltage source converter due to its simplicity and ability to reduce the harmonic content. These techniques can be classified into two types: carrier-based PWM methods and optimal PWM methods. The carrier-based PWM methods include subharmonic PWM (SHPWM) and switching frequency optimization PWM (SFOPWM) [6]. These techniques have also been extended to various multilevel VSI topologies.

#### 2.3.1 Carrier Based PWM Technique

In carrier based PWM techniques, the switches are operated many times in the fundamental ac cycle producing a pulsed waveform with reduced harmonic content. The switching instants are defined by the crossings of a carrier triangular wave and the sinusoidal reference signal.

The SHPWM method uses a set of triangular carriers to compare with the reference sinusoidal wave. The SFOPWM method is similar to the SHPWM method, except that the reference modulation waveform is a sinusoidal wave with a zero sequence voltage added. The zero sequence voltage can be expressed as the average value of the maximum and minimum values of the three reference modulation waveforms, or can be a third harmonic component added to the reference waveform. The advantage of this technique is that it will allow the modulation index to increase by about 15% before overmodulation and pulse dropping occurs and does not produce zero sequence currents in the three-phase, three-wire configuration.

The main parameters of the modulation process are:

- 1) The frequency ratio  $k = \frac{f_c}{f_m}$ , where  $f_c$  is the frequency of the carriers, and  $f_m$  is the frequency of the modulation wave.

- 2) The modulation index  $M = \frac{A_m}{A_C}$ , where  $A_m$  is the amplitude of the modulation wave, and  $A_c$  is the peak to peak of the carriers.

- 3) Usually, the frequency ratio is chosen as an odd number which is the multiple of three so that the triple harmonic will not occur in the line voltage even though some of them appear in the phase voltage.

For the basic two-level VSI, one triangular carrier waveform is compared with the reference waveform to get the device switching signals. The carrier and reference waveform for SHPWM are shown in Figure 2.5a. Figure 2.5b and 2.5c show an example for the corresponding output voltage and its spectrum using the above switching logic where  $f_m$ =60 Hz, k=15 and M=1.

The carrier and reference waveform for SFOPWM are shown in Figure 2.6a. Figure 2.6b and 2.6c show an example for the corresponding output voltage and its spectrum using the above switching logic where  $f_m$ =60 Hz, k=15 and M=1.

Typical results for SHPWM and SFOPWM are shown in Table 3.5, which gives the total harmonic distortion factor (THD) for each case.

The total harmonic distortion factor was defined as the ratio of the root-mean-square of the harmonic content to the root-mean-square of the fundamental quantity, which is expressed as a percent of the fundamental, which gives:

$$THD = (\frac{\text{Sum of squares of amplitude of all harmonics}}{\text{Square of amplitude of fundamental}})^{1/2}$$

Table 2.1 Calculated Percent Harmonic Voltage Content using Carrier-based PWM for Basic VSI

| using Carrier-based PWM for Basic VSI |       |        |  |  |  |  |  |  |

|---------------------------------------|-------|--------|--|--|--|--|--|--|

| Harmonic                              | SHPWM | SFOPWM |  |  |  |  |  |  |

| 1                                     | 95.5  | 1      |  |  |  |  |  |  |

| 5                                     | 3.1   | 1.9    |  |  |  |  |  |  |

| 7                                     | 0.8   | 1.4    |  |  |  |  |  |  |

| 11                                    | 2.4   | 14.8   |  |  |  |  |  |  |

| 13                                    | 30.7  | 17.7   |  |  |  |  |  |  |

| 17                                    | 31.8  | 18.3   |  |  |  |  |  |  |

| 19                                    | 5.3   | 14.7   |  |  |  |  |  |  |

| 23                                    | 2.8   | 7      |  |  |  |  |  |  |

| 25                                    | 3.5   | 11     |  |  |  |  |  |  |

| 29                                    | 20.4  | 20.4   |  |  |  |  |  |  |

| 31                                    | 19    | 19.7   |  |  |  |  |  |  |

| 35                                    | 6.2   | 8.3    |  |  |  |  |  |  |

| 37                                    | 2.2   | 1.7    |  |  |  |  |  |  |

| 41                                    | 15.7  | 4.5    |  |  |  |  |  |  |

| THD <sub>V</sub> %                    | 0.602 | 0.518  |  |  |  |  |  |  |

It is seen from Table 2.1 that the first large harmonic occurs around 15 for both SHPWM and SFOPWM and then around 30. For SHPWM, 13th and 17th harmonics are significant. For SFOPWM, 11th, 13th, 17th and 19th harmonics are significant. These harmonics are all easily filtered. The fundamental component of these two types of carrier-based PWM is a good approximation to the desired reference waveform though still containing some quantities of the characteristic harmonics.

#### 2.3.2 Optimal Pulse Pattern (OPP) Technique

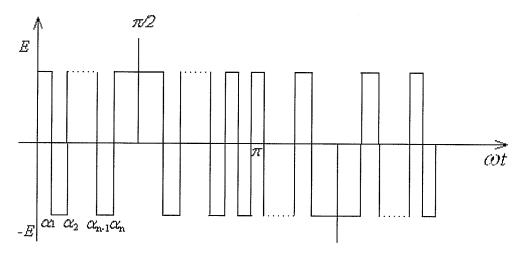

The most important characteristic of the OPP technique is that it can provide the required harmonic reduction with the minimum number of switchings. As an example, for a two-level

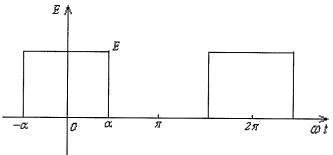

PWM waveform with odd and half-wave symmetries which has n switchings per quarter cycle as shown in Figure 2.7, the magnitude of harmonics are given as follow:

$$b_k = \frac{4E}{k\pi} (1 - \sum_{j=1}^{n} (-1)^j 2 \cdot \cos k\alpha_j)$$

(2.6)

In which  $k=1,3,5,7,\ldots, j=1,2,3,4,\ldots, b_k$  is the magnitude of the kth harmonic and  $\alpha_j$  is the jth primary switching angle. Even harmonics do not appear because of the half-wave symmetry.

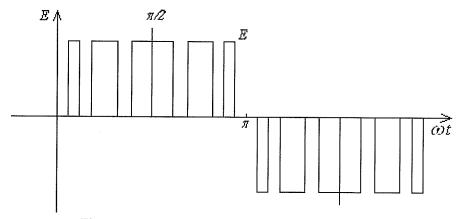

Figure 2.7 A Two Level PWM Waveform with Odd and Half-wave Symmetries

The n switchings in the waveform afford n degrees of freedom. Several control options are thus possible. For example n selected harmonics can be eliminated. Another option that is used here is to eliminate n-1 selected harmonics and use the remaining degree of freedom to control the fundamental frequency magnitude,  $b_1$  of the ac voltage. To find the  $\alpha$ 's required to achieve this objective, it is sufficient to set the corresponding  $b_k$ 's in the above equations to the desired values (0 for the n-1 harmonics to be eliminated and the desired ac magnitude for the fundamental) and solve for the  $\alpha$ 's.

The process of obtaining the correct switching angles for eliminating selected harmonics is normally accomplished in the following step [7]:

- a. Decide on the number and order of harmonics to be eliminated.

- b. By means of Fourier analysis obtain an expression that describes the harmonic content of the required waveform. Use this expression to assemble a set of equations and set to zero those harmonics selected for elimination.

- c. Solve these equations off-line for a range of modulation index values.

- d. Arrange for on-line access to these switching angles.

#### 2.3.3 Comparison of Carrier-based PWM and OPP Techniques

As will be shown later, the dc voltage and reactive power are controlled by the converter output voltage. This control can be achieved only by changing the switching angles when the OPP method is used. As well known, it is always possible to solve the equations for various values of designed fundamental ac voltage and store the results in a large look-up table. But in this case it has the problem that there may be some granularity in the solution when the controlling parameter (ac voltage magnitude) falls in between the two contiguous magnitudes. Using PWM techniques, however, the magnitude of the fundamental component can also be changed by varying the modulation index, which gives a smooth continuous control and fast response. Moreover, from a dynamic control point of view, there are advantages in using PWM techniques. Therefore in the later analysis, we will focus on the carrier-based PWM technique.

#### 2.4 Chapter Summary

This chapter presents the basic operating principle, control and PWM switching technique based on the basic two-level VSI, which can be applied to the multilevel converter. It gives a detailed explanation of the four quadrant operation for the VSI based on a simple equivalent circuit. There are two tasks for the control. One is to control the magnitude of the reactive input current

or its phase angle. The other is to maintain the dc voltage constant. The overall control scheme and the control principle are presented which will be the basis of the control for the multilevel converters discussed later. The carrier-based PWM and OPP techniques are discussed. The advantages and disadvantages of the two types of PWM are presented. The final decision is to focus on the carrier-based PWM.

#### **CHAPTER 3**

#### BASIC THEORY OF MULTILEVEL CONVERTER

Multilevel power converters have received tremendous attention in the past few years in the field of high-voltage and high-power applications such as railway traction, ship propulsion, renewable generation, FACTS and UPFC. To reach such power and such voltage levels (MW, kV), various techniques of association have been used in the past because of the technological limitation of the semiconductor voltage (6kV for the IGCTs at present).

Multilevel converters include an array of power semiconductors and capacitor voltage sources. The general structure of the multilevel converter is to synthesize sinusoidal voltage waveforms from several levels of voltages typically obtained from capacitor voltage sources. As the number of levels increase, the synthesized output waveform adds more steps, producing a staircase

waveform which approaches the sinusoidal wave with minimum harmonic distortion. However, increasing the level means introducing voltage imbalance problems on the capacitors at each level.

Three different topologies have been proposed for multilevel converters: the diode clamped, the cascaded multicell with separate dc sources, and the stacked multicell converter. The most attractive features of multilevel converters are as follows [8]:

- a. They can generate output voltages with extremely low distortion and low dv/dt.

- b. They draw input current with very low distortion.

- c. They generate smaller common-mode (CM) voltage, thus reducing the stress in the motor bearings. In addition, using sophisticated modulation methods, CM voltages can be eliminated.

- d. They can operate with a lower switching frequency.

#### 3.1 Description of Diode Clamped Converter

#### 3.1.1 Neutral Point Clamped Converter

The neutral point clamped (NPC) converter introduced by Nabae [9], is a three-level diode clamped multilevel converter, as shown in Figure 3.1. The three-level converter introduced a new zero voltage level (also called neutral point), other than the negative and positive voltage levels, in comparison to two-level converter. The most simple and well employed method of producing the neutral point is to split the DC link capacitor into two, creating a third level with a zero potential.

Figure 3.1 Three-level NPC Converter circuit

As shown in Figure 3.1, each arm of the three-level converter consists of four switching elements. By turning on upper, lower or middle two switching elements, the output can be clamped to the positive level, negative level or zero potential (neutral point) respectively, as shown in Figure 3.2.

Figure 3.2 A Typical Voltage Waveform for the NPC

Compared with the output voltage waveform of the basic two-level VSI shown in Figure 2.7, it can be seen that for the same device ratings and switching frequency, the power load of the NPC converter has doubled, while each switching involves only half the dc bus voltage and thus power devices could be fully utilized in the high-voltage range. The three-level converter output voltage reduces the harmonic voltages and shows relatively lower harmonic contents in the line currents which result in smaller filter size. Thus, the three-level converter topology is widely

used in heavy power industrial applications due to its high voltage handling and good harmonic rejection capabilities with the currently available power electronics devices.

In summary, the NPC converter has shown a clear market in industrial applications because it offers significant advantages like [10]:

- Small number of additional components to increase the number of levels from 2 to 3(only 2 additional NPC diodes per phase leg)

- Two simple clamp circuits serving the whole 3 phase converter

- Low output voltage harmonics/reduced filter cost and losses because of the three level characteristics

- Simple mechanical design (which is crucial in converters with more than 3 levels)

- Well established direct torque control can be used

- Simple direct series connection of IGCTs to increase the output voltage

#### 3.1.2 Multilevel Diode Clamped Converter (DCC)

As an extension of the three-level NPC, a simplified schematic of one phase of a 7-level DCC is presented in Figure 3.3. Two additional phases would be required for the three-phase converter. As may be seen from Figure 3.3, the general N level converter comprises 2(N-1) switches  $(S_1 - S_6, S_1' - S_6')$  per phase with 2(N-2) diode clamps  $(D_1 - D_5, D_1' - D_5')$  connected to each level of the dc voltage and (N-1) dc capacitors which are common to all the three phases. The voltage across these capacitors is then equal to  $V_{ci_i} = 2E/(N-1)$  in which E is half of the total voltage at the dc link of the DCC.

In this DCC structure, each IGCT thyristor is only required to block the voltage of 2E/(N-1) and is well protected against over-voltage by the clamping action of the dc capacitors. The lower group of IGCT thyristors requires the complementary gating pulses of the upper group of the

same number. That means if  $S_1$  is on, then  $S_1$  must be off. It should be noted here that, for each voltage step, only one thyristor must turn on and one thyristor turn off. For example, if  $S_1$  is off, then  $S_2$ ,  $S_3$  ...  $S_{N-1}$  and  $S_1$  are on, and the terminal voltage +(N-3)E/(N-1) is connected to the output terminal through  $D_1$ ,  $S_2$ ,  $S_3$  ...  $S_{N-1}$  for positive current, or through  $S_1$  and  $S_1$  for negative currents. In other words, in every operating state, N-1 switches are in on state and the other N-1 are in off state. Different switching states provide different output voltages. The corresponding switching logic for the 7-level diode clamped converter is shown in Table 3.1.

Design and An Analysis of The SMC with Comparison to The NPC

Figure 3.4 shows the staircase output voltage waveform of the seven-level CDD. It should be mentioned that the clamping diodes are required to block different voltages. It is easy to see that  $D_2$  must block  $2 \cdot 2E/(N-1)$  and in general the  $D_i$  must block the voltage of  $i \cdot 2E/(N-1)$ .

|                | Thyristor State |                |                |                |                |                  |                  |                  | Output voltage   |                  |                  |                |

|----------------|-----------------|----------------|----------------|----------------|----------------|------------------|------------------|------------------|------------------|------------------|------------------|----------------|

| S <sub>1</sub> | S <sub>2</sub>  | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | S <sub>1</sub> ' | S <sub>2</sub> ' | S <sub>3</sub> ' | S <sub>4</sub> ' | S <sub>5</sub> ' | S <sub>6</sub> ' | Output voltage |

| 1_1_           | 1               | 1              | 1              | 1              | 1              | 0                | 0                | 0                | 0                | 0                | 0                | E              |

| 0_             | 1               | 1              | 1              | 1              | 1              | 1                | 0                | 0                | 0                | 0                | 0                | 2E/3           |

| _0             | 0               | 1              | 1              | 1              | 1              | 1                | 1                | 0                | 0                | 0                | 0                | E/3            |

| 0              | 0               | 0              | 1              | 11             | 1              | 1                | 1                | 1                | 0                | 0                | 0                | 0              |

| 0              | 0               | 0              | 0              | 1              | 1              | 1                | 1                | 1                | 1                | 0                | 0                | -E/3           |

| 0              | 0               | 0              | 0              | 0              | 1              | 1                | 1                | 1                | 1                | 1                | 0                | -2E/3          |

| 0              | 0               | 0              | 0              | 0              | 0              | 1                | 1                | 1                | 1                | 1                | 1                | -E             |

Table 3.1 The Switching Logic for 7-level NPC

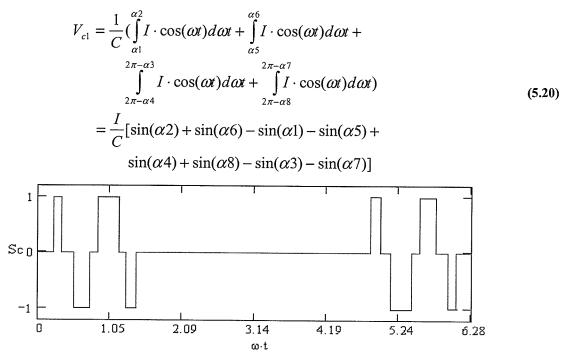

There is no doubt that more levels of the output voltage will produce less distortion and better output quality. But balancing the capacitor voltage at each level becomes a problem due to the fact that when establishing sinusoidal output waveform, charge of inner capacitors is much greater than that of outer capacitors [11]. The seven-level DCC is used as an example to explain this.

Assuming the output current  $I_{OA}$  is a purely sinusoidal waveform with a power factor,  $pf = \cos \beta$ , it can be expresses as:

$$I_O = \sqrt{2}I\sin(\theta - \beta)$$

Thus, the average value  $il_{avg}$ , of input node current il, is given by:

$$i1_{avg} = \frac{1}{2\pi} \int_{\alpha_3}^{\pi - \alpha_3} I_o d\theta$$

$$= \frac{\sqrt{2}I}{\pi} \cos \beta \cos \alpha_3$$

Similarly, the average value  $i2_{avg}$  of i2, and i3,  $i3_{avg}$  are given by:

$$i2_{avg} = \frac{1}{2\pi} \int_{\alpha^2}^{\alpha^3} I_o d\theta$$

$$= \frac{\sqrt{2}I}{\pi} \cos \beta (\cos \alpha 2 - \cos \alpha 3)$$

$$i3_{avg} = \frac{1}{2\pi} \int_{\alpha 1}^{\alpha 1} I_o d\theta$$

$$= \frac{\sqrt{2}I}{\pi} \cos \beta (\cos \alpha 1 - \cos \alpha 2)$$

By symmetry,

$$i4_{avg} = 0$$

,  $i5_{avg} = -i3_{avg}$ ,  $i6_{avg} = -i2_{avg}$ ,  $i7_{avg} = -i1_{avg}$ .

Therefore, the average currents per cycle which should be supplied from each capacitor are as follows:

$$I_{clavg} = il_{avg}$$

which gives  $I_{clavg} = \frac{\sqrt{2}I}{\pi} \cos \beta \cos \alpha 3$

$$I_{c2avg} = i1_{avg} + i2_{avg}$$

which gives  $I_{c2avg} = \frac{\sqrt{2}I}{\pi} \cos \beta \cos \alpha 2$

$$I_{c3avg} = i1_{avg} + i2_{avg} + i3_{avg} \text{ which gives } I_{c3avg} = \frac{\sqrt{2}I}{\pi} \cos\beta\cos\alpha 1$$

Obviously,  $I_{clavg} < I_{c2avg} < I_{c3avg}$  for  $\alpha 1 < \alpha 2 < \alpha 3$ . These result in unbalanced charging and hence, unbalanced voltage in the capacitors. The charge of the capacitor  $C_3(C_4)$  is largest among the three capacitor groups. The second largest charge is from the capacitor  $C_2(C_5)$ . The charge of the capacitor  $C_1(C_6)$  is the smallest. Also from above equation, it can be seen that the capacitor charge unbalance is independent of the control strategy. When any multilevel PWM is employed, the capacitor charge unbalance is always a problem. It should be noted that if  $\cos \beta = 0$ , it can operate as STATCOM, but it is a limiting case of operation.

Space Vector Modulation (SVM) and adding a DC offset are two possible solutions to correct the unbalance. But both of them have drawbacks. Employing some additional regulation circuitry can solve the problem [12], but has not met with industrial acceptance.

#### 3.1.3 Switching Technique for the DCC Converter

For multilevel DCC converter, the carrier-based PWM techniques can be extended from the corresponding two-level carrier-based PWM methods. Usually, for an N-level converter in SHPWM or SFOPWM, there are (n-1) carriers with the same frequency  $f_c$  and peak to peak amplitude  $A_c$  for each phase. By comparing the amplitude of these (n-1) carriers with that of a sinusoidal modulation wave with a certain frequency  $f_m$  and amplitude  $A_m$ , the corresponding switching devices are switched. The intersections of these carriers with the reference modulation waveform produce the gate signals for the thyristors. In order that the bands they occupy are contiguous, the (n-1) carriers are disposed and the whole carrier wave set is distributed symmetrically on both sides of the zero reference. Figure 3.5 gives an example of the carriers and reference waveform for seven-level DCC.

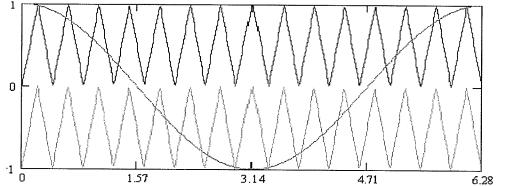

For the three-level NPC converter, two triangular carriers are compared with the sinusoid reference modulation waveform to get the required switching control signal as shown in Figure 3.6a. The carriers and reference modulation waveform for SFOPWM method are shown in Figure 3.7a. It is easily seen that these two triangular carriers are mirror symmetrical around the zero reference. The intersections of the positive carrier with the positive modulation waveform produce the gate signals for  $S_1$ . The intersections of the negative carrier with the negative modulation waveform produce the gate signals for  $S_2$ . The complementary thyristor received the negative of these signals. That is  $S_1'$  and  $S_2'$  received the negative gate signal  $S_1$  and  $S_2$  separately. The gate switching logic to achieve the three voltage levels at the output terminal of the three-level NPC is shown in Table 3.2.

Table 3.2 The Switching Logic for Three-level NPC

|                | State of IGC     | 0.41           |                  |                |

|----------------|------------------|----------------|------------------|----------------|

| S <sub>1</sub> | S <sub>1</sub> ' | S <sub>2</sub> | S <sub>2</sub> ' | Output voltage |

| 1              | 0                | 1              | 0                | E              |

| 0              | 1                | 1              | 0                | 0              |

| 0              | 1                | 0              | 1                | - <b>E</b>     |

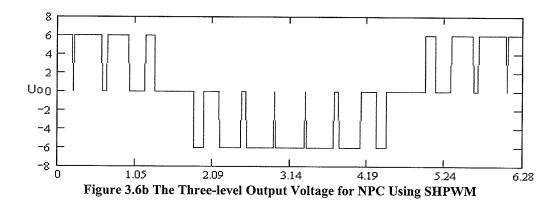

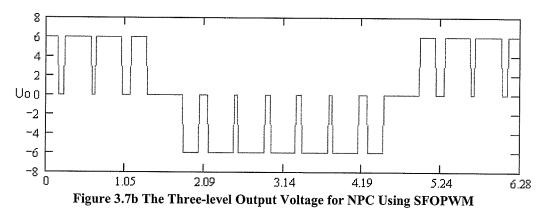

The frequency of the carriers and the magnitude of the modulation waveform will be changed with the changing of the frequency ratio k and the modulation index M. In other words, the magnitude of the fundamental component and harmonic content in the output voltage of the converter as well as the switching losses can be controlled by simply changing k and M. The output for NPC is analyzed further using Mathcad Program. Typical calculation results are shown in Table 3.3 which gives the number of GTO thyristors switched per fundamental cycle (S.No) when the frequency ratio k and the modulation index M are changed, and THD were compared for each case. Figure 3.6b and 3.7b show an example for the corresponding output voltage using the above switching logic for, where  $f_m = 60 \text{ Hz}$ , k=15 and M=1.

**Table 3.3 Typical Calculation Results for the NPC Converter**

| frequency ratio | Modulation index   | SHI   | PWM   | SFOPWM                     |       |

|-----------------|--------------------|-------|-------|----------------------------|-------|

| nequency ratio  | iviodulation index | S.No. | THD   | S.No.                      | THD   |

|                 | M=0.6              | 4X2   | 0.297 | 4X2                        | 0.304 |

|                 | M=0.7              | 4X2   | 0.321 | 4X2                        | 0.321 |

| k=3             | M=0.8              | 4X2   | 0.32  | 4X2                        | 0.313 |

|                 | M=0.9              | 4X2   | 0.313 | 4X2                        | 0.301 |

|                 | M=1                | 4X2   | 0.307 | S.No.<br>4X2<br>4X2<br>4X2 | 0.294 |

|                 | M=0.6              | 20x2  | 0.489 | 20x2                       | 0.501 |

|                 | M=0.7              | 20x2  | 0.446 | 20x2                       | 0.437 |

| k=9             | M=0.8              | 20x2  | 0.4   | 20x2                       | 0.405 |

|                 | M=0.9              | 20x2  | 0.341 | 20x2                       | 0.381 |

|                 | M=1                | 20x2  | 0.331 | 20x2                       | 0.358 |

|                 | M=0.6              | 28x2  | 0.401 | 28x2                       | 0.381 |

|                 | M=0.7              | 28x2  | 0.375 | 28x2                       | 0.357 |

| k=15            | M=0.8              | 28x2  | 0.353 | 28x2                       | 0.35  |

|                 | M=0.9              | 28x2  | 0.335 | 28x2                       | 0.345 |

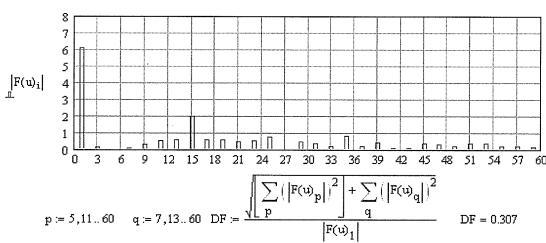

|                 | M=1                | 28x2  | 0.307 | 28x2                       | 0.303 |

Note: x2 in the table means that there are two switching devices in series which switched on and off at the same time.

It is easily seen from Table 3.3 that for three-level NPC, the frequency ratio k=15 or 3 and modulation index M=1 in SHPWM method gives better results among the other combination from the aspect of total harmonic distortion and high fundamental component. For SFOPWM

method, the frequency ratio k=15 or 3 and modulation index M=1 always gives better results among the other combinations. Comparing the results from SHPWM and SFOPWM, there is nearly no difference no matter what the frequency ratio and modulation index is.

Figure 3.6a The Triangular Carriers and Modulation Wave for Three-level NPC Using SHPWM

1 0 1.05 2.09 3.14 4.19 5.24 6.28

Figure 3.7a The Triangular Carriers and Modulation Wave for Three-level NPC Using SFOPWM

#### 3.2 Description of Stacked Multicell Converter

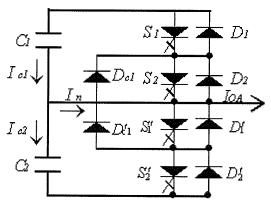

#### 3.2.1 Five-level 2x2 SMC Converter

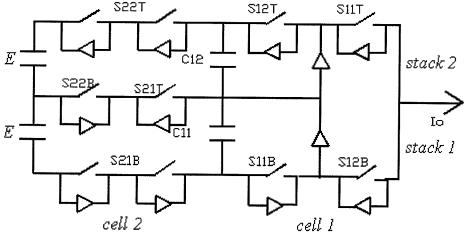

The SMC topology is a very new structure of multilevel converter able to increase the voltage levels, while decreasing the stored energy in the converter. Basically, the SMC is a hybrid association of commutation cells making it possible to share the voltage constraint on several switches, and also improve the output waveforms of the converter in terms of number of levels and switching frequency. The original idea comes from Escaut [13]. The concept of Stacked Multicell Converter topology was first introduced by Meynard with a five-level 2x2 SMC [14] which is shown Figure 3.8.

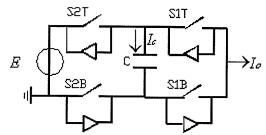

Figure 3.8 Topology of a 2x2 Stacked Multicell Converter

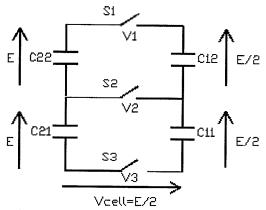

As shown in Figure 3.8, one single cell in one stack of the structure consists of two switches SijT and SijB which have complementary states. The subscript  $i \in [1 \cdots n]$  is the number of cells and  $j \in [1 \cdots p]$  is the number of stacks. In the steady balanced state, the voltage across the floating capacitors C12 and C11 is one quarter of the dc link voltage 2E [15]. The observation of the above figure shows us that the switches S22T and S21B consist of two devices receiving the same firing signals. To explain this difference, Figure 3.9 shows the voltage across switches for SMC converter.

Figure 3.9 Voltage Constraints on Switches

We can see that if the switch S2 is on and S3 is off, and the voltage constraint of the switch S1 is E/2. But if S3 is on and S2 is off, the constraint of S1 is E. This is also true for switch S3 when S1 is on and S2 is off. In conclusion, the voltage constraint V1 (V3) on switch S1 (S3) and V3 depend on the state of other switches S2 and S3 (S1). Therefore S1 and S3 need an additional switch respectively in series to distribute the voltage constraint. But the direct series association of the two switches in the upper and lower branches is not a problem in our case. In fact they switch together only at E/2, and the E is only a static rating. For example, during a half period of modulation, the switches in the upper branch are continuously blocking and the voltage varies between E/2 and E as a consequence of the switching of the bottom cell. Thus the additional series switch could be an ordinary thyristor.

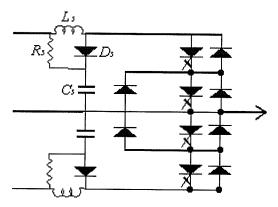

It is now for us to describe the realization of the final cell named cell 1 which is nearest to the AC system. There are two solutions available for the realization of this cell. The first consists in simply replacing the capacitors connected to the AC system by short-circuit. For the second solution, it is possible to replace the final cell by a NPC topology. With the second solution, the number of the controlled power switches is reduced because two IGCT are replaced by the two diodes of the clamp.

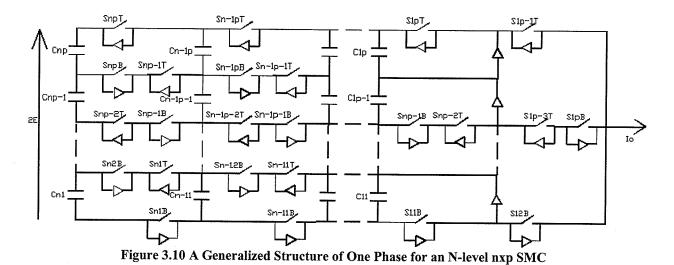

#### 3.2.2 Multilevel SMC Converter

As an extension, a generalized structure of one phase for an N-level SMC is shown in Figure 3.10. Another two phases would be required for the three-phase converter, with the dc capacitors common to all the three phases. For the  $n \times p$  SMC converter, there are  $n \times (p-1)$  floating capacitors  $C_{ij}$  with  $i \in [1...n]$  and  $j \in [1...p-1]$  in which p is the stack number and n is the cell number. Each voltage across these capacitors is then equal to  $V_{Cij} = \frac{i \times 2E}{n \times p}$  in which E is half of the dc link voltage of the SMC. The number of levels for the output voltage equal to:

$$N_{level} = (n \times p) + 1$$

Design and An Analysis of The SMC with Comparison to The NPC

The same voltage constraint applies to all the semiconductors in the structure and is equal to:

$$V_{switches} = \frac{2E}{n \times p}$$

The lower group of IGCT thyristors requires the complementary gating pulses of the upper group of the same number. That means if SijT is on, then SijB must be off. It should be noted here that, for each voltage step, only one thyristor must turn on and one thyristor turn off. For example, if  $S_{1p}T$  is off, then  $S_{2p}T$ ,...  $S_{np}T$ ,  $S_{n1}T$ , ...  $S_{np-1}T$  and  $S_{1p}B$  are on, and the terminal voltage  $+E(n\times p-2)/(n\times p)$  is connected to the output terminal through  $S_{2p}T$ ,...  $S_{np}T$ ,  $S_{n1}T$ , ...  $S_{np-1}T$  for positive current, or through  $S_{1p}B$  and the reverse diode of other IGCT thyristors for negative currents. In order to carry on the various output voltage levels, the corresponding switching logic is shown in Table 3.4.

Table 3.4 The Switching Logic for N-level SMC

| Thyristor State   |           |             |                   |                   |                     |                     |  |                   | <u> </u>          |                 |

|-------------------|-----------|-------------|-------------------|-------------------|---------------------|---------------------|--|-------------------|-------------------|-----------------|

| S <sub>np</sub> T | $S_{np}B$ |             | S <sub>1p</sub> T | S <sub>1p</sub> B | S <sub>np-1</sub> T | S <sub>np-1</sub> B |  | S <sub>n1</sub> T | S <sub>n1</sub> B | Output voltage  |

| 1                 | 0         |             | 1                 | 0                 | 1                   | 0                   |  | 1                 | 0                 | E               |

| 1                 | 0         |             | 0                 | 1                 | 1                   | 0                   |  | 1                 | 0                 | (nxp-2)E/(nxp)  |

|                   |           |             |                   |                   | •                   | •                   |  |                   | •                 |                 |

| <u> </u>          |           | • • • • • • |                   | •                 | •                   | •                   |  |                   |                   |                 |

|                   |           |             |                   |                   | •                   | •                   |  | •                 |                   | •               |

| 1                 | 0         |             | 0                 | 1                 | 0                   | 1                   |  | 1                 | 0                 | 2E/(nxp)        |

| 0                 | 1         |             | 1                 | 0                 | 1                   | 0                   |  | 1                 | 0                 | 0               |

| 0                 | 1         | •••••       | 1                 | 0                 | 1                   | 0                   |  | 0                 | 1                 | -2E/(nxp)       |

| <u> </u>          | •         |             |                   |                   |                     | •                   |  |                   | •                 | •               |

|                   |           |             |                   | •                 | •                   | •                   |  | •                 |                   | •               |

|                   | •         |             | •                 | •                 | •                   |                     |  | •                 |                   | •               |

| 0                 | 1         | •••••       | 1                 | 0                 | 0                   | 1                   |  | 0                 | 1                 | -(nxp-2)E/(nxp) |

| 0                 | 1         |             | 0                 | 1                 | 0                   | 1                   |  | 0                 | 1                 | -E              |

It should be noted that n configurations could be used to produce the same level of output voltage. For example, for the level (nxp-2)E/(nxp), the switches  $S_{1P}T - S_{np}T$  are switched on and off in turn with one off each time, thus there are n switching states to produce the same voltage

level. It should be mentioned that the floating capacitors are discharged or charged in the different switching states. As an example, for the output level E/2 in the 2x2 SMC shown in Figure 2.8, there are two optional switching states. When  $S_{22}T$  is off, the positive output current flows through C12,  $S_{12}T$  and  $S_{11}T$  discharging capacitor C12. When  $S_{12}T$  is off, the positive current flows through  $S_{22}T$ , C12 and  $S_{11}T$  charging capacitor C12. To keep the voltage across the floating capacitors constant, a suitable control strategy should be developed to ensure the discharge and charge are the same. The detail control strategy will be developed in a later chapter.

# 3.2.3 Switching Technique for the SMC converter

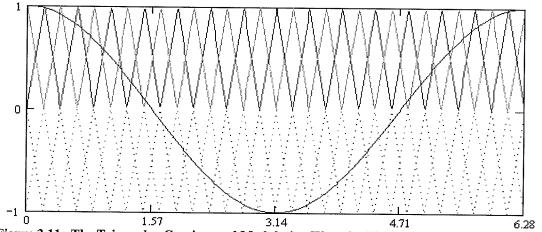

We will limit the discussion of the multilevel SMC to two stacks and n cells. For N-level SMC converter with n cells using carrier-based PWM, there are (N-1) carriers with the same frequency  $f_c$  and peak to peak amplitude  $A_c$  for each phase. (N-1)/2 oscillate between -1 and 0 with a phase shift of  $360^\circ/n$  for cell 1 to cell n at stack 1, and (N-1)/2 between 0 and 1 with a phase shift of  $360^\circ/n$  for cell 1 and cell n at stack 2.

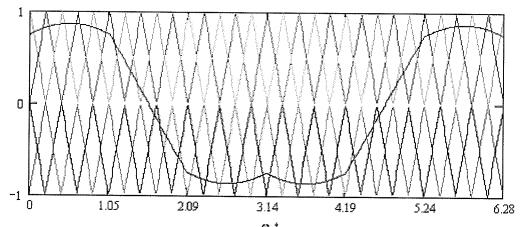

For the five-level SMC converter, four triangular carriers are used. As shown in figure 3.11a and 3.12a, two oscillate between -1 and 0 with a phase shift of 180° for cell 1 and cell 2 at stack 1, and two between 0 and 1 with a phase shift of 180° for cell 1 and cell 2 at stack 2. The intersections of the positive two triangular carriers with the positive modulation waveform produce the gate signals for S22T and S12T separately. Similarly, the intersections of the negative two triangular carriers with the negative modulation waveform produce the gate signals for S21B and S11B. The complementary thyristor received the negative of these signals. The

gate switching logic to achieve the five voltage levels at the output terminal of the five-level SMC is shown in table 3.5.

|      |                          |      |      | •    | _    |      | _    | · <del>-</del> |  |

|------|--------------------------|------|------|------|------|------|------|----------------|--|

|      | State of IGCT thyristors |      |      |      |      |      |      |                |  |

| S11T | S11B                     | S12T | S12B | S22T | S22B | S21T | S21B | Output voltage |  |

| 1    | 0                        | 1    | 0    | 1    | 0    | 1    | 0    | Е              |  |

| 1    | 0                        | 0    | 1    | 1    | 0    | 1    | 0    | E/2(mode 1)    |  |

| 1    | 0                        | 1    | 0    | 0    | 1    | 1    | 0    | E/2(mode 2)    |  |

| 1    | 0                        | 0    | 1    | 0    | 1    | 1    | 0    | 0              |  |

| 11   | 0                        | 0    | 1    | 0    | 1    | 0    | 1    | -E/2(mode 2)   |  |

| 0    | 1                        | 0    | 1    | 0    | 1    | 1    | 0    | -E/2(mode 1)   |  |

| 0    | 1                        | 0    | 1    | 0    | 1    | 0    | 1    | -F             |  |

Table 3.5 The Switching Logic for Five-level 2x2 SMC

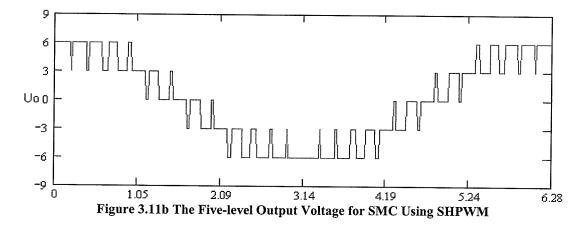

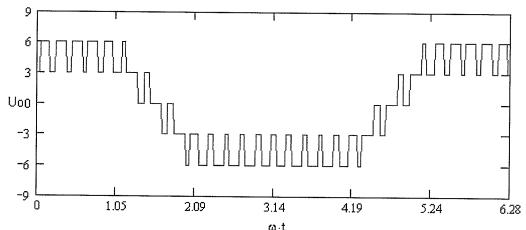

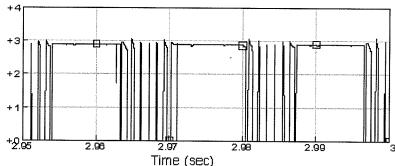

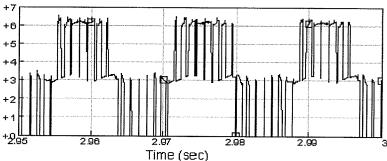

Figure 3.11b and 3.12b show an example for the corresponding output voltage using the switching logic in Table 3.5 using SHPWM and SFOPWM respectively, where  $f_m$ =60 Hz, k=15 and M=1.

Figure 3.11a The Triangular Carriers and Modulation Wave for Five-level SMC Using SHPWM

Design and An Analysis of The SMC with Comparison to The NPC

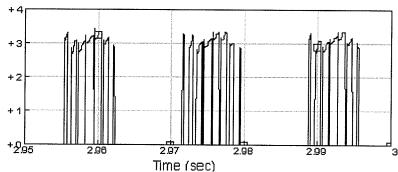

Figure 3.12a The Triangular Carriers and Modulation Wave for Five-level SMC Using SFOPWM

Figure 3.12b The Five-level Output Voltage for SMC Using SFOPWM

As discussed for the NPC converter, we also analyze the five-level SMC using MATHCAD. Typical calculation results are shown in Table 3.6 which also gives the number of GTO thyristors switched per fundamental cycle (S.No) when the frequency ratio k and the modulation index M are changed, and THD were compared for each case.

It can be seen from Table 3.6 that for five-level SMC, the worst condition occurs around M=0.8 for the three different frequency ratios and decreasing or increasing M gives better results for both SHPWM and SFOPWM. The case of k=3, M=1 gives the best result. There is not much difference in total harmonic distortion for M=1 for any of the frequency ratios with SFOPWM technique.

Table 3.6 Typical Calculation Results for the SMC Converter

| frequency ratio | Modulation index | SHF   | WM    | SFO   | PWM   |

|-----------------|------------------|-------|-------|-------|-------|

| noquency ratio  | Woddiation index | S.No. | THD   | S.No. | THD   |

|                 | M=0.6            | 6X2   | 0.201 | 6X2   | 0.196 |

|                 | M=0.7            | 6X2   | 0.29  | 6X2   | 0.31  |

| k=3             | M=0.8            | 6X2   | 0.242 | 6X2   | 0.319 |

|                 | M=0.9            | 6X2   | 0.222 | 6X2   | 0.292 |

|                 | M=1              | 4X2   | 0.16  | 6X2   | 0.259 |

|                 | M=0.6            | 18X2  | 0.213 | 18X2  | 0.25  |

|                 | M=0.7            | 18X2  | 0.253 | 18X2  | 0.335 |

| k=9             | M=0.8            | 18X2  | 0.273 | 18X2  | 0.354 |

|                 | M=0.9            | 18X2  | 0.269 | 18X2  | 0.322 |

|                 | M=1              | 16X2  | 0.253 | 18X2  | 0.274 |

|                 | M=0.6            | 30X2  | 0.139 | 24X2  | 0.196 |

|                 | M=0.7            | 30X2  | 0.216 | 30X2  | 0.274 |

| k=15            | M=0.8            | 30X2  | 0.259 | 30X2  | 0.318 |

|                 | M=0.9            |       | 0.251 | 30X2  | 0.312 |

|                 | M=1              | 28X2  | 0.217 | 30X2  | 0.273 |

Note: x2 in the table means that there are two switching devices which are switched on and off alternatively.

## 3.3 Chapter Summary

A brief overview of the structure of the Neutral Point Clamped Converter and the Stacked Multicell converter has been presented in this chapter. The advantages of using the SMC converter were discussed, and will be examined in detail in later chapter.

The Diode Clamped Converter is described. In summary, for an N-level DCC, it comprises 2(N-1) switches per phase with 2(N-2) diodes and (N-1) DC capacitors. Voltage across these capacitors and the constraint of the IGCT thyristor is equal to  $V_{c_i} = 2E/(N-1)$  in which E is the half of total dc link voltage. The clamping diodes are required to block different voltages but this can be solved by series connection to get equal constraint on these clamped diodes. The voltage unbalance on the dc capacitors for multilevel DCC is a problem. Although some methods were developed to solve this, it was not acceptable in industry. The switching technique is presented in detail based on the three-level NPC.