# THE APPLICATION OF TRANSPUTER ARRAYS TO NUMERICAL ANALYSIS AND COMPUTER-AIDED ENGINEERING

by

### ROBERT ARTHUR MAXWELL ALLEN

A thesis

presented to the University of Manitoba

in partial fulfillment of the

requirements for the degree of

DOCTOR OF PHILOSOPHY

Winnipeg, Manitoba, Canada March 1988

© Robert Arthur Maxwell Allen, 1988

Permission has been granted to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film.

The author (copyright owner) has reserved other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without his/her written permission.

L'autorisation a été accordée à la Bibliothèque nationale du Canada de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur (titulaire du droit d'auteur) se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation écrite.

ISBN 0-315-44199-2

# THE APPLICATION OF TRANSPUTER ARRAYS TO NUMERICAL ANALYSIS AND COMPUTER-AIDED ENGINEERING

BY

#### ROBERT ARTHUR MAXWELL ALLEN

A thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements of the degree of

## DOCTOR OF PHILOSOPHY © 1988

Permission has been granted to the LIBRARY OF THE UNIVER-SITY OF MANITOBA to lend or sell copies of this thesis, to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

To my parents

I hereby declare that I am the sole author of this thesis. I authorize the University of Manitoba to lend this thesis to other institutions or individuals for the purpose of scholarly research. I further authorize anyone to reproduce this thesis by photocopying or by other means, in total or in part, for the purpose of scholarly research.

Robert A.M. Allen

#### ABSTRACT

The objective of this dissertation is to explore ways of achieving high performance for numerical analysis and Computer-Aided Engineering (CAE) algorithms with minimal cost. The transputer microprocessor and its accompanying language (Occam), which provide a readily accessible means to perform Multiple Instruction/Multiple Data parallel processing, were found to ideally satisfy these goals.

The main category of algorithms studied deals with matrix and vector operations since these are so pervasive in the targeted fields. Monadic and dyadic vector operations are shown to be efficient on linear transputer arrays, while scalar product and dense matrix-vector multiplication algorithms are more suited to the shuffle-exchange network. A novel sparse matrix-vector multiplication algorithm is demonstrated for banded matrices.

Matrix solution methods studied include Gaussian elimination and the Polynomial Preconditioned Conjugate Gradient (PPCG) techniques. The Gaussian elimination algorithm is shown to achieve nearly the maximum theoretical efficiency on a linear array of transputers by virtue of communication and computation overlap. A novel implementation of the PPCG algorithm is described, and applied to the finite-difference technique.

As an example of the implementation of a complex CAE algorithm, the MAN-itoba Integrated Transputer/Occam Boundary element Accelerator (MANITOBA) is described. MANITOBA consists of a novel algorithm that tightly couples a parallelized version of the boundary element method (BEM) with a Gaussian elimination matrix solver on a linear transputer array. Fundamental theory of the BEM is presented, along with architectural and algorithmic details of the implementation. The performance of MANITOBA is compared to a similar serial algorithm running on a workstation.

#### ACKNOWLEDGEMENT

I would like to express my sincere appreciation to my advisor and friend Dr. A. Wexler. The trust he has placed in me throughout this research was most encouraging. I am also deeply indebted to my friends and colleges. In particular, Mr. N. Aitken, Mr. A. Ang, and Dr. J. Poltz are thanked for their advice on the theory and implementation of the boundary element algorithm. I would like to acknowledge the financial support of the Natural Sciences and Engineering Research Council of Canada, the Province of Manitoba, and the University of Manitoba. In addition, the financial and moral support of my wife and best friend Val was indispensable. Finally, I would like to thank my parents, whose faith and inspiration have given me the strength to persevere.

### TABLE OF CONTENTS

| ACKNOWLED CONTENT                                   |

|-----------------------------------------------------|

| ACKNOWLEDGEMENT vi                                  |

| TABLE OF CONTENTS                                   |

| LIST OF FIGURES                                     |

| LIST OF TABLES                                      |

| LIST OF PRINCIPAL SYMBOLS                           |

| CHAPTER I INTRODUCTION                              |

| CHAPTER II OCCAM AND THE TRANSPUTER                 |

| 2.1 Occam8                                          |

| 2.1.1 Occam Processes9                              |

| 2.1.2 SEQ Constructor                               |

| 2.1.3 PAR Constructor                               |

| 2.1.4 ALT Constructor                               |

| 2.1.5 Characteristics of Occam Channels             |

| 2.1.6 Occam Time                                    |

| 2.2 The Transputer                                  |

| 2.2.1 Architecture                                  |

| 2.2.2 Support for Occam                             |

| 2.2.3 Constructing Large Transputer Networks        |

| 2.2.4 Hardware Considerations for Occam Programming |

| CHAPTER III MATRIX AND VECTOR OPERATIONS            |

| 3.1 Estimating Algorithm Execution Times            |

| 3.2 Vector Operations                               |

| 3.2.1 Vector Combination                            |

| 3.2.2 Scalar Product                                |

| 3.3 Matrix-Vector Multiplication39                  |

| 3.3.1 Dense Matrices                                |

| 3.3.2 Sparse Matrices                               |

| CHAPTER IV MATRIX SOLUTION ALGORITHMS               |

| 4.1 Gaussian Elimination                            |

| 4.1.1 The Algorithm 51                              |

| 4.1.2 Partitioning of Forward Elimination Phase     |

| 4.1.3 Partitioning of the Back-substitution Phase   |

| 4.2 The Conjugate Gradient Algorithm                |

| 4.2.1 The Classical Conjugate Gradient Algorithm      |

|-------------------------------------------------------|

| 4.2.2 The Preconditioned Conjugate Gradient Algorithm |

| 4.2.3 Polynomial Preconditioning                      |

| 4.2.4 Transputer Implementation                       |

| 4.2.5 Results                                         |

| CHAPTER V PARALLELIZATION OF THE BEM ALGORITHM80      |

| 5.1 MANITOBA: A Boundary Element Accelerator          |

| 5.2 The Boundary Element Method81                     |

| 5.2.1 BEM Theory                                      |

| 5.2.2 Surface and Charge Modelling                    |

| 5.2.3 Matrix Generation                               |

| 5.2.4 Parallel Matrix Generation                      |

| 5.3 Combining the Generator and Solver                |

| 5.4 Results                                           |

| CHAPTER VI CONCLUSION                                 |

| APPENDIX A An Occam-Transputer Programming Example    |

| A.1 The Transputer Development System                 |

| A.2 Specification in Occam                            |

| A.3 Mapping onto a Transputer Network (Configuration) |

| A.4 Observations                                      |

| REFERENCES                                            |

| 133                                                   |

### LIST OF FIGURES

| 2.1  | Example of a parallel system                                          |

|------|-----------------------------------------------------------------------|

| 2.2  | A sequential process servicing three inputs                           |

| 2.3  | The transputer architecture                                           |

| 2.4  | Transputer communication model                                        |

| 2.5  | Transputer communication link                                         |

| 3.1  | A linear array of processors.                                         |

| 3.2  | Partitioning of vectors for parallel computation                      |

| 3.3  | Time sequence of shuffle-exchange operations                          |

| 3.4  | The shuffle-exchange interconnection network.                         |

| 3.5  | Comparison of the scalar-product (distributed addition) algorithms 38 |

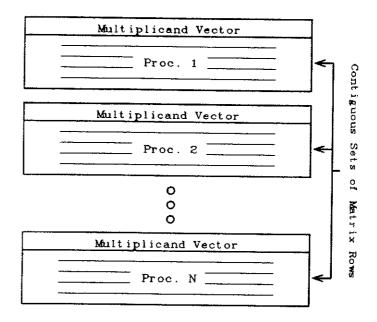

| 3.6  | Row-wise matrix and vector partitioning40                             |

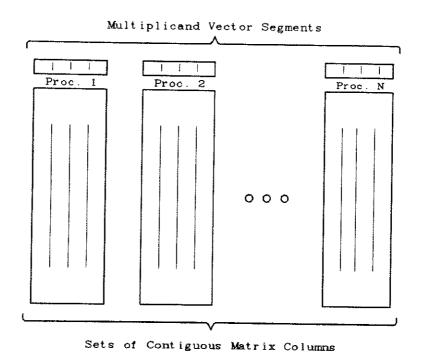

| 3.7  | Column-wise matrix and vector partitioning                            |

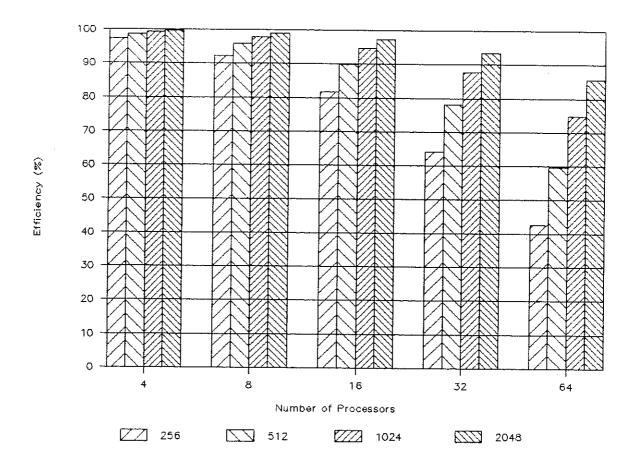

| 3.8  | SE efficiency for dense matrices (T-414).                             |

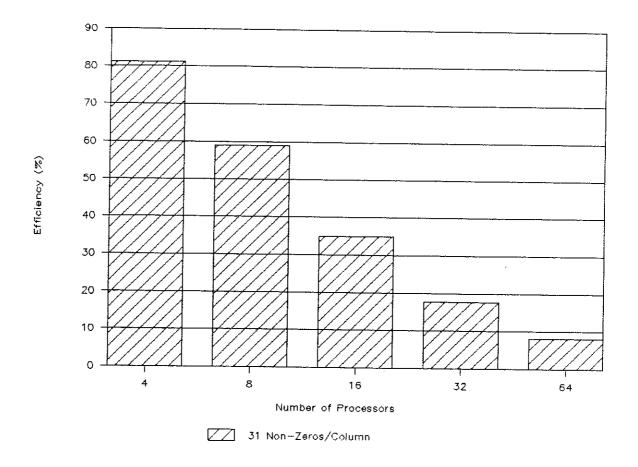

| 3.9  | SE efficiency for 1024 × 1024 sparse matrix                           |

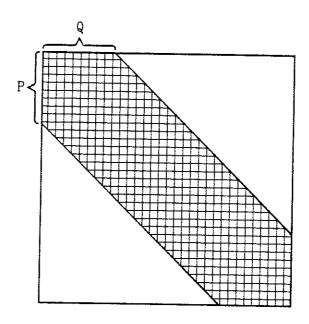

| 3.10 | A banded matrix                                                       |

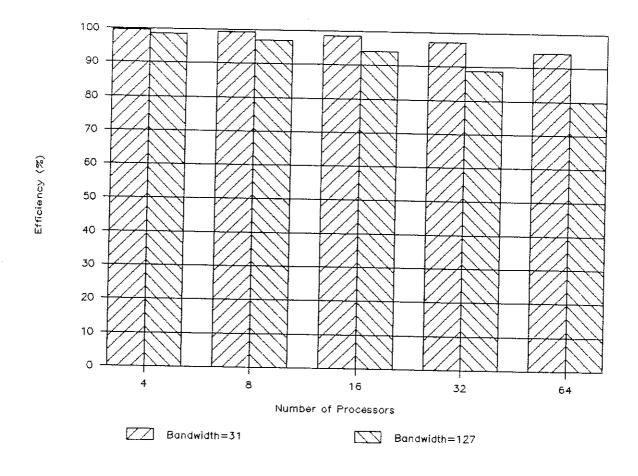

| 3.11 | Estimated efficiency for banded matrix-vector multiplication          |

| 4.1  | Example finite-difference problem                                     |

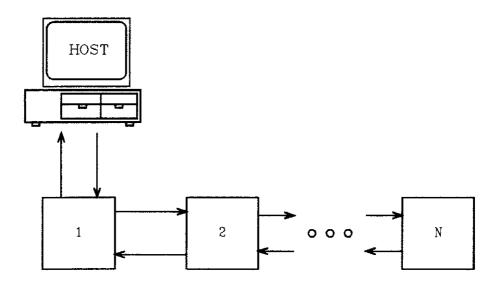

| 5.1  | MANITOBA architecture82                                               |

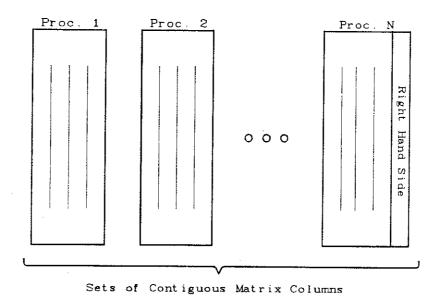

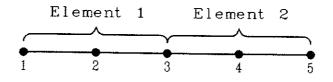

| 5.2  | Matrix partitioning on an array of processors                         |

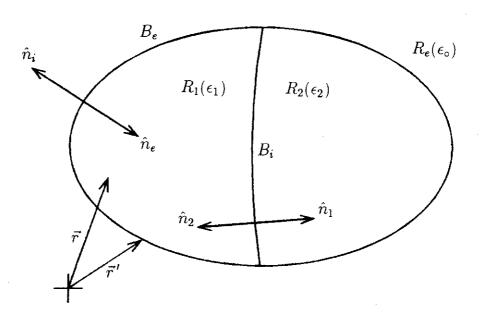

| 5.3  | Region, surface, and normal definitions for multi-media regions       |

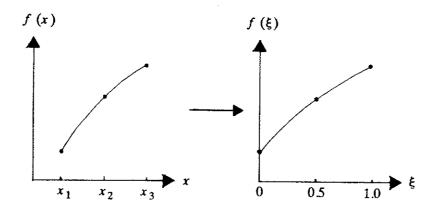

| 5.4  | Mapping of a boundary element from global to local space              |

| 5.5  | Boundary element discretization of a parallel plate capacitor96       |

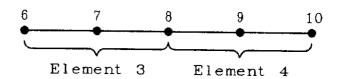

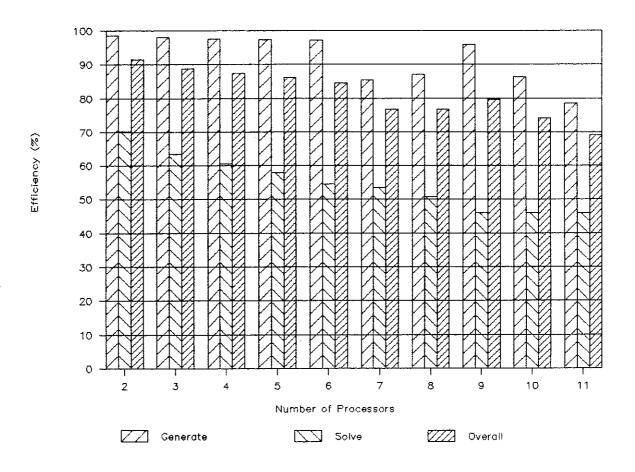

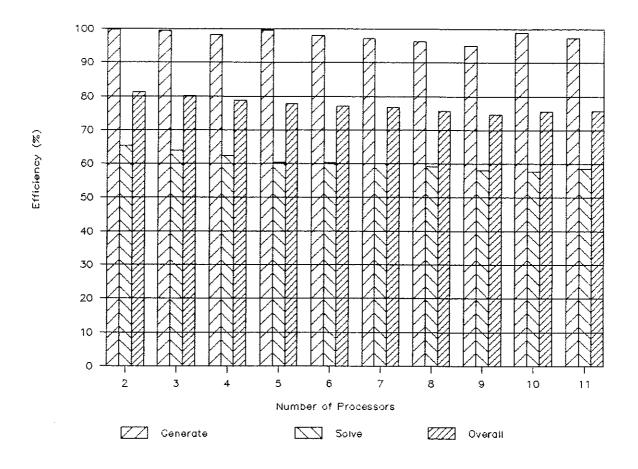

| 5.6  | $E_{N_p}$ for 36 element - 81 node problem                            |

| 5.7  | $E_{N_p}$ for 77 element - 175 node problem                           |

| 5.8  | $E_{N_p}$ for 130 element - 299 node problem                          |

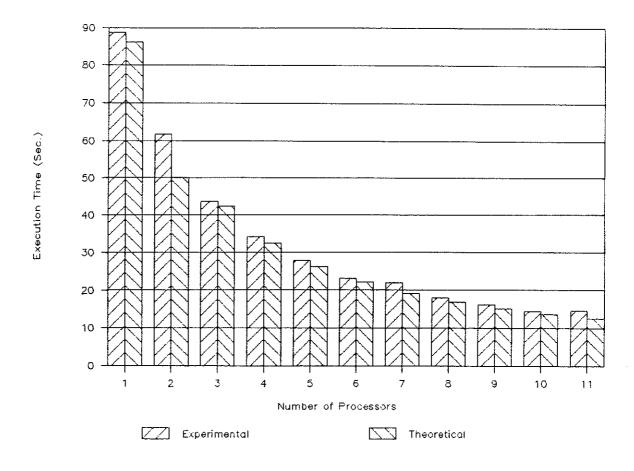

| 5.9  | Theoretical vs. measured elimination execution times                  |

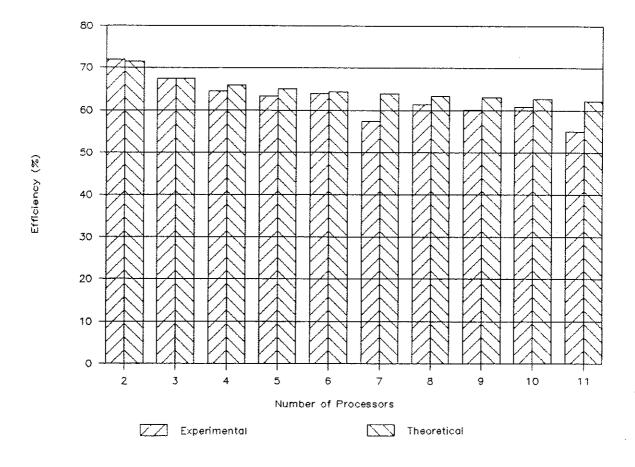

| 5.10 | Theoretical vs. measured elimination efficiencies.                    |

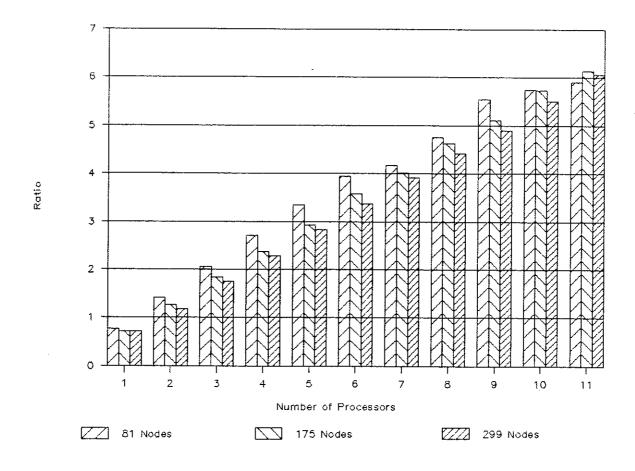

| 5.11 | Comparison of MANITOBA to 68020 based workstation.                    |

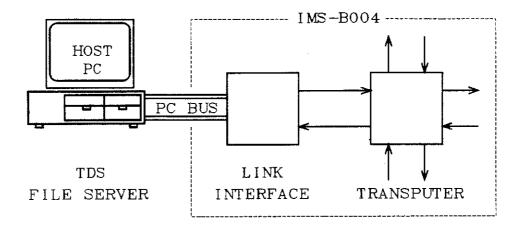

| A.1  | PU-based transputer development system                                |

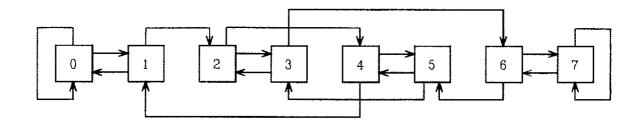

| A.2  | The SE interconnection network.                                       |

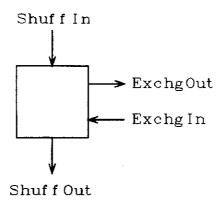

| A.3  | A single SE processor                                                 |

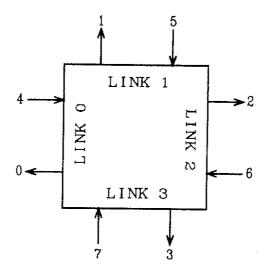

| 4.4  | Transputer link numbering                                             |

### LIST OF TABLES

| 3.1 | Timings for primitive operations on T-414 and T-800          |

|-----|--------------------------------------------------------------|

| 3.2 | Shuffle-exchange vector sum                                  |

| 4.1 | Estimated cost for an iteration of $PPCG(z)$ $(N_p \ge 2)$   |

| 4.2 | $T_{iter}$ estimates and results for PPCG(z) $(N_p = 8)$     |

| 4.3 | Estimated $T_{iter}$ for PPCG(2) for different $N_p$         |

| 5.1 | Example of node numbering required for parallel partitioning |

### LIST OF PRINCIPAL SYMBOLS

### Symbol

### Meaning

### Chapter III

| $T_s$ +                   | Time for scalar addition.               |

|---------------------------|-----------------------------------------|

| $T_s$ $^-$                | Time for scalar subtraction.            |

| ${T_s}^{	imes}$           | Time for scalar multiplication.         |

| $T_s$ ÷                   | Time for scalar division.               |

| $T_v{}^+$                 | Time for vector addition.               |

| $T_v$                     | Time for vector subtraction.            |

| ${T_v}^\times$            | Time for vector multiplication.         |

| $T_v$ $\stackrel{\div}{}$ | Time for vector division.               |

| $T_v{}^{sc}$              | Time to scale vector.                   |

| $T_v$ =                   | Time to assign vector.                  |

| $T_s X$                   | Time to transmit scalar.                |

| $T_v^X$                   | Time to transmit vector.                |

| $T_1$                     |                                         |

| $T_{N_p}$                 | Uniprocessor execution time.            |

| $E_{N_p}$                 | Multiprocessor execution time.          |

| •                         | Efficiency of multiprocessor algorithm. |

| $N_p$                     | Number of processors.                   |

| $P_i$                     | Processor number.                       |

| N                         | Problem size.                           |

| P                         | Matrix row bandwidth.                   |

| Q                         | Matrix column bandwidth.                |

| I                         | Nearest neighbour communication index.  |

|                           |                                         |

### Chapter IV

| $\underline{r}$                     | Residual vector.                 |

|-------------------------------------|----------------------------------|

| $\mathbf{A}, \mathbf{S}$            | System matrices.                 |

| $\underline{x}, \underline{\sigma}$ | Linear system unknown vectors.   |

| $\underline{b}$                     | Linear system source vector.     |

| $\underline{h}$                     | Exact solution of linear system. |

| $\underline{d}$                     | Direction vector.                |

| Symbol              | Meaning                                                                |

|---------------------|------------------------------------------------------------------------|

| $F(\underline{x})$  | Quadratic energy functional.                                           |

| $g(\underline{x})$  | Gradient of $F(\underline{x})$ .                                       |

| $E(\underline{x})$  | Error functional.                                                      |

| $\alpha$            | Optimum line search constant for $\underline{x}$ and $\underline{r}$ . |

| $oldsymbol{eta}$    | Optimum line search constant for $\underline{d}$ .                     |

| I                   | Identity matrix.                                                       |

| $\mathbf{M}$        | Part of system matrix splitting.                                       |

| $\mathbf{M}^{-1}$   | Splitting of A chosen to be $(DIAGONAL(A))^{-1}$ .                     |

| N                   | Part of system matrix splitting.                                       |

| K                   | Preconditioning matrix.                                                |

| $\mathbf{K}_z^{-1}$ | Approximate inverse of system matrix.                                  |

| L                   | Lower triangular factor of K.                                          |

| ρ                   | Spectral radius.                                                       |

| z                   | PPCG accuracy parameter.                                               |

|                     |                                                                        |

### Chapter V

| $B_e$                     | Exterior region boundary.                     |

|---------------------------|-----------------------------------------------|

| $B_i$                     | <b>▼</b>                                      |

| ,                         | Interface boundary.                           |

| $\phi$                    | Electric potential.                           |

| $\phi^{\prime}$           | Normal derivative of $\phi$ .                 |

| $\epsilon_{	exttt{o}}$    | Free-space permittivity.                      |

| $\epsilon$                | Permittivity.                                 |

| $ec{r}$                   | Field point.                                  |

| $ec{r}_{\circ}$           | Reference point.                              |

| $ec{r}''$                 | Source point.                                 |

| $\hat{m{n}}$              | Normal vector pointing outward from a region. |

| $G(ec{r} ec{r}^{\prime})$ | Green function.                               |

| $G'(ec{r} ec{r}')$        | Normal derivative of Green function.          |

| $\sigma(ec{r}^{})$        | Charge density distribution.                  |

| F                         | Energy functional.                            |

| $\alpha$                  | Lagrange interpolation function.              |

| ξ                         | Parametric coordinate.                        |

| J                         | Jacobian.                                     |

#### CHAPTER I

### INTRODUCTION

The goal of this dissertation is to implement high-performance accelerators for numerical analysis and Computer-Aided Engineering (CAE) algorithms in a microcomputer or workstation environment. Using such platforms for CAE is desirable because of their low cost and easy accessibility when compared to operating within a mainframe environment.

Moreover, software provided in a mainframe environment is constrained by the information bandwidth between the mainframe and the user's terminal, and as a result tends not to be user-friendly. The workstation environment, on the other hand, allows high-bandwidth communication to a user's screen.

The problem we address here is that, more often than not, the workstation lacks the power needed to execute CAE algorithms. One strategy to overcome this shortcoming is to use the workstation as a graphical design device with the heavy computation off-loaded onto a mainframe through a network. This best of both worlds approach achieves the desired results but requires the presence of a mainframe computer locally with subsequent high costs.

Another strategy, which we adopt here, is to seek ways of speeding up the workstation itself so that it can solve difficult problems in a reasonable amount of time. Again, because we are operating in a low-cost environment, it is imperative that the methods used be sufficiently inexpensive to justify their use. Naturally,

these goals are somewhat conflicting, and any practical system produced must be a compromise between them.

The workstation can be accelerated in a number of ways. For example, time consuming operations such as multiplication and division could be augmented with special-purpose hardware. Indeed, most present day microprocessors have companion co-processors to perform such tasks. The problem with this approach is that one can only go so far before the cost becomes prohibitive because of the speedup in the support circuitry necessary to keep the fast computation unit busy.

In addition, fundamental physical limits are being reached in the speed at which conventional computer hardware can operate, so even the most optimistic advances in present-day circuit technology can only hope to provide marginal improvements. Even if some unforeseen new technology evolves, it is unlikely that it will be inexpensive enough to find use in desktop computers in a timely fashion.

A better way to achieve speedup is to exploit parallelism in the problems at hand. In the present context, the algorithms used in numerical analysis and CAE need to be dissected into pieces that can be executed in parallel on different processors.

The level at which an algorithm is partitioned is referred to as its granularity (Geist et al. [1987,238]). An algorithm is said to be coarse-grained if each processor is given a significant portion of the problem data to operate on in each computation step. For example, many of the algorithms presented in this dissertation are coarse-grained since each processor is given many columns of a matrix to operate on.

Conversely, we say an algorithm is *fine-grained* if each processor has only a small amount of the computation to perform in each step. An example is the distributed sum algorithm in Chapter 3, where each processor has only to perform a single multiplication and addition in each step of the algorithm.

While the possible partitionings of an algorithm depend intimately upon the algorithm itself, they also depends upon the architecture of the target parallel system. The two main factors are the power (size) of the processors in the system, and the provisions made for communication between them.

Parallel architectures can be broadly categorized into two main groups (Flynn [1972]); Multiple Instruction stream/Multiple Data stream (MIMD); and Single Instruction stream/Multiple Data stream (SIMD). In practice, these groupings support well defined types of parallelism (coarse and fine-grain respectively).

A MIMD machine (multiprocessor) consists of many autonomous computers, each executing a different program (multiple instruction stream) on data in its local memory. Typically, each computer communicates to other processors through either shared memory (bus based multiprocessor) or through point-to-point communication networks. Since every node is a computer in its own right, it is by necessity rather large. Therefore, it is not usual to see large numbers of processors in a system, and small networks of relatively powerful computational nodes are favoured. Because the processors are very powerful, systems of this type most naturally address coarse-grain parallelism.

A SIMD machine consists of many processors, each obeying the commands of a common master controller which interprets a single instruction stream. The processors operate in lockstep (performing identical instructions at identical times) upon data stored in local memory. This architecture tends to favour large numbers of very simple processors. Examples include the Connection Machine with 65,536 single-bit processors (Hillis [1985]), and the ICL DAP with 4096 single-bit processors (Hockney and Jesshope [1981,178-192]). Since there are so many processors, bus based communication through shared memory is impractical, and communication networks are used to share information.

Since it is a rare algorithm that can be partitioned into pieces that are not inter-dependent in some way, efficient and versatile interprocessor communication

is a key requirement of a parallel system. Making the necessary data available to a processor at the proper time encompasses much of a partitioning strategy.

Obviously, if every processor was directly connected to every other processor, this would not be a problem, and all communication could take place in one timestep. However, engineering and cost constraints prevent this for networks of any appreciable size, so we are forced to limit the number of processors to which a given processor can be connected.

Since two processors that need to communicate may not be directly connected, strategies that can facilitate communication through intervening processors must be developed. As such, we are required to continually weigh the gains in parallelism against the communication cost introduced by a particular partitioning on a given communication network.

Many different network topologies have been devised in an attempt to address these issues (Haynes et al. [1982], Gottlieb and Schwartz [1982]). Most represent an attempt to minimize communication costs while maximizing connectivity, and are usually successful only on certain classes of problems.

The hypercube is perhaps the most versatile of the "exotic" interconnection networks. It has the appealing property that, in a  $2^K$  processor hypercube, a processor is never any further than K communication steps from any other processor. This property comes at a the price of hardware complexity, however, since it requires that each processor have K communication links. This in turn translates into high system cost due to the large amount of wire routing required. The other networks step back from this ideal case, and sacrifice communication distance so that hardware requirements will be less stringent.

It can be readily seen that parallel processing is not a panacea. The issues are further complicated by the fact that most of the development of numerical and non-numerical algorithms has been geared toward implementation on scalar (non-parallel) processors. The conversion of scalar algorithms to parallel algorithms is

not a straightforward process. In fact there is no way of predicting whether or not an efficient parallel implementation of a given algorithm even exists. The crux of the problem is to find the right algorithms for a given architecture.

Working in the parallel realm requires a total rethinking of one's approach to programming. It is no longer the case that every variable and procedure in a program is available for use by all other parts. One has to adapt the algorithm so that its parallel components have available (or can obtain through communication) those resources and data that they need to carry out their duties.

After consideration of the above issues, it was apparent that the transputer microprocessor (Barron et al. [1983], INMOS [1985a,1985b], Whitby-Strevens [1985], Homewood et al. [1987]) was very well suited as the basis of a hardware accelerator. The transputer and its companion language Occam (Taylor and Wilson [1982], INMOS [1983]) directly address many of the above-mentioned issues.

The transputer microprocessor is unique in providing direct support for parallel processing. As we will see in Chapter 2, it has been designed from the ground up for this purpose. In many respects it allows one to break the rule that MIMD processors be few in number by allowing the construction of a powerful computational node in minimal circuit board area. This in turn translates into cost effective processing power.

With four high-speed serial I/O channels, a transputer directly addresses communication issues. This allotment of channels allows construction of point-to-point communication networks such as a linear array, square array, shuffle-exchange, 16-node hypercube, and cube connected cycle (Hill [1986]). Thus one can make use of existing algorithms for these network topologies.

Conversely, it should be emphasized that while this work concentrates on transputer networks, the algorithms developed are not limited to them. Any MIMD architecture with point-to-point communication can provide a suitable platform.

The transputer's only advantage is that it provides these required features at low cost.

We begin in Chapter 2 by describing the transputer and Occam in some detail so that the intimate relationship between the two can be better appreciated. The special features that support parallel processing are described.

In Chapter 3, matrix and vector algorithms are discussed. Such algorithms form the core of numerical analysis and CAE and, as such, it is imperative that efficient ways of implementing them exist. Basic vector operations such as vector addition and subtraction are implemented on a linear array. A scalar product algorithm running on a shuffle-exchange network is also implemented.

Two matrix-vector multiplication algorithms are also presented. The first, for dense matrices, makes use of the shuffle-exchange network in a manner quite similar to the scalar-product algorithm to achieve high efficiencies. A novel algorithm for banded sparse matrices, which requires a linear array of processors, is also presented.

Chapter 4 discusses two matrix solution techniques. The first, a novel implementation of Gaussian elimination, is applied to dense matrix systems. This solver was designed in conjunction with the boundary element algorithm discussed in Chapter 5. The second algorithm is a novel implementation of the preconditioned conjugate gradient method for the solution of banded sparse matrices.

Finally, Chapter 5 presents a novel parallel system that combines the Gaussian elimination solver from Chapter 4 with a Boundary Element Method (BEM) matrix generator. The objective was to integrate the two algorithms so that they would execute cooperatively on a problem with a minimum of data movement, so that high algorithmic efficiencies could be achieved.

#### CHAPTER II

### OCCAM AND THE TRANSPUTER

Occam's Razor: "Entities should not be multiplied unnecessarily"

— William of Occam [Ockham], Quodlibeta Septum, c. 1320.

This chapter describes the Occam programming language and the transputer micro-processor which were used as parallel processing tools for the work described in this dissertation. There were a number of reasons for this choice. Firstly, the transputer is designed to allow easy assembly of multiprocessor systems. Secondly, Occam allows the specification of parallel systems in a simple and concise manner. Also important is the fact that they allow inexpensive and powerful parallel processing systems to be constructed.

Together, Occam and and the transputer provide a means of implementing multiple instruction stream/multiple data stream (MIMD) parallel algorithms (Flynn [1972]). As such, many algorithms designed for multiprocessor systems will apply to them. However, some architectural features, such as the lack of shared memory, will invalidate others.

The version of Occam described here is more properly known as Occam 2. It supersedes the original version of the language which has become known as proto-Occam. Proto-Occam was intended only as a demonstration of the Occam parallel processing paradigm and lacked many features consistent with a useful programming language (a major omission being floating-point number support). Occam 2

improves on proto-Occam in many areas and is at least as useful for numerical programming as FORTRAN, but with the advantages that a strongly typed structured language provides.

While this chapter presents some examples of Occam programming, it is not meant as a tutorial. The purpose is to convey the main features and philosophies of the language. Should a tutorial be desired, see Pountain [1987], or Appendix A – which provides an in-depth programming example of a tutorial nature. It should be noted that since Occam is an evolving language, the examples presented here may not be syntactically correct according to future language specifications.

Because technology is fast moving, transputer hardware specifics will only be presented where absolutely necessary. Instead, the generic attributes of a typical transputer are described, with major emphasis on those features that directly support the Occam programming paradigm. Above all else, it is these features that make a transputer what it is.

#### 2.1 Occam

Occam has its roots in the theory of Communicating Sequential Processes (CSP) pioneered by C.A.R. Hoare [1978,1985]. It borrows many of its concepts from that work, but differs from the formal CSP model where required for practical implementation. For example, CSP theory allows recursively defined parallel procedures. Since a hardware implementation of such a construct would be difficult or impossible to realize, such capability was excluded from the language.

Practicality is perhaps the overriding tenet of Occam. True to Occam's razor, it is kept as simple as possible to allow direct hardware implementation of its fundamental features. Thus, on the proper hardware (i.e. the transputer), Occam can execute with an efficiency approaching that of assembly language while still providing the benefits of a high level language. Moreover, the Occam model is simple enough so that such hardware can be inexpensive.

In keeping with its CSP heritage, Occam provides a tool for describing parallel systems which consist of sequentially coded sections (called processes) executing in parallel. These processes are completely separate from one another, except for the existence of communication channels between them. Shared memory is not part of the programming model, avoiding the memory bottlenecks and expense of that multiprocessing technique.

Occam provides a little bit old and a little bit new. A programmer is able to carry over sequential programming skills when writing the sequential parts of Occam programs, while having available parallel execution of the component sequential processes.

#### 2.1.1 Occam Processes

Occam programs are constructed from three primitive processes.

#### 1. The assignment process

#### a := <expression>

The effect is the same as in other programming languages. The variable a is given the value of <expression>.

#### 2. The input process

#### ChannelName ? a

The value received on the communication channel ChannelName is assigned to variable a. The value input can be of any type.

#### 3. The output process

#### ChannelName ! <expression>

The value of **<expression>** ( which can be of any type) is output on the communication channel **ChannelName**. The output process can be treated as a way of assigning a value to a variable in another process. Since shared memory is not part of the Occam programming model, the only way of doing this is through a channel.

An Occam program is created by combining these primitive processes in a hierarchical fashion. The following sections describe the special features of the language which facilitate this process for the construction of both sequential and parallel programs.

#### 2.1.2 SEQ Constructor

The simplest way to combine the primitive processes is with the SEQ constructor. It identifies a list of processes (primitive or complex) that are to be executed in a sequential fashion. Thus SEQ allows the specification of conventional sequential programs. As an example, consider the following Occam code fragment (text that follows a double-dash is a comment):

```

CHAN OF ANY FromKeyboard: -- CHAN OF ANY can transmit

CHAN OF ANY ToScreen: -- any variable type.

BYTE Temp:

SEQ

FromKeyboard ? Temp -- Get keyboard data

ToScreen ! Temp -- Send it to the screen

```

The example displays a number of Occam syntactical and semantic conventions. The indentation of the two lines after the SEQ indicates that they are combined into a single non-primitive (complex) process by the SEQ. Thus, the effect of the SEQ (or any other constructor) is to combine the processes at the same indentation level under it into what is treated as a single process. This can be carried on indefinitely with the component processes themselves being defined in terms of SEQ.

The example also shows how identifiers used by a program are declared. Notice that channels are treated just like any other variable in the program, and must be explicitly declared before they are used. The three identifiers (at the same

indentation level as the SEQ are tied to the process created by the SEQ and are only valid within the scope of that process. In a hierarchy of processes, variables declared in the inner processes are not known outside of those levels (i.e. syntactically at smaller indentation levels).

In terms of Hoare's CSP theory, the SEQ constructor provides the first necessary condition for a CSP computation environment, namely, a way of defining conventional sequential processes (programs). The final step is to combine these processes into parallel programs composed of sequential processes executing in parallel with each other.

#### 2.1.3 PAR Constructor

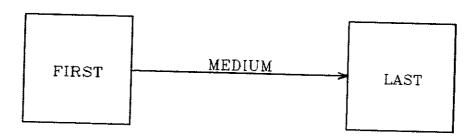

Consider the parallel processing system shown in Figure 2.1. We have two processes that are to execute in parallel with communication over a channel. The processes are totally separate except for communication over the channel. Most importantly, they run asynchronously from one another (except when they communicate), and do not share memory. In Occam, such systems may be specified using the PAR constructor.

Figure 2.1: Example of a parallel system. This represents the basics of the Occam parallel processing paradigm.

Introducing some more Occam syntax, consider the following named procedures:

```

PROC First(CHAN OF ANY ToLast)

INT A:

-- Integer variable

SEO

-- Construct sequential process

A := 10

-- Assignment primitive

ToLast ! A

-- Output on channel ToLast

-- End of PROC

PROC Last(CHAN OF ANY FromFirst)

INT B:

SEO

FromFirst ? B

-- Input on channel FromFirst

B := B * B

```

As in conventional languages, the two code sequences are given names by which they can be referred. Additionally the procedures (processes) can be given arguments which in this case happen to be channels. Using PAR the two processes may be combined into a single concurrent/parallel program.

```

CHAN OF ANY Medium: -- Declare inter-process Comm. CHAN

-- Ends of Medium are assigned to an

-- input and an output process.

PAR

-- Denote parallel construct

First(Medium) -- Component processes of PAR

Last(Medium) -- execute in parallel.

```

### 2.1.4 ALT Constructor

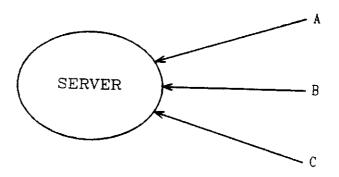

It is often necessary to construct a process that services a number of channels. Consider for instance, the situation depicted in Figure 2.2, in which a process has to take messages from channels A, B, and C and multiplex them down channel D. A parallel construct cannot be used, since it is not possible to share channel D among three processes servicing the input channels separately.

Figure 2.2: A sequential process servicing three inputs.

A possible solution would be to input from each of the channels in sequence, which will work if messages come often and regularly.

WHILE TRUE -- Loop forever

SEQ

ChanA ? Msg

ChanD ! Msg

ChanB ? Msg

ChanD ! Msg

ChanC ? Msg

ChanD ! Msg

The problem with this approach is that once an input statement is entered, the program will wait until it receives an input on that channel. If an input never comes (or comes at random times), the program will be deadlocked. Even though there may be messages ready on the other channels, they will never be serviced.

To handle such situations, the ALT constructor is provided. It provides a way of testing a number of input channels to see if they have messages pending. The first input channel to have a message on it is serviced. In the case of ties, the channels are serviced in an unspecified order. The following Occam code fragment shows how an ALT can be used to solve the present problem.

```

WHILE TRUE -- Loop forever

ALT

ChanA ? Msg -- Inputs if message present.

ChanD ! Msg -- Process executed if message present.

ChanB ? Msg

ChanD ! Msg

ChanC ? Msg

ChanD ! Msg

```

Once the ALT inputs from a channel, it terminates. It therefore must be set up in a loop if it is to repeatedly service all the channels. Note, that the clauses under the ALT are combined into a single process, and that each clause itself forms a process underneath it.

### 2.1.5 Characteristics of Occam Channels

We have seen that communication between parallel Occam processes takes place over channels. First of all, it should be emphasized that channel communication only makes sense between two processes that are executing in parallel. It is not possible to use channel communication between two processes that are components of the same sequential process. In any case, such communication wouldn't be necessary since processes that are components of a sequential process can pass information through variables in the normal way.

An Occam channel is a one way communication link between an input and an output process. Additionally, because (as we will see) channels are identified with fixed hardware resources, they cannot be shared among parallel components of a program. Once a channel is identified as a connection between two parallel components of a program, it can only be used between those two components and in only one direction until those components terminate. In terms of Occam syntax, this requirement is enforced via variable/channel scoping conventions.

Communication on channels can only take place when both the input and output processes on either end of the channel are ready to communicate. If either of them is not ready to enter into communication, the first must wait until the other is ready. Thus, channel communication serves to synchronize the two processes and the programmer does not need to explicitly manage this.

The characteristics of Occam channels, along with the various features of the Occam programming model were not chosen arbitrarily. A major consequence of these design decisions is that a simulation of an Occam program running on a single processor multitasking system will run exactly the same as it would with its component processes split up among a number of processors. This gives the program designer great freedom when partitioning a parallel program to run on a network of processors. The program is guaranteed to run identically no matter how the partitioning is done. The only restriction is that the resources of the target

hardware must be accommodated. One cannot place a process that requires five I/O channels onto a processor that has only four available.

#### 2.1.6 Occam Time

In most languages the concept of time is a superfluous one. Occam makes it an integral part of the language by providing each process with access to a special channel of type TIMER. Channels of this type return the value of a counter that is incremented at regular intervals (ticks). For example, a computation can be timed with the following code fragment:

```

VAL TicksPerSecond IS 1024: -- Hardware dependent value

TIMER Time: -- TIMER channel

INT StartTime, EndTime, TotalTime:

SEQ

Time ? StartTime

... Computation Process

Time ? EndTime

TotalTime := (EndTime - StartTime)/TicksPerSecond

```

Because Occam processes are independent, the Occam sense of time is necessarily local to each process. While the above code will yield identical times on two identical processors within a system, there is no guarantee that StartTime and EndTime will be given the same values on the two processors. Only the difference between them will be the same on each processor.

The timer can also be used to introduce timed delays. For example, the process

```

VAL DelayTicks IS 40:

TIMER Time:

INT CurrentTime:

SEQ

Time ? CurrentTime

Time ? AFTER (CurrentTime + DelayTicks)

```

will delay until the timer counter is greater than the sum of CurrentTime and DelayTicks (for simplicity, the case where this sum exceeds the maximum integer representation is ignored).

The latter usage of the Occam timer is important when channel communication is unpredictable (the result of random external events, for example). In these cases it allows, through the ALT statement, a way to test for input from a channel or a number of channels and escape to do other work if no input is present. Consider the following code fragment:

VAL TimeOutTicks IS 40:

TIMER Time:

INT CurrentTime, TimeOutTime:

INT RandomInput

CHAN OF ANY Random:

SEQ

Time? CurrentTime

TimeOutTime := CurrentTime + TimeOutTicks

ALT

Random? RandomInput

... service random input

Time? AFTER TimeOutTime

... service time out

... other processing duties

If no message on channel Random is received before 40 timer ticks have elapsed, the last clause of the ALT is entered, allowing other processing duties to be performed. Without the last clause, the ALT would wait until a message was received on Random. This mechanism is important as it allows one to have asynchronous interprocess communication.

#### 2.2 The Transputer

We have seen that Occam provides a simple and concise (if not powerful) way to express parallel systems. By itself it might be a useful tool. What makes Occam special is the existence of the transputer microprocessor. The transputer is designed to implement in hardware what the language Occam describes in software. Together they provide a potent tool for the implementation of parallel algorithms.

#### 2.2.1 Architecture

This section describes the architecture of the transputer microprocessor. The features described are that of a generic transputer and represent the minimum hardware requirements that a microprocessor must have to be called a transputer.

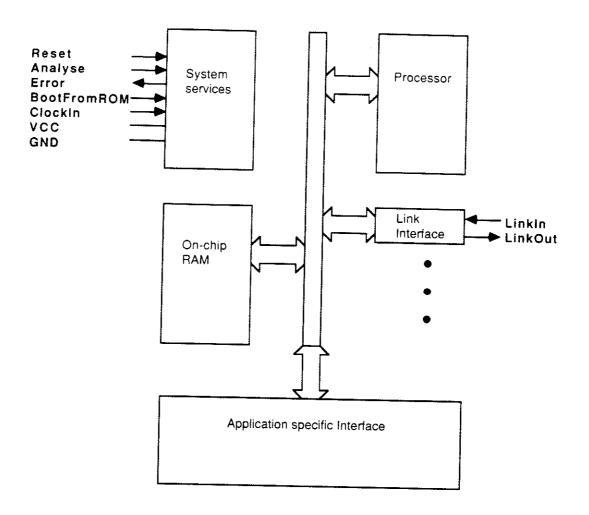

As can be seen in Figure 2.3, the main features of a transputer are:

- 1. CPU: Currently a reduced instruction set (RISC) design. The compactness of the CPU allows other essential features to be integrated on the same die.

- 2. RAM: On-board static RAM that can be accessed at least three times faster than external memory. Current transputers possess 2K or 4K bytes. This is general system RAM, and is not used as cache.

- 3. Communication Links: Current transputers possess four INMOS bidirectional communication links which implement a 10 or 20 MHz Occam channel in each direction (1 or 2 megabytes/second).

- 4. Programmable memory interface: Interfaces the transputer to external memory with the minimum of external interface logic by providing all necessary refresh, timing, and control signals.

- 5. Special purpose function units: architectural extensions that allow transputers to be tailored to specific applications.

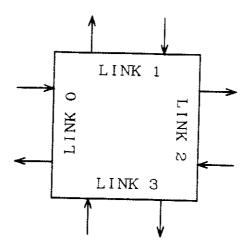

Figure 2.4 depicts the simplest possible view of a transputer – a black-box with four (or more) communication links (an input channel and an output channel are coupled together in pairs to form a link). As such, the transputer can realize any

Figure 2.3: The transputer architecture. Copyright INMOS Corporation. Reproduced with permission.

network which requires four or fewer communication channels per computational node. In this work, they are used in linear array and shuffle-exchange configurations. Other possible networks include the square mesh and the toroidal mesh, as well as various multistage networks and the cube connected cycle (Hill [1986]). This kind of flexibility is important as it allows one to tailor the network topology to the data flow properties of the target algorithm.

Figure 2.4: Transputer communication model.

The transputer definition allows for special-purpose hardware over and above what is pictured. For example, in one version of the transputer (the T-800), an on-board floating point unit is added (Homewood et al. [1987]), while in another a disk-controller is featured (Moore [1986]). Each special purpose transputer then plays a particular role in a given parallel system, with the links serving to tie the entire system together.

With these features, the transputer is really a microcomputer on a chip, possessing built in CPU, communication links, and RAM. In fact, it is capable of functioning with only external power and clock supplied.

The transputer's architecture is designed to support parallel processing. As such, the transputer lacks features desirable in single processor systems that may compromise its applicability to parallel processing (e.g. memory management). The success of this approach can be measured in a number of ways. We will see that the transputer has been designed to minimize cost, communication complexity, and board area - making it ideally suited for constructing large networks.

#### 2.2.2 Support for Occam

The very reason for the transputer's existence is to provide hardware support for the Occam parallel processing model. Perhaps the most visible and important of these features are the on-chip communication channels. They provide the means by which Occam processes can communicate, and have characteristics entirely compatible with the definition of Occam channels in Section 2.1.5. It is important to realize that these are point to point communication channels (as is dictated by the Occam channel model), and there can only be one transputer at either end of a channel. It is not possible to connect one channel to many transputers in a broadcasting type of topology.

The point to point communication architecture that transputers implement has a number of advantages over conventional bus-based systems. Firstly, there is no contention for communication resources as might be found on a bus shared among many processors. Also, as the system grows, total communication bandwidth grows with it. This assumes that the communication requirements of the algorithms to be implemented are predominantly local.

To provide for seamless distribution of Occam processes over a network of processors, the transputer CPU possesses a multitasking kernel in hardware. It maintains two queues of Occam processes (low and high priority) which it timeslices automatically. If a process is waiting to communicate, it is descheduled until its companion process is ready to communicate with it. In this way, CPU cycles are not wasted in busy-wait (polling) loops and communication is carried out with the maximum possible efficiency.

In accordance with the Occam model, these parallel Occam processes communicate via channels. Processes on the same chip communicate via internal virtual channels, while processes on different chips use the external hardware channels. Since channel communication synchronizes communicating processes, the transputer is able to execute any number of them as if each resided on its own processor. This

allows a given Occam program (essentially a collection of communicating processes) to be partitioned on a network as one desires (as long as enough hardware channels are available to support the connectivity of the partitioning).

To handle Occam's sense of time (see Section 2.1.6), each transputer incorporates a timer. In current transputer implementations, the high-priority process timer has greater resolution than the timer for low-priority processes (under the assumption that high-priority processes are more time critical). Occam sees the timer as a special channel which is available to all processes within a given transputer (normal channels can have only one originating and terminating process).

Finally, the transputer's CPU instruction set is designed to optimally implement the various features of the Occam language. We have already seen that the CPU is able to directly implement a PAR Occam construct. It also has instructions for the installation of processes on execution queues, the ALT operation, as well as instructions to perform channel input and output.

### 2.2.3 Constructing Large Transputer Networks

Since the intention of the transputer is to provide a means of doing parallel computation, it is important that such systems be easy to build. A number of features of the transputer make the system engineer's job easier.

The first feature is that the transputer does not require the distribution of a high-frequency clock. Conventional microprocessors require that an external clock be supplied at their internal clocking rate, which could be as high as 20-30 MHz. Such high frequency signals cause much grief for board designers, especially if they are required to travel large distances on the circuit board.

Transputers, on the other hand, only require an external clock of 5 MHz no matter what the internal device clock-rate. This standard input clock is then used to derive a higher internal clock speed. The system designer need only distribute this relatively low speed clock throughout a circuit board.

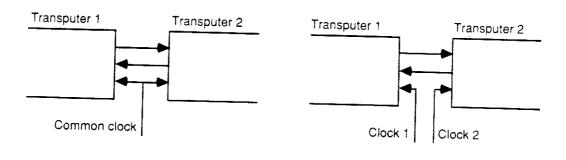

The engineering characteristics of transputer communication channels also support the construction of large networks. Transputer channels are implemented as bidirectional serial communication lines as shown in Figure 2.5, and provide one Occam channel in either direction.

Figure 2.5: Transputer communication link. Copyright INMOS Corporation. Reproduced with permission.

Such an architecture has a number of important characteristics. For one, it is much less costly to distribute a three-line bus than it would be to distribute wide parallel buses. Since transputers may number in the hundreds in a given parallel computation system, reducing cost is paramount.

Besides the obvious ease of routing 3 lines, one does not pay a capacitive load penalty as more transputers are added to the system. In a bus-based system, the whole system must slow down as the bus is lengthened to accommodate more processors. In a transputer system, this penalty is more or less constant for each transputer no matter what the size of the system. Moreover, link communication is insensitive to clock phase between the sending and receiving transputer. All that is necessary is to maintain the clock frequency within fairly loose tolerances, allowing the system designer flexibility in routing clock signals. As Figure 2.5 shows, the input transputer clocks need not come from the same source.

When building systems with a large number of processors, it is desirable to pack as many processors on a single board as possible. The usual limiting factor is the amount of support circuitry that must be placed around a microprocessor to provide interfaces to memory and peripherals. For the most part INMOS channels can interface to peripherals with no external circuitry, offering great savings in board area. Furthermore, the transputer's programmable memory interface virtually eliminates the need for external memory interfacing circuitry by generating all timing, control, and refresh signals for a variety of external memory types.

With these space-saving features, it is possible to construct a transputer node with two Megabytes of RAM in as little as 51 cm<sup>2</sup> of board area (Electronics [1988]). If an application did not require much RAM, the node size could be reduced still further by utilizing only the internal transputer RAM and running the transputer without any external support circuitry save clock generation (which could be shared among all transputers on a single board).

# 2.2.4 Hardware Considerations for Occam Programming

While the transputer hardware is designed to support the Occam programming model, it has architectural features that enhance program performance which are not required by the model. This section outlines two of the most important ones. Further notes about performance issues can be found in Atkin [1987].

### Using On-Board RAM

Unlike microprocessors with on-board cache, the on-board RAM of a transputer is part of its normal address space. Its advantage over external memory is that it can be accessed at least three times faster. Since it is normal memory, it can be used to store both code and/or data.

Since the transputer encodes four instructions within a single word, it fetches instructions faster than it does data words. It is therefore desirable to place critical data into the on-chip RAM, to speed access to it. Indeed, the current Occam

compiler places data on chip in preference to code. If one has large vectors, it is impossible to place code on-chip in preference to data because the vectors will take up all of the on-chip RAM. It is possible that this restriction may be removed in the future, however.

Making use of internal RAM for data storage is (at the moment) an implicit rather than an explicit process. The programmer is given details of how variables defined in the Occam source are placed into memory. By arranging the source code declarations properly, the desired critical variables can be placed into internal RAM.

### Channel Communication

Each link on a transputer possesses an independent controller that has direct memory access (DMA) to the transputer's memory space. Once a transfer is initiated on a link, the controller takes over responsibility for the transaction and frees the processor to do other tasks. Thus each link transfer is a direct memory to memory transfer between the processors at either end of the link.

An important feature of the link controller, called *slice communication*, is the ability to transfer blocks of memory in addition to single byte and word transfers. With processor overhead equivalent to a single word transfer, the CPU is able to initiate a multi-word transfer that is totally controlled by the link hardware. The CPU is then able to perform other tasks while the transfer is taking place. Moreover, slice communication can be performed on three links simultaneously without CPU interaction, and on all four links with only a small CPU degradation because of memory-bus contention.

To use this feature of the transputer, Occam provides a special syntax on the output and input process statements. For example, an integer array of length 1000 could be sent down a channel by the output process

OutChannel ! [IntArray FROM O FOR 1000]

and received by the input process

## InChannel ? [IntArray FROM O FOR 1000]

Slice communication allows the transfer of large amounts of information between processors while computation is being performed at full or nearly full speed. It thus has the potential to provide nearly transparent loading/unloading of data for the next computation step, while the current step is proceeding. This could be especially important in applications such as computer vision, where the next image could be loaded in while the previous one is being analyzed.

#### CHAPTER III

# MATRIX AND VECTOR OPERATIONS

Vector and matrix operations are almost ubiquitous when it comes to algorithms in numerical analysis. For this reason it is particularly important that efficient ways of handling them exist. This chapter details ways of implementing important representatives of these algorithms on transputer arrays.

The most important aspect of the partitioning strategy is the way vector and matrix storage is distributed among the processors. This not only dictates what computations a processor can perform, but what communication is needed. The important thing is to choose a partitioning that minimizes global communication as much as possible.

The algorithms presented in this chapter view an array of processors with local memory as a distributed storage and computation network. The storage of each vector and matrix is divided up more or less equally between the processors, allowing each processor to work on its portion independent of the others.

For the sake of simplicity, and in keeping with the goals of this research, the implementations are restricted to linear arrays of transputers or simple shuffle-exchange (SE) graphs (Stone [1971]). The linear array accommodates algorithms with nearest neighbour communication requirements while the SE network is particularly efficient for performing global accumulations.

The beauty of these two networks is that the transputer is capable of supporting both of them simultaneously, which allows a much greater range of algorithms

to be implemented efficiently. Unfortunately, restrictions in the hardware used for this dissertation prevented the simultaneous use of the two networks. This would have been desirable for the conjugate gradient algorithm presented in Chapter 4.

A final note is in order. The reader will notice that while this chapter contains estimates of algorithm performance, it lacks results from actual implementation. This was done for a number of reasons, the first being that experience has shown the estimates to be quite accurate. The major reason, however, is that most of the algorithms described here are used for the preconditioned conjugate gradient algorithm in Chapter 4. As actual results are given for that implementation, the merits of the algorithms of this chapter can be inferred from there.

#### 3.1 Estimating Algorithm Execution Times

For the algorithms considered here, it is possible to accurately estimate their execution times on transputer or MIMD networks by counting the sequential vector and scalar operations and multiplying by the empirically derived times for these operations. When identical operations are performed in parallel, they count only once toward the final tally (i.e. they are treated as one sequential operation).

Table 3.1 shows timing results for some "primitive" operations on the T-414 and T-800 (a T-414 with floating-point support) transputer microprocessors. Since the T-800 was unavailable, timings for it had to be estimated as indicated in the table. While the list is not exhaustive, it is sufficient to give a fairly accurate estimate of execution times for matrix-vector algorithms.

Some things to note about the table:

- 1. the timings were performed for 32-bit floating-point operations and 32-bit word transfers on a 15 MHz T-414;

- 2. vector timings include the overhead of looping and array subscripting, and are given as the execution time per vector component;

Table 3.1: Timings for primitive operations on T-414 and T-800.

| Symbol                        | Operation                | T-414 $(\mu s)$ | $T-800 \; (\mu s)$ $2.03 \ddagger$ $1.98 \ddagger$ |  |  |  |

|-------------------------------|--------------------------|-----------------|----------------------------------------------------|--|--|--|

| $T_s^+$                       | Scalar Addition          | 20.3            |                                                    |  |  |  |

| $T_s^-$                       | Scalar Subtraction       | 19.8            |                                                    |  |  |  |

| $T_s^{	imes}$                 | Scalar Multiplication    | 15.4            | 1.54‡                                              |  |  |  |

| $\frac{T_s^{\div}}{T_v^{+*}}$ | Scalar Division          | ion 18.5        |                                                    |  |  |  |

| $\overline{T_v^{+*}}$         | Vector Addition          | 26.0            | 2.60‡<br>2.66‡                                     |  |  |  |

| $T_v^{-*}$                    | Vector Subtraction       | 26.6            |                                                    |  |  |  |

| $T_v^{	imes *}$               | Vector Multiplication    | 21.6            | 2.16‡                                              |  |  |  |

| $T_v^{\div*} = T_v^{sc*}$     | Vector Division          | 24.3            | 2.43‡                                              |  |  |  |

| $T_v^{sc*}$                   | Scale Vector by Constant | 19.8            | 1.98‡                                              |  |  |  |

| T.=*                          | Vector Assignment        | 4.8             | 4.8                                                |  |  |  |

| $T_s^X\dagger$                | Transmit Scalar Word     | 10.8            |                                                    |  |  |  |

| $T_v^X\dagger^*$              | Transmit Vector Word     | 8.4             | 8.4                                                |  |  |  |

<sup>\*(</sup>per vector component)

- 3. Vector communication utilizes the "slicing" feature of the transputer hardware discussed in Section 2.2.4; and

- 4. use of on-chip transputer RAM (which is a minimum of three times faster than external RAM) was avoided as it would have artificially decreased the measured timings (thus the numbers presented contain the penalty for off-chip RAM access).

By using actual execution times as weights for the operation counts it is possible to provide clock time estimates for the algorithms of this and the next chapter. This is much more useful than the operation counts alone, as it allows comparison to similar algorithms running on other hardware.

The metric used to characterize the algorithms in this dissertation is speedup efficiency  $(E_{N_p})$ . Letting the time taken for 1 and  $N_p$  processors to solve a problem

<sup>† (</sup>using 10 MHz links)

<sup>‡ (</sup>estimated to be 0.1 of the T-414 value)

be  $T_1$  and  $T_{N_p}$  respectively, the speedup efficiency is defined as

$$E_{N_p} = 100 \frac{(T_1/N_p)}{T_{N_p}} \tag{3.1}$$

and represents the percentage of ideal speedup that is attained. In an ideal world  $E_{N_p}$  would be 100%, but in practice it is less than 100% due to communication and synchronization overhead.

#### 3.2 Vector Operations

We consider two classes of vector operations in this section. The first class includes monadic and dyadic vector operations that yield a vector result. The second is the scalar product, which combines two vectors to produce a scalar result.

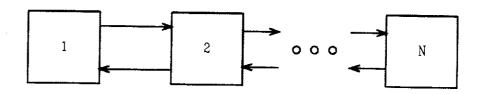

These two classes have very different requirements for parallel execution because of their communication requirements. The monadic and dyadic vector operations are such that they require no inter-processor communication when properly partitioned. However, data input and result output operations are still necessary, so we will implement them on a linear array of processors as shown in Figure 3.1.

The scalar product, on the other hand, requires a great deal of communication, since partial-sums from all of the processors in the network must be brought together for a final summation. While the linear array is fairly efficient for the operation when the network contains a small number of processors, the efficiency would degrade for larger networks. For this reason, Section 3.2.2 introduces the shuffle-exchange network for this operation.

Figure 3.1: A linear array of processors.

#### 3.2.1 Vector Combination

The dyadic vector combination operations considered include addition, subtraction, multiplication, and division. Monadic operations include vector assignment and scaling. In all these cases, vectors are combined or operated on in a component-by-component fashion, giving a vector result. The most notable property of these component operations is that they are independent from one another.

Since each component operation is independent, no inter-processor communication is required for the algorithm if a given processor contains all the information necessary to carry out that operation. In the case of the dyadic operations we require that a processor contain corresponding components of the two vectors that are to be combined. A consequence of this is that we are free to choose any partitioning for the vectors as long as we agree to partition each of them identically.

We are ignoring the case where different processors are operating on disjoint sets of vectors. Each processor could store all the components of the vectors it is operating on and process them independently from the other processors. This is a more macroscopic (larger grain) type of algorithm, however. While it gives an average speedup, it does nothing to speed up an individual operation such as vector addition.

Figure 3.2 shows the vector partitioning that was used in this work. This is not the only imaginable partitioning, merely the most orderly (a special application might require a different partitioning). Each vector is divided into a number of contiguous segments, with each segment stored on a processor within a linear array. The segments are assigned to the processors such that segment i is stored in processor i.

Figure 3.2: Partitioning of vectors for parallel computation.

Given this partitioning, Occam allows us to express the vector operations quite simply. Consider the Occam procedure VectorAdd:

```

PROC VectorAdd( []REAL32 A, -- result

VAL []REAL32 B,C, -- operands

VAL INT NumComponents)

SEQ I = 0 FOR NumComponents

A[I] := B[I] + C[I]

```

Each processor in the network would contain a local copy of this procedure along with the storage for the segments from the vectors involved. A parallel system of four processors could then be denoted (ignoring declarations of the variables):

PAR

VectorAdd(A,B,C,NumComponents)

VectorAdd(A,B,C,NumComponents)

VectorAdd(A,B,C,NumComponents)

VectorAdd(A,B,C,NumComponents)

or more succinctly (where NumProcessors = 4)

PAR I = 0 FOR NumProcessors VectorAdd(A,B,C,NumComponents)

Given knowledge about how many components of the vector it is storing, each processor (each component of the PAR) can operate with virtually 100% efficiency.

### 3.2.2 Scalar Product

The scalar product between two vectors presents a very different problem. Given that each processor can compute a partial sum of the scalar product, we are left with a single number in each processor that must be summed with all the others. What remains then, is the problem of communicating these numbers between the processors so that a final sum can be computed.

First, consider  $N_p$  processors arranged in a linear array. The sum could be obtained in  $(N_p-1)$  communication steps and  $(N_p-1)$  addition steps simply by passing a partial sum from processor to processor — leaving the final answer in the last processor in the chain. If the result is needed in all the processors, an additional  $(N_p-1)$  communication steps are required to distribute the final result, giving a total of  $2(N_p-1)$  communication steps.

This simplistic approach can be improved upon by recognizing that the accumulation of the partial sum is independent of the order in which it is done. Instead of forming the sum from one end of the array to the other, we can have two parallel accumulations proceeding from each end to the middle of the array. With this scheme, the scalar product can be calculated in  $\frac{1}{2}N_p$  computation steps and  $(N_p-1)$  communication steps (including distribution of the final sum to all processors).

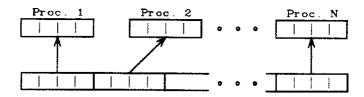

In both these cases, we are constrained by the linear array, and are forced to compute the scalar product in almost a sequential fashion, with considerable communications overhead. As the number of processors increases the operation can become quite costly. This bottle-neck can be overcome using the shuffle-exchange (SE) network shown in Figure 3.3.

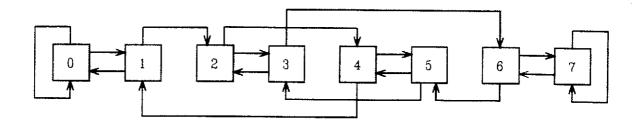

Figure 3.3: Time sequence of shuffle-exchange operations. Each row of processors represents the *same* set of processors at a subsequent step in the communication sequence. The lines represent the interconnections within the set of processors.

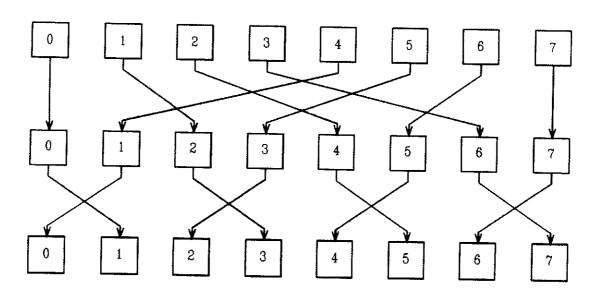

The SE network was first popularized by Stone[1971]. He demonstrated its applicability to a wide variety of problems including the Fast Fourier Transform (FFT) and matrix transposition. Lang and Stone[1976] showed its usefulness as a permutation network. Of interest here is its ability to sum  $N_p$  numbers in  $\mathcal{O}(\log_2 N_p)$  steps.

Formally, the SE topology is defined for networks of  $N_p = 2^K$  processors (K an integer) which we number 0 to  $(2^K - 1)$ . It combines the so called perfect shuffle interconnection with a pair-wise exchange to form a simple, yet powerful interconnection network. The perfect shuffle connects processor  $P_i$  to a processor whose index is given by the following rule (a permutation mapping):

$$P_{i} \longrightarrow \begin{cases} P_{2i}, & 0 \leq i \leq N_{p}/2 - 1 \text{ (lower half)}, \\ P_{2i+1-N_{p}}, & N_{p}/2 \leq i \leq N_{p} - 1 \text{ (upper half)}. \end{cases}$$

(3.2)

The effect of this operation can be seen in Figure 3.3. Messages from the lower and upper halves of the array are shuffled through the array in an alternating fashion, much like the two halves of a deck of playing cards would be when perfectly shuffled.

The shuffle operation is followed by a bi-directional exchange between adjacent pairs of processors according to the rule:

$$P_{2i} \longleftrightarrow P_{2i+1} \quad 0 \le i \le N_p/2 - 1. \tag{3.3}$$

Keeping in mind that these connections involve the same set of processors, Figure 3.3 can be collapsed to give a truer picture of the SE interconnections as shown in Figure 3.4.

Given the SE topology, we can now describe an algorithm for summing a set of  $N_p$  numbers (with one number located in each processor). Let each processor contain one of the numbers to be summed in variable A. Further, let there be a temporary location B in each processor. The following algorithm, which is performed identically by each processor, will sum the  $N_p$  values of A together:

Figure 3.4: The shuffle-exchange interconnection network.

- 1. send A out on shuffle-out port and input into B on shuffle-in port (Shuffle operation);

- 2. output B on exchange-out port and input value into A on exchange-in port (Exchange operation);

- 3. sum B into A (Add operation); and

- 4. loop back to step 1.

If there are  $N_p = 2^K$  processors, then after  $\log_2(N_p) = K$  iterations each processor will contain the sum of all the numbers in variable A. Table 3.2 shows a detailed listing of these operations for an eight processor network adding the numbers 0 to 7 inclusive.

This scheme has two advantages over the linear interconnection network:

- 1. the operation is completed in logarithmic time  $(2 \log(N_p))$  communication steps and  $\log(N_p)$  computation steps to sum  $N_p$  numbers); and

- 2. each processor ends up with the final sum, so there is no need to explicitly distribute it.

Additional insight into the workings of the SE algorithm presented here can be gleaned by following the path of a number from its starting point (the so-called

Table 3.2: Shuffle-exchange vector sum. Each row shows the values contained in A and B after the operation in the first column is performed (S = Shuffle, E = Exchange, and A = Add).

|    | PROCESSOR |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|----|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| OP | 0         |    | 1  |    | 2  |    | 3  |    | 4  |    | 5  |    | 6  |    | 7  |    |

|    | A         | В  | Α  | В  | A  | В  | A  | В  | A  | В  | A  | В  | A  | В  | A  | В  |

|    | 0         | *  | 1  | *  | 2  | *  | 3  | *  | 4  | *  | 5  | *  | 6  | *  | 7  | *  |

| S  | 0         | 0  | 1  | 4  | 2  | 1  | 3  | 5  | 4  | 2  | 5  | 6  | 6  | 3  | 7  | 7  |

| E  | 4         | 0  | 0  | 4  | 5  | 1  | 1  | 5  | 6  | 2  | 2  | 6  | 7  | 3  | 3  | 7  |

| A  | 4         | *  | 4  | *  | 6  | *  | 6  | *  | 8  | *  | 8  | *  | 10 | *  | 10 | *  |

| S  | 4         | 4  | 4  | 8  | 6  | 4  | 6  | 8  | 8  | 6  | 8  | 10 | 10 | 6  | 10 | 10 |

| E  | 8         | 4  | 4  | 8  | 8  | 4  | 4  | 8  | 10 | 6  | 6  | 10 | 10 | 6  | 6  | 10 |

| A  | 12        | *  | 12 | *  | 12 | *  | 12 | *  | 16 | *  | 16 | *  | 16 | *  | 16 | *  |

| S  | 12        | 12 | 12 | 16 | 12 | 12 | 12 | 16 | 16 | 12 | 16 | 16 | 16 | 12 | 12 | 16 |

| E  | 16        | 12 | 12 | 16 | 16 | 12 | 12 | 16 | 16 | 12 | 12 | 16 | 16 | 12 | 12 | 16 |

| A  | 28        | *  | 28 | *  | 28 | *  | 28 | *  | 28 | *  | 28 | *  | 28 | *  | 28 | *  |

<sup>\*(</sup>don't care)

radioactive tracer technique). By marking the processors touched by that number and any numbers affected by it (directly or indirectly) as they cycle through the array, one can see the path fan-out in a binary tree like fashion. At the end of  $\log_2(N_p)$  cycles all processors in the array will have received the number or one of its descendants. Since a number and its descendants never cross paths, they always contribute to an independent sum. Moreover, because this happens from all the processors,  $N_p$  independent sums are accumulated.

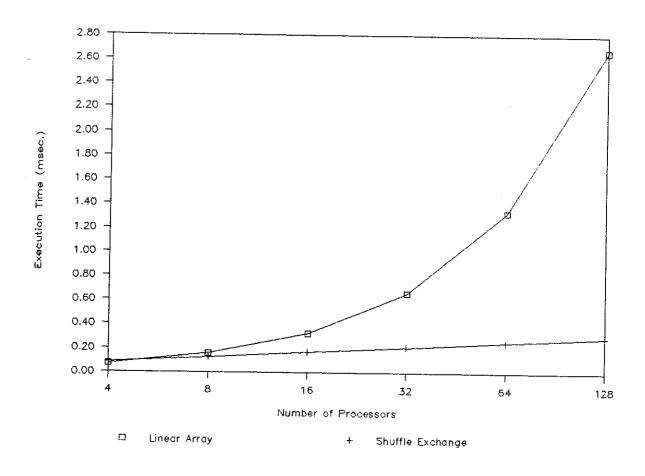

We are now in a position to compare the estimated execution times for the two scalar product/distributed addition algorithms outlined here. Since the time needed to calculate the initial partial sum in each processor is the same for all the algorithms, it is not included in the times given. Figure 3.5 shows the results for

Figure 3.5: Comparison of the scalar-product (distributed addition) algorithms.

various network sizes (constrained by the requirements of the SE network). In all cases of interest, the SE network outperforms the linear array.

Thus the SE network is very useful for combining objects that are distributed amongst a collection of processors. For small numbers of processors, the gains are not great, but owing to the logarithmic growth in costs, the gains are very significant for larger numbers of processors.

This example also serves to illustrate the ability of the transputer/Occam programming model to address both coarse-grain and fine-grain parallelism. The distributed addition algorithm is essentially a fine-grain algorithm, since very little computational work is done at each step. In the next section, we will see the same

SE network used for a coarse-grain algorithm (dense matrix-vector multiplication). This property allows great flexibility when designing algorithms.

An Occam example in Appendix A shows how a SE network could be implemented on a transputer array. The code demonstrates the distinct advantage of the SE network on transputer arrays, namely, ease of implementation. A comparison of the code to implement the bi-directional sum on a linear array to the SE network shows the code for the SE to be simple and elegant, requiring no logic for its execution. The linear array implementation, on the other hand, requires considerable logic to handle special cases in communication, and is generally "messy" in comparison.

### 3.3 Matrix-Vector Multiplication

Matrix-vector multiplication represents a step up in complexity from the vector algorithms described in this chapter. The biggest problem arises from the interaction between storage partitioning of the matrix and the communication requirements that are dictated by that partitioning.