# Design and Implementation of an Automated Testbed for Evaluating Switching Behavior of Power Semiconductors

by

#### Avishek Ghosh

A Thesis submitted to the Faculty of Graduate Studies of

The University of Manitoba

in partial fulfilment of the requirements of the degree of

Master of Science

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg, Manitoba, Canada

Copyright © 2019 by Avishek Ghosh

#### **Abstract**

A Double Pulse Tester (DPT) is a widely used setup for evaluating the switching behavior of power semiconductor devices. The results obtained from double pulse tests provide significant insight into the dynamic behavior of a device under test (DUT) such as its switching losses, switching speed (di/dt, dv/dt), turn-on and turn-off times etc. However, it is a tedious process to perform these tests under different permutations of test parameters and thereafter analyze the experimental data manually. This work presents a newly developed automated DPT prototype, which can run the tests one after another once the test conditions are entered in a Graphic User Interface (GUI). The test-control system also records the switching waveforms, test data, and systematically processes them to generate usable characterization results. The automatic, low cost, compact, modular and user-friendly design allows the proposed testing and measurement system to stand out from the conventional DPT setups. The design principles are experimentally verified by implementing a DPT prototype capable of testing power semiconductor devices up to 1000V, 60A, 250°C.

#### Acknowledgments

It is with immense gratitude that I acknowledge the support and guidance of my supervisor, Dr. Carl (Ngai Man) Ho. It would not have been possible for me to conduct this research work without his endless patience and continual encouragement. During some tough moments in my personal life during the M.Sc. program, he extended his utmost co-operation and mental support for which I will always be indebted to him. His courses have given me a strong foundation in power electronics. I also express my sincere thanks to him for giving me the opportunity to work as a research assistant in the Renewable Energy Interface and Grid Automation (RIGA) lab, a laboratory established by Dr. Ho in 2014. Dr. Ho's strong focus on practical, hands on work and the availability of state-of-the-art instrumentation and facilities at RIGA lab have given me the liberty to design, build and test multiple hardware systems during my M.Sc. program. His extensive industrial experience and technical guidance was invaluable for this work.

I would also like to acknowledge the contribution of undergraduate summer research students Mr. Rahul Singh and Mr. Jared Prendergast in this research work.

My sincere thanks also goes to the Department of Electrical and Computer Engineering academic staffs, Ms. Amy Dario and Ms. Traci Gledhill for their assistance with different paperwork from time to time and technical staffs, Mr. Erwin Dirks, Mr. Sinisa Janjic, Mr. Zoran Trajkoski, Mr. Cory Smit and Mr. Shrimal Koruwage for their assistance with my hardware work.

I would like to thank my friend and colleague, Mr. Yanming Xu for sharing part of his experimental results that helped in performing a case study. I also express my gratitude to other fellow lab members for extending their moral and technical support during the research work.

# **Dedication**

To my dear parents and beloved wife

# **Table of Contents**

| Abstract                                 | ii   |

|------------------------------------------|------|

| Acknowledgments                          | iii  |

| Dedication                               | iv   |

| Table of Contents                        | v    |

| List of Tables                           | viii |

| List of Figures                          | ix   |

| List of Abbreviations                    | xii  |

|                                          |      |

| Chapter 1 Introduction                   | 1    |

| 1.1 Background                           | 1    |

| 1.2 Review of Semiconductor technologies | 2    |

| 1.3 Semiconductor characterization       | 8    |

| 1.3.1 Turn-on Characteristics            | 9    |

| 1.3.2 Turn-off Characteristics           | 11   |

| 1.4 Semiconductors in converters         | 14   |

| 1.5 Overview of Double Pulse Tester      | 16   |

| 1.5.1 Basic Topology                     | 16   |

| 1.5.2 Principles of Operation            | 17   |

| 1.6 Literature Review                    | 19   |

| 1.7 Motivation of the Thesis             | 25   |

| 1.8 Organization of the Thesis           | 30   |

| 1 9 Research contributions               | 32   |

| Chapter 2 Hardware Design of Automatic Tester   |    |

|-------------------------------------------------|----|

| 2.1 System Architecture                         |    |

| 2.2 Control Board Design                        | 37 |

| 2.2.1 Power Supply Unit (PSU)                   | 37 |

| 2.2.2 Sensor and Control Units                  | 39 |

| 2.2.3 Double Pulse Control Unit (DPCU)          | 42 |

| 2.3 Power Board Design                          | 44 |

| 2.3.1 PCB Design criteria                       | 45 |

| 2.3.2 Gate Driver Design                        | 48 |

| 2.3.3 DUT Heating Unit Design                   | 49 |

| 2.4 Load Inductor Selection Criteria            | 52 |

| 2.5 DC Capacitor Bank Design                    | 52 |

| 2.6 Chapter Summary                             | 54 |

| Chapter 3 Controller Design of Automatic Tester | 56 |

| 3.1 Control Architecture                        | 56 |

| 3.2 Control Operation                           | 59 |

| 3.3 Chapter Summary                             | 62 |

| Chapter 4 Data measurement and processing       | 63 |

| 4.1 Specification of Measurement tools          | 63 |

| 4.1.1 Device voltage measurement                | 65 |

| 4.1.2 Device current measurement                | 67 |

| 4.1.3 Probe Calibration                         | 70 |

| 4.2 Waveform Analysis Tool                      | 71 |

| 4.3 Chapter Summary                             | 73 |

| Chapter 5 Experimental Results                     | 74  |

|----------------------------------------------------|-----|

| 5.1 Experimental Setup                             | 74  |

| 5.2 Experimental Results                           | 77  |

| 5.2.1 Switching results Vs. Device current         | 80  |

| 5.2.2 Switching results Vs. Case Temperature       | 81  |

| 5.2.3 Switching results Vs. Gate resistance        | 85  |

| 5.2.4 High-side device measurements                | 87  |

| 5.2.5 Additional Switching results                 | 90  |

| 5.3 Case Study – Switching cell in Boost converter | 91  |

| 5.4 WBG device characterization                    | 95  |

| 5.5 Chapter Summary                                | 97  |

| Chapter 6 Conclusions and Future Work              | 98  |

| 6.1 Conclusion                                     | 98  |

| 6.2 Future Work                                    | 101 |

| Deferences                                         | 102 |

# **List of Tables**

| Table 1.1 Material properties of Si, SiC and GaN [7], [20]                    | 4  |

|-------------------------------------------------------------------------------|----|

| Table 1.2 Definition of parameters used in Figure 1.8 and Figure 1.9          | 17 |

| Table 2.1 Technical specification of DPT PSU converters                       | 39 |

| Table 2.2 Function of microcontroller pins in double pulse generation         | 43 |

| Table 4.1 Technical comparison of latest voltage probes [51]                  | 66 |

| Table 4.2 Technical comparison of the latest current measurement devices [51] | 68 |

| Table 5.1 Technical Specifications of the Experimental Setup                  | 75 |

| Table 5.2 Key parameters used in experimental result analysis                 | 78 |

| Table 5.3 Switching parameters for change in case temperature                 | 84 |

| Table 5.4 Switching parameters for change in gate resistances                 | 87 |

| Table 5.5 Key parameters measured for Anti-parallel Diode                     | 89 |

| Table 5.6 Switching parameter comparison between Boost converter and DPT      | 94 |

| Table 5.7 Switching performance comparison between Si IGBT and GaN FET        | 96 |

# **List of Figures**

| Figure 1.1 Typical operating regions of power semiconductor switches [18], [19]                                                |

|--------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Visualization of material property comparison of Si, SiC and GaN [33], [34]                                         |

| Figure 1.3 On-state resistance vs. breakdown voltage indicating theoretical limits for Si, SiC and GaN semiconductor materials |

| Figure 1.4 Definition of semiconductor switching time [45]                                                                     |

| Figure 1.5 Definition of semiconductor switching energy [45]                                                                   |

| Figure 1.6 Basic switching cell topology                                                                                       |

| Figure 1.7 Basic switching cells in power electronic converters                                                                |

| Figure 1.8 DPT dynamic test circuit with inductive load: (a) DUT ON and (b) DUT OFF 16                                         |

| Figure 1.9 Ideal waveforms of double pulse switching test                                                                      |

| Figure 1.10 High-level comparison between (a) conventional and (b) proposed DPT setup 27                                       |

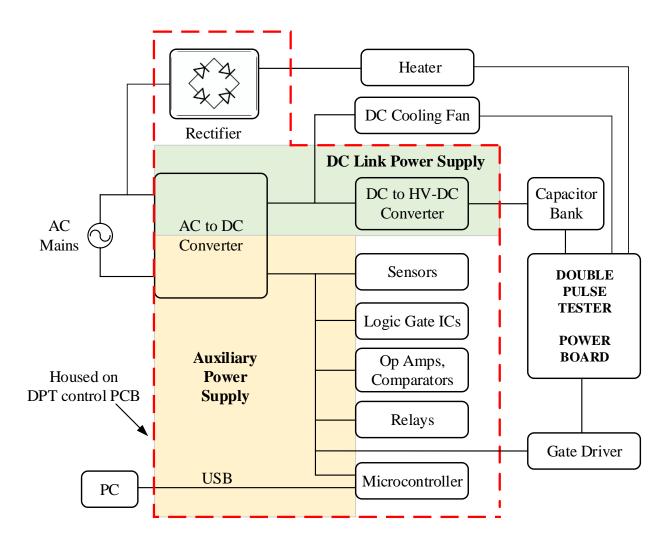

| Figure 2.1 Block diagram of peripheral supporting units in double pulse test bed                                               |

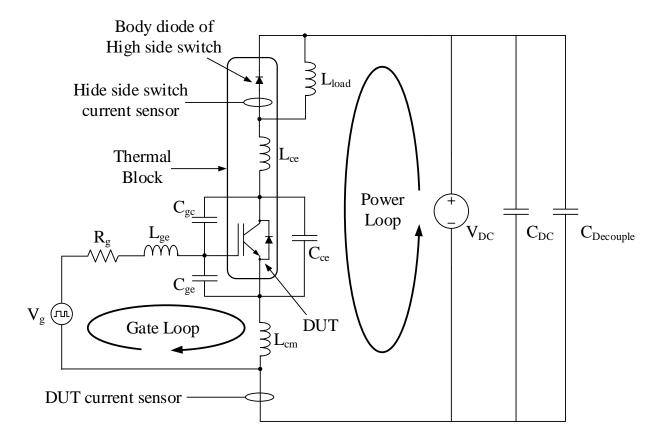

| Figure 2.2 DPT test setup schematic                                                                                            |

| Figure 2.3 Overall design of PSU for proposed DPT                                                                              |

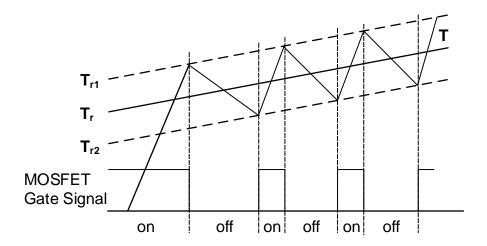

| Figure 2.4 Generation of MOSFET switching signals based on temperature in hysteresis band. 41                                  |

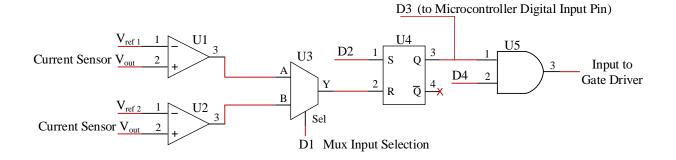

| Figure 2.5 Circuitry for generation of automatic double pulses based on inductor current 43                                    |

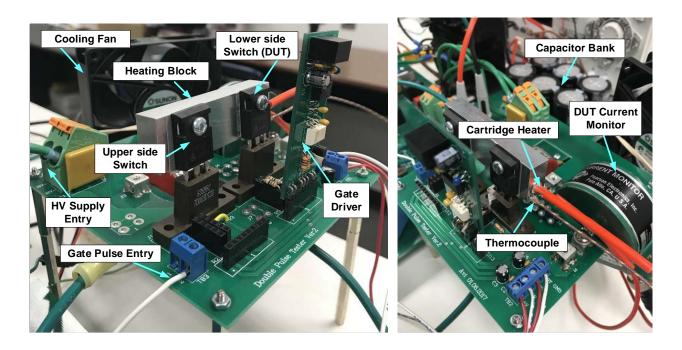

| Figure 2.6 Photos of DPT power board prototype                                                                                 |

| Figure 2.7 DPT test circuit schematic with parasitic elements                                                                  |

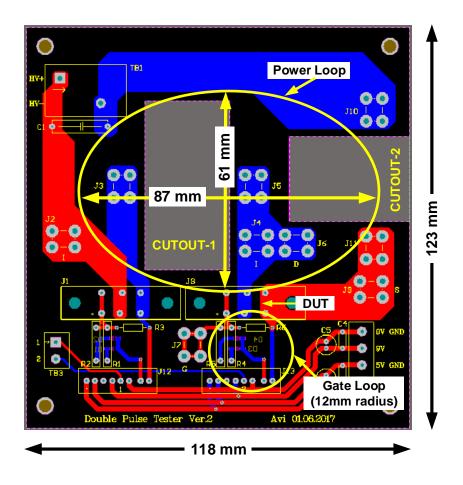

| Figure 2.8 PCB layout of main test circuit – DPT power board                                                                   |

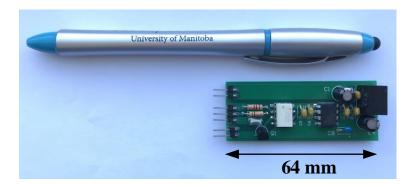

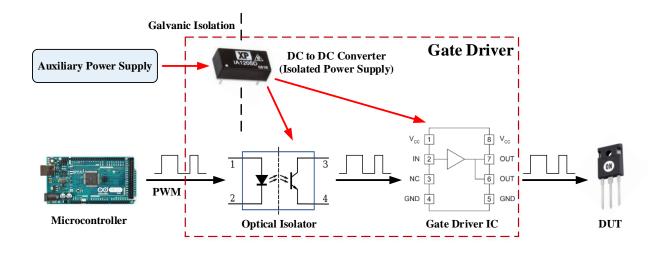

| Figure 2.9 Gate driver for the automatic DPT. 48                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.10 Block diagram showing overall design of DPT gate driver                                                                                                                                                       |

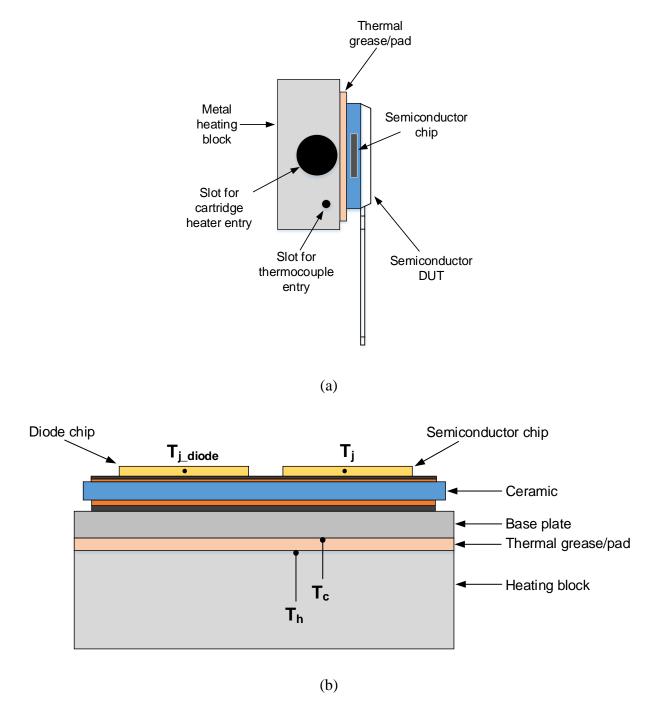

| Figure 2.11 DUT thermal unit arrangement, (a) side-view and (b) cross-sectional view 51                                                                                                                                   |

| Figure 2.12 Image of DPT capacitor bank                                                                                                                                                                                   |

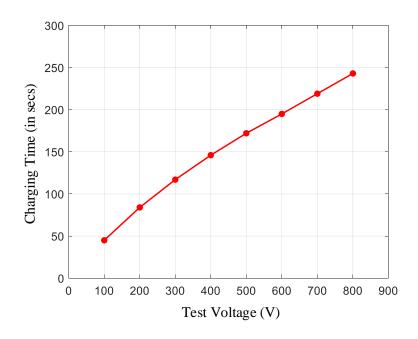

| Figure 2.13 Charging time of capacitor bank as a function of test voltage                                                                                                                                                 |

| Figure 3.1 Graphic User Interface developed for the double pulse test control                                                                                                                                             |

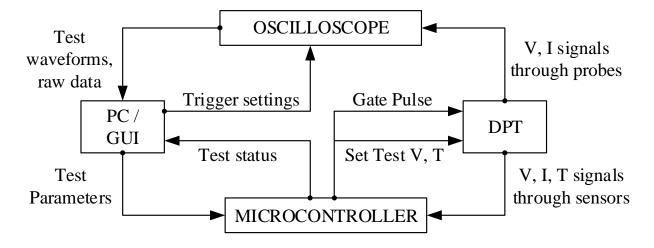

| Figure 3.2 Control block diagram of DPT. 59                                                                                                                                                                               |

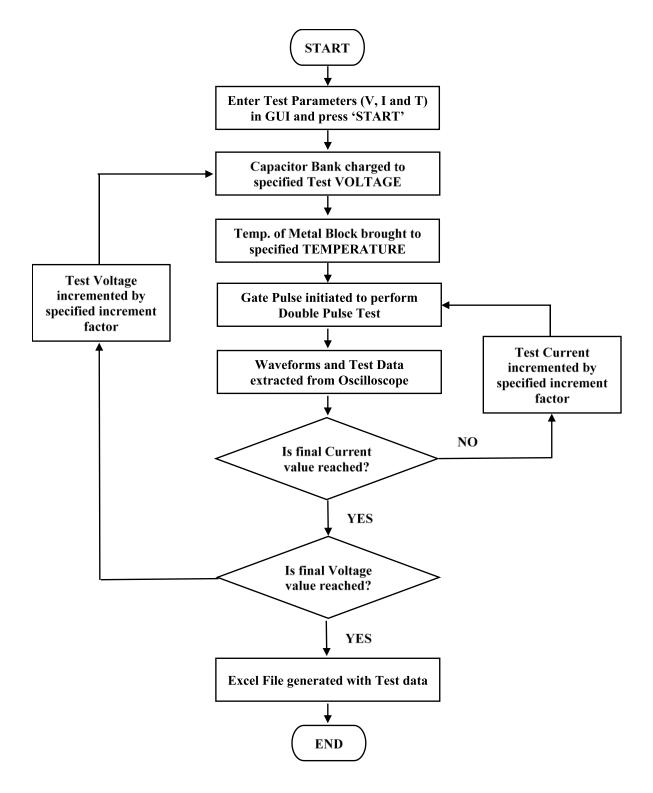

| Figure 3.3 Control flow chart describing operation of DPT                                                                                                                                                                 |

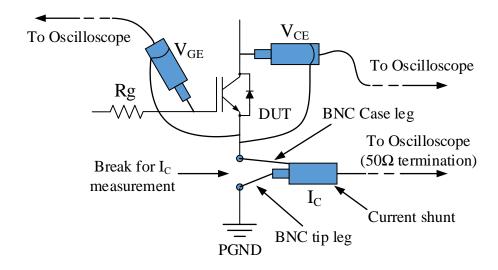

| Figure 4.1 Recommended connection while using passive probes and coaxial current shunt 67                                                                                                                                 |

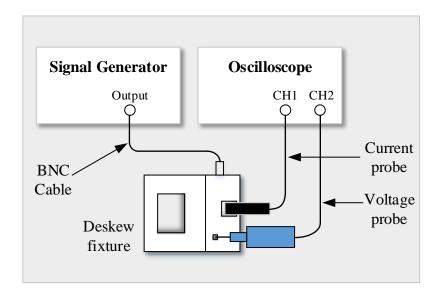

| Figure 4.2 Typical connection for probe deskewing                                                                                                                                                                         |

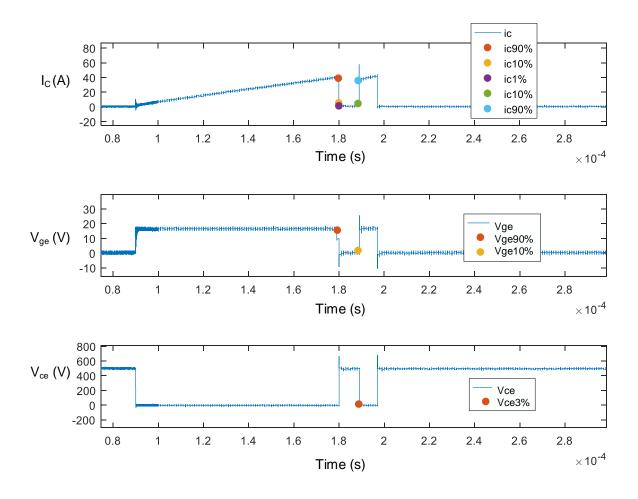

| Figure 4.3 Key points identified on switching waveforms for switching data calculations 72                                                                                                                                |

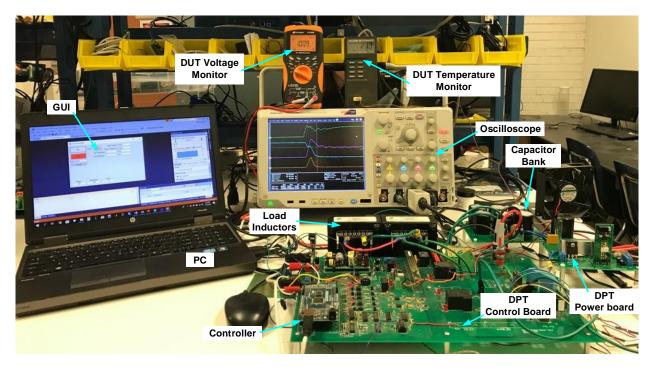

| Figure 5.1 Complete DPT experimental setup                                                                                                                                                                                |

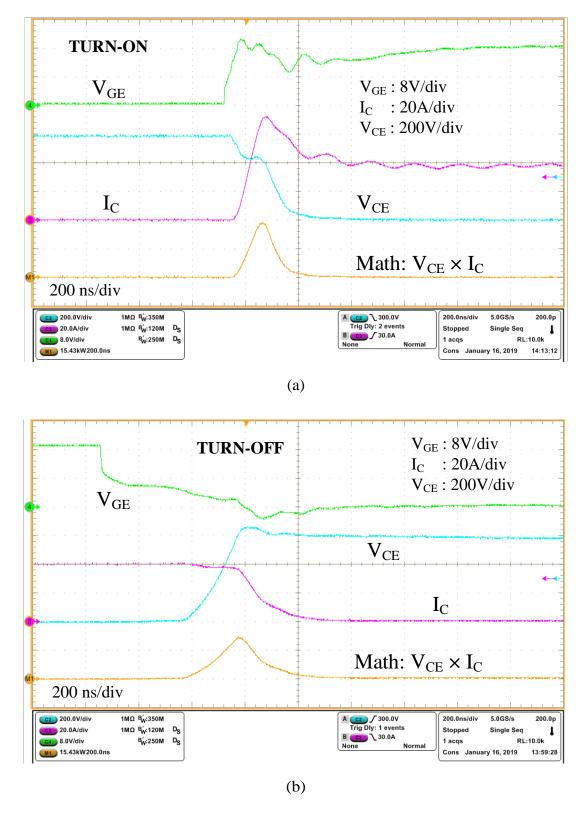

| Figure 5.2 Typical switching performance of DUT with inductive load recorded during double pulse test: (a) Turn-on, (b) Turn-off transient                                                                                |

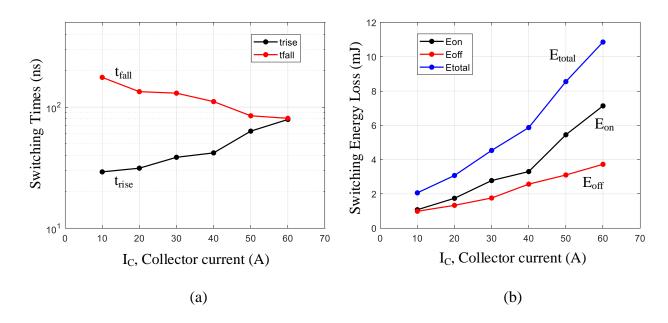

| Figure 5.3 Switching data plotted against collector current: (a) Switching times, (b) Switching Energy Loss; test conditions: V <sub>CE</sub> =600V, T <sub>C</sub> =25°C, Rg=15Ω, V <sub>GE</sub> =0/+15V80              |

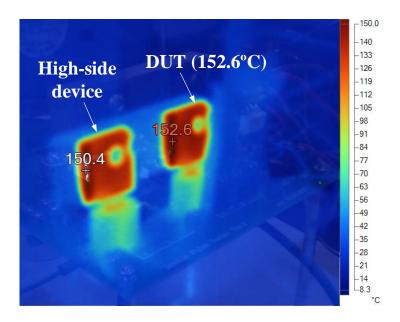

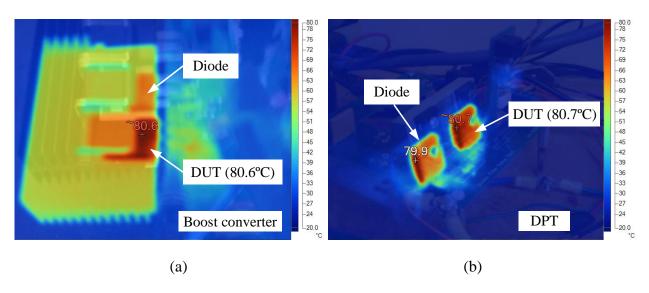

| Figure 5.4 Thermal Image of DUT and high-side device captured during double pulse test, test condition: $VCE = 600\text{V}$ , $IC = 40\text{A}$ , $Rg = 15\Omega$ , $TC = 150^{\circ}\text{C}$ , $VGE = 0/+15\text{V}$ 82 |

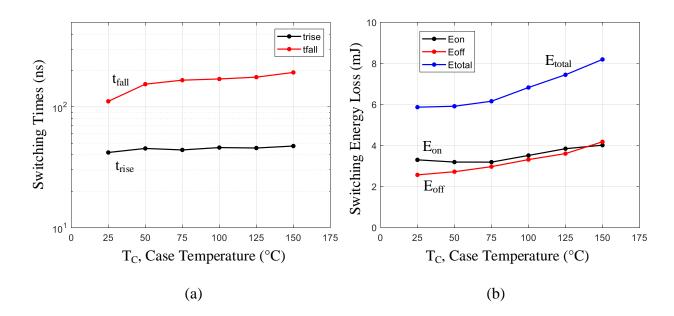

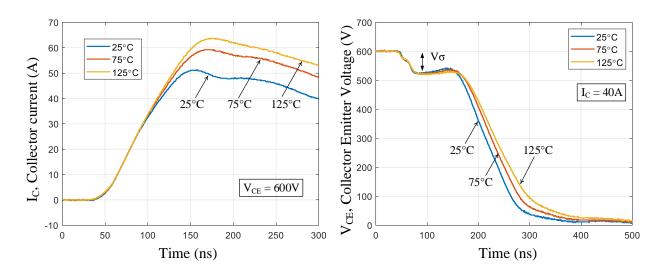

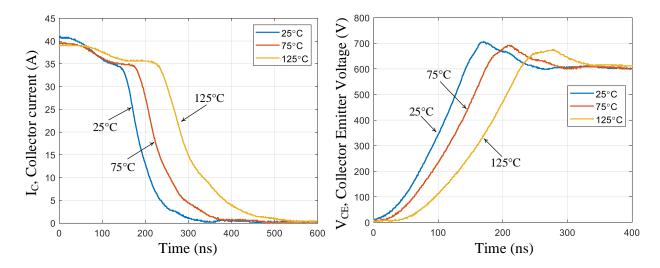

| Figure 5.5 Switching data plotted against collector current: (a) Switching times, (b) Switching Energy Loss, test conditions: $VCE = 600\text{V}$ , $IC = 40\text{A}$ , $Rg = 15\Omega$ , $VGE = 0/+15\text{V}$           |

| Figure 5.6 Switching transient behavior under different case temperatures during DUT turn-on; test conditions: $VCE = 600\text{V}$ , $IC = 40\text{A}$ , $Rg = 15\Omega$ , $VGE = 0/+15\text{V}$                          |

| Figure 5.7 Switching transient behavior under different case temperatures during DUT                                            |

|---------------------------------------------------------------------------------------------------------------------------------|

| turn-off; test conditions: $VCE = 600V$ , $IC = 40A$ , $Rg = 15\Omega$ , $VGE = 0/+15V$                                         |

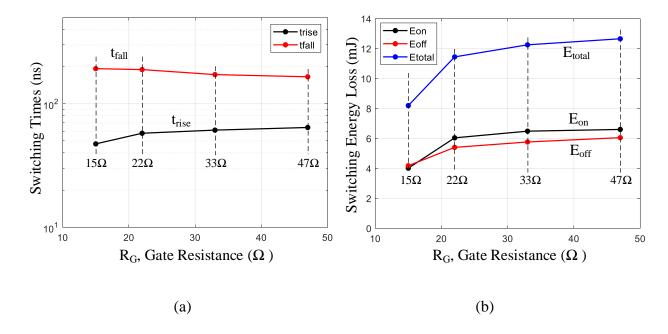

| Figure 5.8 Switching data plotted against gate resistances: (a) Switching times, (b) Switching                                  |

| Energy Losses, test conditions: $VCE = 600\text{V}$ , $IC = 40\text{A}$ , $TC = 150^{\circ}\text{C}$ , $VGE = 0/+15\text{V}$ 8: |

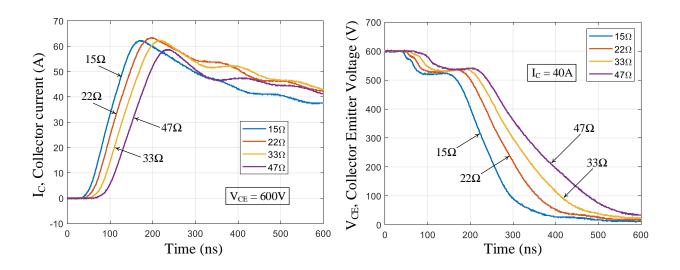

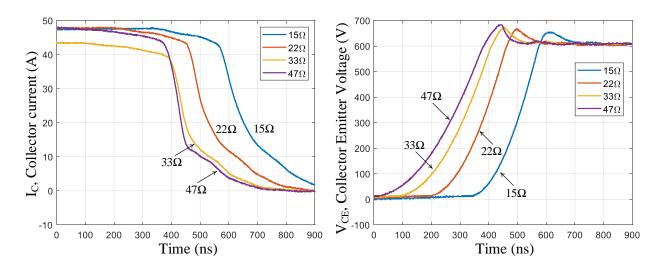

| Figure 5.9 Switching transient behavior under different gate resistances during DUT turn-                                       |

| on; test conditions: $VCE = 600\text{V}$ , $IC = 40\text{A}$ , $TC = 150^{\circ}\text{C}$ , $VGE = 0/+15\text{V}$               |

| Figure 5.10 Switching transient behavior under different gate resistances during DUT turn-                                      |

| off; test conditions: $VCE = 600V$ , $IC = 47A$ , $TC = 150$ °C, $VGE = 0/+15V$                                                 |

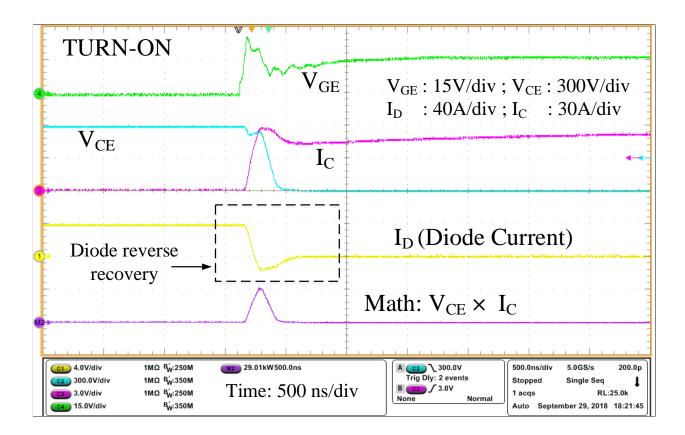

| Figure 5.11 Switching transient behavior during DUT turn-on; test conditions: $VCE = 600V$                                      |

| $IC = 40A, TC = 25$ °C, $Rg = 15\Omega, VGE = 0/+15V$                                                                           |

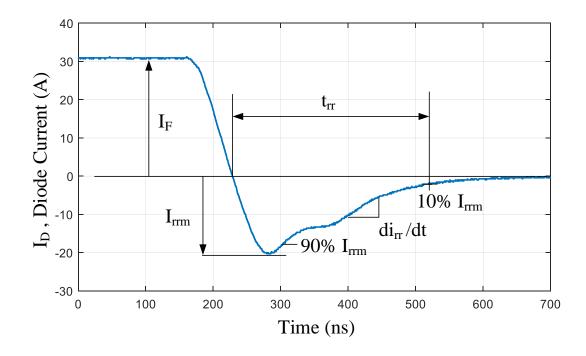

| Figure 5.12 Switching transient characteristics of high side device anti-parallel diode;                                        |

| test conditions: $VCE = 600\text{V}$ , $IC = 35\text{A}$ , $TC = 25^{\circ}\text{C}$ , $Rg = 15\Omega$ , $VGE = 0/+15\text{V}$  |

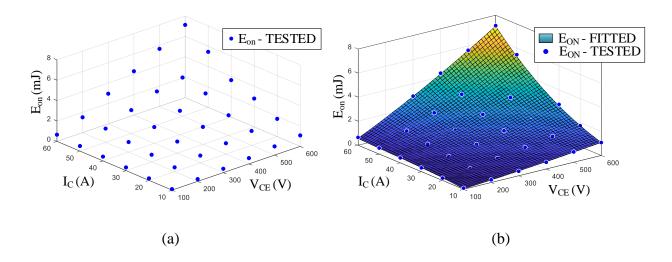

| Figure 5.13 Eon plotted against VCE and IC, (a) Experimental data points, (b) Surface                                           |

| fitted values; test condition $TC = 25$ °C, $Rg = 15\Omega$ , $VGE = 0/+15V$ 9                                                  |

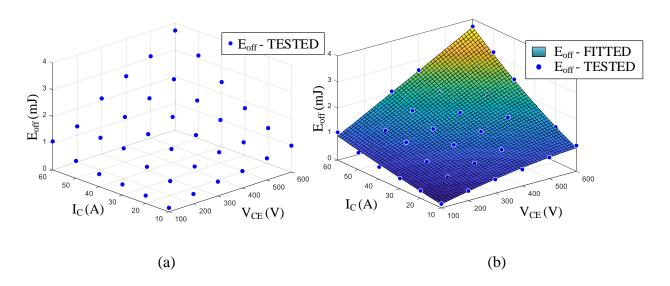

| Figure 5.14 $Eoff$ plotted against $VCE$ and $IC$ , (a) Experimental data points, (b) Surface                                   |

| fitted values; test condition $TC = 25$ °C, $Rg = 15\Omega$ , $VGE = 0/+15V$ 9                                                  |

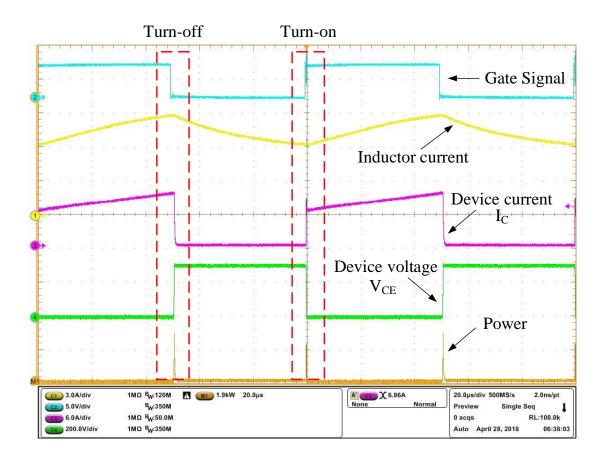

| Figure 5.15 Turn-on and turn-off switching transients in boost converter steady state operation.                                |

| 99                                                                                                                              |

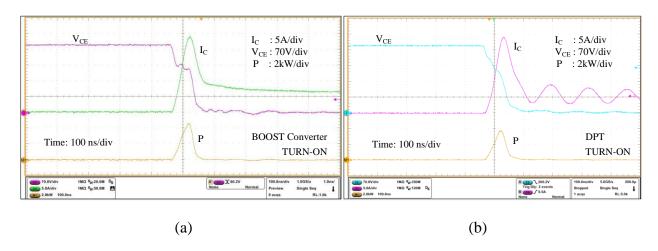

| Figure 5.16 Turn-on switching transient, (a) Boost converter, (b) DPT                                                           |

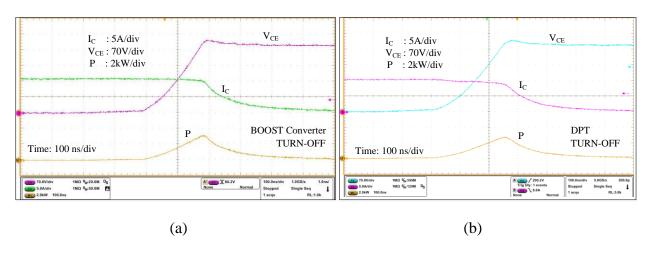

| Figure 5.17 Turn-off switching transient, (a) Boost converter, (b) DPT                                                          |

| Figure 5.18 Thermal image of switching cell, (a) Boost converter, (b) DPT                                                       |

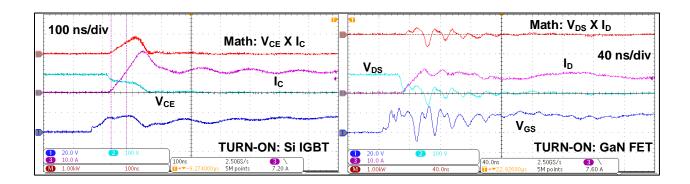

| Figure 5.19 Turn-on performance of Si IGBT and GaN FET at 100V, 10A, $27^{\circ}$ C, Rg = $22\Omega$ 95                         |

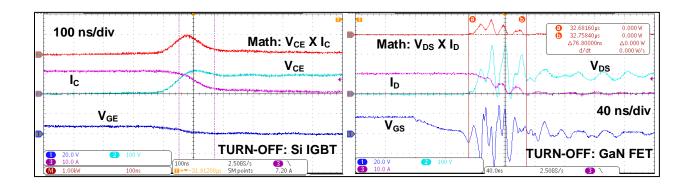

| Figure 5.20 Turn-off performance of Si IGBT and GaN FET at 100V, 10A, 27°C, $Rg = 22\Omega$ 93                                  |

#### **List of Abbreviations**

AC Alternating current

DC Direct current

PE Power Electronic

GTO Gate turn-off thyristor

IEGT Injection-enhanced gate transistor

IGBT Insulated-gate bipolar transistor

FET Field-effect transistor

MOSFET Metal-oxide-semiconductor field-effect transistor

HEMT High-electron-mobility transistor

WBG Wide-bandgap

Si Silicon

SiC Silicon Carbide

GaN Gallium Nitride

DPT Double pulse tester

DUT Device under test

FWD Freewheeling diode

PCB Printed circuit board

EMT Electromagnetic transient

GUI Graphic user interface

SMD Surface mount device

PSU Power supply unit

HV High voltage

DPCU Double pulse control unit

IC Integrated circuit

IDE Integrated development environment

VISA Virtual Instrument Software Architecture

USB Universal Serial Bus

PC Personal computer

PWM Pulse Width Modulation

CVR Current viewing resistor

WAT Waveform Analysis Tool

LUT Lookup table

#### **Chapter 1 Introduction**

#### 1.1 Background

Power Electronic (PE) converters play a significant role in efficient control, conversion and conditioning of electric power in today's energy systems. PE systems are primarily based on switching of power semiconductor devices by applying control signals in order to control the flow of current. The semiconductor devices being the heart of these converters, are one of the key components that determine the efficiency, size, and cost of these PE systems [1]-[7]. With the advent of wide bandgap power semiconductor devices that can be operated at higher switching frequencies, the filter sizes can be reduced leading to improved power density of the PE converters [8]. However, with increased switching frequency, the switching losses become a key contributor of the total converter losses [9],[10]. In the study of power converter optimization, accurate measurement of switching losses is therefore necessary for precise converter loss estimations. Possible techniques for measurement of conduction losses are discussed in [11]. In this thesis, the design and implementation techniques of an advanced device characterization tool for evaluating the switching performance of a semiconductor device has been explored.

The purpose of switching characterization is to study and evaluate the dynamic behavior of a device under various test conditions. The data obtained from the switching tests can greatly facilitate power converters' design regarding the selection of switching frequency, dead time setting, thermal management and efficiency estimation [12]-[14]. A study of the transient behavior of a power device also helps us to predict its dynamic performance in a target application. However, a fast, accurate and reliable testing & measurement system is necessary to capture the high-speed switching transients of a power device. In practice, a Double Pulse Tester (DPT) is

used for this purpose [15]. The DPT is also widely used to tune simulated semiconductor device models to improve possible accuracy so that the models can emulate real devices in terms of overall performance, loss behavior, voltage and current overshoots etc. [16],[17].

#### 1.2 Review of Semiconductor technologies

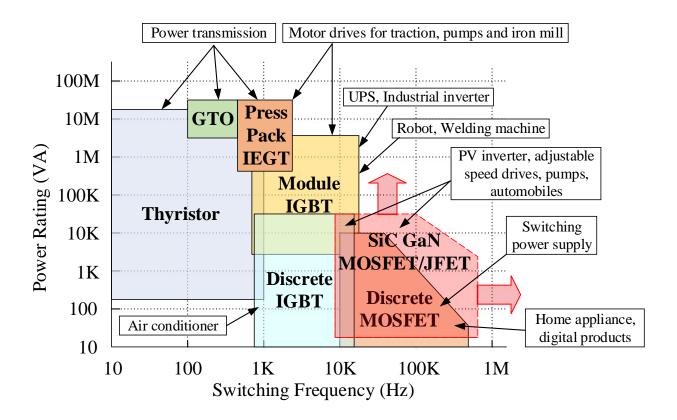

Power semiconductor switches are the heart of any power electronic application. Silicon based power semiconductor devices i.e. diodes, thyristors, IGBTs, MOSFETs have dominated the power electronics and power systems market since the late 1950s. Si IGBTs and MOSFETs still represent the present standard for power switches in typical power applications such as AC/DC, DC/DC supplies, motor drives in low, medium and high power segments. Figure 1.1 depicts the power rating and frequency where the most common power semiconductor devices can operate [18],[19].

Figure 1.1 Typical operating regions of power semiconductor switches [18], [19].

The above plot presents an overall picture on the typical integration of power semiconductors in different industrial areas. The thyristors are used for low frequency, high power applications, IGBTs for medium frequency and power applications, and power MOSFETs for high frequency applications. These devices have undergone continual improvements in their key parameters such as on-state resistance, voltage and current ratings, switching speeds, packages as well as other attributes. However, due to continuous device optimization and improvements in production process, the performance of Si devices are approaching their theoretical limits imposed by its fundamental material properties. The next generation of power electronic systems has to achieve high power density, high efficiency and at the same time has to be cost-effective in terms of production and implementation.

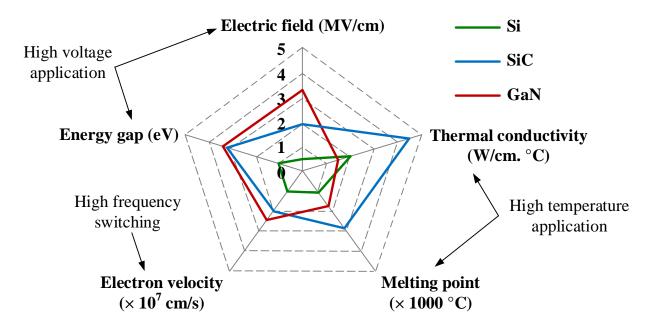

The three major materials used for fabrication of power semiconductor devices are Silicon (Si), Silicon Carbide (SiC) and Gallium Nitride (GaN). The key properties of these materials are compared in Table 1.1 [7], [20]. SiC and GaN, which are categorized as Wide Bandgap (WBG) materials were introduced during the last decade as alternative materials for fabrication of power semiconductors. In recent years, WBG devices especially GaN high-electron-mobility transistor (HEMT) have emerged as promising technology for achieving high frequency, high-density power conversion [21]-[31]. Due to the superior material properties of GaN, it allows system operation at higher voltage, temperature and switching frequency in contrast with the state-of-the-art Si based counterparts [1], [7], [20], [32]. Figure 1.2 is a visual representation of the material property figures of these three popular semiconductor materials and it presents a clear picture of the superiority of WBG materials [33], [34].

Table 1.1 Material properties of Si, SiC and GaN [7], [20]

| Properties                                                      | Si   | SiC  | GaN  |

|-----------------------------------------------------------------|------|------|------|

| Bandgap, $E_g$ (eV)                                             | 1.12 | 3.26 | 3.39 |

| Electric Breakdown/Critical field, $E_{crit}$ (MV/cm)           | 0.3  | 2.0  | 3.3  |

| Saturated electron drift velocity, $V_s$ (10 <sup>7</sup> cm/s) | 1.0  | 2.0  | 2.5  |

| Electron mobility, $\mu_n$ (cm <sup>2</sup> /V.s)               | 1350 | 650  | 2000 |

| Permittivity, $\varepsilon_{\rm r}$                             | 11.8 | 9.7  | 9    |

SiC and GaN are classified as WBG devices because the band gap energy  $E_g$  of these two materials is significantly higher than that of Si, as seen from Table 1.1. The band gap of a semiconductor material reveals the strength of the atomic bonds in its lattice [35]. High band gap in addition to other factors ensure greater lattice structure stability. This is why power semiconductor materials fabricated with these materials tend to have lower leakage current and have the ability to withstand higher operating temperature.

Figure 1.2 Visualization of material property comparison of Si, SiC and GaN [33], [34].

The robust chemical bonds responsible for the wider band gap in WBG devices and other material properties also cause higher critical electric field. The breakdown voltage of a device  $V_{BR}$  can be approximated by the following equation [35].

$$V_{BR} = \frac{1}{2} \cdot w_{drift} \cdot E_{crit} \tag{1.1}$$

Therefore,  $V_{BR}$  is proportional to the width of the drift region,  $w_{drift}$ . For the same breakdown voltage, the drift region in GaN and SiC can be 10 times smaller than Si [35].

The superiority of the material properties of WBG devices with respect to Si devices can be further explained with help of Poison's equation.

$$q \cdot N_D = \frac{\varepsilon_0 \cdot \varepsilon_r \cdot E_{crit}}{w_{drift}} \tag{1.2}$$

In equation 1.2, q is the charge of the electron,  $N_D$  is the total number of electrons in the volume,  $\varepsilon_0$  is the permittivity of vacuum, and  $\varepsilon_r$  is the relative permittivity of a GaN crystal to vacuum. From Table 1.1, it can be seen that the critical field  $E_{crit}$  of GaN is 10 times higher and from equation 1.1, the drift region  $w_{drift}$  is 10 times narrower than Si. By plugging in these two information in equation 1.2, it can be concluded that the number of electrons,  $N_D$  in the drift region can be 100 times greater for WBG devices. This is the reason a significantly better power conversion efficiency can be achieved by SiC and GaN with respect to Si semiconductor devices.

The theoretical on-state resistance  $R_{DS\_ON}$  of a semiconductor device with electron mobility  $\mu_n$  can be expressed as:

$$R_{DS\_ON} = \frac{w_{drift}}{q \cdot u_n \cdot N_D} \tag{1.3}$$

Further combining equations 1.1, 1.2 and 1.3, a relationship between device breakdown voltage and on-state resistance can be derived, which is expressed as:

$$R_{DS\_ON} = \frac{4 \cdot V_{BR}^2}{\varepsilon_0 \cdot \varepsilon_r \cdot \mu_n \cdot (E_{crit})^3}$$

(1.4)

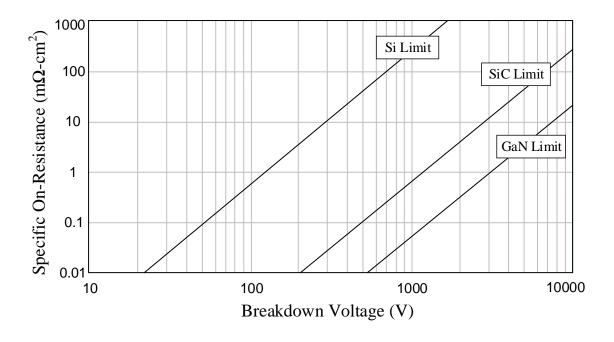

This equation is a clear indication of the fact that devices with high critical field and electron mobility has considerably low on-state resistance. In Figure 1.3, which is a plot based on equation 1.4, the theoretical limits of material properties for Si, SiC and GaN are represented with solid lines. This is one of the popular ways of interpreting the inherent crystal parameters of these materials into a visual reference for comparison of device performance. According to experts, Si solutions have significantly matured and optimized over the last three decades and presently they are in the verge of theoretical limits of its material characteristics. However, a quick glance at Figure 1.3 implies the saturation limit for GaN is far beyond Si and SiC [36]-[38].

Figure 1.3 On-state resistance vs. breakdown voltage indicating theoretical limits for Si, SiC and GaN semiconductor materials.

As compared to Si devices, GaN devices have smaller gate charge and junction capacitors. A faster turn-on, turn-off speed is achieved due to smaller gate charge whereas due to a smaller junction capacitor, relatively less energy is stored during the turn-off period. The switching loss, which occurs due to the current and voltage overlap during the switching transition, is significantly reduced due to these properties. For the same efficiency, GaN devices allow converter operation in much higher frequencies with respect to Si devices. The switching frequency has been continually pushed up to several megahertz that allows reduction in the size of passive components and increase in power density of the system.

Extensive research has been done on performance comparisons between Si and GaN devices [39]. In the recent years, GaN high electron mobility transistor (HEMT) has been commercialized and used in some prototypes of power electronic systems, such as dc-dc converters, power factor correction converters and motor drives [21],[29],[39]-[41]. The performance, size, and cost improvement is significant with use of WBG semiconductors due to lower energy losses and smaller heat sink requirement. Hence, GaN HEMTs have emerged as a promising device for high power density applications [7],[26],[28],[31],[42]. It shows the importance of WBG semiconductor technology for future power electronic applications. However, GaN HEMT being a relatively new semiconductor technology, a lot of information regarding its performance in different application environments is still unknown. Hence, the characterization of switching behavior i.e. measurement of its turn-on and turn-off transients of GaN diodes and HEMTs is an ongoing study in both academia and industry.

The development of power semiconductor technology has led to great improvement in power handling capabilities and switching speed of power devices [43]. Despite its limitations, Si

technologies have proved adaptable and still used in a mass scale by industries around the globe due to their minimal cost, ease of implementation and relatively simpler control techniques.

#### 1.3 Semiconductor characterization

The typical electrical characterization tests performed on a power semiconductor device can be broadly classified into static and dynamic tests. The purpose of static I-V (current-voltage) characterization is to understand the steady-state behavior of a device under certain operating parameters, such as gate voltage, device voltage and current. The junction temperature greatly affects the I-V characteristics of a device. If the device is continuously kept switched on to evaluate the static on-state behavior, the conduction losses may alter the junction temperature thereby affecting the test results. Hence, pulsed I-V test is performed to ensure the test conditions remain unchanged in the temporary on-state period. A curve tracer is typically used to perform pulsed static characterization tests in order to determine several device parameters such as on-state resistance, maximum current capability, leakage current, device breakdown voltage, saturation voltage, transconductance, capacitance etc. Curve tracers are available for purchase from test equipment manufacturers such as Tektronix and Keysight. Some popular models are 370 series curve tracers from Tektronix and B1500 series Semiconductor Device Analyzers from Keysight. The device setup and measurement techniques for static characterization are elaborately discussed in [44].

The dynamic switching characterization of power semiconductor devices gives us insight into the switching behavior of the device under various test conditions. The switching performance of a device changes with the operating voltage, current, junction temperature and the value of gate drive resistances. In a switching characterization test, these parameters are mainly regulated and the transient performance during switching of the device under test (DUT) is observed in an

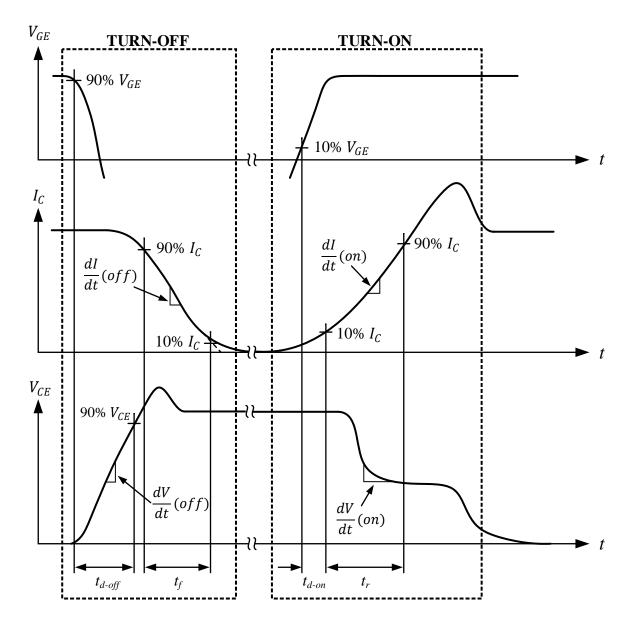

oscilloscope. In this thesis, the terminologies of an IGBT is used in the text and figures however, the same concept applies for other semiconductor devices. One can gain useful information on several key parameters of the DUT such as Current rise/fall gradient (di/dt), Voltage rise/fall gradient (dv/dt), rise time  $(t_{rise})$ , fall time  $(t_{fall})$ , turn-on switching energy loss  $(E_{on})$  and turn-off switching energy losses  $(E_{off})$  etc. after analysing the collector-emitter voltage  $(V_{CE})$ , collector current  $(I_C)$  and gate voltage  $(V_{GE})$  waveforms captured during the switching tests. The definition of the above-mentioned DUT switching parameters are discussed in the following sections and illustrated with Figure 1.4 and Figure 1.5.

#### 1.3.1 Turn-on Characteristics

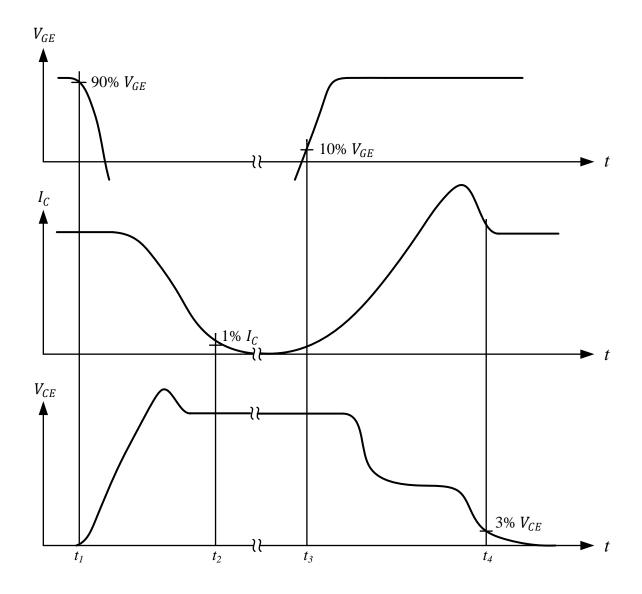

The key switching parameters of a device obtained from dynamic characterization tests are labelled in Figure 1.4 and Figure 1.5. In this section, the parameters are further defined and their implications on power electronic application, mainly converter design are discussed. These definitions are in accordance with JEDEC standard JESD24-1 which states the method for measurement of power device turn-off switching loss [45].

- 1) Current Rise Time ( $t_{rise}$ ): It is the time taken by  $I_C$  to rise from 10% to 90% of the nominal current. This parameter is an indication of how quickly the collector current approaches the load current. It contributes to the total turn-on time and partially determines the maximum allowable switching frequency for the device.

- 2) Turn-on Delay Time  $(t_{d-on})$ : The time interval from  $V_{GE}$  rising to 10% of the nominal gate voltage to  $I_C$  rising to 10% of its nominal value is  $t_{d-on}$ . A measure of  $t_{d-on}$  indicates how fast the device can be turned on and its reaction time from the application of gate pulse. It

is part of the device's total turn-on time and determines the maximum switching frequency the device can handle safely.

- 3) Turn-on Switching Current Gradient  $(di/dt_{(on)})$  and Voltage Gradient  $(dv/dt_{(on)})$ : The turn-on switching current gradient  $di/dt_{(on)}$  is the slope of  $I_C$  during its rising edge, measured typically at 50% of the nominal current. Whereas,  $dv/dt_{(on)}$  is the slope of the falling edge of  $V_{CE}$ , measured at 50% of the nominal voltage. The gradient values indicate the switching speed of the device and these parameters are key contributor of parasitic ringing and EMI in a device switching process.

- 4) Turn-on Switching Energy Loss ( $E_{on}$ ): The Turn-on Energy loss is the integral of the instantaneous product of  $I_C$  and  $V_{CE}$  within the time interval of  $t_3$  and  $t_4$  in Figure 1.5.  $t_3$  marks the time when the rising edge of  $V_{GE}$  hits 10% of its nominal value and  $t_4$  is the time when the falling edge of  $V_{CE}$  reaches 3% of its nominal value.  $E_{on}$  can be mathematically expressed with equation 1.5.  $E_{on}$  partially contributes to the total switching losses of a device and is typically one of the largest source of losses in a high frequency converter application.

$$E_{on} = \int_{t_2}^{t_4} V_{CE} \times I_C \times dt \tag{1.5}$$

Figure 1.4 Definition of semiconductor switching time [45].

#### 1.3.2 Turn-off Characteristics

In this section, the key switching parameters that represents a device's turn-off characteristics are discussed in details. These parameters are also labelled in Figure 1.4 and Figure 1.5.

1) Current Fall Time  $(t_{fall})$ : It is the time taken by  $I_C$  to fall from 90% to 10% of the nominal current. This parameter is an indication of how quickly the collector current can become

zero. It contributes to the total turn-off time and partially limits the maximum allowable switching frequency for the device.

- 2) Turn-off Delay Time  $(t_{d-off})$ : The time interval from  $V_{GE}$  dropping to 90% of the nominal gate voltage to  $V_{CE}$  rising to 90% of its nominal value is  $t_{d-off}$ . A measure of  $t_{d-off}$  specifies the response time of the device turning off with withdrawal of gate drive pulse. It is part of the device's total turn-off time and a key factor in determining the maximum allowable switching frequency.

- 3) Turn-off Switching Current Gradient  $(di/dt_{(off)})$  and Voltage Gradient  $(dv/dt_{(off)})$ : The turn-off switching current gradient  $di/dt_{(off)}$  is the slope of  $I_C$  during its falling edge, measured typically at 50% of the nominal current. Whereas,  $dv/dt_{(off)}$  is the slope of the rising edge of  $V_{CE}$ , measurement at 50% of the nominal voltage. The gradient values indicate the switching speed of the device and these parameters are key contributor of parasitic ringing and EMI in a device switching process.

- 4) Turn-off Switching Energy Loss ( $E_{off}$ ): The Turn-off Energy loss is the integral of the instantaneous product of  $V_{CE}$  and  $I_C$  within the time interval of  $t_1$  and  $t_2$  in Figure 1.5.  $t_1$  marks the time when the falling edge of  $V_{GE}$  hits 90% of its nominal value and  $t_2$  is the time when the falling edge of  $I_C$  reaches 1% of its nominal value.  $E_{off}$  can be mathematically expressed with equation 1.6.  $E_{off}$  in addition with  $E_{on}$  constitutes the total switching losses of a power semiconductor device and is typically one of the largest source of losses in a high frequency converter application.

$$E_{off} = \int_{t_1}^{t_2} V_{CE} \times I_C \times dt \tag{1.6}$$

Figure 1.5 Definition of semiconductor switching energy [45].

With these data in hand, a power electronic designer can quantify the switching performance of power semiconductor devices and select a right device for a particular PE converter design. In a nutshell, the switching results act as a guideline for selection of switching frequency and dead time, choice of thermal management and efficiency estimation for PE applications.

#### 1.4 Semiconductors in converters

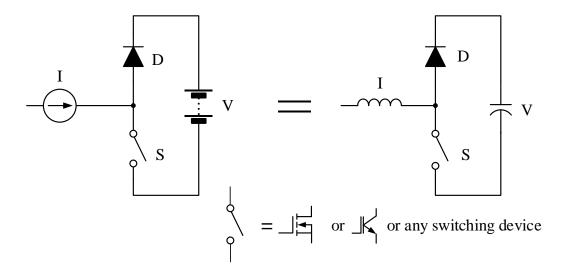

The fundamental structure of modern power electronic converters is a Switching Block/Cell. As seen in Figure 1.6, a basic switching cell includes a diode (D), semiconductor switch (S), current source (I) and voltage source (V). In most cases, the current source is an inductor and the voltage source is a capacitor. The semiconductor switch, which can be a MOSFET, IGBT or any other switching device, is typically paired with a diode to provide current commutation during the switching process in hard switching conditions.

Figure 1.6 Basic switching cell topology.

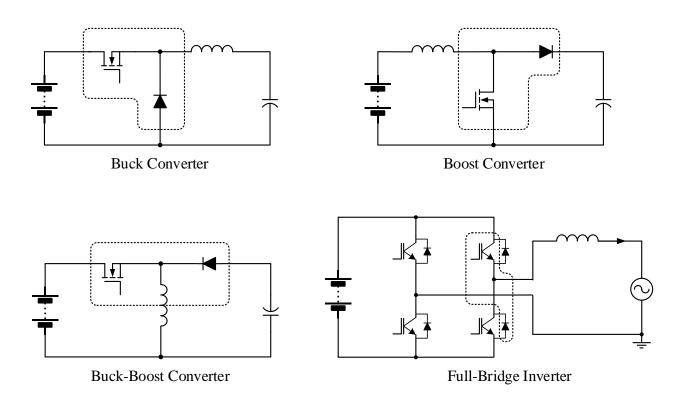

Based on the position of the switching device in a typical switching cell, the cell can be configured as two basic structures, P-cell and N-cell. For a P-cell, the switching device is connected to the positive terminal of the voltage source whereas in an N-cell it is connected to the negative terminal of the voltage source or capacitor [46], [47]. In all modern power electronic converters, at least one switching cell can be found. The switching cells present in the classical dc-dc converters i.e. buck, boost and buck-boost as well as an inverter are identified in Figure 1.7. Each of these topologies can be represented with P-cell and N-cell circuits and discussed elaborately in [47].

However, for inverters it is not always straightforward to identify a switching cell because the diode is in parallel with another switch and the inductor is shared by multiple switching cells.

Figure 1.7 Basic switching cells in power electronic converters.

The behavior of the switching device affect the switching performance of the diode, and the operational behavior of the diode reflect back to the switching device. Since their dynamic behaviors are interrelated, it is useful to define a switching cell for estimating switching and conduction losses in a converter. The study of the switching cell reveals the comprehensive switching behavior of the devices concerned.

#### 1.5 Overview of Double Pulse Tester

#### 1.5.1 Basic Topology

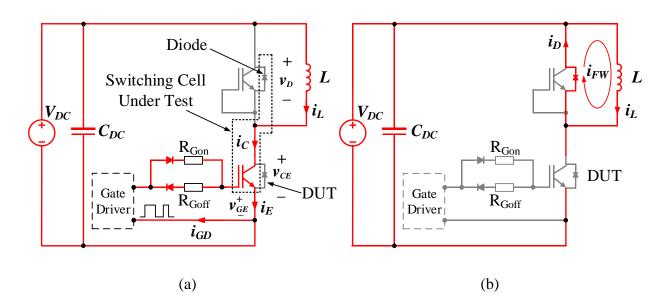

A common application of a power semiconductor device is clamped inductive switching [15],[48],[49]. Since a Double pulse tester (DPT) emulates this typical application, it is a widely accepted test system to evaluate the dynamic performance of a switching cell. The DPT test circuit shown in Figure 1.8 closely represents a phase-leg of voltage source converter. The semiconductor device under test (DUT) is tested as a lower side device along with a freewheeling diode (FWD) as the upper (high) side device. Many a times, discrete IGBTs or MOSFETs with anti-parallel diode are used in both positions, where the anti-parallel/body diode of the upper side device plays the role of a FWD and the low side device is the DUT for the switching test.

Figure 1.8 DPT dynamic test circuit with inductive load: (a) DUT ON and (b) DUT OFF.

An N-cell configuration is typically chosen for the test circuit because placing the DUT in the lower side simplifies the gate drive circuit due to ground referenced gate signal. The converter circuit is relatively immune to supply noise and gate drive noises in a ground referenced gate drive circuit.

Table 1.2 Definition of parameters used in Figure 1.8 and Figure 1.9

| Parameter         | Description                   | Parameter         | Description                   |

|-------------------|-------------------------------|-------------------|-------------------------------|

| $V_{DC}$          | High Voltage DC Supply        | $C_{DC}$          | DC link capacitor             |

| $v_D$             | Voltage across diode          | L                 | Load inductor                 |

| $v_{\it CE}$      | DUT collector-emitter voltage | R <sub>Gon</sub>  | DUT Turn-on gate resistance   |

| $v_{\mathit{GE}}$ | DUT gate-emitter voltage      | RGoff             | DUT Turn-off gate resistance  |

| $i_C$             | DUT Collector current         | $i_L$             | Current through load inductor |

| $i_E$             | DUT Emitter current           | $i_D$             | Current through diode         |

| $i_{GD}$          | Current through gate driver   | $i_{FW}$          | Freewheeling current          |

| V <sub>TEST</sub> | Test voltage                  | I <sub>TEST</sub> | Test current                  |

#### 1.5.2 Principles of Operation

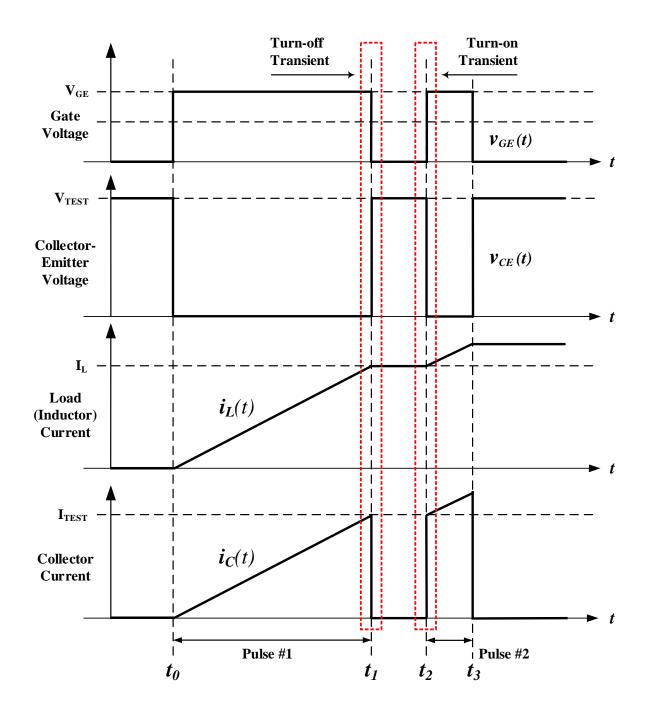

The operating principle of the DPT system in Figure 1.8 can be briefly described with the aid of characteristic switching waveforms in Figure 1.9. The figure shows the waveforms of interest i.e. the gate voltage, collector-emitter voltage, load current and collector current under double pulse operation. Two pulses with a delay time between them are sent to the gate of DUT through a suitable gate driver. At time  $t_0$ , the first pulse turns 'on' the DUT and it is held on until  $I_C$  reaches the desired test current level. At time  $t_1$ , the gate pulse is shut off and the turn-off switching characteristics of the DUT are captured. From time  $t_1$  to  $t_2$ , the DUT is held off and this is when the inductor current  $I_L$  retreats from the DUT path and flows through the upper side diode creating a freewheeling current. The delay time between the two pulses i.e. the freewheeling time should be long enough to damp out the parasitic ringing in  $V_{CE}$  and  $I_C$  before the DUT is switched on again. However, it is short enough to keep the inductor current fairly constant in this period. The

choice of high load inductance also ensures  $I_C$  does not drop considerably. At time  $t_2$ , the second gate pulse turns the DUT on again and this time the turn-on characteristics of the DUT are recorded. The switching on of the DUT causes the FWD to undergo reverse recovery. At this time, both the reverse recovery current and the inductor current flow through the DUT. In practical testing scenarios, an overshoot is noticed in the device current  $I_C$  during this process. The time interval  $t_2$  to  $t_3$  is kept long enough for any possible switching ringing to subside and short enough to ensure  $I_C$  stays within the device's safe operating limits. At time  $t_3$ , the gate is forced low and the device is turned 'off'. This process is repeated under different test conditions, in this way the device does not heat up and the characterization can be performed under desired and controlled junction temperature condition.

The device voltage and current waveforms are measured using a high bandwidth high voltage probe and current monitor respectively. The specifications of the probes used for the testing as well as factors behind the choice of instrumentation for DPT is elaborately discussed in Chapter 4. The raw test data for all necessary channels that represent the switching waveforms are then extracted from the oscilloscope to a PC for further processing and analysis. Multiple tests are performed on a particular DUT with different gate resistances at different voltage, current and temperature levels to derive its typical switching curves. In order to control the *di/dt* and *dv/dt* of the DUT, the gate resistances (turn-on and turn-off) are kept adjustable for limiting the current responsible for charging up the input capacitance of the DUT.

Figure 1.9 Ideal waveforms of double pulse switching test.

#### 1.6 Literature Review

A double pulse test is a widely accepted method for switching performance evaluation of power semiconductor devices. Unlike static characterization, which is performed by industrial grade test equipments such as curve tracers/semiconductor device analyzers, there is no such commercially

available instrumentation from test equipment manufacturers for dynamic switching characterization. Industries and academia customize and design their own DPT setups based on the technical resources available to them and also considering the type of device to be tested. Some of the DPT setups mentioned in technical literatures are briefly discussed in this section.

In technical literature [50], the design principles and PCB design recommendations for implementing a double pulse test prototype to investigate the switching behavior of SiC MOSFET (Cree's C2M0080120D) in a TO-247 package are described. The literature highlights the different parasitic element associated with the DPT circuit and presents the effect of these parasitic components on the DUT switching characteristics through simulation results. For the hardware implementation stage, it discusses the circuit layout techniques adopted to minimise effect of parasitic elements on the switching characterization results.

A relatively broader picture of the dynamic characterization test process is presented in [51] and some of the key topics of a DPT, including components and layout design, instrumentation selection criteria, considerations during measurement, grounding effects as well as data processing are discussed. The authors provide an overview of the entire double pulse test process and the setup identifying the key components involved and their individual functions. The design criteria of main DPT components such as load inductor and DC capacitor bank are described. The power stage and gate driver circuitries are separated and modularized to allow DPT testing regardless of specific topologies. Like most of the literatures in this domain, this paper also highlights the importance of parasitic impedance minimization in PCB layouts to obtain test results that are genuine representation of the DUT's switching performance. Thereafter, the authors discuss the latest voltage and current measurement techniques for DPT as well as list the latest high bandwidth probes that can capture the high-speed switching transients during the test with adequate fidelity.

Experimental results are shown for double pulse tests conducted on a phase-leg module built with 1200V/500A SiC MOSFET and SiC Schottky diode. The authors also propose a method for switching loss evaluation of WBG devices in phase-leg configuration.

The switching characteristics of a WBG based 1200V, 35A SiC MOSFET in [15]. In this literature, the authors provide a brief description of the double pulse test process followed by presentation of simulation and experimental results. Simulation of double pulse circuit is performed in LT-Spice simulation platform and both turn-on and turn-off switching characteristics are presented in addition to a table of switching loss figures for different test conditions. The DPT hardware is realized with a six layer PCB consisting of SiC MOSFETS, DC filter capacitors, gate driver and an eight bit PIC microcontroller. Some key attributes of the gate driver design and component selection are presented. The authors also study the temperature dependent switching behavior by attaching the DUT to a hot plate. Finally, the DPT results are analysed to highlight the superiority of WBG devices.

A different approach is taken in [52] for designing a Multifunctional DPT for Cascode GaN Devices. The authors propose a tester that builds on a conventional DPT but is capable of carrying out the double pulse test and diode reverse recovery characterization on the same board without the need for moving the DUT from one setup to another. The tester is able to characterize device turn-on and turn-off transition like a conventional tester but in addition, it is also capable of measure the dynamic on-state resistance of the GaN devices in both hard and soft switching conditions (with use of additional zero-voltage transition circuitry for soft switching). Like other literatures, this work also specifies the importance of a compact PCB layout for DPT with a focus of keeping the parasitic inductance of the gate loop and high-frequency power loop to the lowest level possible. This will limit the chances of gate voltage ringing, unwanted triggering of the device

and overshoot on device voltage. The authors uses a finite-element analysis (FEA) tool, ANSYS Q3D package to extract and quantify the loop inductances and parasitic capacitances in the PCB layout. The functions of the proposed tester are validated with tests on a cascade GaN device.

A conventional DPT i.e. a clamped inductive switching circuit is implemented in [48] to test a 600V normally-off GaN-on-Si transistor. A test bench is constructed to house the DPT circuit, oscilloscope, high-voltage source, pulse generator and auxiliary unit with a computer controlling the entire setup. The test bench is made of plastic to avoid any parasitic capacitive coupling path. The device temperature is controlled with air flow around the device and monitored using an infrared thermometer. The paper also discusses techniques for measurement of gate charge and on-state resistance. The results obtained from the double pulse measurements is used as a basis to design a GaN based DC/DC converter.

Both static and switching characterization of a SiC JFET and SiC MOSFET device are covered in [53]. As a common practise, the author chooses the double pulse test circuit for the switching characterization because switching under clamped inductive load is the most common commutation mode for power devices in a pulse width modulated, hard-switching type converter. The ideal MOSFET switching behavior is studied along with a discussion on the effect of non-idealities on the high-speed switching waveforms. From the description of the DPT setup, it is noted that the double pulse signals are generated using an Agilent waveform generator and the test setup is powered by external power supply units. The test setup does not include any thermal system to conduct characterization tests under different temperatures. It requires manual configuration of the test equipments for each test condition. Finally, the characterization result is compared with simulation results in order to comment on the accuracy of the spice models.

There are some double pulse evaluation boards commercially available from semiconductor device manufacturers. EVAL-IGBT-650V-TO247-4 [54] from Infineon is an evaluation board for 1200V IGBTs in TO-247 packages, and with either three or four leads. It allows double pulse tests for switching voltages and currents upto 650V and 150A respectively. The board consists of the capacitor bank, load inductor and has connectors for external connection of signal generators, high voltage and auxiliary power supplies. The presence of probe tip adaptors facilitate easy connection of probes. A heat sink is connected to the DUT for temperature dependent dynamic testing. Moreover, this board can be configured as step-down or step-up DC/DC converter and used in continuous operation due to the basic phase-leg topology. This evaluation board is presently listed for sale in Mouser Electronics website for a unit price of \$884.75.

GA100SBJT12-FR4 [55] from GeneSiC Semiconductor is a Double Pulse Switching board designed for performing switching tests on Si and SiC power transistors. The board is capable of testing devices upto 1200V and 100A. The board comes with a capacitor bank comprised of twenty 1μF, 630V capacitors and connection pads for external component connection. The DUT, freewheeling diode, external inductor and gate driver have to be soldered directly on to the board by an user. This evaluation board does not provide any provision for DUT case temperature adjustment. Like most of the conventional setups, the high voltage has to be supplied to the test board from an external power supply through a coaxial connection. This evaluation board is presently listed for sale in Mouser Electronics website for a unit price of \$388.72 but for a minimum order quantity of 25 boards.

PGA26E07BA-SWEVB008 (~800W) and PGA26E19BA-SWEVB008 (~400W) [56] from Panasonic Semiconductor Solutions Co., Ltd. are half-bridge evaluation boards for evaluating the switching characteristics of Panasonic make X-GaN power transistors. The maximum DC input

voltage is 410V. The board consists of X-GaN Power Transistors in SMD package, Gate Driver IC and general purpose Half Bridge Isolator. This evaluation board offers a platform for testing and developing power circuits using only Panasonic make X-GaN devices. It has to be accompanied by external DC power supply units and Pulse generator for double pulse testing and does not come with any provision for adjusting DUT case temperature. The board supports continuous power supply test depending on the thermal design. This board can be used as a reference design for PCB layout and gate driver circuit. However, it cannot be considered as an universal setup for testing devices of different specification and packages. The evaluation board is listed in mouser electronics for an unit price of \$585.12.

An application note available online from CREE [57] describes the design principles of a SiC MOSFET Double Pulse Fixture. The test fixture contains a test socket for the DUT, gate driver, capacitor bank, freewheeling diode and a tightly integrated two stage current transformer. This document is mainly focused on the design considerations of the double pulse test power circuit and gate driver. It shows the tester schematic, photos, PCB layout, bill of materials, test waveforms and provides recommendation for distortion-free measurement of switching waveforms for SiC devices. However, this test fixture is not commercially available from the manufacturer and not listed in any electronic component distributors' website.

GS66508T/GS66516T-EVBDB [58] evaluation board from GaN Systems Inc. includes 650V GaN Enhancement-mode HEMTs (E-HEMTs), half-bridge gate drivers, isolated power supplies and optional heatsink to form a continuously operated half bridge power stage. As other evaluation boards mentioned earlier, this serves as a reference design for the main DPT power board for the latest low-footprint, surface mount GaN devices. The two GaN devices along with their gate drive circuitries are implemented in a daughter board, which can be plugged into a universal mother

board GS665MB-EVB (sold separately). The mother board consist of connection pads for external load inductor connection, high voltage DC and auxiliary power supply units connection and a PWM control & dead time circuit. Provision is kept for attaching a heat sink with the switching devices in the daughter board but no such thermal arrangement is provided that allows temperature adjustment.

All the evaluation boards listed above consist the main half-bridge power stage, which represent the main DPT power circuit. These boards are designed by power semiconductor device manufacturers, hence can serve as a good reference while designing the power and gate drive circuit layout for testing the latest WBG semiconductors. However, the power board is only one of the key components amidst the several test elements involved in the overall double pulse testing process. These boards have to be accompanied with additional support equipments to conduct the double pulse testing. To the best of the author's knowledge, a complete DPT solution that can cover testing, recording and data processing aspects of switching characterization is not yet available from the test equipment manufacturing industry.

#### 1.7 Motivation of the Thesis

A typical datasheet of a power semiconductor switch provides switching results for a particular test condition. However, the operating condition of a device in a real life target application may be different from the datasheet specified test condition. In this scenario, a designer requires a fully equipped dynamic test bench to conduct the switching test in a desired test condition. A DPT is a widely used setup for evaluating the switching behavior of power semiconductor devices. For conventional DPTs, the test control and data processing operations are done manually. However, it is a tedious, time-intensive process to perform these tests under different permutations of test parameters and thereafter analyze the experimental data manually. Although the switching event

occurs in fraction of a second, manually setting up the test bed multiple times for each test conditions, extracting the post-test raw data and thereafter processing the raw data to obtain switching characteristics involve considerable amount of time and effort. An automatic test control and data processing system needs to be developed to minimize user interaction in the overall test process.

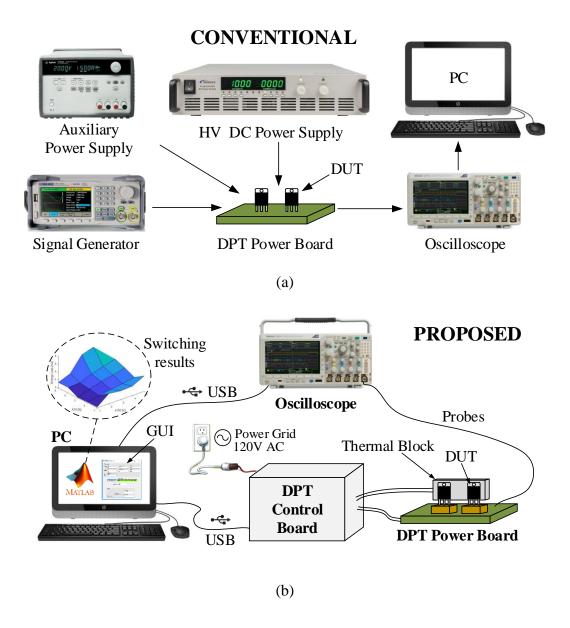

Moreover, conventional manually operated DPT systems, as discussed in Section 1.5, are expensive and consume substantial bench space due to involvement of several peripheral support equipments such as signal generators and bulky power supply units (PSU). To make the overall dynamic characterization setup compact and economic, the peripheral equipments need to be replaced with alternate solutions but to perform the same functions.

As mentioned in section 1.5, only DPT evaluation power boards are commercially available from semiconductor device manufacturers. A complete DPT solution is required that covers testing, recording and data processing aspects of switching characterization. However, to the best of the authors' knowledge, presently there is no such complete DPT system commercially available from any test equipment manufacturers. In view of the above discussion, an innovative DPT solution is proposed. Figure 1.10 shows a comparison between conventional and proposed DPT setup.

Figure 1.10 High-level comparison between (a) conventional and (b) proposed DPT setup.

To summarize, the motivation of this thesis is to develop a compact, cost-effective, fully automated, universal test platform for dynamic characterization of power semiconductor devices. It will also be a complete DPT solution for monitoring, measurement, recording and processing the switching data. The switching loss data obtained using this testing system can be used to generate switching time and loss databases for widely used semiconductor devices. These databases can be linked with simulation platforms to obtain more practical simulation results. It

will help engineers to create, optimize and validate power semiconductor devices models in power electronic simulation platforms such as PLECS and power system electromagnetic transient (EMT) simulation software like PSCAD etc. Due to availability of switching data with variation of operating temperature, thermal models can be developed. The thermal simulation results can provide information on converter loss and increase in device junction temperature. These results will greatly facilitate an user with heat sink design for a particular application since these information cannot be obtained easily from a typical datasheet.

#### **Research Objective**

The proposed research work is focused on integrating power electronics, control, communication and data processing techniques to develop a novel test bench that can characterize the dynamic performance of the existing as well as the latest power semiconductor technologies. This compact, automatic test setup will help engineers to quantify the switching behavior of power semiconductors effortlessly. In this phase of continually evolving semiconductor industry when new devices are regularly launched in the market from numerous manufacturers, this kind of test setup will be required in both academia and industry for understanding the potential of these devices in a lab environment before implementing them in real life applications. There is a considerable amount of human involvement in the power semiconductor conventional switching characterization methods. Hence, the critical research objective of this thesis is to explore ways of establishing automation in all the major test segments i.e. test control, double pulse testing, data acquisition and data processing in order to save labour and reduce the overall testing time.

#### Methodology to meet research objectives:

- Conduct a thorough literature review to learn about the recent work in the area of proposed research. Study about the existing dynamic characterization setups, any recent developments published in technical literatures or commercially available products from the semiconductor/test equipment manufacturing industry that can shape the trajectory of the proposed research work.

- Plan the hardware with an intention of scaling down the overall test setup footprint with respect to conventional setups, consider possible elimination of any heavy equipments involved in the test process and implement alternate solutions for carrying out same functions. Use voltage, current and temperature sensors to establish closed loop control of test bed, employ power electronic converters as power supply units and control pulses with help of logic circuitries.

- Design a control system to exercise necessary control on the hardware elements, prepare

test bed, conduct test as well as co-ordinate the test process. Develop a GUI to allow

interaction between an user and the control system. Establish communication between

control system and other key units involved in the testing such as microcontroller and

oscilloscope.

- Amalgamate the hardware and software elements systematically. Thereafter subject the

prototype through series of open loop and closed loop tests to assess the performance of

individual modules and finally ensure the system is capable of conducting high voltage

double pulse tests.

- Characterize power semiconductor devices in a wide range of test conditions to demonstrate the stable operation of the proposed universal and automatic test setup.

- Develop a program to methodically process the raw test data, calculate values of different switching parameters as per relevant switching definitions in order to generate usable characterization results.

### 1.8 Organization of the Thesis

This thesis is organised in six chapters, a brief description of the chapters is provided below:

- Chapter 1: Introduction This chapter presents background information related to the research work described in this thesis, review of literature and research objectives. Different semiconductor technologies are reviewed, the importance of dynamic characterization of semiconductor devices is discussed and key switching parameters are defined. Thereafter, the topology of a Double Pulse Tester (DPT) is introduced and its operating principles are explained. A comprehensive review of current literatures is presented to discuss pros and cons of existing conventional DPTs and research objective of the thesis is formulated accordingly. This chapter is concluded mentioning the thesis contribution.

- Chapter 2: Hardware design This chapter focuses on the hardware implementation techniques of the Automatic DPT. The objective behind the segregated, modular design of the power and control modules is addressed. The detail design criteria of individual key units of both the control and power modules is presented and their contribution in achieving test automation is discussed. The PCB layout design considerations are discussed because the physical layout highly affects the switching test results.

- Chapter 3: Controller design In this chapter, the control architecture of the Automatic DPT is introduced. The design principles of the PC based test control software and its Graphic User Interface (GUI) is elaborately discussed. Thereafter, the interaction between the control system, on-board microcontroller and other key elements of the DPT system is explored. Control flow chart and block diagrams are used to depict the systematic functioning of the control and power board units for seamless and automatic operation of the proposed DPT system.

- Chapter 4: System Evaluation The specification and special technical requirements of the measurement tools such as probes, sensors, and oscilloscope for accurate recording of dynamic characterization results are discussed in detail in this chapter. The operation of the Waveform Analysis Tool (WAT), which is developed in MATLAB to process the vast amount of data captured during double pulse tests, is reviewed.

- Chapter 5: Experimental Verifications The complete DPT experimental setup is described in this chapter along with presentation of various experimental results. The design principles of the automatic test bed are verified and validated by demonstrating its successful operation. The same switching cell is implemented in a boost converter and the switching results from the converter is compared with that obtained from DPT for similar test condition. Both Si and WBG devices are characterized by changing the DPT power interface board thereby illustrating the universal design of the setup. Oscilloscope waveforms, plots and figures generated from the processed data are presented and analysed to understand the dynamic behavior of the switching cell.

Chapter 6: Conclusion and Future Work – This chapter summarizes the contribution of

this thesis as well as key conclusions that are drawn from the studies conducted. It also

discusses some of the potential future extensions.

#### 1.9 Research contributions

This thesis proposed an innovative design of a power semiconductor dynamic characterization tool that is cost-effective, compact, automatic and user-friendly. The major contributions of this thesis is summarized below:

- A thorough literature review has been conducted to gather background information on the conventional and existing device characterization setups used in both the academic and industrial domain. Their pros and cons are discussed and the shortcomings of the conventional setups are narrowed down in order to conceive the original research idea and present the motivation behind this research work.

- An innovative test bench is designed and implemented that is capable of automatically conducting dynamic characterization tests on a device under test following an user-specified test routine. The prototype built to materialize the research idea is capable of testing devices up to 1000V, 60A and 250°C. The design principles have been validated by successfully characterizing a TO-247 style, 3 pin Si IGBT and TO-227 style GaN FET.

- Considering the vastness of raw data originating from tests conducted under numerous

permutations of test parameters, a smart data processing program is developed in

MATLAB to scan through the raw data and identify key points for calculating switching

results. Raw data obtained from tests conducted on the proposed test bench is processed

using this tool and results are presented and discussed.

- The results of this research work will provide a new understanding of the trade-offs involved in the design process of an universal test bench. The hardware designs produced out of this research work will serve as a good reference for physical layout design of PCB, gate drive circuitries in a power electronic converter. This work will also create a platform to attract discussion, criticism and learn the views of other experts in this domain.

- This research has fuelled other researches in this domain. The dynamic characterization results obtained from this test platform have been utilized by fellow researchers to develop thermal and transient models for switching cell loss estimation in Electromagnetic transient simulation software PSCAD [17]. As opposed to a lossless model, this new model closely emulates the performance of a real semiconductor in terms of its loss behavior. The research output has been transferred to local industry such HVDC research centre for enhancing the semiconductor models in the PSCAD library. The research output has been published in relevant literatures as well.

## **Chapter 2 Hardware Design of Automatic Tester**

The objective of this chapter is to introduce the design considerations and methodologies adopted for the hardware realization of the proposed Double Pulse Tester. The entire design is fragmented into multiple units for ease of implementation, testing and debugging. The component selection for each these units are guided by the objective of designing a compact and automatic test bench. The impacts of the parasitic elements on the physical layout of the power stage are investigated and PCB design is optimized to obtain characterization results that reflect the true performance of the DUT.

## 2.1 System Architecture

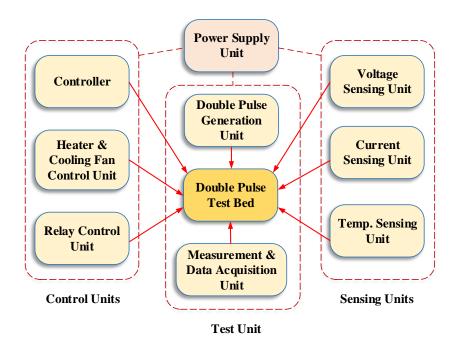

The overall double pulse testing system is designed with a multiple module approach for ease of implementation, testing and debugging. These modules or support units by performing their individual tasks at pre-programmed time slots, build up an intricate network of routine actions through which automation is realized in the proposed DPT. A block diagram shown in Figure 2.1, categorizes and tags these support units with their respective functions. The specification and design principles of these individual support blocks are further explored in the sections below.

Figure 2.1 Block diagram of peripheral supporting units in double pulse test bed.

The process of obtaining the switching characteristics of a power semiconductor device can be broken down into discrete stages. The first stage involves preparation of the test bed at user-defined test voltage and temperature levels. Once the testing environment is ready, the main switching test is conducted in the next stage by feeding two controlled pulse trains into the gate of the device through a specialized gate driver. The post-test activities include extraction of the raw experimental data from the oscilloscope and thereafter processing the data to obtain facts and figures that describe switching performance of the DUT. The automation in each of these stages mentioned above is achieved through systematic interaction between the key elements associated with each of these stages.

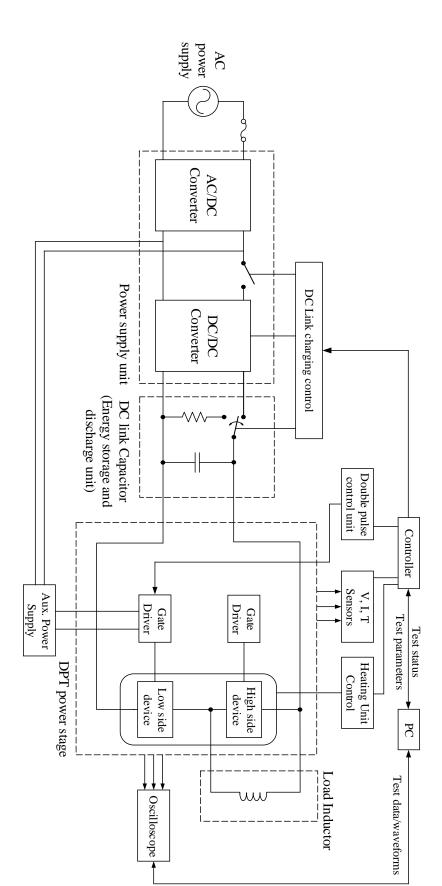

Figure 2.2 shows a block diagram schematic of the proposed automated DPT indicating its key elements. The design considerations behind each of these hardware elements and support units are further discussed.

Figure 2.2 DPT test setup schematic.

## 2.2 Control Board Design

The overall DPT system has been implemented with a mother control board and replaceable DPT power boards. This modular approach facilitates easy debugging and allows freedom in independent designing of the two boards to meet their specific design requirements. The control board is a PCB that houses the power supply units, microcontroller, sensor, logic and relay circuitries. In the subsequent sections, the design of each of these units are explored.

#### 2.2.1 Power Supply Unit (PSU)

One of the key focus in the design process is to make the testing system compact and stand-alone. Conventional setups use discrete DC power supply and Auxiliary power supply units, which consume a considerable amount of bench space and require manual control & configuration for every test condition [12],[15],[49]. In order to eliminate the need for such bulky units, a compact power supply system is designed to power up the main DPT board and its associated control and sensor circuitries. The overall design of the PSU and the units powered by it are shown in Figure 2.3. This compact PSU feeds the entire DPT setup i.e. the high voltage DC link voltage for the switching test, the gate driver, the DUT heating unit as well as the entire control circuitries on the control board including the controller. This makes the DPT system a stand-alone setup that can be installed and operated in any location that has access to a standard 120V AC power source.

An isolated dual output, PCB mount, 30W AC/DC converter (Model: ECL30UD03) is used to rectify the AC mains voltage to obtain 12V & 5V outputs. The 12V is used to power an ultra-small Volgen High Voltage DC/DC converter (Model: VHV12-1.0K2000P) to energize the High Voltage DC Bus up to 1000V for charging the capacitor banks. The availability of a voltage control pin in the High Voltage DC/DC converter facilitates automatic regulation of the converter's output voltage as per the set test voltage by isolated control signals from the microcontroller. The

converter's another useful pin, the ON/OFF pin is used as part of the protection system of the DPT. The microcontroller shuts off the high voltage output through this pin in the event of a fault. The 5V output from the AC/DC converter constitutes the Auxiliary power unit that feeds the microcontroller, sensor & gate drive circuitries, cooling fan and all the relays. The basic technical specifications as well as the key features of the DC/DC converters used in designing the PSU are encapsulated in Table 2.1.

Figure 2.3 Overall design of PSU for proposed DPT.

Table 2.1 Technical specification of DPT PSU converters

| Type               | Model                                                                    | Input Supply requirements                                                        | Output Power<br>Specification                                   | Salient features                                                                                                                                                                                                     |

|--------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC/DC<br>Converter | Make: XP<br>Power<br>Model:<br>ECL30UD03                                 | • 85-264<br>VAC<br>• 0.8A rms at<br>230VAC<br>• < 0.3W No<br>load Input<br>Power | Total: 30 W Output 1: 15 W (3 A, 5V) Output 2: 15 W (1.3A, 12V) | <ul> <li>Isolated Dual output</li> <li>PCB mount</li> <li>Encapsulated</li> <li>Output power is<br/>sufficient to meet power<br/>requirements of all<br/>connected components</li> </ul>                             |

| DC/DC<br>Converter | Make:<br>Volgen/<br>Kaga<br>Electronics<br>Model:<br>VHV12-<br>1.0K2000P | • 10.8 to 16.5<br>Vdc<br>• 280 mA typ.                                           | Power: 2 W<br>Voltage: 0 to +1000<br>V<br>Current: 2 mA         | <ul> <li>PCB mount</li> <li>Ultra compact HV supply unit</li> <li>Output voltage can be regulated by application of external voltage</li> <li>On/Off Pin allows remote switching on/off of output voltage</li> </ul> |

#### 2.2.2 Sensor and Control Units

<u>Voltage Control Unit</u>: In conventional DPT setups, the DC link voltage switched by the DUT comes from a separate HV power supply unit. This unit is manually regulated to the desired test voltage before each test. Considering the fact that in a double pulse test a DUT is characterized in a wide range of test voltages, manual configuration of the PSU before every test seems is a crude and laborious approach. In order to implement an automatic voltage setup system, it is essential to read the real time voltage in the power leg of the DPT. The real time monitoring of the DC link voltage will allow the controller to regulate and maintain the voltage at user specified values at all times.

The ACPL-C87A from Avago technologies, which is a precision optically-isolated amplifier is the key component used in the voltage-sensing unit. A resistive voltage divider is used to scale down

the DC-link voltage to suit the 2V input range of the sensor. A differential output voltage proportional to the input voltage is then passed through an amplifier and fed to the analog input pin of the on-board microcontroller. The galvanic isolation of the sensor protect the control circuitries from any possible surges from the power stage.