# Modelling of Custom Power Devices on an Electromagnetic Transients Program

Ву

#### Leena Palay

#### A Thesis

Submitted to the Faculty of Graduate Studies in partial fulfillment of the requirements for the degree of

#### **Master of Science**

The Department of Electrical and Computer Engineering

The University of Manitoba Winnipeg, Manitoba, Canada

© September, 1998

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reference

Our file Notre reférence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-35079-7

#### THE UNIVERSITY OF MANITOBA

## FACULTY OF GRADUATE STUDIES \*\*\*\*\* COPYRIGHT PERMISSION PAGE

## MODELLING OF CUSTOM POWER DEVICES ON AN ELECTROMAGNETIC TRANSIENTS PROGRAM

BY

#### LEENA PALAV

A Thesis/Practicum submitted to the Faculty of Graduate Studies of The University of Manitoba in partial fulfillment of the requirements of the degree

of

MASTER OF SCIENCE

Leena Palav C1998

Permission has been granted to the Library of The University of Manitoba to lend or sell copies of this thesis/practicum, to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film, and to Dissertations Abstracts International to publish an abstract of this thesis/practicum.

The author reserves other publication rights, and neither this thesis/practicum nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

#### Acknowledgements

To Dr. Gole, my supervisor. It has been a rare pleasure to interact with your energetic and dynamic personality. Your vast range of knowledge, your amazing insights helped me resolve many a glitch in this thesis.

And to Anurag Thakur, my fiance and my closest friend.

Thanks are due to the HVDC Centre for funding this thesis and very much due to Rohitha and Ioni of the Centre for bearing my numerous queries with calm fortitude.

I would also like to express my gratitude to Dr. Menzies. Sir, you have been a very inspiring presence in my life here.

## **Abstract**

Custom Power Devices comprise a group of power electronic controllers that seek to improve the level of quality of power available to the customer. Novel configurations using semiconductor switching devices can be designed to mitigate power quality problems such as voltage sags, harmonics and voltage flicker in distribution systems.

This thesis deals with the modelling of Custom Power topologies in the electromagnetic transient simulation programme PSCAD/EMTDC<sup>TM</sup>. Several configurations of Solid State Breakers and Dynamic Voltage Restorers have been studied and their control logic designed, using this simulation tool. The results of various tests have been enumerated in this thesis and it is shown that dynamic power electronic controllers can be designed to provide high quality of power to sensitive loads. These Custom Power models can now be used for detailed system studies at the distribution level.

## **Table of Contents**

| Abstract       |                                                             | i  |

|----------------|-------------------------------------------------------------|----|

| Table of Con   | itents                                                      | ii |

| List of Syml   | ools                                                        | v  |

| List of Figur  | res                                                         | vi |

| Dist of Figure |                                                             |    |

|                |                                                             |    |

| Chapter 1.     | Power Quality and Custom Power                              |    |

| 1.1            | Introduction                                                | t  |

| 1.2            | Scope of Thesis                                             | 2  |

| 1.3            | Reliability and Quality of Power                            | 2  |

|                | 1.3.1 Common Power Quality Issues                           | 2  |

|                | 1.3.2 Power Quality Standards                               | 5  |

| 1.4            | Custom Power                                                | 7  |

|                | 1.4.1 The Static Controllers                                | 7  |

|                | 1.4.2 Contributions of the Thesis                           | 9  |

| 1.5            | A Brief Note on EMTDC/PSCAD                                 | 10 |

| Chapter 2.     | The Solid State Breaker Configurations                      |    |

| 2.1            | Introduction                                                | 11 |

| 2.2            | The Solid State Breaker as a Transfer Switch                | 13 |

|                | 2.2.1 Introduction                                          | 1- |

|                | 2.2.2 Controls                                              | 15 |

| 2.3            | Results of Simulations for the SSTS                         | 17 |

|                | 2.3.1 The Simulation System                                 | 17 |

|                | 2.3.2 Response to Different Levels of Sags                  | 19 |

|                | 2.3.2 Response to Unbalanced Sag                            | 20 |

| 2.4            | Make before Break or Break before Make                      | 21 |

|                | 2.4.1 Problem with Mechanical Breakers                      | 23 |

|                | 2.4.2 Advantage of Intelligent Polarity Selection with SSTS | 22 |

|                | 2.4.3 Response to Induction Motor load                      | 24 |

| 2.5            | The Solid State Breaker as a Fault Current Limiter          | 21 |

|           | 2.5.1        | Introduction                                   | 27 |

|-----------|--------------|------------------------------------------------|----|

|           | 2.5.2        | Topology                                       | 27 |

|           | 2.5.3        | Controls                                       | 30 |

| 2.        | 6 Results of | f Simulations for the SSB-FCL                  | 32 |

|           | 2.6.1        | The Simulation System                          | 32 |

|           | 2.6.2        | Response of the Breaker                        | 32 |

|           | 2.6.3        | Response with Current Limiting Reactor         | 34 |

|           | 2.6.4        | Response with Current Control by Thyristors    | 35 |

|           | 2.6.5        | Response to Transient Faults                   | 36 |

| 2.        | 7 Conclusio  | ons and Future Work                            | 37 |

| Chapter 3 | . The Seri   | es Power Flow Controller                       |    |

| 3.        | I Introduct  | tion                                           | 38 |

| 3.        | 2 Series Re  | eactive Power Compensation                     | 38 |

|           | 3.2.1        | Basic Theory                                   | 38 |

|           | 3.2.2        | Theory of Advanced Static Series Compensation  | 40 |

|           | 3.2.3        | Phasor Diagrams                                | 41 |

|           | 3.2.4        | Comparison of Various Series Power Controllers | 43 |

| 3.        | 3 The Serie  | es Power Flow Controller                       | 46 |

|           | 3.3.1        | The STATCOM Configuration                      | 46 |

|           | 3.3.2        | The Transformers and Filters                   | 48 |

|           | 3.3.3        | The STATCOM Controls                           | 50 |

|           | 3.3.4        | The Transmission Line System for Simulations   | 51 |

| 3.        | .4 Results o | f Simulations for the SPFC                     | 54 |

|           | 3.4.1        | Response to a Step Change in Power Order       | 55 |

|           | 3.4.2        | Inductive Compensation                         | 55 |

|           | 3.4.3        | Response to a Change in Load Angle             | 57 |

|           | 3.4.4        | Reactive Compensation for Voltage Regulation   | 58 |

| 3         | .5 Conclusio | ons and Future Work                            | 60 |

| Chapter 4 | . The Dyn    | amic Voltage Restorer Configurations           |    |

| 4         | . I Requiren | nents for a DVR                                | 61 |

| 4         | •            | C as a DVR                                     | 62 |

|           | 4.2.1        | Discussion on Feasibilty and Limitations       | 62 |

|           | 4.2.2        | Formulae for Sag Compensation by SPFC-DVR      | 65 |

| 4.3            | Simulati   | ons for the pure SPFC-DVR                         | 67  |

|----------------|------------|---------------------------------------------------|-----|

|                | 4.3.1      | The Simulation System                             | 68  |

|                | 4.3.2      | Controls                                          | 69  |

|                | 4.3.3      | Results                                           | 70  |

| 4.4            | Ideal Sag  | Compensation                                      | 72  |

|                | 4.4.1      | Introduction                                      | 72  |

|                | 4.4.2      | Modifications to the SPFC-DVR for Ideal Sag Comp. | 73  |

|                | 4.4.3      | Controls                                          | 74  |

|                | 4.4.4      | Simulations for the modified SPFC-DVR             | 77  |

| 4.5            | The Shur   | nt Fed Dynamic Voltage Restorer                   | 79  |

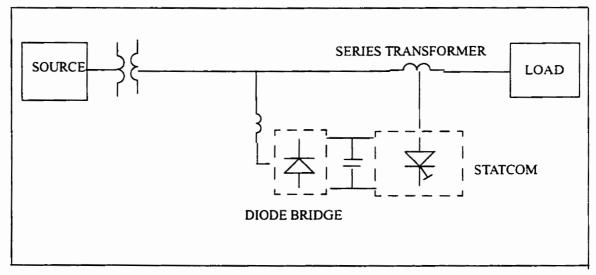

|                | 4.5.1      | Introduction                                      | 79  |

|                | 4.5.2      | The Simulation System                             | 80  |

|                | 4.5.3      | Controls                                          | 83  |

| 4.6            | Results    | of Simulations for the Shunt Fed DVR              | 4-8 |

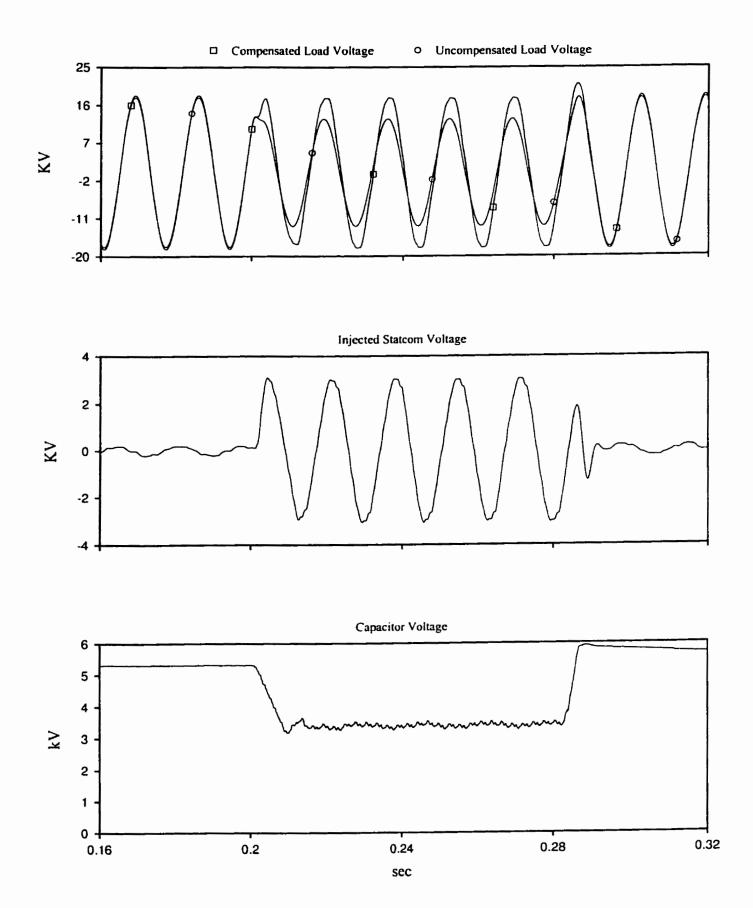

|                | 4.6.1      | Compensation for Balanced Sags                    | 84  |

|                | 4.6.2      | Compensation for Unbalanced Sag                   | 87  |

| 4.7            | Conclusi   | ons and Future Work                               | 89  |

|                |            |                                                   |     |

| Summary ai     | nd Concl   | lusion for the Thesis                             | 90  |

| References     |            |                                                   | 92  |

| Appendix A : ( | Comparisor | n of Various Series Control Devices               | 94  |

## **List of Symbols**

GTO: Gate Turn Off Thyristor

IGBT: Integrated Gate Bipolar Transistor

HP: Horse Power

kHz : kilohertz (frequency)

SSB : Solid State Breaker

STATCOM: Static Compensator

SPFC: Series Power Flow Controller

DVR: Dynamic Voltage Restorer

FCL : Fault Current Limiter

SSTS: Solid State Transfer Switch

μs: microseconds (time)

kA: kiloamperes (current)

kV: kilovolts (voltage)

MVA: megavoltampere (apparent power)

MW: megawatts ( real power)

MVAR: megavars ( reactive power)

FFT: Fast Fourier Transform

RL Load: Load consiting of resistors and inductors only

p.f: power factor

S-L-G: Single Line to Ground (fault) di/dt: rate of change of current

δ: Load Angle

XI: Inductive Reactance Xc: Capacitive Reactance

PWM: Pulse Width Modulation (Firing)

Vd: Capacitor DC Voltage n: Transformer Turns ratio

pu: per unit

ma : Modulation Index cosφ : power factor

PCC: Point of Common Coupling

L-L: Line to Line (values)

## **List of Figures**

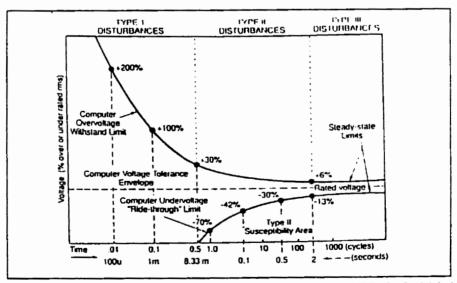

| 1.1 The CEBA graph for Voltage Tolerance (Std. 446-1987)                         | 6  |

|----------------------------------------------------------------------------------|----|

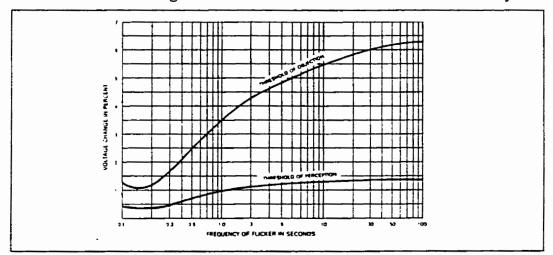

| 1.2 Range of Objectionable Flicker versus Time (Std. 141 -1986)                  | 7  |

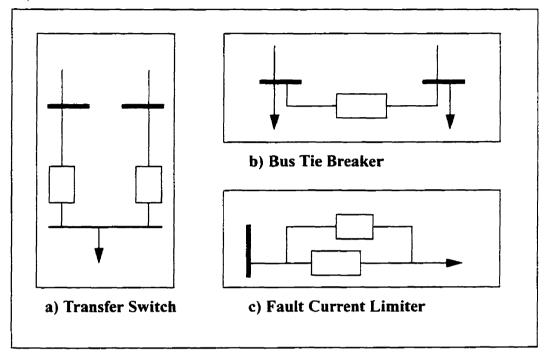

| 2.1 Various Applications of the Solid State Breaker                              | 12 |

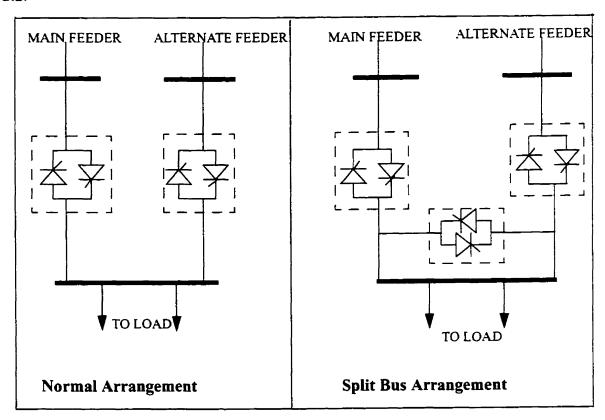

| 2.2 Two Configurations of the Transfer Switch                                    | 13 |

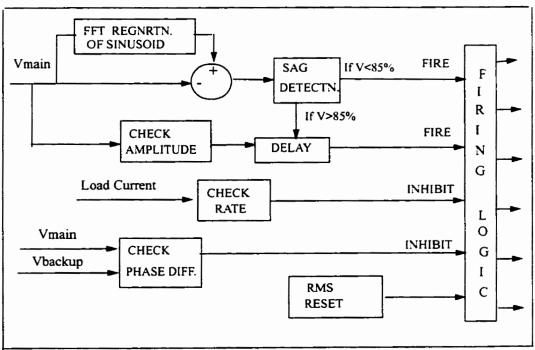

| 2.3 Control Logic for the Transfer Switch                                        | 15 |

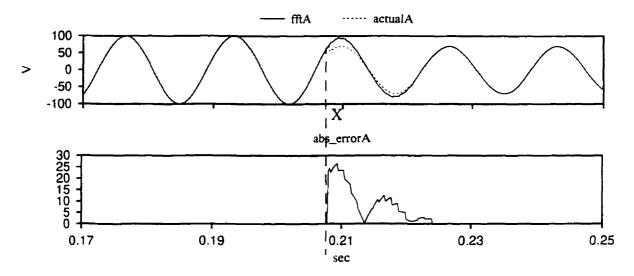

| 2.4 Generation of an error signal using FFT                                      | 16 |

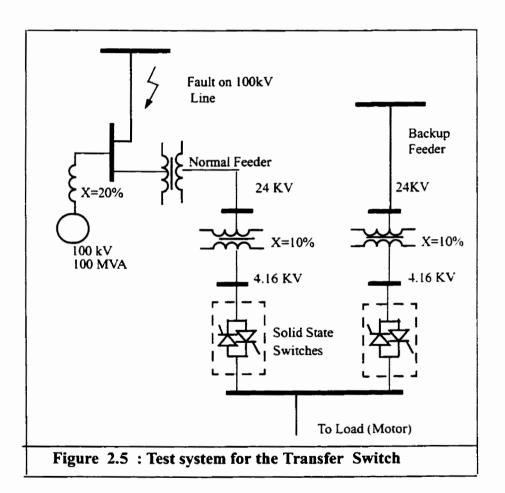

| 2.5 Test system for the Transfer Switch                                          | 17 |

| 2.6 The PSCAD/EMTDC Draft Circuit for the Transfer Switch                        | 18 |

| 2.7 Transfer of a RL Load for a 40% Sag                                          | 19 |

| 2.8 Transfer for an unbalanced sag                                               | 20 |

| 2.9 Make before Break Transfer with Mechanical Breakers and 30 deg. phase diff.  | 21 |

| 2.10 Break before Make Transfer with Mechanical Breakers and 30 deg. phase diff. | 22 |

| 2.11 Make before Break Transfer with SSTS                                        | 23 |

| 2.12 Make before Break Transfer with SSTS and a 30 deg. phase difference         | 24 |

| 2.13 Make before Break Transfer for Induction Motor Load                         | 25 |

| 2.14 Break before Make Transfer for Induction Motor Load                         | 26 |

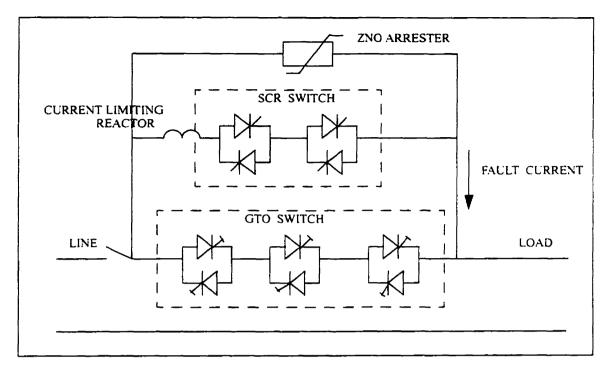

| 2.15 A Solid State Breaker with a Fault Current Limiting Unit                    | 28 |

| 2.16 Basic Control Blocks for the SSB -FCL                                       | 30 |

| 2.17 Control Algorithm for Automatic Reclosing mode                              | 31 |

| 2.18 Simulation system for the SSB-FCL                                           | 32 |

| 2.19 The PSCAD/EMTDC Draft Circuit for the SSB-FCL                               | 33 |

| 2.20 Response of the GTO Switch                                                  | 34 |

| 2.21 Response with Current Limiting Reactor                                      | 34 |

| 2.22 Load Current Waveforms with Current Modulation Loop                         | 35 |

| 2.23 Response of the SSB-FCL in the Automatic Reclosing mode                     | 36 |

| 3.1 The Basic Series Power Flow Controller                                       | 40 |

| 3.2 Series Power Flow Control by Voltage Insertion                               | 41 |

| 3.3 Phasor Diagrams for Series Power Flow Control                                | 42 |

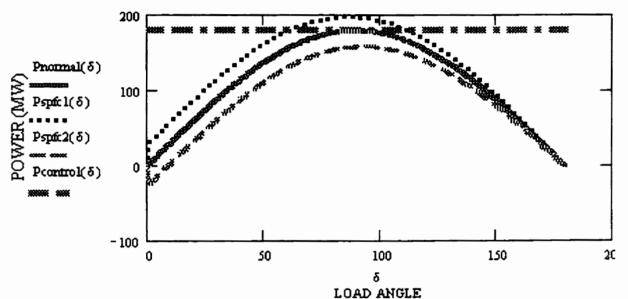

| 3.4 Comparison of Various Series Power Controllers for Various Load Angles       | 44 |

| 3.5 Comparison of Various Series Power Flow Controllers at a Load Angle (30°)    | 45 |

| 3.6 A Basic 6 Pulse STATCOM                                                      | 46 |

| 3.7 Sinusoidal PWM waveform generation                                           | 47 |

| 3.8 A Floating Neutral Series Transformer connection with Filters                | 48 |

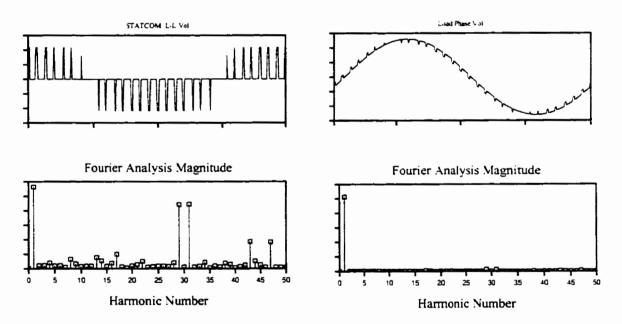

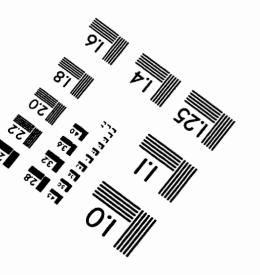

| 3.9 Fourier Analysis of SPFC waveforms                                           | 49 |

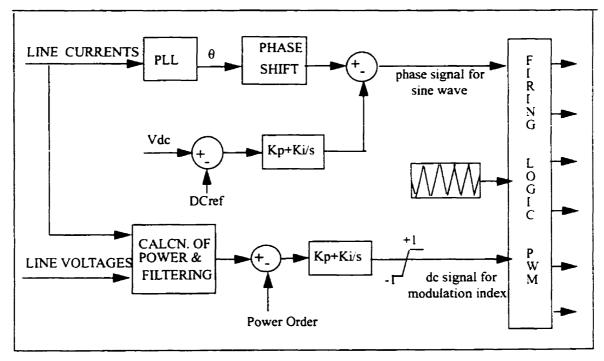

| 3.10 Block Diagrams of the SPFC -STATCOM Controls                                | 50 |

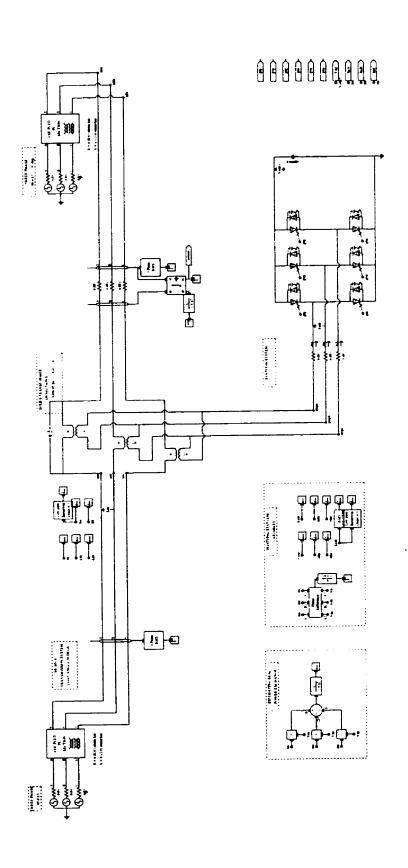

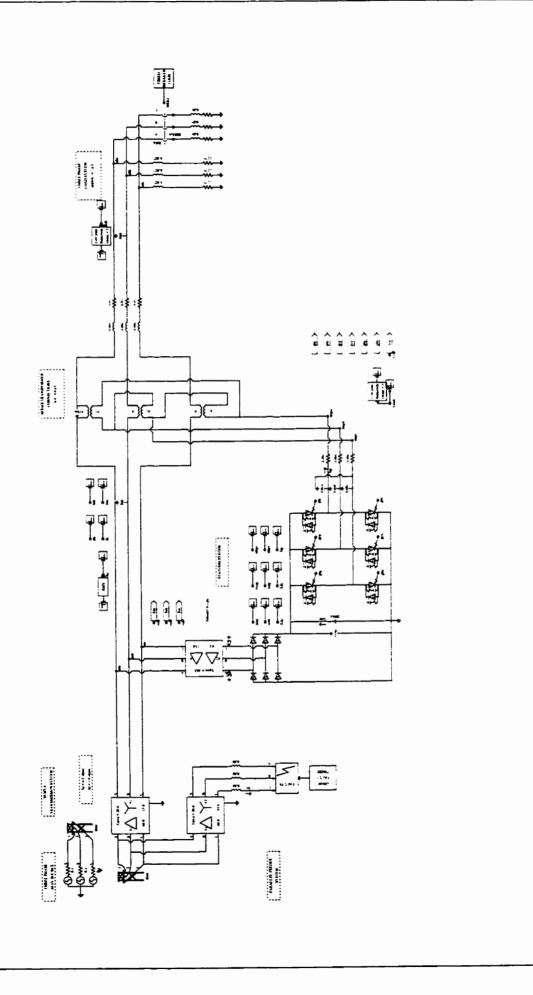

| 3.11 The EMTDC/PSCAD Draft Circuit of the SPFC                                   | 53 |

| 3.12 Range of Power Flow Control for the 66.0 kV line                            | 53 |

| 3.13 Response to Sten Changes in Power Order                                     | 54 |

| 3.14 Inductive Compensation                                           | 56 |

|-----------------------------------------------------------------------|----|

| 3.15 Response to Swing in Load Angle                                  | 57 |

| 3.16 Voltage Regulation in a Distribution System with SPFC            | 58 |

| 3.17 Voltage Regulation by a SPFC with changes in the Load Current    | 59 |

| 4.1 Operation of the DVR during System Voltage Sags                   | 61 |

| 4.2 The SPFC -DVR                                                     | 63 |

| 4.3 Phasor Diagram for Compensation of a sag                          | 64 |

| 4.4 The EMTDC/PSCAD Draft Circuit of the SPFC -DVR                    | 68 |

| 4.5 Block Diagrams of the SPFC -DVR Controls                          | 69 |

| 4.6 Response of the SPFC -DVR with a 0.788 pf. and a 0.34 pf load     | 70 |

| 4.7 Phasor diagram for Ideal Sag Compensation                         | 72 |

| 4.8 Phasor Diagrams for Ideal Sag Compensation                        | 72 |

| 4.9 Controls for the modified SPFC -DVR                               | 74 |

| 4.10 Generation of Error Signal for Ideal Sag Compensation            | 76 |

| 4.11 Changes in the Modulation Index with change in Capacitor voltage | 77 |

| 4.12 Response of the Modified SPFC -DVR to 40% sag                    | 78 |

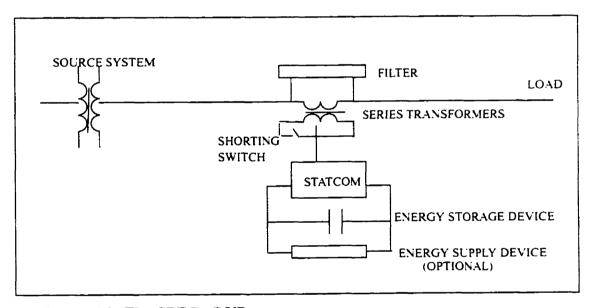

| 4.13 The Shunt Fed DVR                                                | 79 |

| 4.14 The EMTDC/PSCAD Draft Circuit for the Shunt Fed DVR              | 82 |

| 4.15 Controls for the Shunt Fed DVR                                   | 83 |

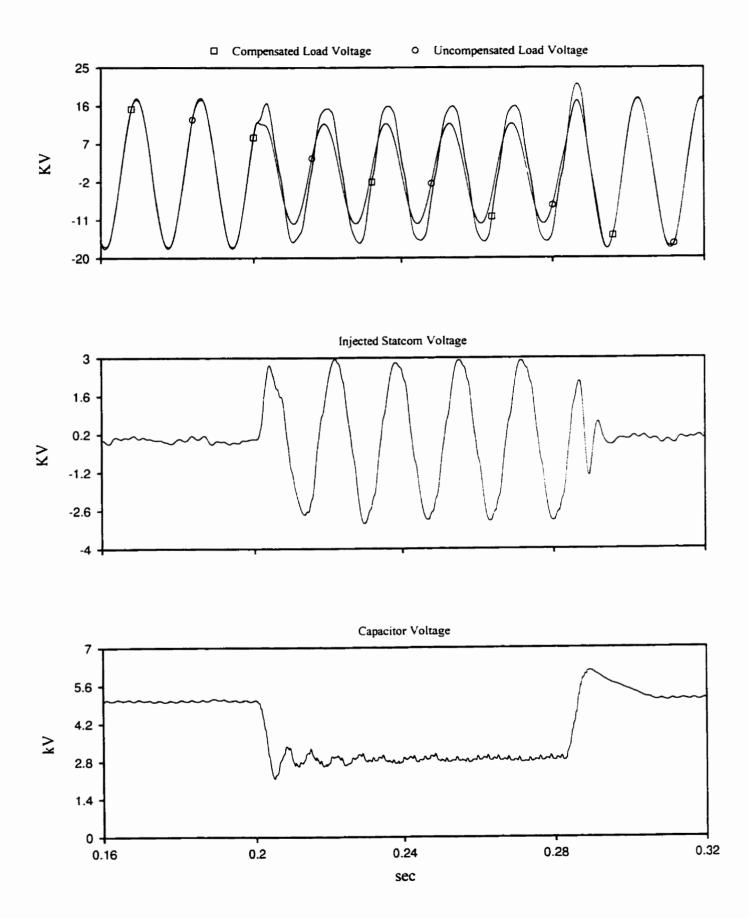

| 4.16 Compensation by a Shunt Fed DVR for a 40% sag                    | 85 |

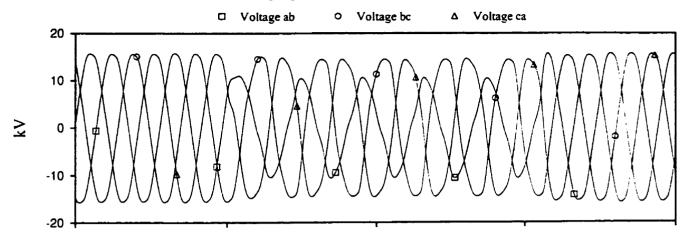

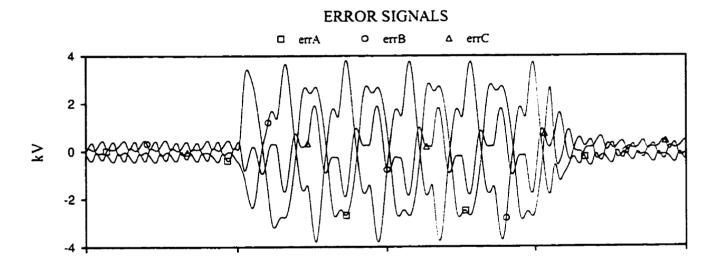

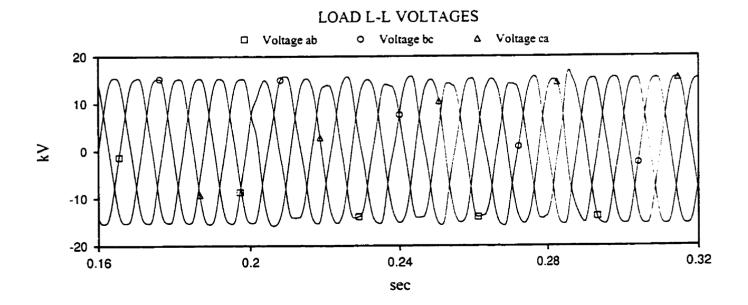

| 4.17 Compensation of Unbalanced Sags by a Shunt Fed DVR               | 88 |

#### Chapter 1

## **POWER QUALITY AND CUSTOM POWER**

#### 1.1 INTRODUCTION

There has been an increasing amount of focus on power quality in distribution systems. Due to factors like competitive generation patterns in a deregulated electric grid and an increasing level of sensitive end user devices, it has become necessary to ensure both reliable and quality power to the discerning customer.

Until recently, utility efforts in this direction were typically limited to installing passive filters or improving distribution capacity. If the customers require a high quality of power, low voltage power controllers, such as Uninterruptible Power Supplies, had to be installed at their end. But now, with the advent of cheap, high-power rated semiconductor devices like Gate Turn Off Thyristors (GTOs) and Integrated Gate Bipolar Transistors (IGBTs), it has become possible to design novel electronic controllers for high speed and precise control of power by the utility itself.

Such controllers are already in use in large transmission systems like Flexible AC Transmission Systems (FACTS) and High Voltage Direct Current Systems (HVDC) for providing functions like reactive power compensation, direct current transmission, damping of power oscillations etc. Custom Power now seeks to implement such designs for improving

dynamic power flow control in the distribution system and thus provide value added power to the customer [1].

#### 1.2 SCOPE OF THIS THESIS

This thesis deals with the modelling of Custom Power topologies in the electromagnetic transient simulation programme PSCAD/EMTDC<sup>TM</sup>. A brief description of the programme is given in Section 1.5.

With this objective, the scope of the thesis is

- to understand the issues involved in the operation of Custom Power topologies.

problems and their traditional solutions are discussed in the following section.

- to design control strategies that address most of these issues.

- to make simulation models in PSCAD/EMTDC for further studies in Power Quality.

The various Custom Power devices are enumerated in Section 1.4. The power quality

#### 1.3 RELIABILTY AND QUALITY OF POWER

#### 1.3.1 Common Power Quality Issues

Reliability of power forms the first component of power quality requirements. IEC (1000-

-2-2/4) and CENELEC (EN50160) standards define power quality as the physical characteristics of the electrical supply provided under normal operating conditions that do not disrupt or disturb the customers' process. Therefore, reliability of power is the first prerequisite to power quality issues.

A power supply may be said to supply reliable power if there are no outages or if there is a fast recovery from outages by fast fault clearance or backup generation. A considerable amount of reliability has been ensured by the various utilities over the years by increasing grid networking and improving breaker devices. But due to the complexity of the distribution network, outages and interruptions are far more common on the distribution system than on the transmission grid [6].

Quality of power combines all the elements of reliability with additional considerations to the voltage waveforms at the customer bus. Ideally this voltage should be a perfect Sun-View without any distortions, at it's nominal magnitude and nominal frequency. Further, for a three phase system, the voltages should form a perfectly balanced set, with each phase displaced by 120 degrees with respect to the others [2].

Distortions in the voltage waveform may be due to harmonics, transients, voltage over shoots or undervoltages. Such distortions, which were hitherto tolerated, manifest as severe problems when it comes to highly sensitive consumer devices such as the computers, lamps, communication systems, industrial sensors and controls.

Table 1 gives a concise summary of the various power quality problems, their causes and effects, based on a literature review with references like [4]....[8].

**Table 1: A Summary of Various Power Quality Problems**

| TERM                             | EFFECTS                                                                                                                                                                              | CAUSES                                                                                                                                                                                           | TRADITIONAL SOLUTIONS                                                                                                        |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Voltage<br>regulation            | A decrease in the voltage at the utilisation terminal.                                                                                                                               | Impedance drops in<br>the feeders, house<br>wiring etc.                                                                                                                                          | Reducing impedance by paralleling transformers. Increasing primary feeder voltages, feeder size.                             |

| Voltage outages/interruptions    | A complete loss of voltage; called an interruption if it is for < 5 mins.  An expensive loss to the industry due to long downtime.                                                   | Open circuit faults in the cables. Operation of protective equipment during fault clearance.                                                                                                     | Faster fault clear-<br>ance.<br>Increasing paral-<br>lel feeders and<br>grid networking.                                     |

| Voltage<br>unbalance<br>Vc<br>Vb | Produces negative sequence components. May cause sags. Three phase motors, if run on single phase generate excessive heat.                                                           | Mostly caused due to Single Line to Ground faults. May be caused by unbalanced loading such as railway load or even by untransposed lines.                                                       | Improved balancing of loads. Faster fault clearance                                                                          |

| Voltage dips/sags                | A reduction in the rms value of voltage for 0.5-30 cycles. Cause malfunctioning in loads such as computers and VCRs; tripping of relays, motor contactors in drives, mercury lights. | Remote faults /paral-<br>lel faults, lasting until<br>fault clearance.<br>Reclosing operations<br>may give multiple<br>sags. Starting of<br>induction motors<br>may initiate/aggravate<br>a sag. | Mechanical transfer of sensitive loads in a selective type of system. Localised application of a saturated ferrotransformer. |

| Voltage flicker                  | A momentary fluctua-<br>tion in voltage, caus-<br>ing irritation to the<br>human eye if resulting<br>in visible light fluctua-<br>tions.                                             | Motor start-up, switching on of large capacitor banks, oper- ation of arc furnaces and rolling mills. May also be caused                                                                         | Use of saturable reactors / ferrotransformers. Isolation of heavy duty loads from sensitive loads.                           |

|                                  | May interfere with functioning of sensitive equipment.                                                                                                                               | by fractional HP motors as in refrigerators.                                                                                                                                                     | ivaus.                                                                                                                       |

**TRADITIONAL** TERM **EFFECTS** CAUSES SOLUTIONS Harmonics A superimposition of Y-Δ transformers Mainly electronic voltages of different switching load such to restrict third frequencies on the funas thyristor drives, harmonics. rectifiers, UPS etc. damental, leading to Underground Non linear loads such additional losses and cabling to use overheating. as lights. shunt capaci-Possible resonances tance filtering. with local induct-Passive low-pass/ ances. Telephone intertuned filters near ference. the customer end.

Table 1: A Summary of Various Power Quality Problems

#### 1.3.2 Power Quality Standards

There are attempts by the concerned agencies such as the IEEE [4] [5] [7], to fix a set of standards to accurately define and quantify the quality of power supplied to the customer. But standards for the amount of allowable power line disturbance vary with the type of load and the magnitude of the disturbance. Indeed, power quality is firstly defined to be that level of power which satisfies the customer. The CEA 9109 U 856 Series classifies the power quality into five classes ranging from "pure" Class A, as in the Uninterrupted Power Supply (UPS), to "almost ideal" Class B, as for the Computer Business Equipment Manufacturers Association (CBEMA) Voltage Tolerance Curve, and so on till Class E where frequent outages for long seconds could be allowed.

A general idea of the power quality requirements could be had from Table 2 below, which are taken from IEEE Standards 446-1987 for the Computer Manufacturing Industry.

Table 2: Typical Range of Input Power Quality and Load Parameters of Major

Computer Manufacturers

| - | Parameters                                                                                        | Range or Maximum                                                                          |

|---|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| l | Voltage regulation                                                                                | +5,-10% to +10,-15%                                                                       |

| 2 | Undervoltage                                                                                      | -25% to -30% for less than 0.5 s;<br>-100% acceptable for 4 to 20 ms;<br>(see Figure 1.1) |

| 3 | Transient overvoltage                                                                             | +150 to 200% for less than 0.2 ms                                                         |

| 4 | Voltage harmonic distortion                                                                       | 3 to 5% with a linear load                                                                |

| 5 | Frequency variation                                                                               | 60 Hz +/- 0.5 Hz to +/- 1 Hz                                                              |

| 6 | Noise                                                                                             | No standard                                                                               |

| 7 | 3 \phi voltage unbalance<br>= $\left(\frac{3 \cdot (Vmax - Vmin)}{Va + Vb + Vc} \cdot 100\right)$ | 2.5 to 5%                                                                                 |

| 8 | Power factor                                                                                      | 0.8 to 0.9                                                                                |

Figure 1.1: The CEBA graph for Voltage Tolerance (IEEE Std. 446-1987)

Figure 1.1 shows the CBEMA curve for voltage quality for computers, which is mostly used as a guide for voltage quality studies. It can be seen that while a 13% sag can be borne for 2 seconds, a 70% sag cannot be tolerated for even 16 ms.

It is more difficult to set a standard for voltage flicker as it is primarily defined to be that level of fluctuations in brightness that would cause irritation to the human eye.

Figure 1.2: Range of Objectionable Flicker versus Time (IEEE Std. 141 -1986)

Figure 1.2 may be used to determine whether voltage fluctuations will cause objectionable fluctuations in the light output of incandescent lamps. The range between permissible flicker and objectionable flicker is to accommodate the differences in human perception and the environmental conditions. It can be seen that even a 2% change for 1/2 second is intolerable. It also shows that the flicker is mostly in the range of a few hertz, say 7-9 Hz.

#### 1.4 CUSTOM POWER

#### 1.4.1 The Static Controllers

As was stated in the introductory paragraph, it is now possible to use fast acting switching

semiconductor devices to improve power quality, which is the objective of this thesis. The semiconductor devices can not only be used as simple switches, they can also be used to generate complex waveforms with controllable magnitude, phase or frequency and to inject them into the line and thus compensate for quality problems from the source. These devices have only been possible due to the rapid strides in the semiconductor industry which offers high power rating devices such as GTOs with ratings such as 3 kA and 4.5 kV peak values (for a symmetrical GTO pair) or IGBTs, which can bear higher switching frequencies like 2 kHz[12]. The rapid response of such devices enable them to operate in real-time and online and provide continuous and dynamic control of the supply [1].

These devices are incorporated into the following topologies to improve various power quality problems.

- 1. The Distribution Static Compensator (D-STATCOM) for reactive compensation and flicker control by being placed in shunt with the load for dynamic compensation.

- 2. Active Filters for harmonic elimination by injection of a controlled harmonic current to oppose the instantaneous harmonics produced by the load.

- 3. The Solid State Fault Current Limiter (SSB-FCL) for reducing fault current levels to that of the downstream protection devices.

- 4. The Solid State Transfer Switch (SSTS) for fast transfer of sensitive loads to protect against system side faults such as voltage sags.

- 5. The Series Power Flow Controller (SPFC) for series reactive power flow.

- 6. The Dynamic Voltage Restorer (DVR) for compensation of voltage sags by series injec-

-tion of a controlled voltage.

- 7. A Unified Power Controller or Conditioner, seeking to incorporate all the features of the above mentioned devices into one.

- 8. A rechargeable source of energy such as the Superconducting Magnetic Energy Storage (SMES).

#### 1.4.2 Contributions of the Thesis

This thesis has covered

- i) development of the power circuits of

- (a) The Transfer Switch

- (b) The Fault Current Limiter

- (c) The Series Power Flow Controller

- (d) The Series Voltage Regulator

- (e) The Dynamic Voltage Restorer

- ii) analysis of the various issues involved in the performance of these devices.

- iii) designing of control strategies that would result in successful, working models.

- iv) testing for various conditions and evaluation of results.

These configurations are modelled, analysed and discussed in individual chapters later in this thesis. While the Transfer Switch and the Fault Current Limiter use the thyristor

switching device as a plain Solid State Breaker, the rest of the topologies involve the GTO switching device in a STATCOM configuration with a Pulse Width Modulated (PWM) type of switching control.

The results are computed with the help of a simulation tool PSCAD/EMTDC<sup>TM</sup>: a word on it follows.

#### 1.6 PSCAD/EMTDC

PSCAD is a collection of programs, providing a very flexible interface to electromagnetic transient simulation software. EMTDC is the library of power system component models and procedures which constitutes the simulation software[3]. Together, they offer a very powerful tool for transient analysis.

Circuits are drawn using the graphical DRAFT module, which are then compiled and run using the RUNTIME module. Parameters can be accessed and changed during a run and the results can be plotted using the MULTIPLOT module. The basic code is in FORTRAN.

#### Chapter 2

#### SOLID STATE BREAKER CONFIGURATIONS

#### 2.1 INTRODUCTION

The time required for mechanical interruption of faults on a transmission line is known to be typically in the order of 1.1-10 secs.[9]. Similarly, mechanical transfer of loads from a faulty feeder to a healthy one can cause a power interruption of at least 2 secs [10].

On a distribution line, sensitive equipment like computers, programmable drives, consumer electronic equipment like televisions and VCRs cannot tolerate a disturbance of such a length of time and show perceptible effects in their operation. As was shown in Chapter 1, even a small sag of 30% lasting for half a second can cause malfunction in a computer. Further, many industries using thyristor based drives have reported hours of equipment downtime and considerable losses due to voltage sags [11].

A Solid State Breaker (SSB), on the other hand, typically acts within 1/4 of a cycle and offers fast isolation / transfer of feeders or loads [1]. This swift action can be used advantageously, even in conjugation with the slower mechanical breakers, for protection schemes. The objective of this chapter is to study the possible applications of the SSB that can be used with the existent distribution network.

Figure 2.1 shows three configurations that are possible with the SSB viz. a Transfer Switch, a Bus Tie Breaker and a Fault Current Limiter.

Figure 2.1: Various applications of the Solid State Breaker

A Solid State Transfer Switch (SSTS) is used to protect sensitive loads by switching it onto a healthy backup feeder if there are any problems on the main feeder. This can be incorporated using thyristors. A Solid State Breaker-Fault Current Limiter (SSB-FCL) is used to limit fault current levels to downstream protection device levels and can be designed using both GTOs and thyristors.

A Bus Tie Breaker is used to isolate buses during faults and can easily be incorporated by using just a self commutated GTO based SSB. Present designs rely on expulsion fuses, which have to be reset manually. A Bus Tie Breaker can be considered to be a special case of the Fault Current Limiter and hence only the other two configurations are further studied in this chapter.

#### 2.2 THE SOLID STATE BREAKER AS A TRANSFER SWITCH

#### 2.2.1 Introduction

The transfer switch is used to protect sensitive loads from system side faults. These could include outages, voltage swells, sudden phase changes, but they are most predominant as voltage sags. Detailed descriptions of sags, their causes and their effects have already been discussed in Chapter 1. The transfer switch here is used to mitigate the effects of such sags on sensitive loads. Generally, it could be used in two configurations as shown in Figure 2.2.

Figure 2.2: Two Configurations of the Transfer Switch

Normally, this SSTS is designed to detect a voltage disturbance within 4 ms and immediately transfer power for sensitive loads from one source to another healthy source [1]. The two feeders could be at different points on the same network or they could be from entirely different systems, as in a stand-by emergency supply. The split bus arrangement is used to reduce transients during handover.

The semiconductor device used in the SSTS are thyristors. This is so because the switch is in continuous conduction mode and requires in addition to a continuous current rating, a short time overcurrent rating equal to the load side faults. Thyristors have a high short time overcurrent rating of 16 kA and also have low conduction losses [12].

The thyristors in the main branch are normally continuously energised by continuous, synchronised firing. On detection of a sag, these firing pulses are stopped. The thyristors which would have then stopped conducting at the first natural current zero in that phase, are now subjected to a high reverse voltage from the other feeder and are immediately turned off. Current interruption is thus achieved in sub cycle.

Some considerations that are to be addressed while incorporating this device [10], [11], [12], and used in this thesis for the design of the control system include:

- 1. The detection method for a sag should be fast (preferably within 1/4 th of a cycle) and should be so even in the presence of a reasonable amount of harmonics or transient phase changes or unbalance.

- 2. There should be no transfer in case of sags due to faults on load side.

3. There should also be no transfer if the phase difference between the two feeders is considerable (taken here to be >10 degrees) as this would cause high inrush currents for loads such as induction motors and transformers.

#### 2.2.2 Controls for the Transfer Switch

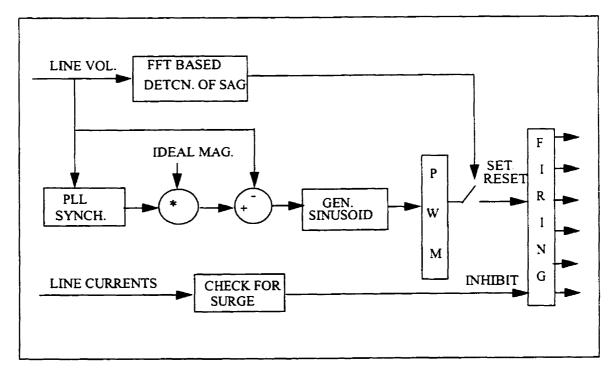

Figure 2.3: Control Logic for the Transfer Switch

Instantaneous detection of a sag is obtained by constant comparison of the voltage waveform with a ideal sinusoid in phase with it and having a magnitude equal to the pre -sag

value. This sinusoid is reconstructed using the fundamental frequency component of the

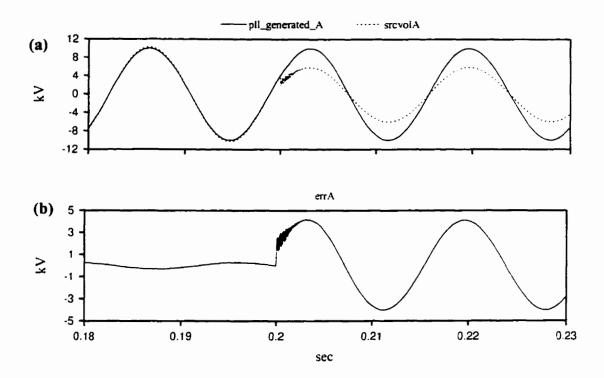

Fast Fourier Transform of the voltage waveform from a previous cycle. If the actual waveform has a lower instantaneous value over the predicted waveform, an error signal is generated for a sag, as shown in Figure 2.4.

Figure 2.4: Generation of an error signal using FFT

The sag is applied at point 'X'. It is seen that the FFT generated waveform 'fftA', which is delayed by 1 cycle, remains at the previous steady state value for at least 1 cycle, giving rise to an instantaneous detection of an error, lasting for 1 cycle. This can be further processed for developing the firing pulses for the thyristors.

It is obvious that such an error signal will be generated for any other form of distortions such as a phase change, harmonics or voltage swells. This would give rise to "nuisance tripping" and in order to avoid that, a more robust method of detection for small sags is used, whereby some more time (1/2 cycle) is used to check the peak of the waveform and detect a sag.

Inhibition blocks are used to detect faults on load side and / or excessive phase differences between the two feeders and prevent the transfer.

#### 2.3 RESULTS OF SIMULATIONS

#### 2.3.1 The Simulation System

Simulations were performed on a three phase 100 MVA system as shown below. This system is identified as a suitable candidate for Transfer Switch studies [11].

Faults are applied on a parallel line to induce the necessary levels of sags on the main feeder. The circuit is tested for two types of loads: a 0.7 p.f. RL load and a Induction Motor load. The detailed PSCAD/EMTDC Draft circuit is shown next in Figure 2.6.

Solid State breaker as a Transfer Switch University of Manitoba, EE Dept.

Created: Last Modified: Printed On:

June 01, 1997 (leena) September 21, 1998 (leena) September 21, 1998 (leena)

1 S.S.

Subsystem #1 of 2

#### 2.3.2 Response to Different Levels of Sags

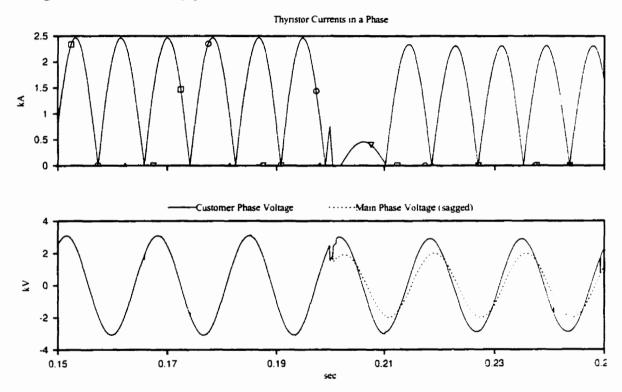

Figure 2.7 illustrates the rapid action of the transfer switch for a remote fault on the main bus, causing a sag of around 40%. The alternate bus was at zero phase difference with respect to the customer bus and the load was a 12 MVA load at 0.8 p.f.

Figure 2.7: Transfer of a RL load for a 40% sag

Figure 2.7(b) shows the voltage at the customer bus. Since the sag was well above 20%, it got detected within 1/4th of a cycle and an immediate transfer was initiated. The customer voltage remained almost undistorted.

For sags smaller than 15%, as was mentioned earlier, a higher margin of time is allowed for detection by measurement of the amplitude of the source voltage.

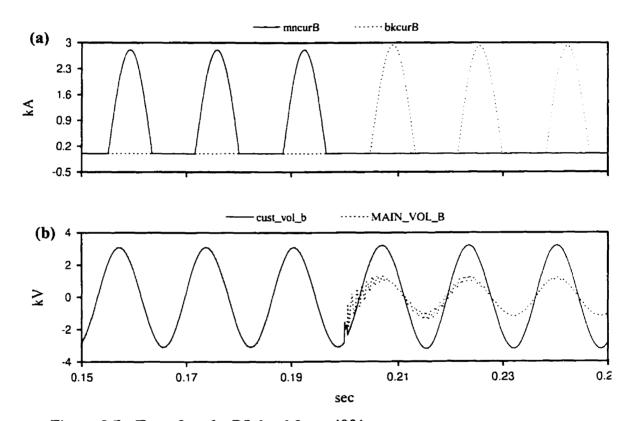

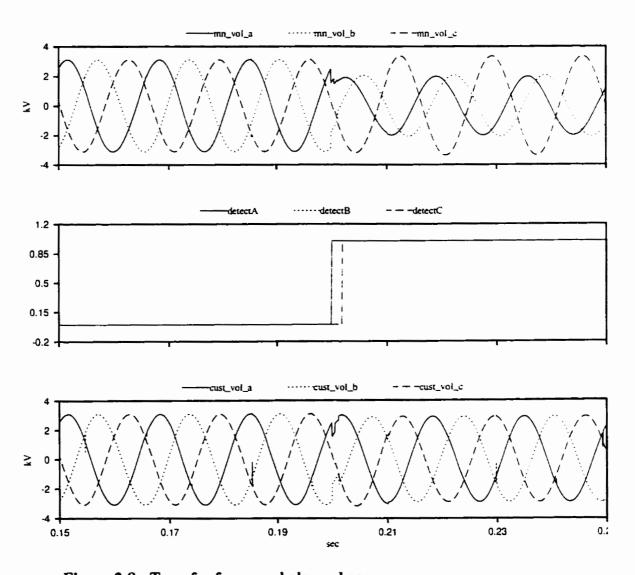

#### 2.3.2 Response to Unbalanced Sag

Figure 2.8 shows the result of applying an unbalanced 90% sag, by putting a S\_L\_G fault on a parallel feeder. It can be seen that while the affected phase transfers almost instantaneously, the unaffected phases (phase C) are made to transfer only at a current zero, to reduce thyristor stresses.

Figure 2.8: Transfer for an unbalanced sag

#### 2.4 MAKE BEFORE BREAK OR BREAK BEFORE MAKE

#### 2.4.1 Problem with Mechanical Breakers

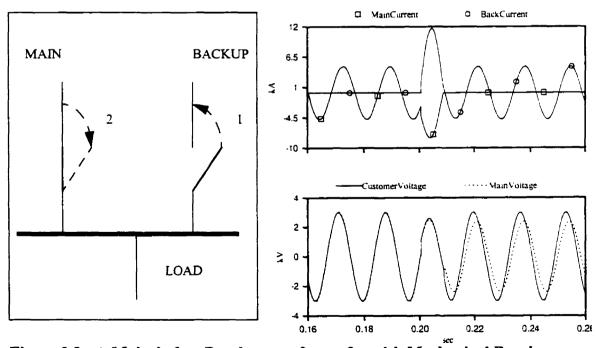

The type of transfer logic used for the Transfer Switch is a make-before-break transfer in which the main feeder is disconnected only after the alternate feeder is switched. This type of transfer is known to cause the least amount of transient in the customer voltage [11]. If mechanical transfer switches were used with a make-before-break type of transfer, there could be a high momentary short circuit through the breakers. This short circuit current increased with increase in the phase difference between the two feeders and could be quite severe.

Figure 2.9: A Make before Break type of transfer with Mechanical Breakers and a 30 degree phase difference

This problem could be avoided if the type of transfer is changed to a break before make type of transfer wherein the load is disconnected from both systems momentarily before switching it onto the backup feeder, after phase monitoring, if necessary. But this, of course, distorted the voltage at the customer bus for a long period which is not the aim of Custom Power.

Figure 2.10: A Break before Make type of transfer with Mechanical Breakers and a 30 degree phase difference

#### 2.4.2 Advantage of Intelligent Polarity Selection with SSTS

The advantage offered by thyristor based breakers is that there is no single bi-directional breaker per line but there are *two* opposite polarity thyristors which form one breaker. Each thyristor conducts only for half a cycle at the maximum while the voltage across it is

a forward bias and stops conducting in the other half when the current through it reaches zero. This makes it possible to achieve a degree of freedom per half cycle, which can be used advantageously to eliminate short circuit currents through the thyristor breakers.

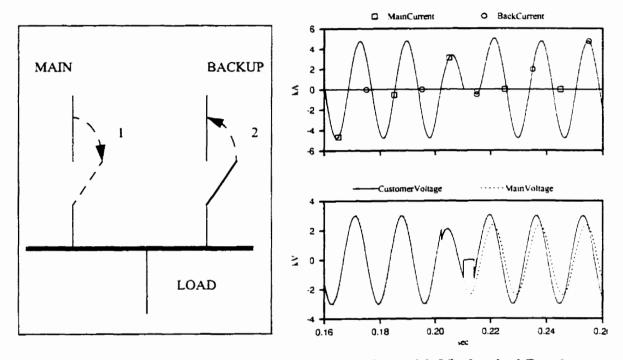

Figure 2.11: Make before Break type of Transfer with SSTS

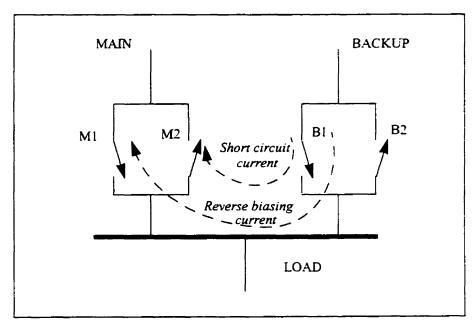

If there is a make before break type of transfer performed with a thyristor based transfer switch, (Figure 2.11) and if we use a transfer logic whereby M1, M2 and B1. B2 are both either on or off, as in the mechanical breakers, we can see that there are two types of currents that can flow per half cycle. A momentary reverse bias current flowing due to the sag on the main feeder which is necessary to turn off the thyristor (say M1) on the main branch. And a momentary short circuit current which would flow through B1 and M2 at high phase differences between the main feeder and the backup. (This current would not flow if there is no phase difference as M2 would not be conducting in the half cycle that M1 would be conducting in).

Thus this short circuit current can be easily avoided if we completely ensure that M2 is never on when M1 is on - even at high phase differences- which can be easily had by not issuing a pulse to M2 when there is a pulse for M1. Thus even if M2 may become forward biased at large phase differences, it will not conduct since there is no firing pulse for it. This method of polarity selection ensures that there is absolutely no short circuit current through the breakers at any phase difference between the feeders.

Figure 2.12: A Make before Break type of transfer with an SSTS and a phase difference of 30 degrees between the main and the backup source

#### 2.4.3 Response to Induction Motor Load

For loads such as induction motors, the dynamics during transfer also depend on factors

such as motor residual voltage and phase angle between this voltage and the power supply voltage and a mismatch between them may induce abnormally high inrush currents and shaft torques[11]. These high currents may again aggravate a sag during transfer. Thus even if a Make before Break type of transfer is possible with a SSTS, it may not be the best logic for an Induction Motor load.

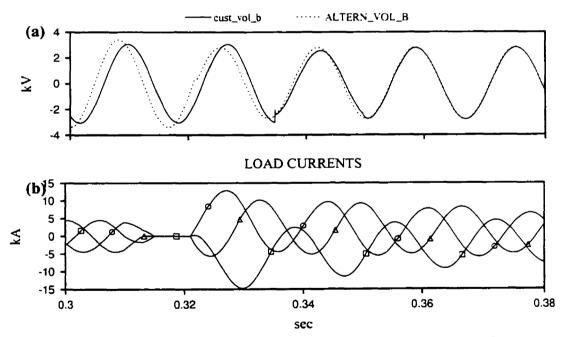

Figure 2.13 shows some results that are obtained with an induction motor load of 3000HP transferred to an alternate feeder at 30 degrees phase difference with the main feeder.

Figure 2.13: Make before Break Transfer for Induction Motor load

It is seen that the customer voltage gets minimum distortion due to the main source voltage, but it draws very high inrush currents(Figure 2.13(b)) on being re-energised by a voltage at a high phase difference (around 70 degrees). These currents may be so high that they can cause an additional sag.

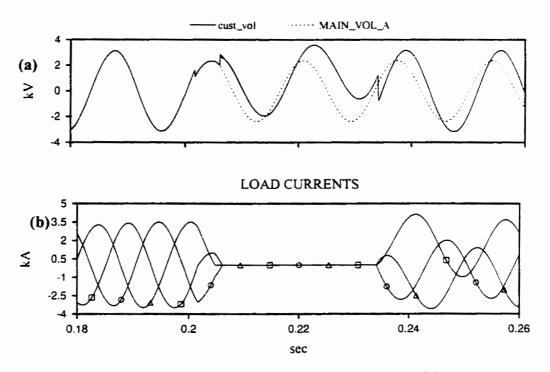

Figure 2.14 shows the possible advantages of allowing the induction motor bus to develop certain voltage and phase characteristics of it's own and closing the alternate feeder switch only if the phase difference is within 10 degrees. The load currents drawn are reduced significantly as shown in Figure 2.14 (b).

Figure 2.14: Break before Make transfer for an Induction Motor load

Issues regarding the Induction Motor load have different schools of thought [11], [21]. The decision for a Make before Break type of transfer or the reverse, for such a load, shall have to be made only after a complete analysis of the particular load behaviour.

#### 2.5 THE SOLID STATE BREAKER AS A FAULT CURRENT LIMITER

#### 2.5.1 Introduction

The present-day ac networks have an increasing level of short circuit faults. This is due to addition of system interconnections, paralleling of generation or increased loading[13]. Therefore, it sometimes happens that the level exceeds the ratings of the switchgear installed on the line and jeopardises protection operations during faults. Fault current limiters are, therefore, used upstream, to interrupt the fault and limit it to the protection level of the downstream protection devices. They only allow sufficient current to initiate downstream breaker operations. They can also be used in cases where an essential load has to be supplied. A Bus -tie Switch can be taken to be a special case of a Fault Current Limiter without the Current Limiting option.

The typical fault current limiter consists of an overcurrent fuse in parallel with a current diverting reactor. The fuse blows within 1/4 th of a cycle of the fault and diverts the current to the reactor. Fuses are limited in rating to 27 kV and have to be manually replaced.

## 2.5.2 Topology of a SSB-FCL

The SSB is connected directly in series with the line and is capable of providing sub-cycle interruptions(<1ms) on faulty feeders [1].

Figure 2.15: A Solid State Breaker with a Fault Current Limiting unit

The GTO provides rapid interruption capability. During normal value of load currents the GTO branch works like a short circuit, but if the value increases beyond a certain preset level, the control circuitry switches off the GTO modules. Current immediately gets transferred to a parallel thyristor switch module with a current limiting reactor. A resistor could also be used at the risk of higher thermal losses.

The benefits of GTOs is that they are capable of instantaneous turn off with negligible delay on application of a appropriate gate signal. Since the general view of protection equipment for the distribution class is of 15kV, 600 A (with fault currents of value greater than 6kA) [12], a 3 kA rated GTO has sufficient margin to detect and turn off at the fault current. It thus provides an interruption at the first fault loop itself and eliminates the complexities of trying to introduce a high impedance at the very first loop [14], as

would be the case if current limitation is attempted using the typical Moulded Circuit Breakers with the resultant arc complexity [14]. Here, there is no attempt to insert the reactance until the current has been brought to zero.

But the GTO cannot carry the fault current for greater than 1 cycle due to its limitation of rating (a di/dt of 500 A/us). It is, therefore, difficult to use the SSB by itself in a practical electrical system, where the device has to coordinate with slower downstream protection systems. Except for a bus -tie location where protection coordination is not required, a SSB has to carry the fault current for a limited period of time till the slower breakers downstream are actuated and the fault is cleared [12]. A survey conducted by EPRI[12] indicated that the current interrupting device has to be able to conduct fault currents for about 10-15 cycles repeatedly for 3-4 times, consistent with the fault clearing sequences of existing distribution reclosers.

Therefore the current is transferred to a high inductance shunt branch for the remainder of the fault. The shunt branch can also have back to back thyristors, whose firing can be controlled to further limit the fault currents and thus reduce the size of the reactor used. The ZNO Arrester provides a clamping level of voltage and protects from lightning surges. Further, this design also responds to source side faults on a bus -tie situation, where there is source capacity on both sides [12].

Some considerations that are to be addressed while incorporating this device are:

1. The detection method should be almost instantaneous and should recognise both symmetrical and asymmetrical faults.

- 2. The breaker should not contribute to "nuisance tripping", hence, it should be closely tuned for all possible maximum transients by loads such as switching of capacitors and starting of induction motors.

- 3. It should be able to coordinate with the slower downstream protection devices.

- 4. The reactor should not cause any resonances with any capacitor banks.

- 5. There should be a reclosing option.

#### 2.5.3 Controls for the Fault Current Limiter

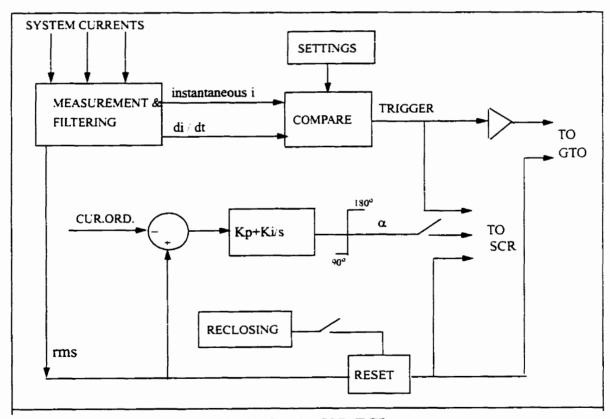

Figure 2.16: Basic Control Blocks for the SSB-FCL

Detection of a fault is based on both overcurrent measurements and measurement of di/dt.

Continuous instantaneous values are recorded and the SSB can be set to operate at any

point on the waveform. Operation is instantaneous and can be achieved in approximately 1/4th of a cycle.

Comparison of the rms value of the load current with the current order is used to generate a value of the phase control angle  $\alpha$  for the thyristors;  $\alpha$  is kept between 90° and 180°, to achieve symmetrical firing in the inductive thyristor branch. Though it is the reactor which primarily limits the fault current, the alpha modulation by thyristors also helps in reducing the rms values of the current and thus the cost of the reactor.

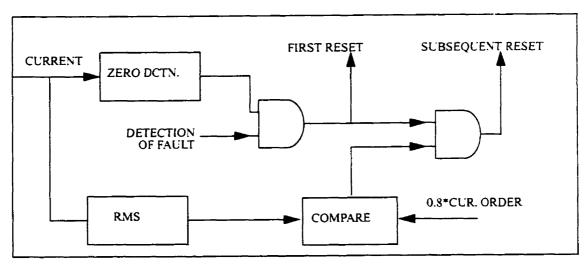

Resetting could be done by considering the rms value of the current, where, once the fault is cleared the total current is less than the current order for at least one cycle. Automatic reclosing for transient faults is offered as a separate option and is controlled by detection of the first zero crossing of the current as shown in Figure 2.17.

Figure 2.17: Control Algorithm for Automatic reclosing mode

#### 2.6 RESULTS OF SIMULATIONS

# 2.6.1 The Simulation System

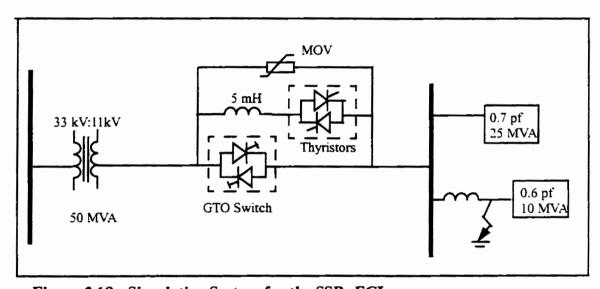

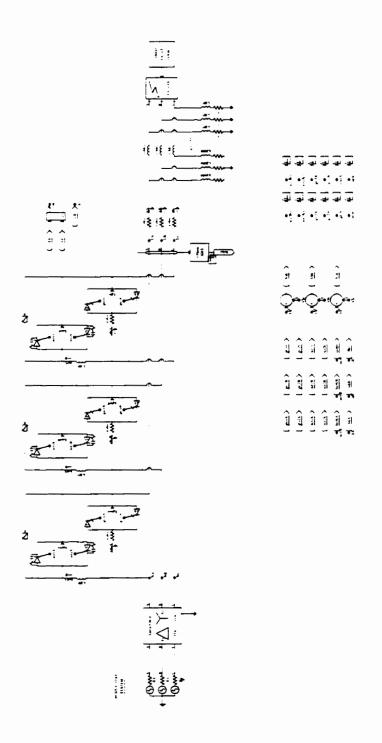

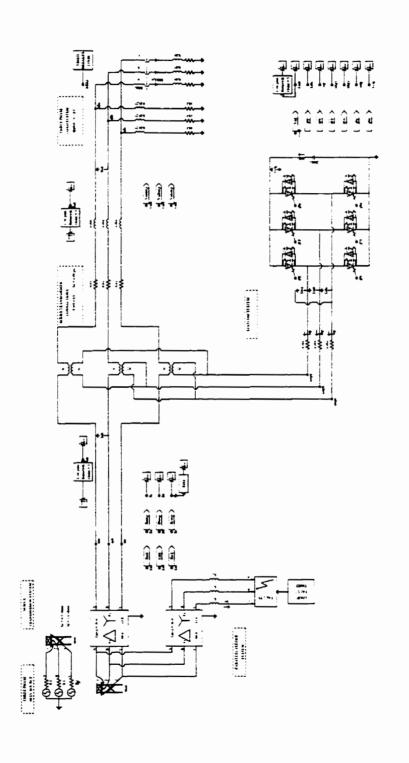

Simulations were performed on a 11kV/50 MVA system as shown below in Figure 2.19.

Figure 2.18: Simulation System for the SSB-FCL

Faults were applied on the load side and a fault level of 6 kA was obtained. The detailed PSCAD circuit is shown in Figure 2.19.

#### 2.6.2 Response of the Breaker

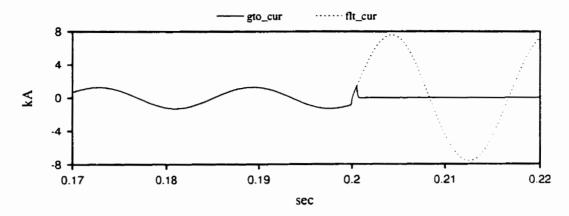

Though the SSB is never used by itself, except in a Bus Tie position [1], this result is used to illustrate the swift action that can be brought about by the GTO branch. A fault current level of 6.0 p.u. is chopped down to zero within 1/4th of a cycle as seen in Figure 2.20.

Created: February 23, 1997 (leena)

Last Modified: August 31, 1998 (leena)

Printed On: August 31, 1998 (leena)

Subsystem #1 of 3

188

University of Manitoba, EE Dept. Solid State Breaker with fault current limiter

Figure 2.20: GTO Switch Operation during Faults

# 2.6.3 Response with Current Limiting Reactor

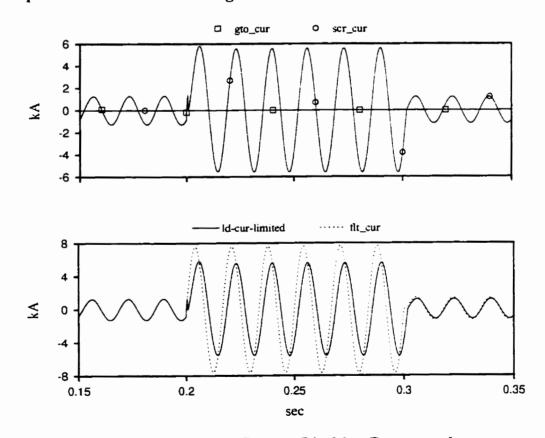

Figure 2.21: Response with Current Limiting Reactor only

After the GTO switch brings down the current to zero, the resultant surge of high voltage developed across it forces the current through the parallel current limiting reactor (scr\_cur

in Figure 2.21) and thus reduces it to around 4 kA from the 6 kA fault level. The high voltage is clamped to a protection level by the MOV.

## 2.6.4 Response with Current Control by Thyristors

Figure 2.22 shows current controlled to 1 kA. Without α control, the fault current was just limited by the impedance imposed by the reactor alone, and it is seen to be around 4 kA.

Figure 2.22: Load current waveforms with current modulation loop

It can be seen that with r.m.s. control for the thyristors, there is a delay of one cycle before the current settled to its new current order. It can also be seen in the first cycle of the fault that the fault current was momentarily zero - specifically for the time the gto controls were solely in operation and had brought down the current to zero - before the thyristor control loop took over. The initial upswings in the currents shown in Figure 2.22 above is because the thyristor loop began in a fully conducting state ( $\alpha = 90^{\circ}$ ).

# 2.6.5 Response to Transient Faults

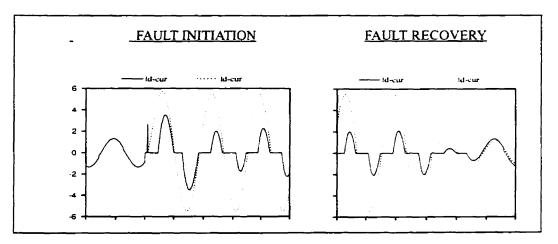

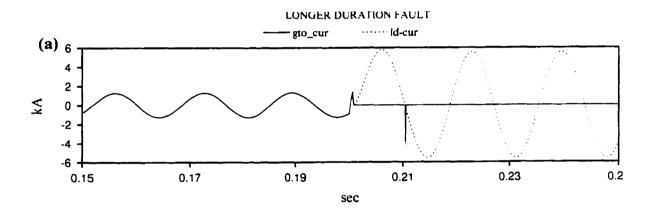

The fact that the thyristor can only be switched off at a natural zero, brings in a delay of one cycle for reclosing. Reclosing can, at best, be had at the first current zero. This is offered as a separate option. Figure 2.23 (a) shows the working of the SSB-FCL in the automatic reclosing mode for a normal fault, where after a single recloser, the Breaker detects the fault again and operates. Figure 2.23(b) shows it working for a transient fault wherein it gets resetted after a cycle.

Figure 2.23: Response of the SSB-FCL in the Automatic Reclosing Mode

#### 2.7 CONCLUSIONS AND FUTURE WORK

Some applications of the Solid State Breaker have been presented in this chapter. Control algorithms to address the various issues in using the Solid State Breaker as a Transfer Switch and as a Fault Current Limiter have been developed. The advantages offered by thyristors over mechanical breakers in a Make before Break type of transfer have been presented. A control scheme for instantaneous detection of voltage sags has been developed. The importance of current zeroes while working with thyristors has been highlighted.

It has been shown that a GTO based Solid State Breaker, when used online in a system within its ratings, can achieve instantaneous current interruption. This can then be used in a Fault Current Limiter to immediately insert a high inductance in series with the line and limit the fault current. With an additional thyristor based current limitation, it can be shown to reduce the rating of the reactor used in a typical Fault Current Limiter.

Future work would involve analysing the effects of particular loads such as capacitors and induction motors on the operation of these devices.

## Chapter 3

# THE SERIES POWER FLOW CONTROLLER

#### 3.1 INTRODUCTION

This chapter analyses the use of the STATCOM as a Series Power Flow Controller (SPFC). The ability of the STATCOM to generate fast, precise and complex voltage shapes is exploited for various functions such as controlling dynamic power flow. injecting compensating harmonics or even injecting a voltage boost. This chapter studies the use of the SPFC for series reactive compensation.

Reactive compensation by a SPFC in distribution systems can be considered for improving voltage regulation in long distribution lines, as in the rural distribution systems. But since the basic SPFC is used to control the power flow in a line [15], [16], [18], it is first studied here for dynamic power flow control at subtransmission levels, by reactive compensation. The model is then used for voltage regulation, as discussed later in the chapter.

### 3.2 SERIES REACTIVE POWER COMPENSATION

#### 3.2.1 Basic Theory of Series Reactive Compensation

The SPFC, in its most basic form can supply continuously variable series reactive power

to the distribution line. The theory for series reactive power compensation can be illustrated by the following simple analysis.

The power transmitted through a transmission line can be approximately written as

$$P = \frac{(VsVr\sin\delta)}{Xl}$$

where Vs = the sending end voltage

Vr = the receiving end voltage

XI = the series inductive reactance of the line

$\delta$  = the load angle

If part of this series inductance XI, could be cancelled out by a series capacitance, the power flow in the line can be increased by a factor

$$Xl / (Xl-Xc)$$

where the current is

$$I = \frac{Vs - Vr}{jXl - jXc}$$

and the power transferred can be increased for the same load angle.

This method of increasing power transfer through a line is well known and is typically achieved with the use of series capacitors. The series capacitors are also controlled by thyristor switches (TSC) to vary the capacitance inserted in the line. But the problems with these devices viz. potential resonances with shunt reactors or alternators, switching transients/ overvoltages, reactive power flow control by step changes of capacitance only, make the series capacitors option more difficult for fast dynamic power flow control.

# 3.2.2 Advanced Static Series Compensation

The Advanced Static Series Compensator, instead, makes use of an injected *voltage* of arbitrary magnitude, frequency and phase, which can affect the power flow along the line.

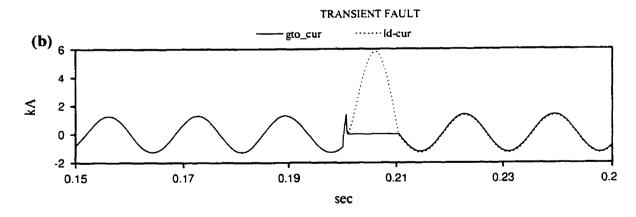

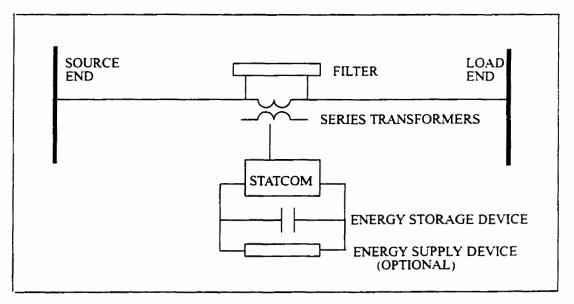

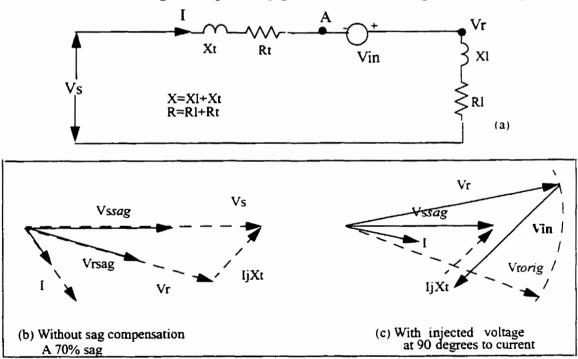

The voltage could be obtained from a Voltage Source Inverter and the series connection could be obtained by a series transformer. Details of the topology are discussed further in this chapter in Section 3.3, but the basic concept can be seen in Figure 3.1.

Figure 3.1: The Basic SPFC

Though the phase of this inserted voltage can be controlled to any arbitrary angle, for purely reactive power compensation, this voltage has to be at 90 degrees to the line current in the steady state.

As compared to a capacitor for series compensation, the SPFC is an attractive alternative as it is unlikely to cause resonances with passive components of the system. The size of

the capacitor required here for transitory energy storage is much smaller than that required for series capacitors. The dynamic performance is also tremendously improved.

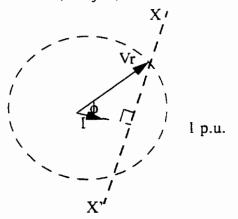

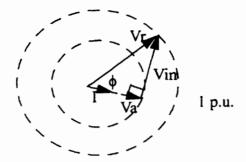

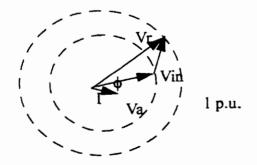

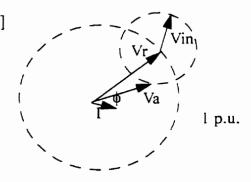

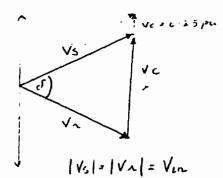

# 3.2.3 Phasor Diagrams

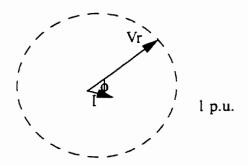

If we have a transmission line connecting two strong sources with equal voltages and a constant phase angle  $\delta$  between them, and if we connect a series power flow controller which injects an arbitrary voltage in quadrature with the line current such that

$$V_{spfc} = \pm j \cdot X_{spfc} \cdot I$$

in Figure 3.2 below,

Figure 3.2: Series Power Flow Control by Voltage Insertion

We can write the current to be

$$I = \frac{Vs - Vr}{jXl \pm jX_{spfc}}$$

Thus it is seen that the magnitude of the current (and hence the real power flow) can be controlled by the magnitude of the constant " $X_{spfc}$ ", which could be achieved by a Voltage Source Inverter. It has to be noted here, though, that the Voltage Source Inverter offers

only the voltage  $V_{spfc}$  for controllability and that there cannot be a direct control of  $X_{spfc}$ , as in the capacitor, unless the line currents are continuously measured. The power flow equations then differ, as shall be discussed in section 3.2.4.

The magnitude of the inserted voltage is limited by the rating of the device, or the dc link voltage of the inverter and the turns ratio of the series transformer. Since the inserted voltage is in quadrature to the current, it does not draw any real power. It affects the real power flow along the line by changing the magnitude and phase of the line current.

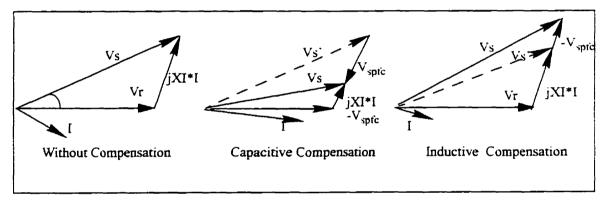

Figure 3.3: Phasor Diagrams for Series Power Flow Control

It can be seen from Figure 3.3 that the inserted voltage  $V_{spfc}$  is always in quadrature to the line current, either decreasing the line inductance (capacitive compensation) or increasing it, as in inductive compensation. Inductive compensation is not generally needed, but could be used in fault current limiting situations [1]. It could also be effectively combined with a fixed capacitor to provide a wide range of compensation at reduced sizes [15]. It can also be inferred from the phasor diagrams that there could be no power flow control by purely series reactive compensation if Vs and Vr are in phase, as can be done with a Phase Angle Regulator [15].

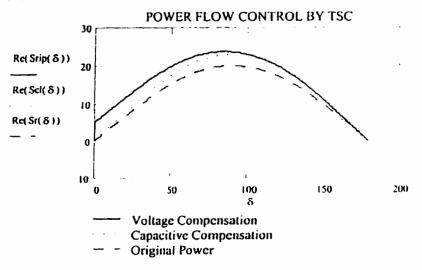

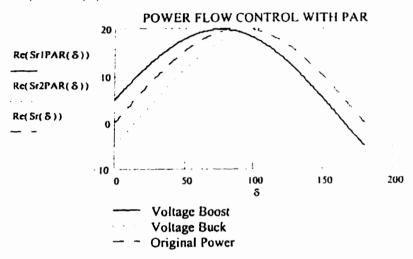

## 3.2.4 Comparison of Various Series Controllers

As an exercise, the operating characteristics of various series power flow controllers were compared for the same value of voltage insertion.

The devices selected are a Fixed Series Capacitor, a Thyristor Switched Variable Series Capacitor (TSC), a Phase Angle Regulator (PAR) and the Series Power Flow Controller (SPFC).

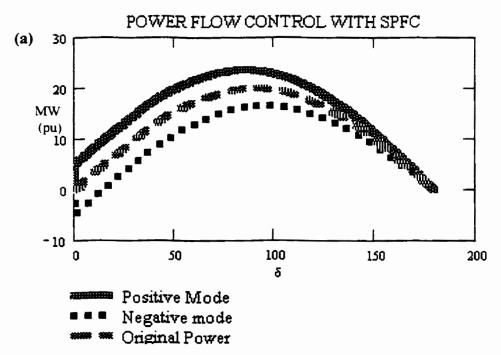

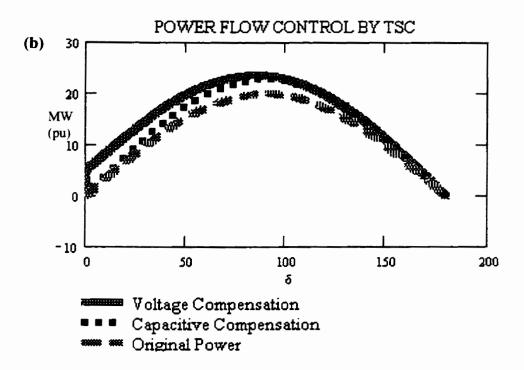

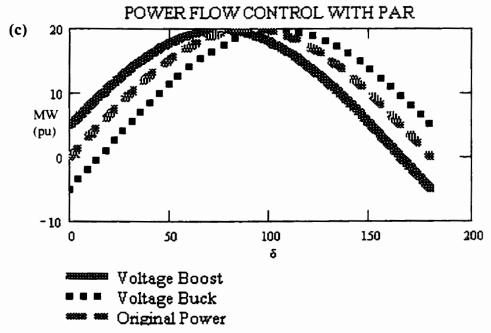

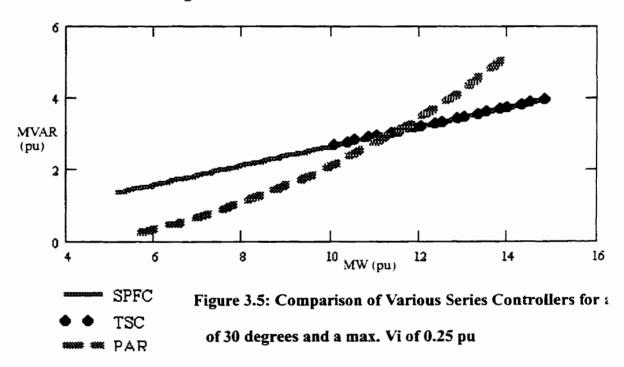

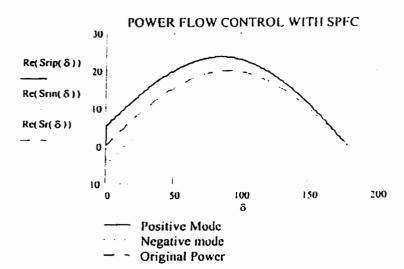

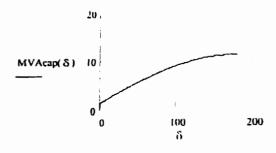

An example system of a 100 MVA transmission system with 100 kV sending and receiving voltages and a inductive reactance of Zl = j0.05 pu is used. Details of the calculations are to be found in Appendix A, but the final power control characteristics for each device. with respect to the load angle ( $\delta$ ) can be seen in Figures 3.4 (a), (b) and (c) below.

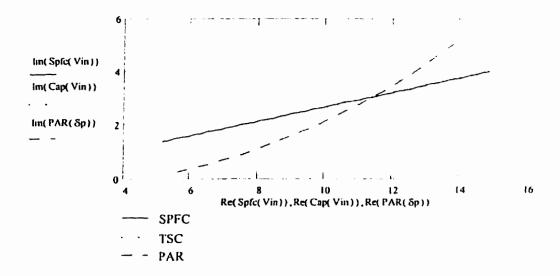

Figure 3.4: Comparison of Series Power Controllers for Various Load Angles (δ)

Figure 3.4: Comparison of Series Power Controllers for Various Load Angles ( $\delta$ )

.

The three devices were compared on the basis of equal voltage insertion in the line. It can be seen from Figures 3.4(a) and (c) that both the SPFC and the PAR can offer either an

increase or a decrease in power, at any load angle. The TSC will not be able to perform this unless it is biased by inductors. Furthermore, the capacitors are also additionally limited by their ratings, based on the worst line current that may be expected to flow through them. If this is taken into consideration, the nature of power flow characteristic will change, as shown as "Capacitive Compensation" in (c).

The three devices can also be compared [Appendix A] for a fixed load angle (say, 30°) and the result can be seen in Figure 3.5.

The series capacitor here, is again assumed to have sufficient MVA to allow constant Vi at any load angle.

There are two caveats to be noted in series reactive compensation. For a line with a lower X/R ratio, increase in current by reactive compensation may lead to an increased drop across the resistance, which is not compensated [17] and further, there may be dangers of overvoltages at higher levels of compensation.

## 3.3 THE TOPOLOGY OF THE SERIES POWER FLOW CONTROLLER

## 3.3.1 The STATCOM Configuration

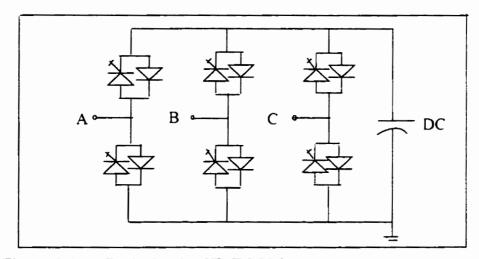

The Voltage Source Inverter used here is a Basic 6 pulse STATCOM. Multipulse configurations can be considered for better harmonic performance.

Figure 3.6: A Basic 6 Pulse STATCOM

A 6 pulse STATCOM consists of 6 solid-state switches - here, self-commutated GTO switches- with anti-parallel diodes (Figure 3.6). The firing of each can be controlled to generate a set of three alternating voltages at terminals A, B and C, with controllable amplitudes, phases and frequencies. The capacitor is kept charged to provide the dc stored energy, when necessary.

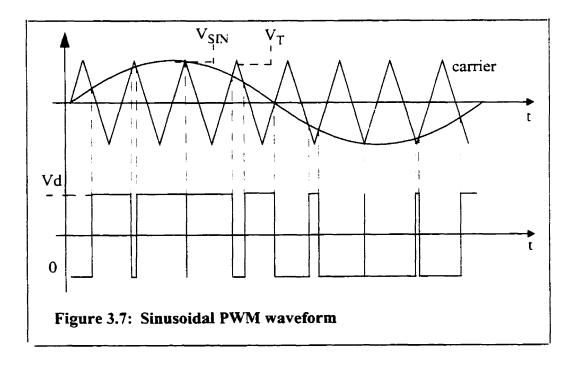

A sinusoidal pulse width modulation technique [2] is used to control the upper and lower arms of each branch; the PWM switching pattern is determined through the comparison of

a sine wave with a synchronised, high frequency triangular wave. A carrier frequency of 900 Hz. is employed. Neglecting the harmonics, the value of the fundamental voltage (peak) obtained is

$$V_{AN} \angle 0 = \frac{1}{2} \times ma \angle 0 \times Vd = \frac{1}{2} \times \frac{V_{SIN} \angle 0}{V_T} \times Vd$$

and so for phases BN and CN.

where ma = modulation index

= ratio of peak of modulating signal  $(V_{SIN})$  to peak of carrier signal  $(V_T)$ .

The instantaneous value of the output voltage is determined by the magnitude of the modulating signal with respect to that of the carrier, which can be controlled and the dc capacitor voltage Vd, which is kept constant. The instantaneous phase is determined by the phase of the modulating signal, which can be also controlled.

#### 3.3.2 The Transformer and Filters

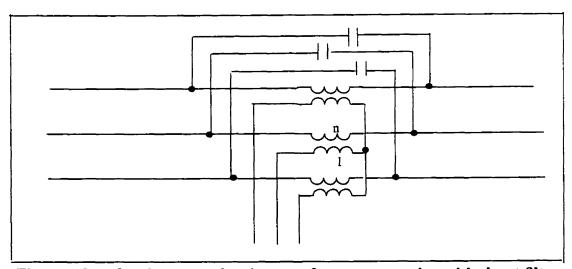

When this voltage is applied in series in the line via an injection transformer, its magnitude is scaled according to the turns ratio (n) of the transformer. Further, the intratransformer connections on the STATCOM side and their polarity also has a bearing on the performance [16].

A floating Y connection [Figure 3.8] with a dc voltage of Vd, gives a primary side peak phase voltage of  $(n \cdot ma \cdot Vd/2)/\sqrt{3}$ , while a delta connection with the same dc voltage gives a primary voltage of  $n \cdot ma \cdot Vd/2$  but has increased line currents on the secondary side. A delta connection prevents zero sequence currents from entering the STATCOM and thus protects it from system faults. Further, three single phase STATCOMs give the best performance in terms of harmonics produced [16], but they involve at least 12 switches, as compared to 6 switches for a three phase type. Therefore, the type of transformer connection shall be decided by an optimization of needs and limitations.

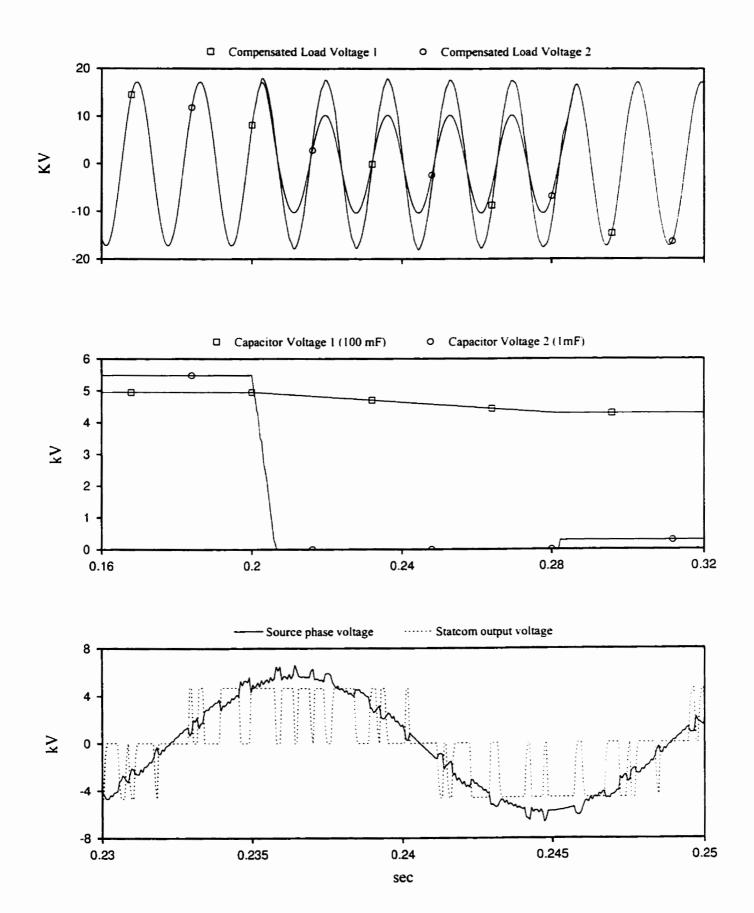

Figure 3.8: A floating neutral series transformer connection with shunt filters

Harmonics could be filtered using passive LC circuits where the L is supplied by the transformer inductance [19]. Significant harmonics are not expected as a suitable PWM firing scheme can be designed (Section 3.3.1). With a switching frequency of 15 \* $f_o$ ,  $f_o$  being the fundamental frequency of 60 Hz, the major harmonics expected were at 14, 16, 29, 31..., or " $f_o \pm 1$ ,  $2f_o \pm 1$  ..." [2].

For a low modulation index like 0.2, the value of these harmonics could be as high as 1.24 times the fundamental, but they decrease with higher values of modulation index to around 0.6 Vo [2]. Also, the amount of distortion in the load voltage is almost negligible, as can be seen from Figure 3.9. which is at a low modulation index of 0.3.

Figure 3.9: Fourier Analysis of Voltage Waveforms obtained in a SPFC operatio

With such considerations, no filters were used in the simulation system and some complexity was reduced.

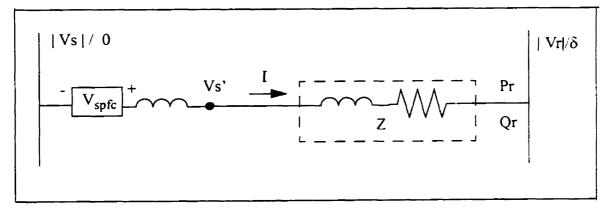

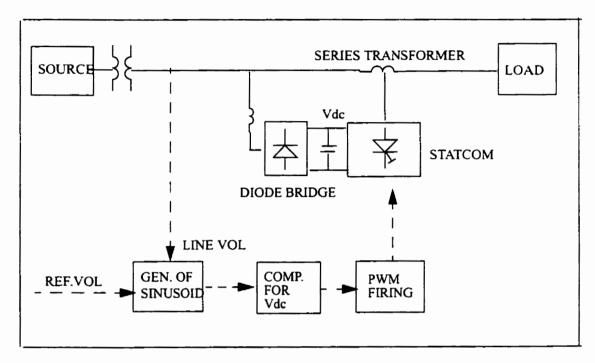

### 3.3.3 STATCOM Controls for the SPFC

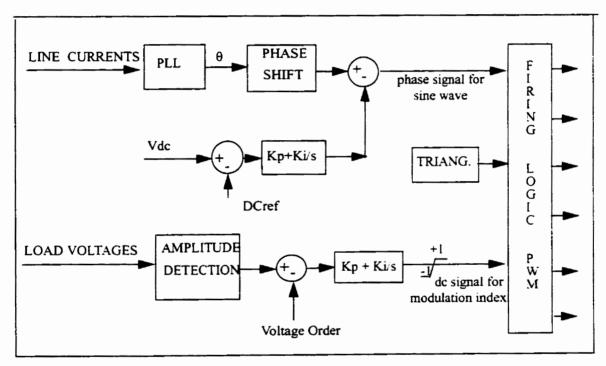

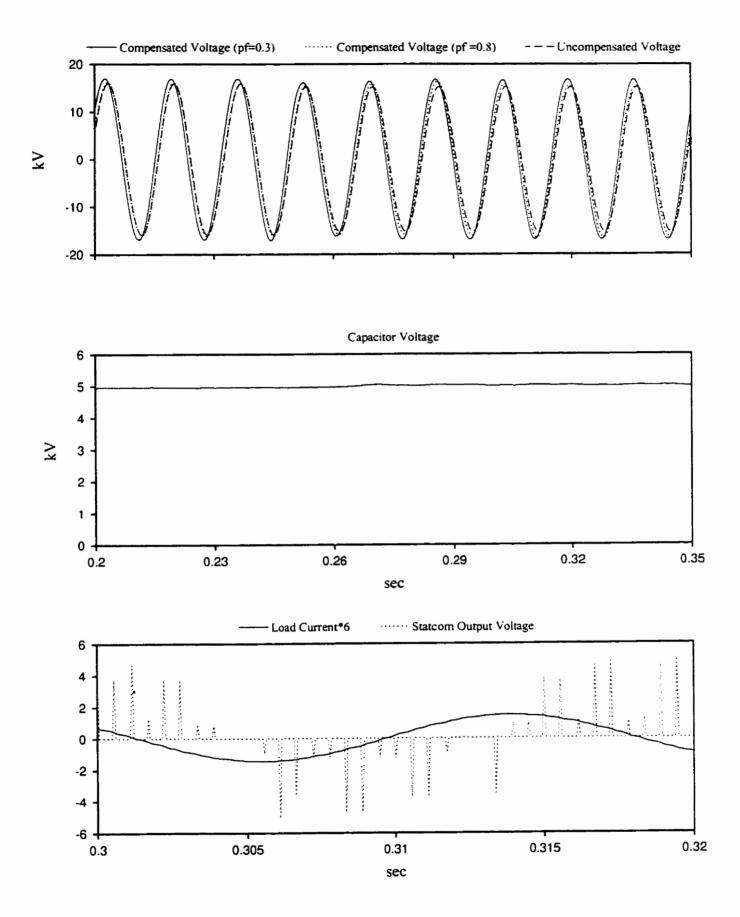

Figure 3.10: Block Diagrams of the SPFC-STATCOM Controls

The line currents are used for synchronisation, as they are ones with the least distortion during SPFC operation and the reference for firing can be easily generated with respect to the line currents. For low PWM switching frequencies, even the triangular signal is kept synchronised to reduce harmonics [2].

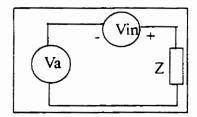

The phase of the output voltage of the STATCOM is controlled by adding a phase shift to the phase of the line currents. The charging and discharging of the capacitor is taken to be an indication of real power exchange and therefore the change in dc voltage is fed as an error signal to the phase control. A PI controller drives this error to zero such that the dc voltage is restored to the reference value and the STATCOM voltage is held at almost 90° to the current, except for small differences to compensate for losses [18].

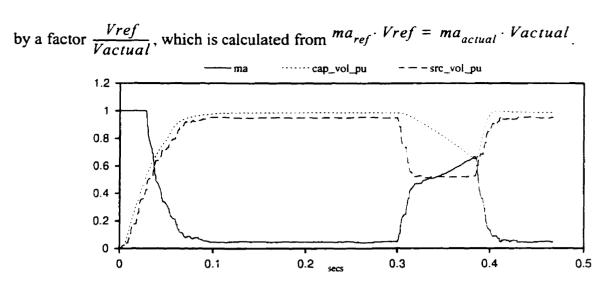

The main power loop is driven by a Real Power signal, computed from instantaneous values of the line currents and voltages and filtered. This is compared to a Power Order and the error is fed through a PI controller as the modulation index (ma), defined in Section 3.3.1. Inductive or capacitive compensation is generated automatically as the polarity of the index changes with the change in the type of compensation required. A hard limit is placed at ma =1, though overmodulation could also be considered [19].

The two PI control loops are decoupled by different time constants, with the DC control loop being much slower. Further, the change in polarity of the index is fed to the gains of the DC Control loop to change the direction of control with a change in polarity of required compensation. The voltages injected are always maintained balanced and synchronised to the positive sequence of the currents.

#### 3.3.4 The Transmission Line System for Simulations

The SPFC is placed at the midpoint of a 200 km line with equal sending and receiving end voltages of 66 kV, with a base short circuit MVA of 300 and a load angle of 30 degrees. The sequence parameters of the line are as below.

| PARAMETERS    | R(Ω/km) | L(Ω//km) | C(MΩ km) |

|---------------|---------|----------|----------|

| Pos. sequence | 0.02430 | 0.1219   | 400.0    |

| Zero sequence | 0.12    | 0.18     | 410.0    |

The size of the capacitor was kept  $10000 \,\mu\text{F}$  to reduce the ripple content. The dc link voltage was maintained to 8 kV by rectification from the line.

Mam System

October 14, 1993 (kurs3) September 21, 1998 (leenu) September 21, 1998 (leena)

Created: Last Modified: Printed On:

THE SERIES POWER FLOW CONTROLLER University of Manitoba, EE Dept.

Subsystem #1 of 2

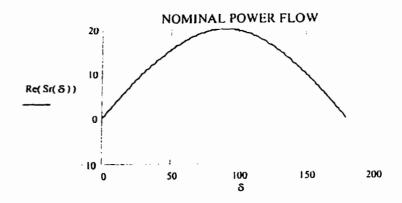

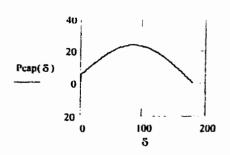

Using methods outlined in Appendix A, the nominal power flow and the expected range of increase in power is shown in Figure 3.12. The nominal line power at  $\delta=30^{\circ}$  is 87 MW. The maximum voltage that can be injected with a transformer turns ratio of 6.0 / 5.0 kV and a dc voltage of 8 kV is  $\left[\sqrt{3} \cdot \frac{(1 \cdot 8/2)}{\sqrt{2}}\right] \cdot \frac{6}{5} = 5.88$  kV r.m.s. and the rating of the SPFC is 18 MVA.

Hence maximum increase in power at any given load angle is shown in Figure 3.12.

Figure 3.12: Range of Power Flow Control for the 66.0 kV line

Here Pnormal( $\delta$ ) is the nominal line power at that load angle. Pspfc1( $\delta$ ) and Pspfc2( $\delta$ ) show the maximum increase or decrease in power that can be brought about by the 18 MVA SPFC at that load angle. Pcontrol( $\delta$ ) shows the actual performance of the SPFC controls as the actual value of the power is controlled to that of the Power Order fed to the controls. There could be a greater increase in line power by the same SPFC, if the transformer turns ratio is increased further. But this would also lead to increased currents on the STATCOM side, which is not advisable.

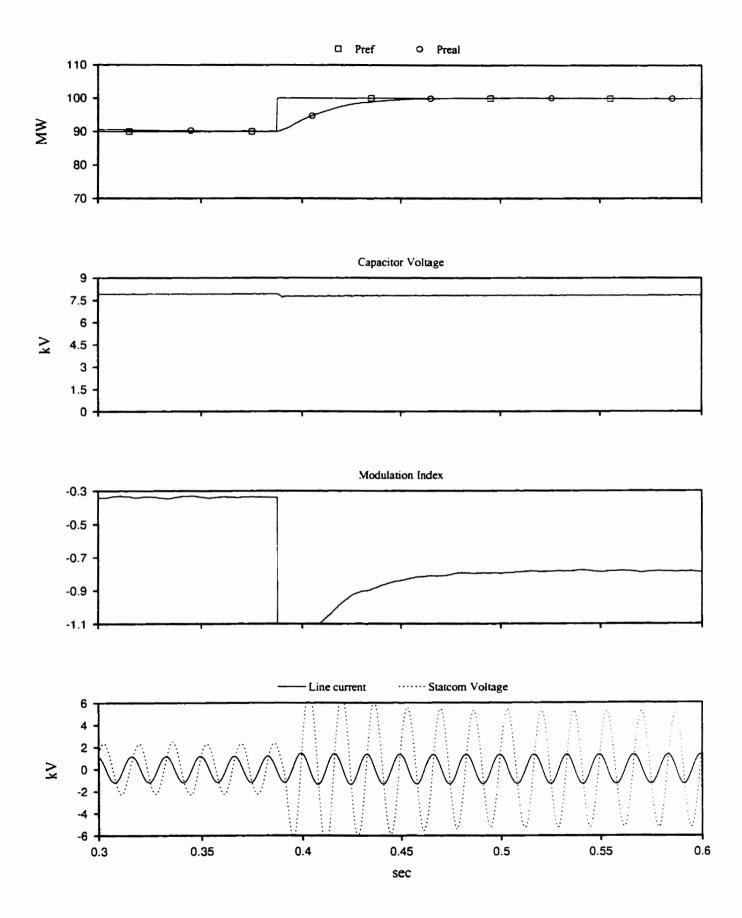

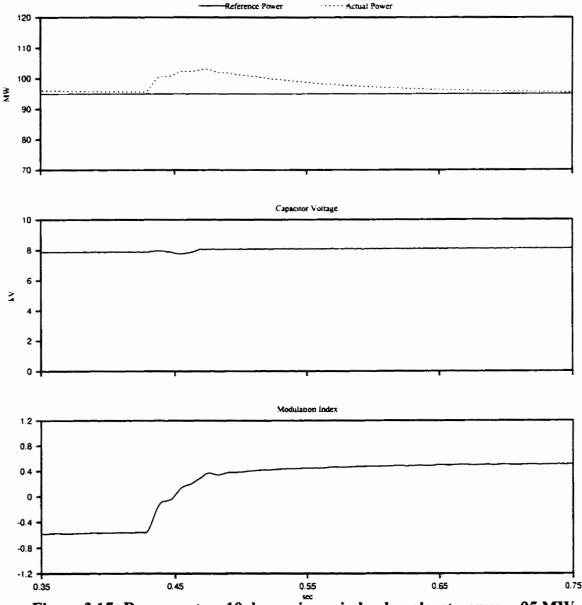

Figure 3.13: Response of the SPFC to a step increase in Power Order

#### 3.4 RESULTS OF SIMULATIONS

### 3.4.1 Response to Step Changes in Power Order

It is seen from Figure 3.13 that a substantial increase in transmission power can be brought about by almost no exchange of real power between the SPFC and the line. The capacitor voltage is steady at 8 kV. There seems to be a slight delay in the catching up of 'Real Power' measured in the line as compared to the Pref, the Power Order in Fig. 3.10. But, as can be seen in the plot of instantaneous line current, the change in line current is much faster. The delay in response of Preal can be attributed to the time constant of the power measurement device. Power control by this 18 MVA SPFC for this line can be had from 105 MW (maximum) to 70 MW (minimum), where 87 MW is the nominal value.

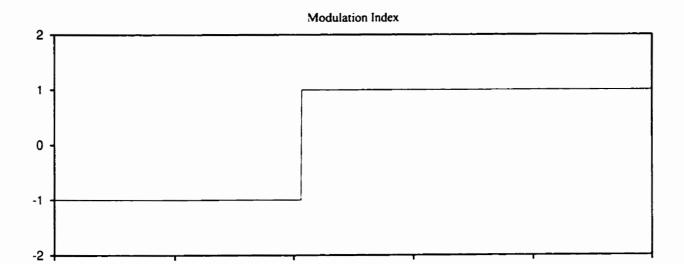

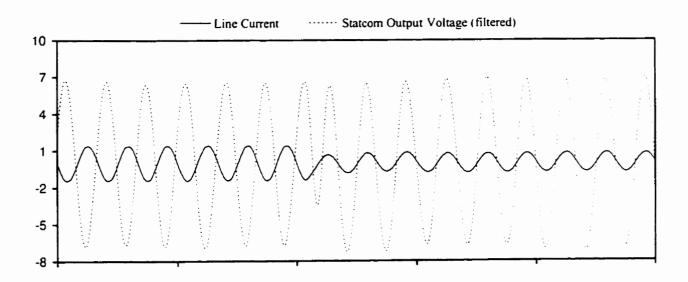

#### 3.4.2 Inductive Compensation

As was discussed earlier, the SPFC can also operate in the inductive region as long as it is purely a reactive device. Since the normal operating point is Po = 87 MW, any decrease in power would have to be attained by increasing the impedance in the line by inductive compensation. As is seen in Fig. 3.14, the change from capacitive to inductive is smooth, even if it is from 100% capacitive to 100% inductive. The line current moves from leading the STATCOM output voltage to lagging the STATCOM output voltage, and the power decreases to the minimum of 70 MW.

Figure 3.14: A STEP CHANGE FROM CAPACITIVE TO INDUCTIVE

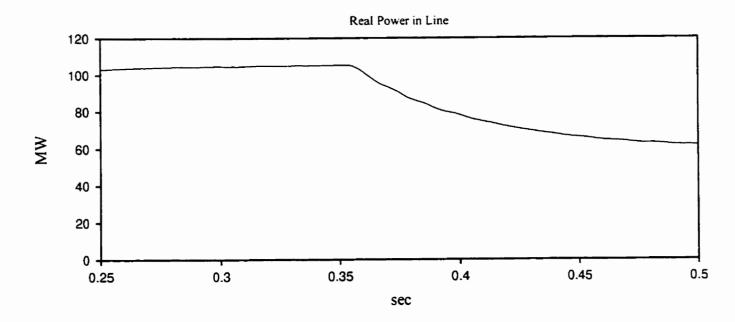

# 3.4.3 Response to a Swing in Load Angle

As a test of the robustness of the controls to system parameters, the load angle was given a step change from 30 degrees to 40 degrees. It can be seen that the controllers are stable and power is brought down to the control order, albeit with a delay in the power measurement transducer.

Figure 3.15: Response to a 10 degree jump in load angle at power = 95 MW

# 3.4.4 Reactive Compensation for Voltage Regulation

As was mentioned earlier, reactive compensation in distribution systems would be of significance only for improving voltage regulation. The voltage at the end of a distributing line is not usually equal to that of the sending end, but is reduced by the amount of voltage dropped across the line impedance. A SPFC can also behave like a series capacitor and reduce the apparent inductive reactance drop in the line and bring back the load voltage to 1 pu or equal to the sending end voltage.

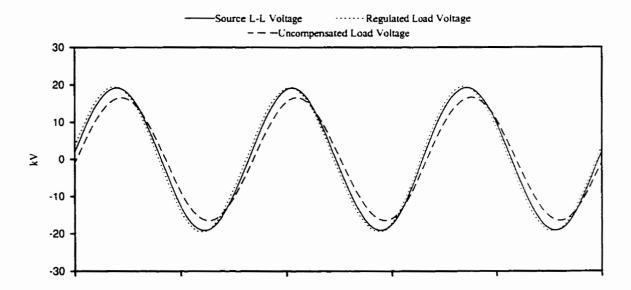

The distribution system used here is a 13.8 kV system with a 20 MVA load of 0.7 pf. The inductive reactance in the line is taken to be an exaggerated 0.38 pu. It can be seen from Figure 3.16 that the load voltage is maintained equal to that of the source.

Figure 3.16: Voltage regulation in a distribution system with a SPFC

The load currents in a distribution system can vary widely from time to time, and the SPFC has to work for voltage regulation at any value of load current. Unlike a capacitor, where the required change in series compensation with load current is naturally brought about [22] - I<sub>L</sub>\*Xc changes with a change in I<sub>L</sub>\*Xl - the series compensation by a SPFC would have to be *controlled* likewise.

This is done by measuring the load voltages and comparing it to a reference voltage, not dependent on load current, and feeding the error through a PI controller to the modulating signal of the PWM firing scheme. As can be seen in Figure 3.17, this control strategy works even for a change in load current.

Figure 3.17: Voltage regulation by a SPFC with changes in the load current

#### 3.5 CONCLUSIONS AND FUTURE WORK

A Series Reactive Power Compensator was presented in this chapter and the controls were designed to achieve successful performance. This device can be effectively used for reactive compensation in longer distribution lines.

This chapter has shown the use of reactive compensation for transmitting increased power in a transmission network and also the use of reactive compensation for improving voltage regulation in a distribution network. Furthermore, this topology can also used to compensate for source side voltage sags. This aspect will be discussed in the following chapter. More work would have to be done for SPFC studies to check for adaptivity of the controller to system side faults. A DQ method of control could be studied for improved speed of response of the system.

#### Chapter 4

# THE DYNAMIC VOLTAGE RESTORER

## 4.1 REQUIREMENTS FOR A DYNAMIC VOLTAGE RESTORER

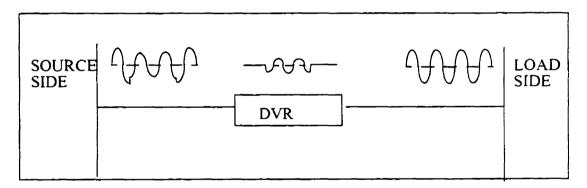

As discussed earlier in Chapter 1, a Dynamic Voltage Restorer is required to inject a controllable voltage of such a magnitude and phase that the voltage at the customer bus suffers minimum distortion if the voltage on the source side suffers a sag.

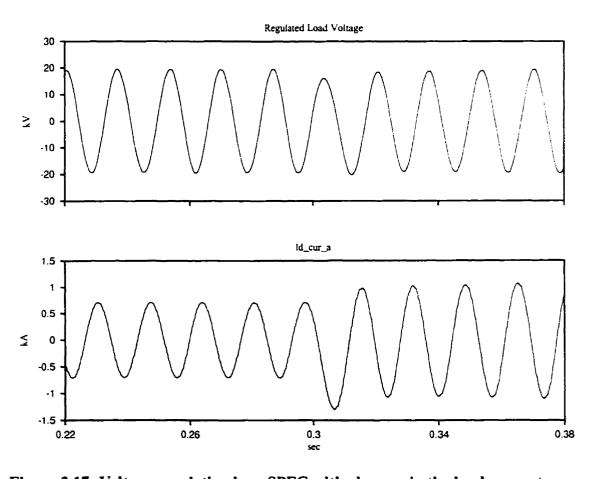

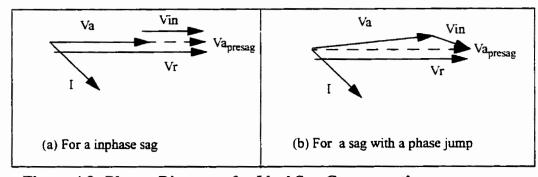

Figure 4.1: Operation of the DVR during system voltage sags