### TRANSIENT IMPEDANCE DISPLAY UNIT

by

JIHAD M. A. RASHID

A thesis

presented to the University of Manitoba

in partial fulfillment of the

requirements for the degree of

Master of Science

in

Electrical Engineering

Winnipeg, Manitoba, 1983

(c) JIHAD M. A. RASHID, 1983 June 29, 1983

### TRANSIENT IMPEDANCE DISPLAY UNIT

BY

### JIHAD M.A. RASHID

A thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements of the degree of

MASTER OF SCIENCE

6 1983

Permission has been granted to the LIBRARY OF THE UNIVER-SITY OF MANITOBA to lend or sell copies of this thesis. to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

To:

Miss Layalee K. Rashid with LOVE

### **ACKNOWLEDGMENTS**

The author wishes to acknowledge his true indebtedness to professor GLEN SWIFT for suggesting the topic and never failing, father style, guidance and support during work on this thesis. Many thanks to professor MAURICE YUNIK, his many suggestions and assistance were of great importance.

The author would like to thank Dr. DOUG CHAPMAN of Manitoba Hydro and professor FRED ZEILER of department of applied mathematics for examining this thesis.

In addition the author would like to express his gratitude to all technical staff in the electronics shop for their help and in particular for Mr. Ken Biegun for building the final design version and the continuous assistance.

Manitoba Hydro and NSERC financial aid is appreciated.

### **ABSTRACT**

In this thesis it is attempted to design an Impedance display device capable of providing a visual display, on an oscilloscope screen, the trajectories of the 60-Hz transient impedance seen at a relaying point during a power system swing. A digital approach is adopted using the Motorola Inc. MC6802 microprocessor. The design is built and tested on a simulated one machine versus infinite bus power system.

# CONTENTS

| ACKNOW | VLEDGMI | ENTS                            |                  | •                   |                 | •                 | •         | •         | •          | •               | •         | •         | •         | •   | •       | •       | •  | •  | •       | • | •  | iv                 |

|--------|---------|---------------------------------|------------------|---------------------|-----------------|-------------------|-----------|-----------|------------|-----------------|-----------|-----------|-----------|-----|---------|---------|----|----|---------|---|----|--------------------|

| ABSTRA | ACT .   |                                 |                  | •                   |                 | •                 | •         | •         | •          | •               | •         | •         | •         | •   | •       | •       | •  | •  | •       | • | •  | v                  |

| Chapte | er      |                                 |                  |                     |                 |                   |           |           |            |                 |           |           |           |     |         |         |    |    |         |   | pa | ge                 |

| I.     | INTRO   | DUCTI                           | ON               | •                   |                 |                   | •         | •         | •          | •               | •         | •         | •         | •   | •       | •       | •  | •  | •       | • | •  | 1                  |

| II.    | POWER   | SWIN                            | IGS              | ANI                 | ) PI            | ROTI              | ECI       | ΊV        | Æ          | RE              | LA        | ΥI        | NG        |     | •       | •       | •  | •  | •       | • | •  | 4                  |

|        | Po      | ntrod<br>Powe<br>wer S<br>mbine | er S<br>Swin     | yst<br>ig I<br>Syst | em              | Re                | lay<br>on | ir<br>R-  | ng<br>-X   | on<br>di        | R<br>aq   | -X<br>ra  | D<br>m:   | ia  | gr<br>• | an<br>• | 1: | •  | ·<br>on | • | •  | 4<br>9<br>14<br>21 |

| T T T  | TRANS   | _                               | R-X:             |                     | י<br>אררו       | <br>E D           | ·<br>TSI  | •<br>>T.7 | •<br>4 Y   | ·               | •<br>IT   | •<br>• D  | ·<br>ES   | ·   | ·       | •       | •  |    |         |   |    |                    |

| III.   |         |                                 |                  |                     |                 |                   |           |           |            |                 |           |           |           |     |         |         |    |    |         |   |    |                    |

|        | Dı      | splay<br>Inpo                   | ut/(<br>(<br>tem | Outp<br>Ciro<br>Dec | out<br>cui      | Si<br>ts:<br>ina  | gna       | al<br>nd  | C c        | onc<br>•<br>•mc | iit       | 10<br>• M | nı<br>lap | nç  | •       | •       | •  |    |         |   |    | 26                 |

|        | Di      | MC6<br>A/D<br>spla              | and              | Coni                | nec<br>/A<br>So | tio<br>Cha<br>ftw | n:<br>ra  | ct<br>e   | er:<br>De: | ist             | ic<br>in: | S         | ar        | nd  | W       | r       | in | •  | •       | • | •  | 33<br>36<br>41     |

|        |         | Pea<br>Sin                      | k-P<br>e-c       | Sub                 | rou             | tin               | e:        |           |            | •               |           | •         | •         | •   | •       | •       | •  | •  | •       | • |    | 41                 |

|        |         | Res                             | ist              | Sub<br>anc          | rou<br>e-R      | tin<br>eac        | e<br>ta   | nc        | e (        | ca:             | lci       | 1ء        | at:       | i o | n I     | Ro      | ut | in | e •     | • | •  | 44<br>47           |

| IV.    | COMPL   | JTATI                           | ON               | TEC                 | HNI             | QUE               | A         | ND        | E.         | RRO             | OR        | Αì        | 1A]       | LY  | SI      | S       | •  | •  | •       | • | •  | 51                 |

|        | Co      | /D an<br>omput<br>nase<br>rror  | ati              | ona<br>le           | l e             | rrc               | rs<br>Vo  | :<br>lt   | a a        | • /(            | cu:       | rre       | •<br>en:  | t · | Co      | ns      | ta | nt | s:      | • | •  | 58                 |

| v.     | DEVI    | CE TE                           | STI              | NG                  | ANI             | CA                | \LI       | BR        | TAS        | 10              | N I       | PR(       | OC:       | ED  | UR      | E       | •  | •  | •       | • | •  | 61                 |

|        | De      | evice                           | te               | sti                 | ng              | and               | d r       | es        | ul         | ts              | :<br>re   |           | •         | •   | •       | •       | •  | •  | •       | • | •  | 61<br>70           |

| VI,.  | CONCLUSIO | ONS    | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | •  | 74  |

|-------|-----------|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|-----|

| Appen | dix       |        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | pa | ige |

| Α.    | BIBLIOGRA | APHY . | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | •  | 76  |

| В.    | SOURCE P  | ROGRAM | • | • |   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | •  | 78  |

| c.    | OBJECT P  | ROGRAM | • | • | • | • | • |   | • |   | • | • | • | • | • | • | • | • | • | •  | 91  |

† \*

# Chapter I

### INTRODUCTION

Since many protective relays work on the principle of sensing the current and voltage at a relaying point and calculating the 60-Hz impedance seen in a particular direction, it is useful to plot system apparent impedance as seen by the relay on an impedance plane. A visual display of this instantaneous impedance trajectory on an oscilloscope screen, along with relay characteristics, gives a better understanding of system performance. From these trajectories the difference between normal, fault, and swing conditions can be detected.

When a power system "swings", the apparent impedance seen by a distance relay can be mis-interpretted as a fault condition and cause an undesired trip. A distance relay should be capable of discriminating between fault and power swing conditions. It is necessary too that the relay is set for the maximum expected steady-state loading. A power system apparent impedance along with an ohmic type of protective relay characteristic gives a complete picture of system behaviour under swing conditions.

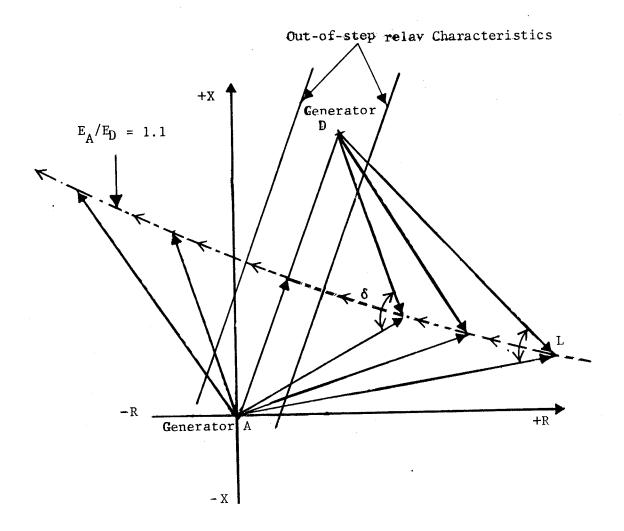

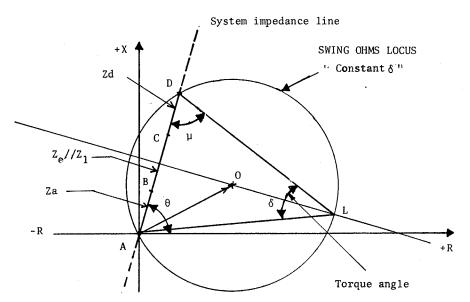

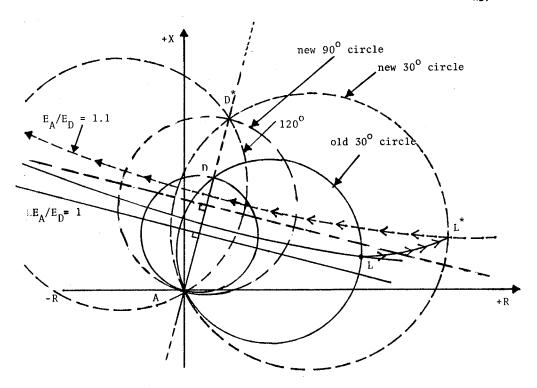

The impedance diagram in Figure 1.1 shows two generators at the ends of a transmission line swinging with respect to

each other. The locus of the apparent impedance as seen by a relay at point A is shown in dotted line. Point L on this locus represent the normal steady-state loading of the system. As instability develops and one generator (A) swings ahead of the other generator (D), this point will drift along a trajectory defined by the ratio of generators voltages, say  $\rm E_A/E_D=1.1$ . A distance relay located at A may interpret the swing as a fault, and to avoid this, out-of-step blocking can be employed. Conversely, a relay may be used to detect an unstable condition. This is called an out-of-step tripping relay shown in Fig. 1.1.

Fig. 1.1 Swing ohm trajectory on impedance plane

### Chapter II

### POWER SWINGS AND PROTECTIVE RELAYING

# 2.1 INTRODUCTION TO POWER SYSTEM STABILITY:

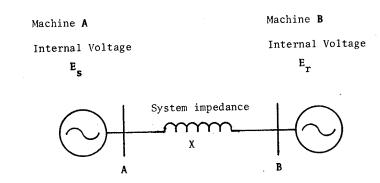

Instability of a power system comes about as a result of attempting to transfer power from one location to another in excess of the system capability. This system capability is known as stability limit and is dependent on the source voltage levels, the impedance between the sources and sine of the electrical angle between these voltages assuming all resistances and saliency can be ignored. The steady-state limit can be expressed in mathematical form for a two machine system as:

$$P_{\text{max.}} = \frac{E_s \cdot E_r}{x}$$

Watt .....2.1

where the symbols have the following meanings:

$P_{\max}$ . is the maximum power transfered

E is the sending end generator internal voltage (line to line volts)

is the receiving end generator internal voltage (line to line volts)

Equation 2.1 gives the maximum power transfer for the basic system shown in Figure 2.1 and this is for the condition where the angle between sending and receiving end voltages is ninety degrees. This equation can be generalised to give the system power transfer capability

$$P = \frac{E_s \cdot E_r}{X} \cdot \sin(\delta) \cdot \dots \cdot 2.2$$

where  $\delta$  is the angle of separation between  $E_s$  and  $E_r$  .

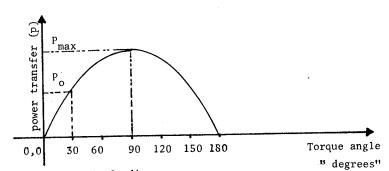

Plotting this power versus the angle of separation gives us a very useful power-angle curve as shown in Figure 2.2. It is often used in preliminary power system stability studies.

Stability studies are usually classified into three types depending upon the magnitude and nature of disturbances. These three types are transient, dynamic, and steady-state stability studies.

Transient stability studies are aimed at determining if the system will remain in synchronism and survive a major disturbance. Major disturbances can be classified as transmission system faults, line switching, loss of generating units, or sudden load changes.

Dynamic and steady-state stability studies are aimed at the stability of the locus of essentially steady-state operating points of the system. The distinction between these three types comes in the degree of detail used to model the system machines. Dynamic and steady-state stabilities are

essentially the same. Steady state problems use a simple generator model which treats the generator as a constant voltage source. But in dynamic stability problems the turbine-governing system and the excitation system along with a synchronous machine model which provides for variation in flux-linkages in machine air-gap is used. The nonlinear differential algebraic equations for the system can be replaced by a set of linear equations which are then solved to determine whether the set of machines will remain in synchronism following small disturbances from the operating point.

Transient stability studies are undertaken more often reflecting their greater importance in practice. They involve, in detail, large disturbances which do not permit the linearization of system non-linear differential and algebrate equations which must be solved by a step-by-step procedure or direct methods. Transient stability problems can be categorized into two categories:

- First-swing category which is based on a simple machine model without representation of control systems. The time period under study is usually the first few seconds following system faults.

- 2. Multi-swing category which takes into account a representation of machine control systems and more complex machine models to reflect its proper behaviour. The time period under study extends usually to a longer period than that for the other two types.

Fig. 2.1 Basic two machine system

Fig. 2.2 Power - Angle diagram

As was stated before, to show whether a set of machines will remain in synchronizm after a disturbance or not, a solution of the differential equations has to be investigated.

The fundamental equation which governs the rotational dynamics of these synchronous machines in stability studies, called the swing equation, is of second order and can be written in the form  $^9$

where the symbols have the following meanings:

H = stored kinetic energy in megajoules at sync.

speed divided by machine rating in MVA

- J is the total moment of inertia of the rotor masses in Kg-m

- $\boldsymbol{\omega}_{S}$  is the machine synchronous speed in mechanical radians per second

- $_{\rm S_m}$  is machine three phase rating MVA

- is the rotor angular displacement in units consistent with  $^{,\omega}{}_{\rm S}$  , e.g. radians.

- is the mechanical input power to the machine shaft less rotational losses.

- $P_{\rm e}$  is the electrical power crossing machine air-gap

- P<sub>a</sub> is the accelerating power, that is, the unbalance

between electrical and mechanical power.

The aforementioned second-order differential equation can be written as two first order differential equations

$$\frac{2H}{\omega_{s}} \frac{d\omega}{dt} = P_{m} - P_{e}$$

$$\frac{d\delta}{dt} = \omega - \omega_{s}$$

$$2.5$$

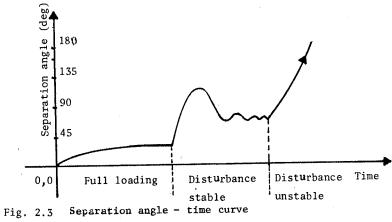

When the swing equation is solved we obtain the expression for  $\delta$  as a function of time. A graph of this solution is called the swing curve of the machine. Inspection of these swing curves for all machines in the system will yield whether the machines will remain in synchronism after a disturbance or not. A typical swing curve is shown in Figure 2.3

# 2.1.1 Power System Relaying on R-X Diagram:

Practical system economics and reliability demands that more and more dependance be placed on system relaying. Because of this increased dependence on relay performance, relays using multiple operating quantities were developed. These operating quantities are voltage, current and phase angle. One advantage of these three operating quantities is that relay characteristics as well as power system conditions can be plotted on the same R-X diagram from which system and relay behaviour can be predicted and analyzed.

These relays are known as ohmic relays. In order to understand the operating characteristics of these relays we must look into the torque-producing components, namely:

- Current component: Torque is proportional to square of current.

- Voltage component: Torque is proportional to square of voltage.

- 3. Voltage and current product component: Torque is proportional to current-voltage product times a function of the angle between them.

- 4. Control spring torque.

The general torque equation for an ohmic relay can be written in the form?

Torque(T) =

$$\pm K_1 \cdot E^2 \pm K_2 \cdot I^2 \pm K_3 \cdot E \cdot If(\gamma, \theta) \pm K_4$$

.....2.7

The conventions adopted for this equation are

- 1. Positive torque for contact closing.

- 2. Constants  $K_1$ .  $K_2$ ,  $K_3$  and  $K_4$  are independent relay constants.

- 3. Spring torque,  $K_{\underline{A}}$ , is assumed to be constant.

- 4. Operating quantities voltage (E), current (I) and  $\theta$  the phase angle between them, are supplied to the relay.

With proper choice of relay constants and associated signs, different types of relay elements can be developed. Some of these are tabulated in Table 2.1

Table 2.1 Ohmic relay elements and their torque equations

| Relay Type                               | Choice of Constants                                                                     | Torque Equation                                |

|------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------|

| Directional element                      | $K_1 = K_2 = K_4 = 0$ $f(\gamma, \theta) = \sin(90 + \gamma - \theta)$                  | $T = K_3.E.I.sin(90+\gamma-\theta)$            |

| Reactance<br>relay                       | $K_1 = K_4 = 0$ , $K_2$ positive<br>$f(\gamma, \theta) = \sin \theta$<br>$K_3$ negative | $T = K_2.I^2 + K_3.I^2.X$                      |

| Impedance<br>element                     | $K_3 = K_4 = 0; K_1 > 0; K_2 > 0$                                                       | $T = K_2 \cdot I^2 - K_1 \cdot E^2$            |

| Directional element with volt. restraint | $K_2 = K_4 = 0; K_1 > 0; K_3 > 0$ $f(\gamma, \theta) = \sin(90 + \gamma - \theta)$      | $T = K_3.E.I.sin(90+\gamma-\theta)$ $-K_1.E^2$ |

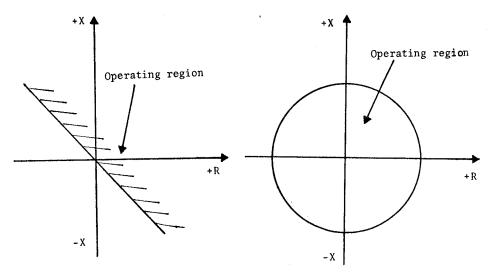

The characteristics of these relays are shown on the R-X diagram in Figure 2.4. It should be noted that the directional element is not an ohmic element in the usual sense, although its characteristics may be conveniently shown on an R-X diagram. one advantage of the R-X diagram is that it displays the same characteristics inspite of voltage variations due to different system faults or for the same fault under different system conditions.

The last item in table 2.1, the directional element with voltage restraint, uses the torque equation

$$T = K_3.E.I.\sin(90+\gamma-\theta) - K_1.E^2$$

..... 2.8

Where y is the angle of maximum torque

Positive torque will be developed i.e. relay operation, under the condition

$$K_3.E.I.\sin(90+\gamma - \theta) > K_1.E^2$$

........ 2.8a

If we set the equality condition, i.e. operate-restraint condition, we get

$$K_{3} \cdot E \cdot I \cdot \sin(90 + \gamma - \theta) = K_{1} \cdot E^{2}$$

.......... 2.8b

I.

$$sin(90+\gamma-\theta) = \frac{K_1}{K_3}$$

.Ε ......... 2.8c

Using the fact that the impedance between a fault location and the relaying point as seen by the relay is

$$Z = \frac{E}{I}$$

$$Z = \frac{K_3}{K_1} \sin(90+\gamma-\theta) \qquad \dots \qquad 2.8d$$

Inspecting this last equation we see that a positive contact closing torque will be realized whenever the term on the right hand side is greater than the left hand side. This equation, when plotted on an R-X diagram, is shown in Figure 2.4d. This simple plot does not depend on any parameters of operating quantities but defines the operating characteristics for all values of E, I and phase angle  $\theta$ .

a) Directional relay charact

$T = E \times I \times \sin(150 - \theta)$

( γ= 60 degrees)

c) Impedance relay characteristics

$$z = \sqrt{K_2 / K_3}$$

b) Reactance relay element

$\chi = \kappa_2 / \kappa_3$

d) 600 Mho relay charac.

$Z = K_3/K_1 \sin(150 - \hat{\theta})$   $(\gamma = 60 \text{ degrees})$

Fig 2.4 Ohmic elements characteristics on R-X diagram

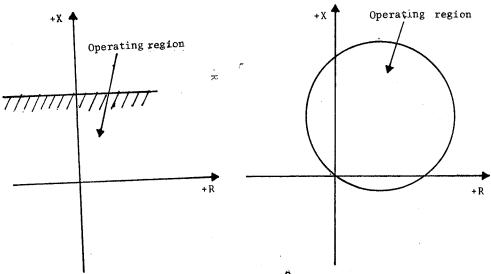

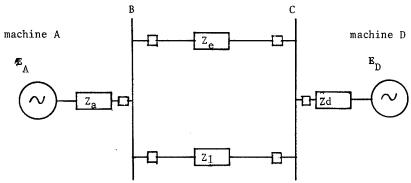

# 2.2 POWER SWING LOCUS ON R-X DIAGRAM:

An analysis of the characteristics of different types of relay elements has been explained on the R-X diagram. A better understanding of the whole power system and relaying system will be accomplished if both systems are plotted on one diagram. From this plot the locus of the ohmic value seen by a distance relay during power swings will give an accurate insight into the performance of the relaying system. To show the swing locus on the R-X diagram the two machine system and transmission line representation shown in Figure 2.5 will be used.

For power flow from point A to point D, the voltage at point A will lead the voltage at point D. The total current will lag  $E_{AD}$  by the angle of the total impedance between these two points. For a fixed torque angle  $\delta$  (the angle between equivalent source voltages), the apparent impedance seen from point A will fall on a circle which is defined by this given torque angle. A particular impedance point on this circle is entirly dependent on the ratio of voltage magnitudes at points A and D. Figure 2.5b shows the swing locus for the system and can be determined geometrically as shown in reference 3 Appendix III. The centre of this circle is the vector AO with magnitude

and

Fig 2.5a example system

Fig 2.5b

Fig 2.5 Swing ohms locus on R-X diagram

$$Arg(\overline{AO}) = \theta_{-90+\delta}$$

where

$\theta$  = is the phase angle between E & I

$\delta$  = is the torque angle

The vector  $\overline{AL}$ , which represents the load ohms as seen from point A, has the magnitude and angle as a function of the torque angle, to be:

$$\overline{AL} = \frac{\overline{AD}.\sin \mu}{\sin \delta}$$

..... 2.11

and

$$Arg(\overline{AL}) = \theta + \delta + \mu - 180 \qquad .... 2.12$$

where  $\mu$  is given by

Equation 2.13 shows us how point L on the circle diagram will behave for different source voltage ratios. Assuming that torque angle remains constant, the left hand term in equation 2.13 will increase for increasing  $\frac{E}{D}/E_A$  ratio and, therefore, the angle will be decreasing which results in point L moving clockwise along the Swing Circle.

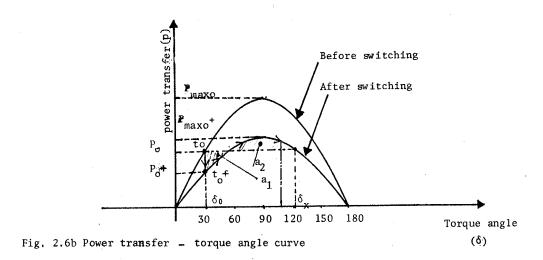

To show how the apparent impedance moves on the R-X diagram due to line switching, the system shown in figure 2.5a will be used. Assume this system was initially running at synchronous speed with  $E_A/E_D=1.1$ ,  $P=P_0$  and  $\delta=30$  degrees. From the  $P=\delta$  curve of Figure 2.6b the maximum

Fig. 2.6a Apparent impedance locus on R-X diagram

steady-state power transfer before switching line  $\mathbf{z}_{L}$  (  $\mathbf{t} < 0$  ) is equal to  $\mathbf{P}_{\text{maxo}}$ .

At the first instant of switching, the impedance between points A and D has increased to AD\*. This means that the power transfer capability is reduced and is shown as  ${}^{p}_{o}^{+}$ . The difference in power,  ${}^{p}_{o}^{+} - {}^{p}_{o}^{-}$ , is the accelerating power which accelerates the rotor and the rotor angle advances to say  $\delta_{x}$ . For the machine to stay in synchronism, area's all and all have to be equal according to the equal are criterion:

$$\int_{\delta_0}^{\delta_x} (P_m - P_e) d\delta = 0$$

where  $P_{m} - P_{e}$  is the accelerating power.

If the equal-area criterion cannot be satisfied, this means that  $\delta_{\rm x}$  goes beyond about 120 (typically) and the machine goes unstable. As is seen on the R-X diagram, the original operating condition is the point L corresponding to t=0 or (Power = P\_0). After line switching the new operating point is L\* which corresponds to the same voltage ratio (1.1) and torque angle (30 degrees), but the electrical power output is  $P_0^+$ . As the torque angle advances towards  $\delta_{\rm x}$ , point L\* moves along the circle  $E_{\rm A}/E_{\rm D}=1.1$  as shown by the arrows on Figure 2.6a. If the system goes unstable, this point crosses the approximate transient stability limit circle, then it continues advancing till it crosses the system impedance line at  $\delta_{\rm x}=180$  degrees where machine A will be 180 degrees out of phase with machine D.

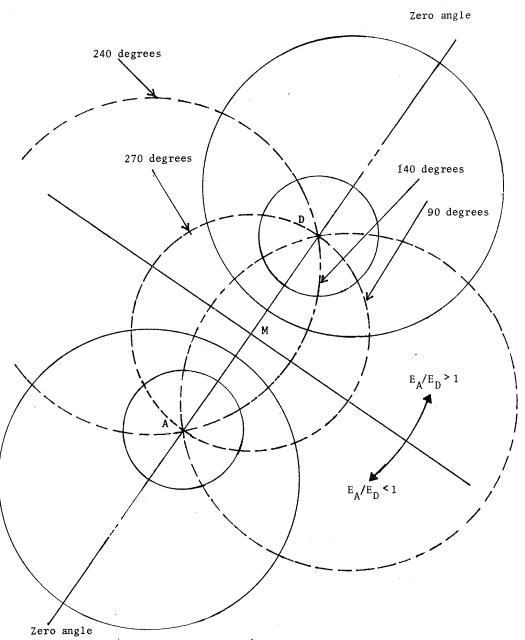

In a general case, if the angular separation of the two machines is maintained constant while varying the voltage ratio, the apparent impedance will follow a circle which passes through both points A and D with their centers on the perpendicular bisector of the system impedance line with radii and offsets determined by the various values of this voltage ratio. This family of circles is shown in dashed lines in Figure 2.7. Another set of circles can be constructed by holding the voltage ratio constant while varying the angular separation. This new family of circles is all centred on the system impedance line with radii and offsets determined by the voltage ratio and shown in solid line in It should be noted that these two families of Figure 2.7. curves are orthogonal. For full details and mathematical derivation of these curves, the reader is advised to see Note too an interesting circle which is cenreference 4. tred at the system impedance centre and passes through both points A and D. For any value of voltage ratio, the apparent impedance of the system must pass through this circle as the separation angle reaches and passes 90 degrees which is the approximate steady-state stability limit.

Fig. 2.7 General impedance diagram  $^{4}$

# 2.3 COMBINED SYSTEM AND RELAY CHARACTERISTICS ON R-X:

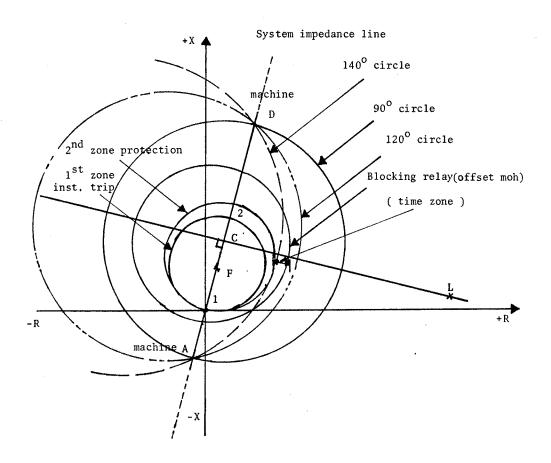

In order to use the R-X diagram effectively and for better understanding of total system behavior, both relay characteristics and how the system apparent impedance will vary as system conditions vary, i.e. as system machines go out of step, must be shown on the same diagram. In order to accomplish this, Figure 2.8 will be used. On this figure, only the approximate steady-state stability limit circle, i.e. 90 degree separation circle and the approximate transient stability limit, i.e. 120 degree separation circle, and the swing line for the special case where voltage ratio  $\mathbf{E}_{\mathbf{A}}/\mathbf{E}_{\mathbf{D}}=1$  are shown. On the same figure, a portion of the system impedance line between stations 1 and 2 is to be protected. First zone instantaneous trip protection for 80 per cent of the line is provided by a mho element.

We have seen that the system apparent impedance follows a definite curve during an out-of-step condition or power swing. This particular curve is dependent on the voltage ratio and intersects the system impedance line at 180 degrees. Let us consider at one instant the system was carrying an interchange of loading equivallent to point L shown on Figure 2.8. A fault on the line portion 1-2 will result in a change of impedance from point L to point F on the line in practically zero time. On the other hand, during the first few swing cycles for an out- of-step condition, the apparent impedance drifts along the curve  $\mathbf{E}_{\mathbf{A}}/\mathbf{E}_{\mathbf{D}}=1$

Fig. 2.8 Combined system and relay characteristics on R-X diagram

relatively slowly as compared to the fault case. If the offset mho element was set up to block the first and second zones of the mho relay, these elements would not trip as long as the out-of- step condition progressed from the initial separation condition to a 90 degree to 120 degree separation to any point inside the blocking element in a time which exceeds a predetermined minimum time. This shows that the blocking element has to pick up before the first and second zone trip element with a sufficient time for the auxiliary relays to operate. But if this time is not enough or if both the blocking and tripping elements pick up at the same time, blocking will not be realized. This time delay has to be sufficiently large to allow for the fastest swings anticipated and yet be practical to avoid unnecessary tripping.

Since practical system operation and system conditions do occasionally force the system to go out-of-step, tripping relays must detect the out-of-step condition and take the necessary measures. The basic distinction of an out-of-step condition can be realized by the fact that the apparent impedance, as seen from any one point in the system, changes from a point to the right of the system impedance line to a point on this line to a point to the left of the system impedance line. This sequence applies for power transfer from point A to point D as the machine at point A advances ahead of machine D. Another characteristic of an out-of-

step condition is that the aforementioned apparent impedance change takes place over a finite period of time which is long as compared to impedance change associated with a fault An ohmic relay which will recognize these discondition. tinctive characteristics can be a relay with two reactance Each element has an angle of maximum torque perelements. pendicular to the system impedance line, and an operating characteristic parallel to the system impedance line with an adjustable offset for pick-up setting selection. requirement for these settings is that the relay should opknow this erate for the fastest slip cycle expected. To maximum slip would involve various system parameters and should be based on a transient stability study of the system A second requirement for these setunder consideration. tings is that the relay characteristics should cover the system impedance plot on the R-X diagram. This means that any fault on the system should fall between the relay characteristics.

# Chapter III TRANSIENT IMPEDANCE DISPLAY UNIT DESIGN

# 3.1 <u>DISPLAY UNIT HARDWARE DESIGN:</u>

The transient impedance display unit is a microprocessor based device which is capable of calculating the apparent impedance seen at a relaying point using readily available input signals. These signals are a voltage signal proportional to the line voltage and a second voltage proportional to the current in that phase. The apparent impedance is outputed in the form of a voltage signal proportional to line resistance and another voltage signal proportional to the line reactance. Applying the resistance equivalent voltage to the horizontal channel of an oscilloscope and the reactance equivalent voltage signal to the vertical channel, the apparent impedance seen at the relaying point can be displayed on the oscilloscope screen

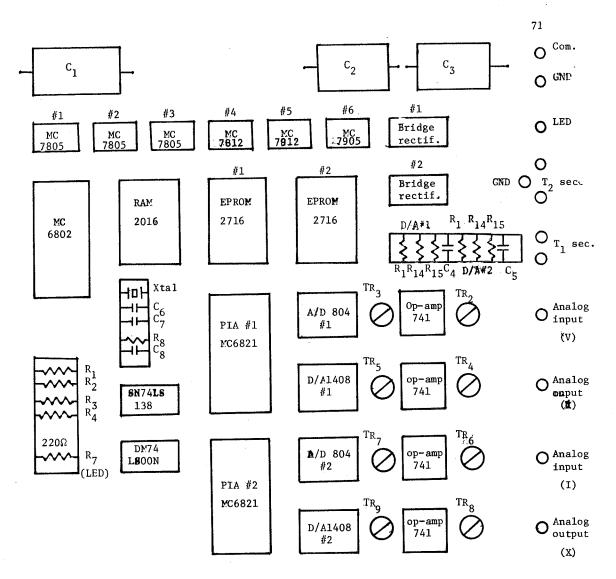

The central processing unit is the Motorola Inc. type MC6802 microprocessor. Most of the other supporting chips such as the peripheral interfacing adapters ,decoder, digital to analog and analog to digital converters are either manufactured by Motorola or National Semiconductors Inc. The main reason behind this choice is the availability of the supporting equipment and facilities such as a main computer

system crossassembler and a diagnostic emulator used for system software development and system debugging.

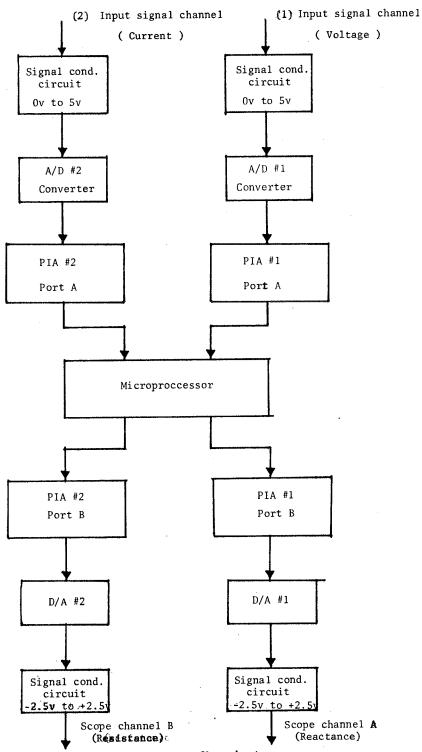

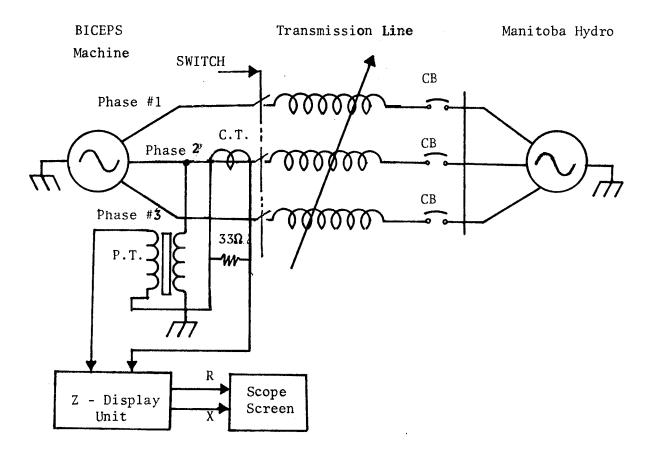

Fig. 3.1 shows the device hardware function flow chart. It shows two almost identical circuitry used for both voltage and current input signal channels with differences in the design of signal conditioning circuits. The voltage signal is derived from the BICEPS machine line voltage through a potential transformer that provides a 6.3 V secondary voltage. The current signal is derived from the same phase through a 33 ohms resistor connected across the secondary terminals of a current transformer wired to the same line at the same point.

## 3.1.1 Input/Output Signal Conditioning Circuits:

The analog to digital converter chosen in this design is the ADC0804 manufactured by National Semiconductor Inc. The electrical specifications state that for a +5V DC power supply to this chip, the input range will be 0V to +5V. This comes about as a result of two on-chip diodes which are tied to each analog input terminal,  $V_{\rm in}(+)$  and  $V_{\rm in}(-)$ . For a zero differential input signal at  $V_{\rm in}(-)$  and  $V_{\rm in}(-)$  the output code will be

[0000 0000]

and for diferential input =  $V_{cc}$  digital output code will be

[1111 1111]

-Fig. 3.1 System hardware function flow chart

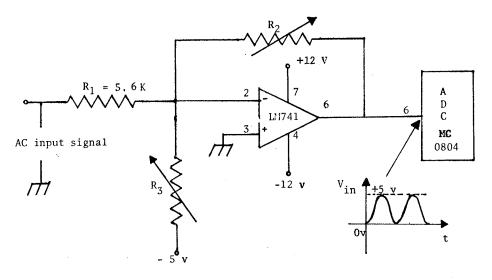

To achieve this OV to +5V analog input range the input signal conditioning circuit shown in figure 3.2a is designed. As was mentioned earlier, the available signal from the BICEPS line potential transformer is 6.3  $V_{\rm rms}$  or -8.9V to +8.9V peak-to-peak. For the output of the operational amplifier (op-amp) to be OV to +5V, the feedback resistance to the input resistance ratio will be

$$\frac{R_2}{R_1} = -\frac{V_0}{V_{in}} = \frac{5}{17.82}$$

......3.1

or

$$R_2 = 0.28 R_1$$

.....3.2

and to bias the signal

$$R_3 = 2.0 R_2$$

.....3.3

Selecting the input resistance  $\mathbf{R}_1$  to be equal to

$$R_1 = 5.6 \text{ K} \Omega$$

will yield

$$R_2 = 1.57 \text{ K }\Omega$$

$R_3 = 3.14 \text{ K }\Omega$

Similar arguments apply to the current signal derived from the current transformer

$$\frac{R_2}{R_1} = -\frac{V_0}{V_{in}} = \frac{5}{8}$$

$$R_2 = 0.625 R_1$$

.....3.4

and setting

$$R_3 = 2 R_2$$

Selecting the input resistance to be

### a) Input signal conditioning

### b) output signal conditioning

Fig. 3.2 Input/Output signal conditioning circuit

$$R_1 = 5.6 k\Omega$$

yields

$R_1 = 3.5 k\Omega$

$R_3 = 7.0 k\Omega$

# 3.1.2 System Decoding and Memory Map

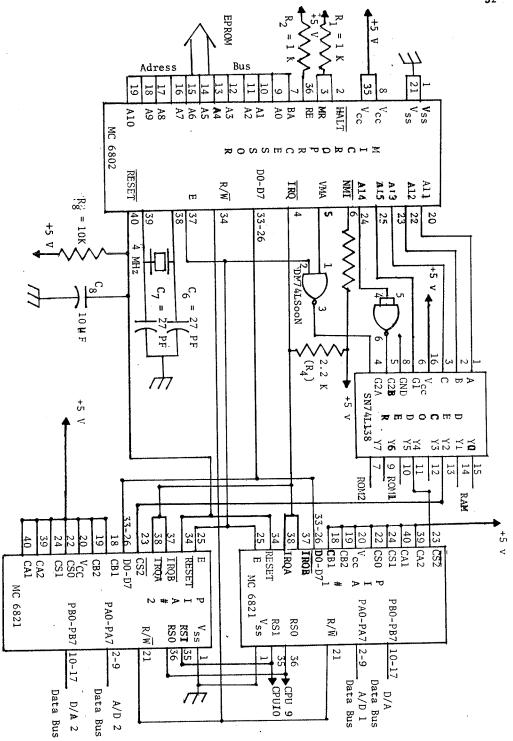

The Decoder/Demultiplexer chosen for system decoding is This decoder chip is shown Texas Instrument type SN74S138. in Figure 3.3 and provides partial address decoding using only three of the high order address lines Al3, Al4, and The decoder accepts these three binary inputs, which A15. are wired to chip select terminals A, B, and C. When enabled by proper signals on the input enable terminals, it provides one of eight mutually exclusive active low outputs (Y0-Y7) dependent on the conditons at the three select inputs as shown in Table 3.1. The chip enable terminals are Terminal Gl is always high (+5 V), connected as follows: G2B terminal is connected to ground and terminal G2A is wired to the processor VMA and E terminals through a NAND As a result of this partial decoding gate type DM74LSOON. scheme, table 3.2 and memory map Table 3.3 are constructed to show all on board chips and the address to which each one will respond.

Table 3.1 Partial decoding function table

| Inputs |     |   |   |   | · · · · · · · · · · · · · · · · · · · |    |    |    |     |    |    |    |

|--------|-----|---|---|---|---------------------------------------|----|----|----|-----|----|----|----|

|        |     |   |   |   | Outputs                               |    |    |    |     |    |    |    |

| G1     | G2* | С | В | Α | Y0                                    | Y1 | Y2 | Y3 | Y4  | Y5 | Y6 | Y7 |

| Н      | L   | L | L | L | L                                     | Н  | Н  | Н  | Н   | Ħ  | Н  | Н  |

| Н      | L   | L | L | Н | Н                                     | L  | Н  | Н  | Н   | Н  | Н  | Н  |

| Н      | L   | L | Н | L | Н                                     | Н  | L  | Н  | Н   | Н  | Н  | Н  |

| Н      | L   | L | Н | Н | Н                                     | Н  | Н  | L  | Н   | Н  | Н  | Н  |

| Н      | L   | Н | L | L | H                                     | Н  | Н  | Н  | L . | Н  | Н  | Н  |

| Н      | L   | Н | L | Н | Н                                     | Н  | Н  | Н  | Н   | L  | Н  | Н  |

| Н      | L   | Н | Н | L | Н                                     | Н  | Н  | Н  | Н   | Н  | L  | Н  |

| Н      | L   | Н | Н | Н | Н                                     | Н  | Н  | Н  | Н   | Н  | Н  | L  |

|        |     |   |   |   |                                       |    |    |    |     |    |    |    |

$G2^* = G2A + G2B$

H = high level

L = low level

Table 3.2 On board chips addresses

| Chip Name | Chip Addre <b>s</b> s |

|-----------|-----------------------|

| . PIA #1  | \$ D000-D003          |

| PIA #2    | \$ E000-E003          |

| EPROM #1  | \$ F000 <b>-F7FF</b>  |

| EPROM #2  | \$ F800-F <b>F</b> FF |

| RAM       | \$ C000 <b>-C</b> 7FF |

Fig. 3.3 System wiring diagram

Table 3.3 Memory map for transient impedance display unit

|              | Memory Location |

|--------------|-----------------|

| Reset Vector | \$FFFF,\$FFFE   |

| EPROM #1     | \$F000 - \$F7FF |

| EPROM 2      | \$F800 - \$FFFF |

| PIA #2       | \$E000 - \$E003 |

| PIA #1       | \$D000 - \$D003 |

| RAM          | \$C000 - \$C7FF |

| Not used     | All others      |

# 3.1.3 MC6802 Microprocessor and Peripheral Connection:

The MC6802 is an eight bit microprocessor. A detailed block diagram, programming model of the processing unit and pin assignment diagrams are given by the (manufacturer Motorola Inc.) in the appropriate data manual. Some of the features in this microprocessor chip are:

- 1. an on-chip internal clock oscillator and driver,

- 2. a 128x8 on-chip RAM located at hex addresses \$0000 to \$007F with the top 32 bytes having memory retention capability by utilizing the standby power supply,

- 3. sixteen lines unidirectional address bus, and

- 4. an eight line bidirectional data bus.

The programming model for this processor shows that the MPU has three 8-bit registers, two accumulators, one condition code register, and three 16-bit registers called 1) index register, 2) programme counter, and 3) stack pointer. All are vailable for use by the programmer. The two 8-bit accumulators are used to hold operands and the results of the arithmetic logic unit, ALU. The condition code register contains eight bits of information and only the two highest order bits are not used and set to ones, the other six bits are used as testable condition codes for the conditional branch instructions. Bit number four is the interrupt mask in this condition code register.

The 16-bit index register stores sixteen bits of memory address for the index mode of memory addressing. The programme counter is a 2-byte (eight bit each) register that points to the current program instruction. The stack pointer is a 2-byte (eight bit each) register that contains the address of the next available location in the stack for use.

Figure 3.3 shows the pin connection and wiring diagram of this microprocessor interfaced to two peripheral devices and a decoder. This figure shows that the HALT line is not used and, therefore, set in the high state for the interrupts to be serviced. Memory ready is also set high indicating that the clock seen at the ENABLE terminal E operates in the normal condition or unstretched. A 4MHz crystal is connected to pins 38 and 39 and because of the divide-by-four circui-

try inside the chip, gives an operating clock frequency of lMHz. The  $\overline{\text{IRQ}}$  input is wired to terminals 37 and 38 on both PIAs. A low level on this input requests that an interrupt sequence be generated in the chip. The processor will first complete the current instruction before it responds to the interrupt request. At this time, if the interrupt mask bit is not set, the processor will start the interrupt sequence.

The RESET terminal is wired to the RESET terminal on each PIA. When this line is low, the MPU is inactive and the information in all the registers will be lost. When this terminal goes high, the MPU begins the restart sequence by executing a routine to initiate the processor from its reset state. For the restart, the last two memory locations (hex addresses \$FFFE and \$FFFF) will be used to load the program that is addressed by the program counter. During the restart routine, the interrupt mask bit is set and must be reset for the MPU to be interrupted by IRQ line.

Two peripheral interfacing adapters manufactured by Motorola Inc. type MC6821 are shown in fig.3.3. These adapters will appear to the microprocessor as memory locations. The processor will read a digital word from the input register and write a digital word into the output register under program control. The input digital word is equivalent to the analog input into the A/D converter and the output digital word is equivalent to the analog output from the D/A converter. For a complete discussion of this PIA diagram,

initialization and control lines discription, the reader is advised to see reference 8 pages 212-231.

## 3.1.4 A/D and D/A Characteristics and Wiring:

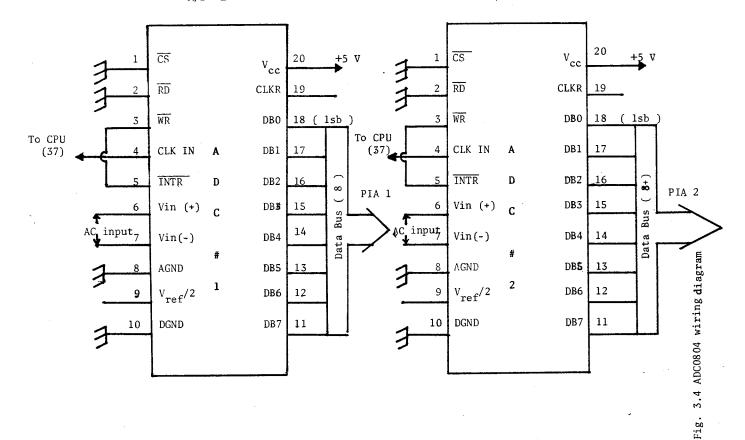

Figure 3.4 shows the wiring diagram for the ADC0804 chosen for this application. This A/D can appear like a memory location or an I/O port to the microprocessor and no interfacing logic is needed other than the chip select  $\overline{CS}$  terminal. Block diagram and electrical specifications with the maximum ratings are given by the manufacturer (see reference 6).

This converter works on the successive approximation principle. It accepts an analog input signal,  $v_{\rm in}$  at the input terminal and provides a corresponding digital output signal according to the equation

$$M \equiv \begin{bmatrix} v_{in} \\ v_{ref} \end{bmatrix}$$

where  ${

m ^V}_{

m ref}$  is the reference voltage applied to  ${

m ^V}_{

m ref}/2$  terminal. The brackets indicate that M is the closest approximation to within the resolution of M. In binary approximation form

$$M = \frac{V_{in}}{V_{ref}} \approx \left[ a_1 \ 2^{-1} + a_2 \ 2^{-2} + \dots + a_n \ 2^{-n} \right]$$

This equation shows that the output signal M is a binary approximation of the voltage ratio

The A/D data bus (DBO-DB7) is wired to the PIA, port A, data bus. Because the PIA is already memory mapped by the processor and the data lines are connected to the processor data bus under program control, both terminals CS and RD are connected to ground.

The A/D Converter is clocked using the clock in microporcessor by connecting the CLK IN terminal MC6802 directly to the E terminal on the processor. By virtue of this connection the CLKR terminal is left floating since the internal circuitry will generate the required clock by using the built-in clock oscillator. Terminal WR is connected to INTR terminal. This connection with  $\overline{CS}$  connected to ground makes the A/D run in the free-running mode. start- up under all possible conditions an external WR write pulse is required during the first power-up cycle. starting process is accomplished by having  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  terminals simmultanously low which gives the internal clock signal combined with the internal starting flip-flop circuit, START F/F, the responsibility of the start-up process.

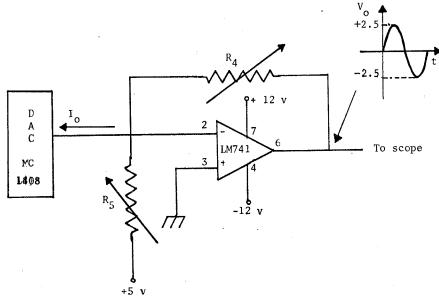

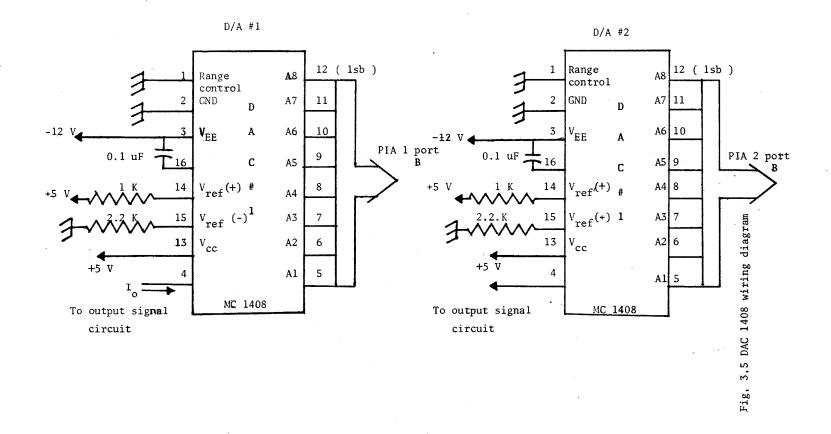

The digital-to-analog converter used is the Motorola DAC1408. Figure 3.5 shows the wiring diagram for this converter. The input is an 8-bit digital word via the (A1-A8) input lines connected to the PIA port B data bus. This digital word is the result of the CPU mathematical calculations representing the resistance and reactance seen by the impedance display device. Specifications and

characteristics issued by the manufacturer, reference 6, state that the reference amplifier input current must always flow into V (+) regardless of the reference voltage poreflarity. This terminal,14, is therefore tied to the reference voltage +5V DC. The reference terminal, V  $_{\rm ref}$ (-), is tied to ground through 2.2k $_{\Omega}$  resistor.

Output voltage is obtained by connecting the output terminal pin 4, which provides a current signal going into the converter, to the output signal conditioning circuit shown in Figure 3.2b. This circuit uses an operational amplifier with a feedback resistor  $\mathbf{R}_4$ . This configuration keeps the output of the MCl408 at ground potential and the operational amplifier can generate a positive voltage limited only by its power supply. The magnitude of the output voltage is dependent on the digital input and given by the equation:

$$V_{o} = \frac{V_{ref}}{R_{14}} \cdot R_{4} \cdot \left[ \frac{1}{2} + \frac{1}{4} + \frac{1}{8} + \dots + \frac{1}{256} \right]^{volts}$$

where:

[ Al A2 ... A8 ] is the digital input  $V_{\rm ref}$  is the reference voltage at Pin 14  $R_{14}$  is the resistance connectedd to Pin 14  $R_4$  is the feedback resistor accross the op-amp.

A detailed analysis of the output signal and the converter accuracy is given in Chapter 4.

#### 3.2 DISPLAY UNIT SOFTWARE DESIGN:

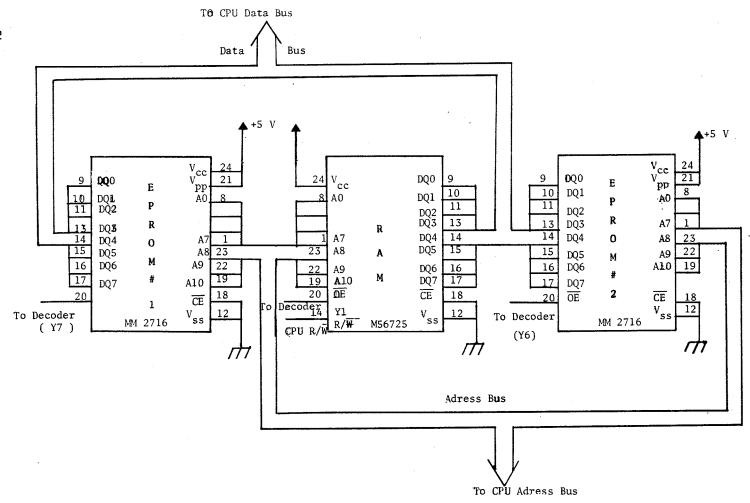

The analog input to the A/D converter is a voltage signal 0V to +5V. This A/D converter puts out a digital word \$00 to \$FF. The zero-crossing of the input signal to the signal conditioning circuit is the same as the +2.5V value of the input signal to the A/D converter which is equivalent to digital word \$80 at the output of A/D converter. A software program was developed to calculate the resistance, reactance and their locations on the R-X diagram. This programme is stored in a two (2K-byte each) EPROM memory chips wired and decoded as shown in fig. 3.6

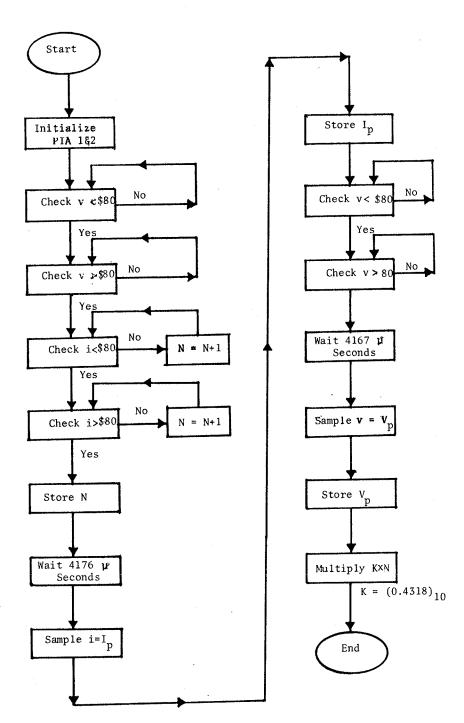

### 3.2.1 Peak-Picking and Phase Shift Calculation Subroutine:

Figure 3.7 is the flow chart for this subroutine. It starts with initializing the peripheral interphace adapters at the starting address \$F000. Port A in each PIA is initialized as an input register and port B as an output register. The input register contains the instantaneous digital word equivalent to the analog input signal. Whenever the processor detects a change from  $v_{\rm in} < \$80$  to  $v_{\rm in} \ge \$80$  it will be interpretted as zero-crossing and continue to check for current signal zero-crossing by detecting the change in  $v_{\rm in} < \$80$  to  $v_{\rm in} \ge \$80$ . During the time of looking for a current-zero, a counter is incremented by 1 for each time the processor branches back to check for current-zero. The number in this counter, N, is a Hex number equal to the phase

Fig. 3.6 EPROM and RAM wiring diagram

Fig. 3.7 Peak-picking and phase shift calculation routine

shift in number of laps. After the current-zero is detected the phase shift is stored and then the processor waits for 4167  $\mu$  seconds (equivalent to 90 degrees) by multiple looping in a specified loop then samples and stores the PIA #2 input register to give the current peak.

The processor then follows similar steps to find the voltage signal peak. The phase shift measurment is then multiplied by a constant to give the equivalent value in degrees. A list of important addresses used by this subroutine follows:

| PIA #1 input register  | \$D000         |

|------------------------|----------------|

| PIA #1 output register | \$D002         |

| PIA #2 input register  | \$E000         |

| PIA #2 output register | \$E002         |

| phase shift in degrees | \$CA02, \$CA03 |

| voltage peak value     | \$CA10         |

| current peak value     | \$CA09         |

After the processor calculates the three variables (current, voltage, and phase shift) it executes the sine-cosine calculation subroutine.

## 3.2.2 Sine-cosine the Phase Shift Angle Subroutine

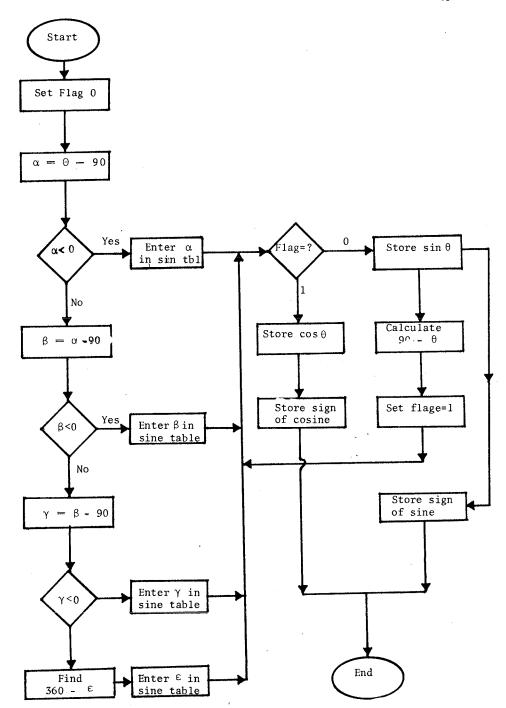

The algorithms of these subroutines are shown in Figures 3.8 and 3.9. The main idea behind the sine-cosine routine is that the processor keeps subtracting 90 degrees from the phase shift angle and continuously checking for carry bit set. When the carry bit set is detected it branches to

Fig. 3.8 Sin/Cos phase shift angle calculation

Fig 3.9 Table search flow chart

execute the table search routine where it calculates the sine and cosine of the phase angle. The signs are identified by setting the first bit in the corresponding flag registers as shown below:

| Sign of Sine/cosine | Angle location | R - X Flag |

|---------------------|----------------|------------|

| cosine negative     | second quad.   | \$CA3B     |

| cosine negative     | third quad.    | \$CA3C     |

| sine negative       | third quad.    | \$CA3D     |

| sine negative       | fourth quad.   | \$CA3E     |

# 3.2.3 Resistance-Reactance Calculation Routine

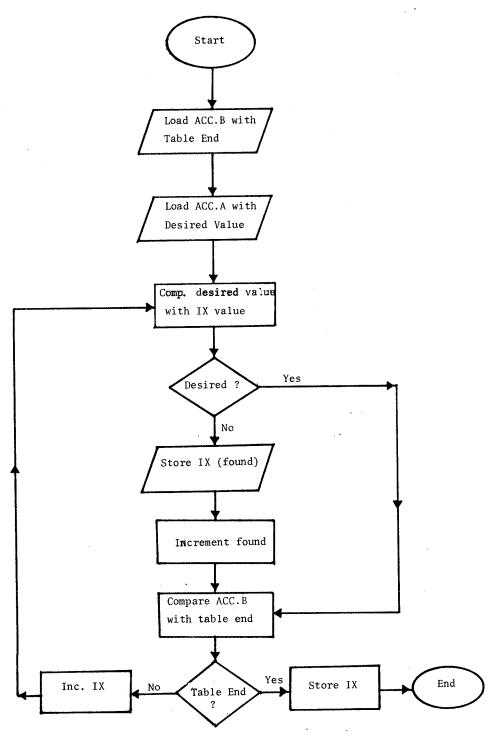

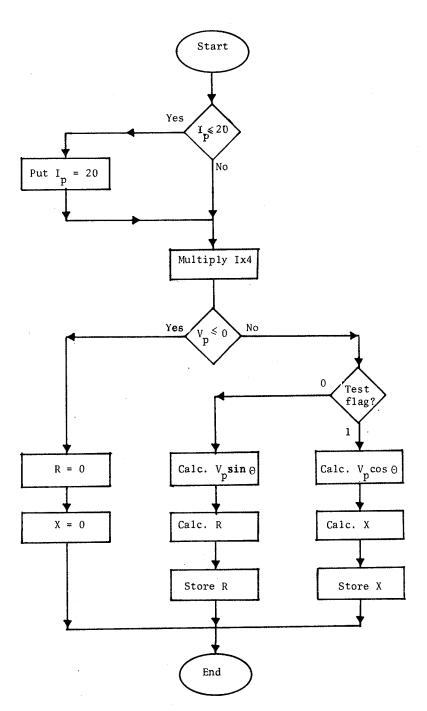

Figure 3.10 is a flow chart for the impedance calculation RTN. The program starts by reading the current  $I_p$  and imposing a minimum value of \$20, then multiply this Ip by 4. The processor then reads the voltage  $V_p$ . If  $V_p$  is equal to zero, the resistance and reactance values are forced to \$00 and outputed in PIA #1 and PIA #2 output registers otherwise it tests R-X flag to do either resistance or reactance calculations:  $V_p = \frac{V_p \cdot \cos \theta}{p}$

R =  $\frac{V_{p} \cdot \cos \theta}{I \cdot 4}$   $X = \frac{V_{p} \cdot \sin \theta}{I \cdot 4}$

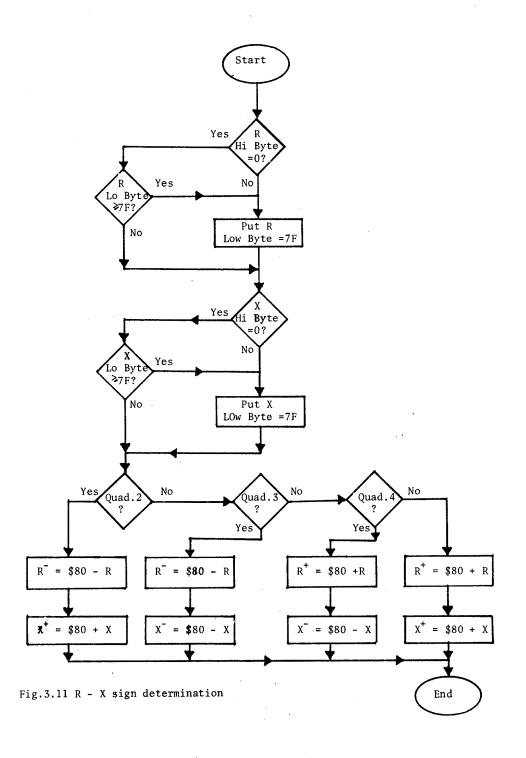

The sign of the R and X is determined by the subroutine shown in figure 3.11. The processor starts by putting a limit on maximum R and maximum X to be equal \$7F. Then it checks the sign of sine/cosine and implements the logic given in the following table.

Logic table for sign of R & X in four qudrants

| lst quad. | 2nd quad. | 3rd quad    | 4th quad | 1    | ogic |   |   |

|-----------|-----------|-------------|----------|------|------|---|---|

| yes       |           |             |          | R+ = | \$80 | + | R |

|           |           |             |          | X+ = | \$80 | + | X |

|           | yes       |             |          | R- = | \$80 | - | R |

|           |           |             |          | X+ = | \$80 | + | x |

|           |           | yes         |          | R- = | \$80 | - | R |

|           |           |             |          | x- = | \$80 | - | X |

|           |           | No. 400 400 | yes      | R+ = | \$80 | + | R |

|           |           |             |          | X- = | \$80 |   | x |

Where R and X are the previously calculated values and R+, X+, R-, X- are the adjusted values with corresponding signs.

Fig. 3.10 Impedance calculation routine flow chart

### Chapter IV

#### COMPUTATION TECHNIQUE AND ERROR ANALYSIS

The device is designed to work on a 60 Hz system, with no harmonic content or dc offset, by accepting two voltage signals with the following ranges:

$$V_{in}(v) = -8.9v \text{ to } +8.9v$$

$$V_{in}(i) = -4v \text{ to } +4v$$

As was mentioned before, these signals are conditioned to have the ranges

$$V_{in}(v) = 0v \text{ to } +5v$$

$$V_{in}(i) = 0v \text{ to } +5v$$

The BICEPS (The Basic instrumental controllable Electrical Power system) machine rating is;

Full load line current = 0.33 Amps

Line voltage = 120 Volts

Full load power = 40 Watt/phase

From these ratings we get

Impedance at full load =  $364\Omega$

For a maximum short circuit current =  $^{5}$   $^{I}$ <sub>f.1</sub>.

$$Z_{\min} = 72 \Omega$$

under light load condition  $I = \frac{1}{4} I_{f.1}$ .

$$Z_{\text{max}} = 1454 \Omega$$

The impedance range is  $z_{\min} < z > z_{\max}$  from which the resistance and reactance are calculated.

$$R = Z \cos \theta$$

$$X = Z \sin \theta$$

Sources of errors can be classified into two categories. The first category is component errors, mainly A/D and D/A converter errors. The second category is computational errors as a result of multiplication and division routines, sine table approximations and phase shift calculations.

### 4.1 A/D AND D/A CONVERTER ERRORS

Since the A/D terminal  $V_{\rm in}(+)$  is grounded and the reference terminal is floating, the zero digital code will need no adjustment and will be equivalent to zero analog input. Also the full digital code, \$FF, will be equivalent to +5V analog input and no adjustment is needed. Manufacturers specification gives a full scale error of  $\frac{\pm 1}{4}$  LSB at a clock frequency of lMHz.

Quantization errors are inherent in all digitization techniques. For A/D converters the minimum quantization error is the smallest increment of analog voltage to which the output signal can be approximated. This quantization error is given by

$$\Delta V_{q} = \frac{V}{r^n}$$

where

V is the analog input voltage,

r is the radix (r=2 for binary system), and

n is the number of digits (n=8 bits).

This will give the LSB bit a weight of

LSB =

$$\Delta V_q = \frac{5v}{2^8} = 19.53 \text{ mV}$$

Another type of error is the sampling error. This arises from the fact that an A/D converter will look at the input signal for a short interval and leave it for a much longer time. In a general case, to minimize sampling error, a sinsoidal analog input is restricted in its maximum frequency by the relation

$$f \leq \frac{\Delta V}{V_p \cdot \Delta T}$$

where:

$v_{_{\mathrm{D}}}$  is the peak input signal,

$\Delta T$  is the aperture time of the converter, and

$\Delta V$  is the resolution voltage.

Since the processor has a clock period of 1  $\mu$  sec, the time taken by this converter to count from 2  $^0$  to 2  $^8$  is

conversion time =  $T_c$  =  $1\mu sec \times 2^8$

The conversion rate is therfore

$$f_c = \frac{1}{T_c}$$

= 3906 conversions per second.

For a 60 Hz analog input the conversion rate is thus

$$f_c = 65 \text{ conversions/cycle.}$$

From this conversion rate we can say that the sampling error for the A/D converter is negligible.

The D/A converter output is a current signal

$$I_0 = K \left( \frac{A_1}{2} + \frac{A_2}{4} + \frac{A_3}{8} + \dots + \frac{A_8}{256} \right)$$

Amps

$$I_0 = K \times A$$

Amps.

where:

$$K = \frac{V_{ref}}{R_{14}}$$

$K = \frac{V_{ref}}{R_{14}}$ is the most significant bit MSB

is the least significant bit LSB

is either 1 or 0 Α

is the resistance connected to the converter at pin 14

In this design, these components were choosen to have values

$$R_{14} = 1 K$$

$$v_{ref} = +5v$$

$$K = 5m Amp$$

The output current and voltage conversion is accomplished by the output signal conditioning circuit shown in Figure 3.2.

$$V_0 = K \cdot A \cdot R_{14}$$

volts

The output current for a digital word (00) is = 0 A and for a digital word (FF) is approximately 2 mA.

$$I_0 = 0.005 \left( \frac{1}{2} + \frac{1}{4} + \frac{1}{8} + \dots + \frac{1}{256} \right)$$

Amps

Trim pots  $R_4$  and  $R_5$  on figure 3.2b are used for final adjustment to give a scaled output voltage to be

The accuracy test done by the manufacturer on this converter showed that the accuracy is within  $\pm \frac{1}{2} LSB$  at 25 degrees C at full scale output current.

### 4.2 <u>COMPUTATIONAL ERRORS</u>:

Computational errors can be classified into the following three different types;

- 1) Errors in the phase angle calculation process where the phase angle in number of clock cycles has to be converted into degrees in hexadecimal number.

- 2) Errors due to the sine/cosine of the phase angle calculation. All entries in the look-up table are approximated to one byte long hexadecimal number. This approximation has an appreciable effect for angles between 84 to 90 degrees.

- 3) Errors resulted from the two-byte by two-byte divide routine.

Divide subroutine contributes largely to the total accumulated error in resistance and reactance calculation. This contribution is a function of the dividend and the divisor magnitudes. The quotient part of the division result is outputed to the D/A converter only and the remainder is discarded. The effect of discarding the remainder can be shown in an example. Assume that the input voltage is fixed at a value \$7F and in phase with the input current signal for illustrative purposes. For a current signal magnitude equal to \$30, the calculated impedance will be,

$$R = \left(\frac{\$7F}{\$30}\right)_{16} = \left(\frac{128}{48}\right)_{10}$$

$$R = \left(2.66\right)_{10}$$

$$X = 0$$

The divide routine will discard 0.666 and retain the quotient 2. The maximum R can be calculated by knowing the minimum allowed value of current signal which is equal to \$20,

$$R_{\text{max}}$$

=  $(\frac{\$7F}{\$20})_{16}$  =  $(\frac{128}{32})_{10}$

This value represents the maximum scale. The discarded value, 0.666, in the previous calculation gives an error of

% of full scale =

$$(\frac{0.66}{4})_{10}$$

= 16.65 %

By taking different magnitudes of the divisor, I, table 4.1 is constructed to show the percentage error in R calculations. It shows too that the maximum error occurs at minimum value of divisor and is equal to 21.9%, The effect of this error can be reduced by multi-precision division calculation.

Table 4.1 Error in impedance due to division calculation

Subroutine

| Input I                                                                                                                      | Imp                                                               | pedance                                                                                                                                          | % error of                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Hex value                                                                                                                    | Quotient                                                          | Remainder-                                                                                                                                       | full scale                                                                                         |

| \$20<br>\$21<br>\$22<br>\$23<br>\$24<br>\$25<br>\$26<br>\$27<br>\$28<br>\$30<br>\$35<br>\$40<br>\$50<br>\$60<br>\$70<br>\$80 | 43333333333222111<br>\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$ | 0.0<br>0.878<br>0.765<br>0.657<br>0.5555<br>0.459<br>0.368<br>0.282<br>0.20<br>0.122<br>0.666<br>0.415<br>0.462<br>0.60<br>0.333<br>0.143<br>0.0 | 21.9 % 19.1 % 16.4 % 13.9 % 11.5 % 9.2 % 7.0 % 5.1 % 16.66% 10.37% 11.50% 15.0 % 8.3 % 3.5 % 0.0 % |

Note: Remainder is listed in base 10

### 4.3 PHASE ANGLE, PEAK VOLTAGE/CURRENT CONSTANTS:

To calculate the peak values of both current and voltage signals, a voltage zero is detected first then the processor looks for a current zero by looping in a specified loop. During this looping process the processor keeps incrementing a counter by one count for each lap till a current zero is detected. The number stored in the counter, N, is the measure of the phase shift . The processor then waits for a period of 90 degrees by looping in a timing loop for 346 times. This constant is calculated by knowing the number of instructions, the time needed to execute each instruction in the loop and the processor clock period. The processor then will read the PIA #2 input register which will contain the peak value of the current signal. To calculate the voltage peak, the processor will look for the next voltage zerocrossing and waits a time equivalent to 90 degrees as it did for the current signal except that the constant will be 231.

Since the processor is running at lMHz frequency, the clock period is 1 sec, and for a 60 Hz system the count (N) in number of laps can be changed into degrees as follows:

#### $\theta$ = constant x N.

To complete one lap (one increment in N) the processor needs 20 seconds: calculated by knowing the number of instructions in this loop and the number of clock cycles needed to execute each instruction.

Since

$$\frac{46.3 \ \mu \ \text{sec/ degree}}{20 \ \mu \ \text{sec /degree}} = 2.31$$

the phase angle =  $0.4319 \times N$ , in degrees In hexadecimal form,

$$(0.4319)_{10} = (0.6E90)_{16}$$

Therefore

$$(\theta)_{10} = (0.6E90)_{16} N$$

After the phase angle is calculated, the sine and cosine are found out by the table look-up method.

A sine table for the phase angle was constructed and written into memory for angles beteen  $(0)_{10}$  to  $(90)_{10}$  degrees,  $(00)_{16}$  to  $(5\text{A})_{16}$ , in 1 degree increments which makes the table length equal to (5A) entries. This table is located at address \$F100 to F15A. The sine of any angle can be obtained by going to that location. To calculate the cosine of the same angle the processor calculates

$$\cos \theta = \sin (90 - \theta)$$

by using the same table. As was stated in Chapter 3, the sign of sine/cosine is indicated by setting a corresponding "R-X flag " register for each quadrant.

#### 4.4 ERROR AVERAGING TECHNIQUE:

of the sources of computational errors discussed earlier contributes to the total error in the output signal. This total error was found to be an unacceptable percentage of the total output signal. Therefore, an output signal averaging subroutine was developed. This routine performs the duty of filtering the errors resulting from the computation process before outputing the resistance and reactance values to the peripheral device. This duty is accomplished by av-During the device starteraging 8 samples of calculation. ing process and after a reset signal a stack of 16 consecutive values, 8 for average resistance calculation and 8 for average reactance calculation, is cleared and the first sample of R and X is divided by 8 using the logic shift-right instruction three times. This first sample is stored in the stack and the PIA output register. The processor then loops back to calculate the second sample. After 8 samples have been added, the processor outputs the stack sum to the PIA to give the average value of 8 calculations.

After the processor obtains the first sample in the next cycle, it subtracts the oldest one from the total sum of the stack and adds the new one to both the stack and the stack sum for outputing.

### Chapter V

#### DEVICE TESTING AND CALIBRATION PROCEDURE

To determine the accuracy and performance of this device two different types of tests were performed. In the first test the device was subjected to steady state-conditions and in the second test, to transient conditions.

#### 5.1 DEVICE TESTING AND RESULTS:

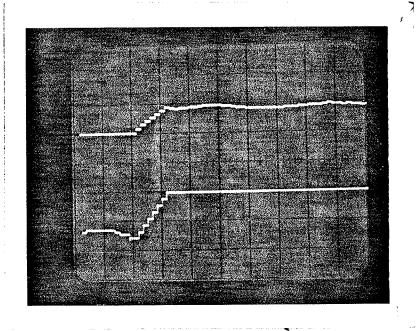

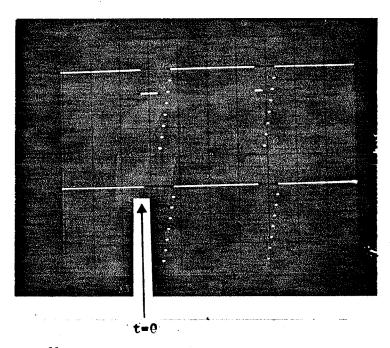

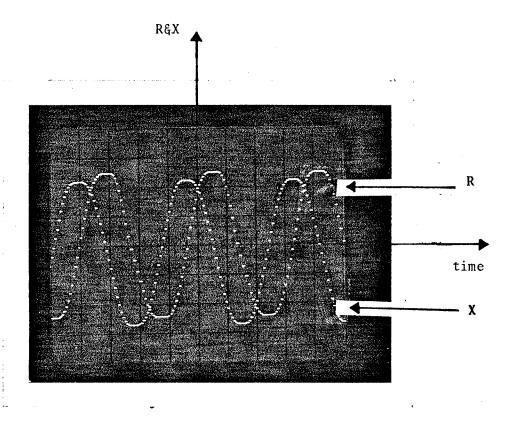

In the first test two steady-state signals where applied at the input terminals V and I with amplitudes  $\pm 8.9~V_{p-p}$  at 60-Hz and  $\pm 4~V_{p-p}$  at 60-Hz respectively. When the device was reset and running, the output resistance and reactance where observed on a two channel oscilloscope as a function of time and shown in figures 5.1a and 5.1b. These figures show that when the device is reset ,t=0, the output R and X are zero and start increasing in eight steps to their full values. This is the result of the 8-samples averaging routine mentioned in Chapter 4. The length of each step is the time taken by the program to detect the V and I zero crossing and performing the calculation cycle. This time (t<sub>s</sub>) is equal to

$t_s = 0.2 \times 0.2 \text{ sec/div}$

= 0.04 seconds

Fig. 5.1a

Fig. 5.1b

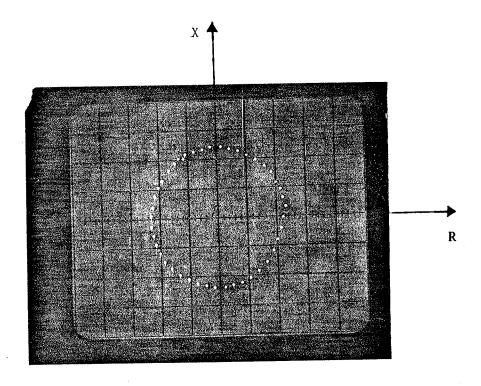

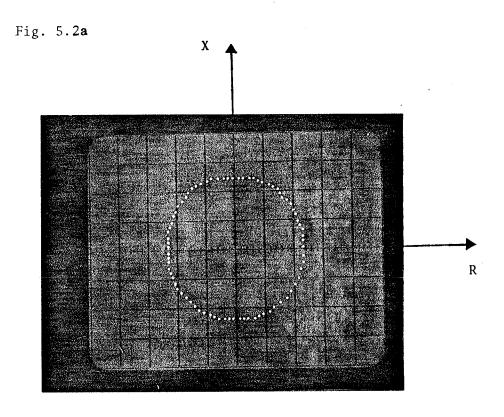

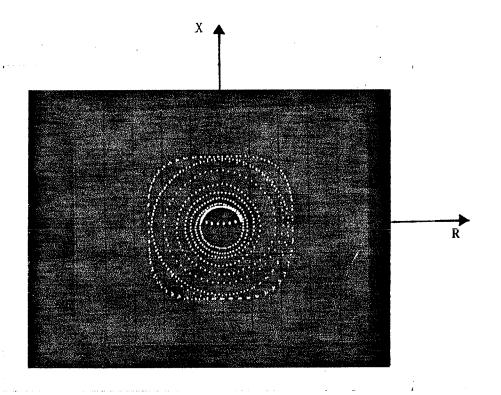

Figure 5.2a shows a plot of R versus X for 60-Hz input voltage signal and a 60.4-Hz input current signal. difference in frequency is to simulate continuously variable The amplitude of both signals is constant. phase shift. The plot in figure 5.2b is an n-sided polygon. The reason for not being a circle is that the phase shift does not vary fast enough for the program to calculate new values for R and X and keep on outputing the same values till a new set of calculations are made. Another reason is the number saturation due to the multiplication and division subroutines. The effect of these sources of errors appears in fig.5.2d where the flat sides in the outermost distorted circle are due to number saturation and the limitation imposed on the minimum current signal to be \$20. Figure 5.2c shows R and X versus time plot were flat peaks are due to the same reasons.

In the second test, the device was connected to the BICEPS machine as shown in figure 5.3. The current and voltage transformers are connected to phase 2. Line switching transients were created by switching the line length from 1.5pu to 2.75pu. This is accomplished by using a switch, not shown in the figure, to change line length to one of four different pre-set line lengths. As was explained in chapter 2, the power transfer capability of the system will decrease by switching off one of the lines in fig. 2.5a.

Fig. 5.2b

Fig. 5.2c

Fig 5.2d

Fig. 5.3: Transient test connection on the BICEPS machine

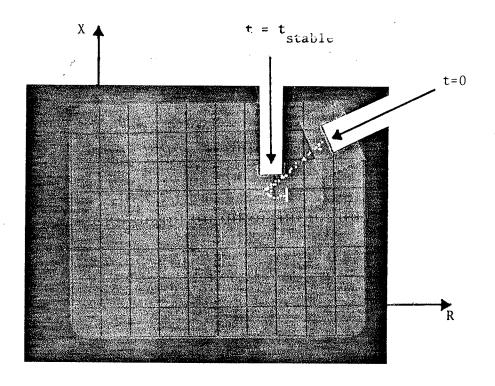

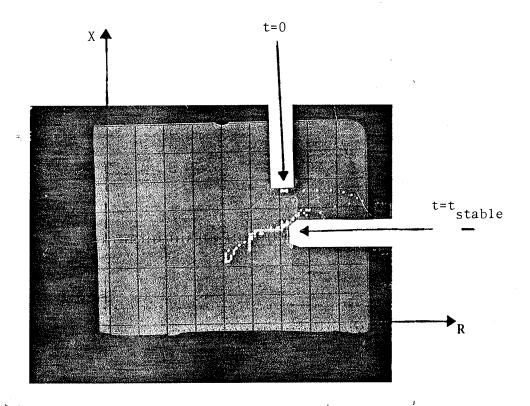

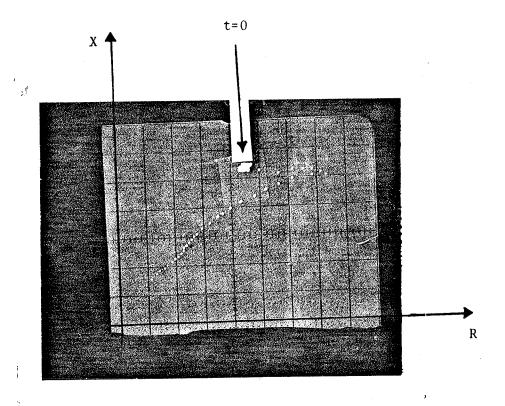

Following the same argument, the generator was loaded to 0.65pu at a line length of 1.5pu. The corresponding system operating point on the impedance plane is shown in figure 5.4a at point t=0. After line switching to 2.75pu, the operating point was oscillating along the dotted curve as shown and finally stabilized at t=t . Each dot on this curve corresponds to one R and X calculation. Generator loading was increased to 0.68pu at line length of 1.5pu. After switching to 2.75pu, the system was stable with the operating point oscillating along the dotted locus as shown in Figure 5.4b.

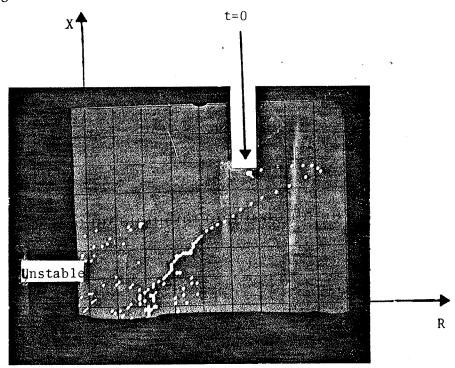

To obtain an unstable transient, the generator was loaded to 0.75pu at line length =1.5pu. By switching to 2.75pu line length, the impedance locus was displayed on the scope screen as shown in Figure 5.5b in dotted line. The area shown by the 'unstable' sign indicates that the impedance display device could not generate the proper impedance locus. A smooth curve as shown on Figure 2.6a is the desired target. An 8-sample averaging routine was developed, to filter out the accumulated calculation error, and the device was tested one more time. One effect of this routine is to slow down the device response, a penalty for obtaining smooth curves under steady-state tests as shown in Figures 5.2c and 5.3a.

Fig. 5.4a Stable transient ( p = .65 pu )

F.ig. 5.4b Stable transient ( p = .68 pu )

Fig 5.5a

Fig. 5.5b Unstable power swing

# 5.2 DEVICE CALIBRATION PROCEDURE:

To calibrate the device, apply input sinusoidal voltages at the specified terminals analog input (V) and analog input (I) in Fig. 5.6. The analog input voltage range is -8.9 < V < +8.9 volts and the analog input current signal is -4 < V <+4 volts. The input signal conditioning circuits adjust these signals to the range accepted by the A/D converters 0 < V < +5 Volt).

Trim pots TR3 and TR7 are used for signal biasing. Trim pots TR2 and TR6 are used to adjust operational amplifier gains.

The following steps are recommended for troubleshooting and device calibration:

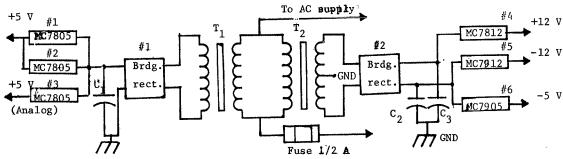

- 1. This device runs on 5V DC and 12V DC. Test power supply circuit in Figure 5.1b for noise and ripple\_free power supply

- 2. Apply a full scale 60 Hz analog voltage signal (-8.9v to +8.9v) to terminal Analog input (v) in figure 5.la. A biased signal, (0v to +5v) should appear on terminal #6 on the A/D converter #1. If not, check the input signal conditioning circuit #1.

- 3. Apply a full scale 60 Hz analog current signal (-4v to +4v) to terminal Analog input (i). A biased signal (0v to +5v) should appear at terminal #6 on the A/D converter #2. If not, check the input signal conditioning circuit #2.

Fig. 5.6a Impedance display unit board layout

Fig. 5.6b power supply circuit

- 4. The microprocessor runs at a lMHz frequency. This can be checked from terminal E by using an oscilloscope. The same clock signal shoul appear at pin 25 on PIAs #1 and #2, if not, check the crystal circuit.

- 5. For Chip selection and software changes, the Diagnostic Emulator should be used as follows:

- a) Connect the emulator Probe into the microprocessor socket.

- b) Switch Emulator ON. RESET and CLK indicators should be off; otherwise check the RESET or Crystal circuit as required.

- c) With the RAMOVERLAY switches in the OFF position the Emulator display should read \$F000 otherwise check decoder circuit.

- d) When all above points are properly checked and corrected as required, decoding of the peripheral devices #1 and #2 should be tested as follows:

First: initialize both PIAs as shown in the software program. Call memory locations \$E000 and \$D000 on the address display. Pressing the Emulator EXAM key the DATA readout should give the digital word for each analog input. If not, check PIAs and A/D converters.

Second: call memory locations \$E002 and #D002 and push \$FF in each. A scope at Analog output (R) and analog output (X) on Fig. 5.6a should read +2.5 volt,

if not, check PIAs and the output signal conditioning circuits for adjustments.

Third: Into the same memory locations, \$E000 and \$D000, push \$7F, adjust trim pots TR4 and TR8 to obtain a zero volt output on the scope.

6. Apply the analog input signals (I) and (V) to the device vice then press the Emulator RUN key, the device should run giving the calculated resistance and reactance. If the device does not run repeat steps 1 through 6.

# Chapter VI

### CONCLUSIONS

- 1. This device is capable of computing and displaying, in real time, the impedance seen at a point in a power system.

- 2. Tests under steady-state conditions with simulated phase shift indicate that the device is able to generate a smooth impedance locus in spite of the errors accumulated during the R and X calculation process (mainly in the divide routine where the remainder of the division is discarded).

- 3. Stable transient tests on a model power system resulted in an acceptable swing locus, but the error was appreciable during an unstable transient test. Filtering out this error by an 8-sample averaging routine was effective in smoothing out the impedance locus but resulted in degraded dynamic response.

In light of these results, the author would like to recomend the following to enhance the device performance and duties:

- 1) Develope a software algorithm to plot the actual relay characteristics on the oscilloscope screen possibly by using the existing hardware.

- 2) Optimize the device performance by implementing multiprecision divide and multiply calculations.

3) Design a digital read-out using the existing software algorithm as an enhancement to the BICEPS teaching tool.

## Appendix A

#### BIBLIOGRAPHY

- 1) Ronald L. Krutz, "Microprocessors And Logic Design," John Wiley & sons, Inc. 1980

- 2) General Electric, "Use of R-X diagram in relay works," switchgear puplications, GET - 2230b, 1966

- 3) W.A. Elmore, "Fundamentals of out-of-step Relaying," Westinghous electric Corporation, Relay - Instrument division, January 1979.

- 4) Edith Clarke, "Impedances seen by relays during power swings with and without faults," AIEE Transactions, Vol. 64, 1945, pp 372-384

- 5) Herbert Brunner, "Introduction to Microprocessors,"

Resto puplishing company, INc. 1981

- 6) National Semiconductors, " Data Conversion Acquisition Databook," 1980

- 7) Joseph D. Greenfeild, William Wray, "Using Microprocessors and Microcomputers: The 6800 Family," John Wiley & sons, 1981.

- 8) A.R. vanC. Warrington, "Protective Relays: Their Theory

And Practice volume two," John Wiley & sons 1978

- 9) William D. Stevenson, Jr., "Elements of power systems,"

McGraw-Hill Book company, 1982

- 10) L.M. Wedepohl, " Polarized Mho Distance Relays, New

- approach to the analysis of practical characteristics," IEE PROC. Vol 122, No. 3, March 1965

- 11) Lance A. Leventhal, " Introduction to Microprocessors

Software, Hardware, Programing,"

- 12) Motorola Incorporation, "Linear Interface Integrated Circuits," 1979

```

SO OS OCCO 48 44 52 1B

$1 13 FOOC CE OC 04 FF 00 00 CE FF 04 FF DO 02 CE OC 04 FF ES

$1 13 FOOC CE OC 04 FF 00 00 CE FF 04 FF DO 02 CE OC 04 FF ES

$1 13 FOOC CE OC 05 FF 04 FF EO 02 FE FA 10 7F CS $1 8F 00 3A

$1 13 FOOC 08 7C CS $1 85 CS $1 $1 17 28 F3 8E FA 02 FE FA ES

$1 13 FO3O 00 B5 DO 00 81 FA 08 2B 02 20 F8 85 DO 00 B1 FA 1F

$1 13 FO3O 00 B5 DO 00 F1 FA 08 2B 02 20 F8 85 DO 00 B1 FA 1F

$1 13 FO5C 08 01 01 09 08 ED 00 0F 1 FA 08 2B 02 02 F5 FF CA 02 FE FA DS

$1 13 FO5C 08 01 01 09 08 ED FC F8 ED 00 F1 FA 08 2B 02 02 FF FA DS

$1 13 FO5C 08 01 01 09 08 ED FC F8 ED 00 F1 FA 08 2B 02 02 FF FA DS

$1 13 FO5C 08 01 01 09 08 ED FC F8 ED 00 F1 FA 08 2A 02 FC F8 ED

$1 13 FO5C 08 61 FA 08 2B 02 20 F5 B8 DO 00 B1 FA 08 2A 02 20 11

$1 13 FO5C 08 FF FE FA 04 01 02 08 08 ED 00 B1 FA 08 2A 02 20 11

$1 13 FO5C 08 FF FE FA 04 01 DS 08 08 ED 00 B1 FA 08 CD 08 7 CA 03 DS

$1 13 FO5C 08 FF FE FA 04 01 DS 08 CB FF CC 02 B8 CA 02 B7 CC 03 D1

$1 13 FO5C 08 FF FE FA 04 01 FD 00 B8 CC 08 B7 CA 03 F8 18

$1 08 FOSC CC 08 F7 CA 02 FE F4 00 4E

$2 SB 03 0000 FC

```

MOTORDLA MESSAM CROSS-ASSEMBLER

PAGE 1

# MOBSAM IS THE PROPERTY OF MOTOROLA SPD. INC

MOTORDLA MESOO CROSS ASSEMBLER, RELEASE 1.3 MODIFIED IAMC VER: 1.0

```

NAM PEAKPICK

DRG SFOOO

C0002 F000

C0002

00003

00004

C0008

00008

PEAK PICKING ROUTINE & PHASE ANGLE CALCULATION

00007

00008

00009

00010 F000 CE 0004

00011 F003 FF D000

00012 F005 CE PF04

00013 F005 FF D002

00014 F00C CE 0004

00015 F00C CE 0004

00015 F012 CE FF04

00017 F015 FF E002

00018 F018 FF E002

00018 F018 FF E002

00019 F018 FF C881

00020 F018 FF C881

00020 F018 F0 C881

00021 F020 08 INK

00022 F021 7C C881

00023 F024 85 C851

00024 F027 81 7

00008

#$04

$000

#$FF04

$D002

#$000

#$FF04

$E002

$FA10

$C861

0, X

LDX

STX

LDX

STX

INIT. Pla2 INPUT REGISTERS

LDAD IND. REG. WITH MEX SPFO

INIT. PIA2 DUTPUT REGISTERS

LOAD IND. REGISTER WITH MEX.

INIT. PIA1 INPUT REGISTERS

LOAD INDEX REGISTER WITH SPFO

INIT. PIA1 OUTPUT REGISTERS

LDAD IX WITH STARTING ADDRESS

LDX

STX

LDX

STX

LDX

CLEAR BYTE COUNT

CLEAR LOCATION INDICATED BY I

CLR

CLEAR

INC SCS61

LDA A $CS61

CMP A #$17

BM1 CLEAR

INCREMENT COUNTER

LOAD ACC.A WITH COUNT VALUE

BRANCH TO CLEAR REST OF TABLE

```

```

| OCCUPATION | COCCUPATION | C

```

P A.P C. MOTOROLA MESSAM CROSS-ASSEMBLER

PAGE 2

00055 F06D B5 D000 P1A2V1 LDA A SD000 CD056 F070 B1 FA08 CMP A SFA05 CDMPARE INST. VALUE OF V WITH 00057 F073 28 02 BMI P1A2V2 D0058 F075 20 F5 BMI P1A2V2 LDA A SD000 CMP A SFA06 CDMPARE INST. VALUE OF V WITH 00058 F075 20 F6 BRA P1A2V2 BRANCH ALWAYS LDAD ACC.A WITH INST. VALUE OF V WITH 00058 F075 20 F6 BRA P1A2V2 BRANCH ALWAYS LOAD ACC.A WITH INST. VALUE OF V WITH 00058 F075 20 F6 BRA P1A2V2 BRANCH IV V > SA0 BRANCH IV V

```

00070 F08D B7 CA0A

00071 F080 &8 8E

00072 F085 C8 80

00074 F085 C8 80

00074 F087 F7 CC02

00075 F08A 86 CA02

00077 F08D 87 CC03

00077 F08D 87 CC03

00078 F08D 87 CC03

00078 F08A 87 C004

00080 F08A 87 CA03

00081 F08A 87 CA03

00082 F08F F CA03

00083 F08F F CA03

00084 F08F 7 E F400

00085 F000

00087 F000 0001

00088 F400 0001

SCAOA

#SEE

SCCOO

SCCOO2

SCCOO3

SCCOO3

SCCOO4

SCCOO3

SCCOO5

STORE MAX. VALUE OF V

LOAD ACC.A WITH A CONSTANT SE

INITIALISE MUL2RTH

JUMP TO SINCOS SUBROUTINE

ORG

RMB

ORG

RMB

END

$ F D O O

MUL2RT

$F400

SINSTR

00010

SYMBOL TABLE

BIGIN

STX1

44 52

144 52

1C 7F CA 42

48 25

F1 F0 CO 27

F1 F1 F0 CO 27

F1 F0 CO

PIA2VH FO3B

PIA2V1 FO8D

SINSTR F400

18 FAD 38 FAD 38 FAD 38 CA 37 CA 20 B 7 CA 20 B 7 CA 20 CA 20 CA 20 CA 21 C CA 21 C CA 21 C CA 21 C CA 20 CA

OTFA2A28547A807510AEF2E

7AC7108D8AB07AA1EDC8E7

C17CBOCBC17OO11F57C7FC

07FABAF252C5103707AFA32

7FAD807781AD187A7AC84C7

C17C2CC2F380FC001FCBBC

7FA3022007EADCA777033ACCAA11

7C3F24F82F0F17C3FA8103

27C157AA208891AC6A7A781

13FACESAA10SAA5ADDASA0AA1

3102097765070000878118

```

13 F550 13 F570 13 F550 13 F550 13 F550 08 F550 03 0000 DO 38 F6 F5 CA FA 00 AA 70 B7 CA CA 08 10 25 7C F3 43 7E 87 14 CA A1 F5 CA F8 24 F7 00 58 12 CA 8D 28 3E 88 41 F5 CA 85 CA 1A 43 10 5A F7 F6 58 06 7C CA F7 80 EE CA 12 CA FF FF 38 87 17 CA FF 7C CA 86 43 \$ 1 \$ 1 \$ 1 \$ 1 \$ 1 \$ 1 \$ 9 C 6 40 24 BD BO CA FE E1 CA 60 43 F7 0E 27 88 CA CA 86 04 5A 24 43 7E

PAGE

#### MESSAM IS THE PROPERTY OF MOTOROLA SPD. INC COPYRIGHT 1974 TO 1976 BY MOTOROLA INC

MOTOROLA MESSAM CROSS-ASSEMBLER

MOTOROLA M6800 CROSS ASSEMBLER, RELEASE 1.3 MODIFIED IAME VER: 1.0

| 00001 |      |     |         |        | NAM     |     |       | NE    |       |      |     |     |     |     |     |     |      |     |      |     |    |     |     |     |     |     |     |

|-------|------|-----|---------|--------|---------|-----|-------|-------|-------|------|-----|-----|-----|-----|-----|-----|------|-----|------|-----|----|-----|-----|-----|-----|-----|-----|

| 00002 | F400 |     |         |        | DRG     |     |       | 40    |       |      |     |     |     |     |     |     |      |     |      |     |    |     |     |     |     |     |     |

| 00003 |      |     |         |        |         |     |       |       |       |      |     |     |     |     |     |     |      | ٠.  |      |     |    |     |     |     |     |     |     |