# VLSI Implementation of a Digital Neural Network with On-Chip Learning

by

#### Darrell Gates

A thesis

presented to the University of Manitoba

in partial fulfillment of the requirements

for the degree of

Master of Science

Department of Electrical and Computer Engineering University of Manitoba Winnipeg, Canada 1990

© Darrell Gates 1990

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada-de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-71831-5

# VSLI IMPLEMENTATION OF A DIGITAL NEURAL NETWORK WITH ON-CHIP LEARNING

bу

Darrell Gates

A thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements of the degree of

Master of Science

#### © 1990

Permission has been granted to the LIBRARY OF THE UNIVER-SITY OF MANITOBA to lend or sell copies of this thesis, to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

## Abstract

This thesis explores the VLSI implementation of a neural network with on-chip learning capabilities. This digital ASIC is intended to be used as the basis for a high-speed neural accelerator board. A unique digital neural network architecture is presented and analyzed. A novel VLSI design style is introduced and developed. Implementation details and design issues are also presented. Fundamental issues of neural networks are introduced and major learning paradigms are discussed. A thorough examination of digital ANNs is presented.

## Acknowledgements

With the encouragement and support of Dr. Howard Card, this thesis has finally become a reality. Many thanks to the 'boys' in the VLSI lab.

A special thanks to DB.

This work was partially supported through funding from the Natural Sciences and Engineering Research Council of Canada and through equipment loans from the Canadian Microelectronics Corporation.

# Contents

| List of Tables |                            |                              | viii |  |

|----------------|----------------------------|------------------------------|------|--|

|                | List                       | t of Figures                 | ix   |  |

| 1              | Inti                       | roduction                    | 1    |  |

|                | 1.1                        | Purpose                      | 8    |  |

|                | 1.2                        | The Problem                  | 9    |  |

|                | 1.3                        | Scope                        | 10   |  |

| 2              | Bac                        | kground                      | 12   |  |

|                | 2.1                        | Neural Networks              | 12   |  |

|                |                            | 2.1.1 Chronology of Events   | 14   |  |

|                |                            | 2.1.2 Model of a Neuron      | 16   |  |

|                |                            | 2.1.3 Topologies             | 19   |  |

|                | 2.2                        | Learning Paradigms           | 21   |  |

|                | 2.3                        | Artificial Neural Networks   | 32   |  |

| 3              | Implementation and Results |                              |      |  |

|                | 3.1                        | Considerations               | 47   |  |

|                | 3.2                        | A VLSI Design Strategy       | 50   |  |

|                | 3.3                        | Implementation in Silicon    | 61   |  |

| 4              | Con                        | clusions and Recommendations | 82   |  |

| A              | Gen                        | neralized Delta Rule         | 84   |  |

# List of Figures

| 2.1  | Difficult Perceptron Convergence Task                             | 15 |

|------|-------------------------------------------------------------------|----|

| 2.2  | Simplified Neuron Models                                          | 17 |

| 2.3  | Typical Activation Functions                                      | 18 |

| 2.4  | Multi-layer Feedforward Network                                   | 19 |

| 2.5  | Single-layer Feedback Network (Hopfield)                          | 20 |

| 2.6  | Overview of Backpropagation Learning Applied to a 3-layer Network | 28 |

| 2.7  | Sigmoid Function (and derivative)                                 | 29 |

| 2.8  | Error Surface with Local Minima                                   | 30 |

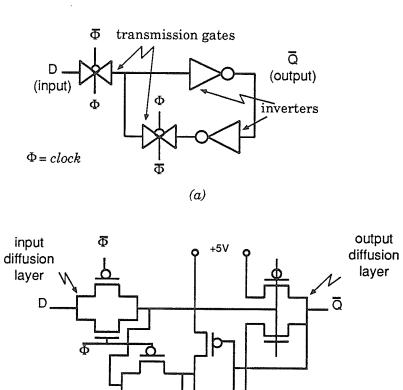

| 3.1  | Simple Static DFF                                                 | 55 |

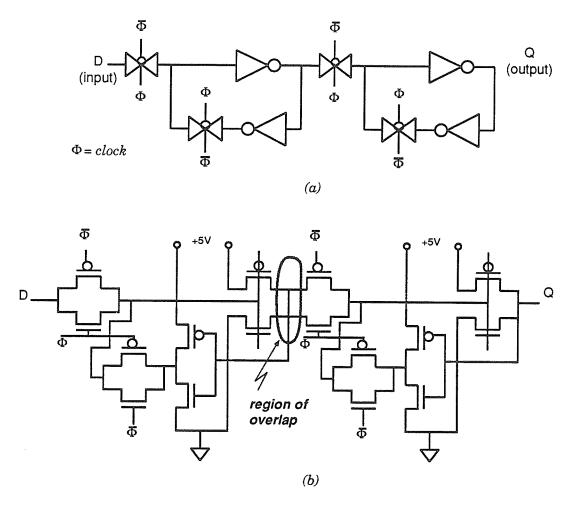

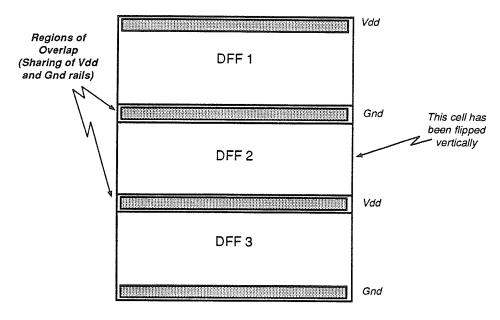

| 3.2  | Overlapping in a 2-bit Shift Register                             | 57 |

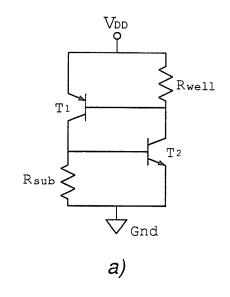

| 3.3  | CMOS Latchup                                                      | 59 |

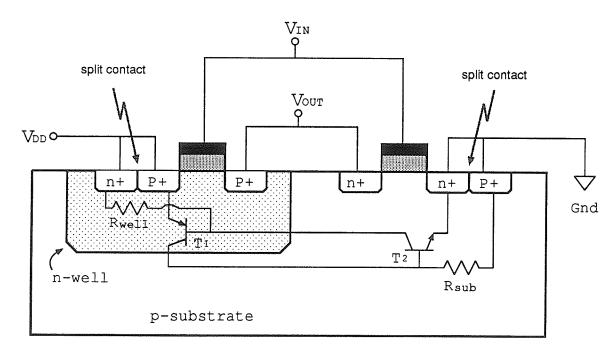

| 3.4  | Stacked (overlapped) DFF Cells                                    | 60 |

| 3.5  | Overview of Backpropagation Layer                                 | 62 |

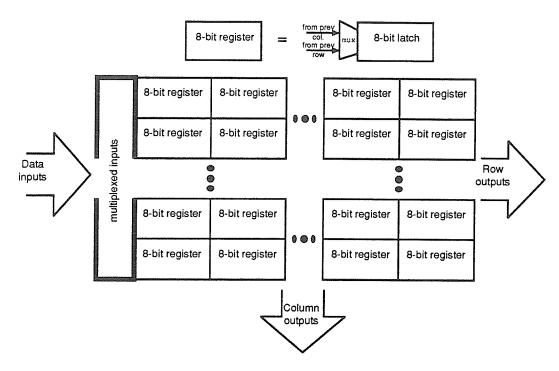

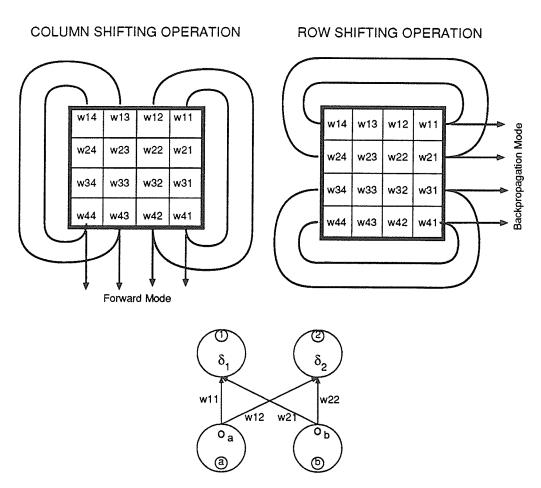

| 3.6  | Architecture for Backpropagation Neural Network                   | 63 |

| 3.7  | Bit-Serial Pipelined Multiplier Cell                              | 65 |

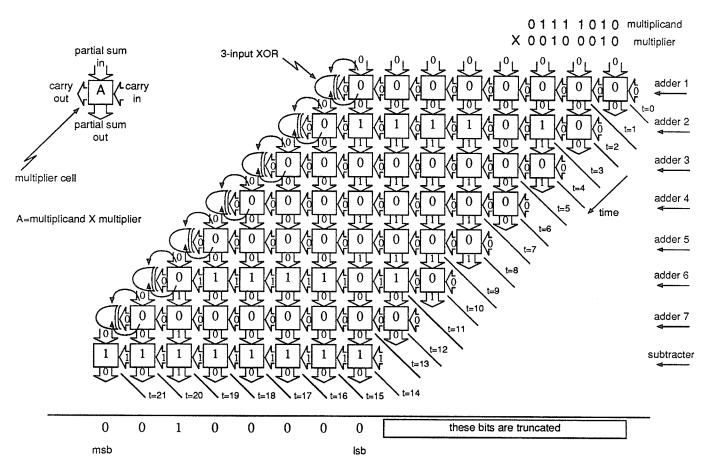

| 3.8  | Bit-Serial Pipelined Multiplier                                   | 66 |

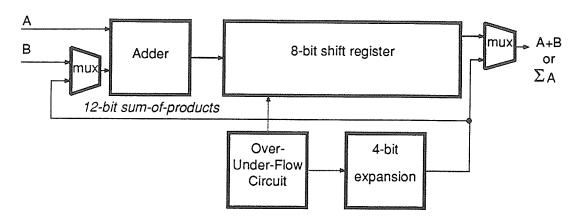

| 3.9  | Bit-Serial Pipelined Adder                                        | 67 |

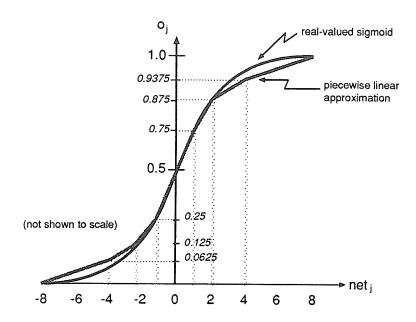

| 3.10 | Sigmoid Function                                                  | 68 |

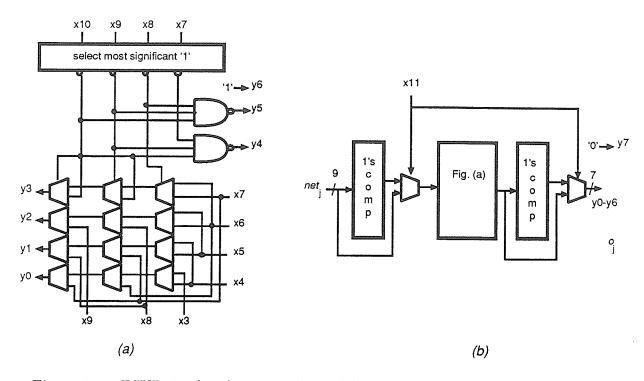

| 3.11 |                                                                   | 69 |

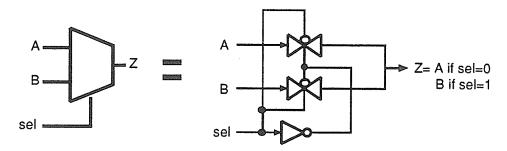

| 3.12 | 2-Input Active Multiplexor                                        | 70 |

| 3.13 | Synaptic Weight Register                                    | 73 |

|------|-------------------------------------------------------------|----|

| 3.14 | Reconfiguration to Support Backpropagation Learning         | 75 |

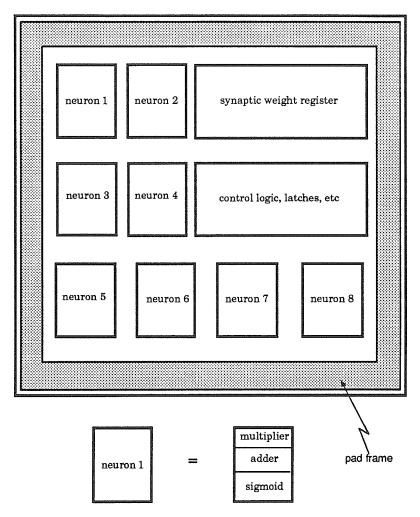

| 3.15 | Neural Network with Backpropagation Paradigm ASIC           | 78 |

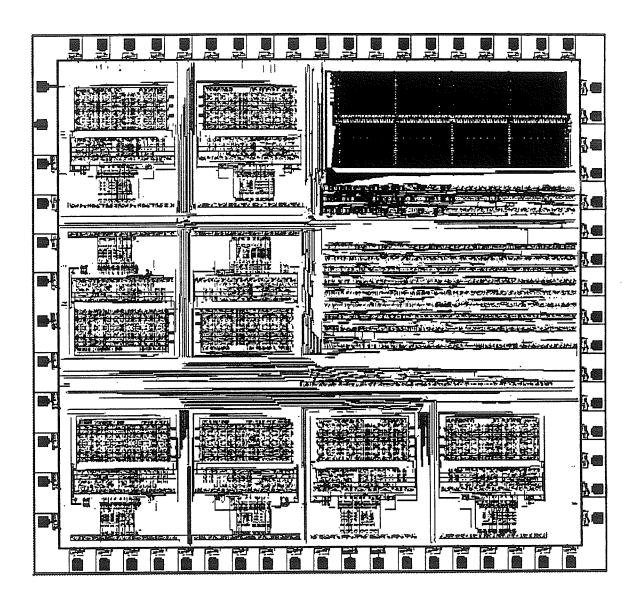

| 3.16 | Block-level Diagram of the ASIC Layout                      | 79 |

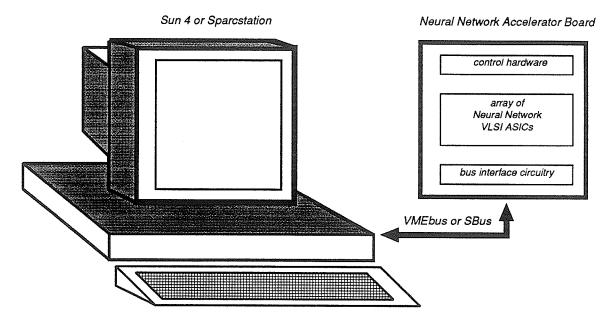

| 3.17 | Typical use of the VLSI ASIC in a Neural Network Simulation |    |

|      | System                                                      | 81 |

# List of Tables

| 2.1 | Comparison of the Brain and Neural Network Computing | 13 |

|-----|------------------------------------------------------|----|

| 3.1 | PWL Activation Truth Table for Positive Input        | 70 |

| 3.2 | Comparison of Multiplier Architectures               | 72 |

| 3.3 | General ASIC Description                             | 80 |

## Chapter 1

## Introduction

Artificial Intelligence (AI) is a broad term which encompasses all computer systems that can exhibit some form of human intelligence. These *human-like* computers are capable of performing operations that are analogous to the human capacities of learning and decision-making.

Computers that can exhibit some form of human-like intelligence based upon certain rules or statistical inferences have been the mainstream of traditional AI expert systems. These expert systems have traditionally been of assistance in situations involving the laborious task of making sense out of large amounts of data (such as the databases currently being used in the medical profession for making preliminary diagnoses) or in performing tasks that any human would consider to be too tedious (such as a robotic arm used in manufacturing) or too dangerous (such as a robotic arm used in a nuclear energy plant). However, all of these traditional AI systems suffer from serious flaws. These expert systems require permanent operators and preprogrammed sets of rules for their operation—all of which have a dramatic effect on the overall ability of the system to perform well in new environments and under

different circumstances.

A relatively new area of AI has emerged in the last few years. Researchers, in order to distance themselves from traditional AI and to emphasize the fact that the field contains new approaches to AI, have coined the term **neural networks** for this new discipline.

In the 1950s, researchers discovered that architectures of simple processing elements configured in a specific order and performing simple calculations could exhibit brain-like properties. That is, a network of interconnected processing elements¹ could make semi-intelligent decisions based upon experience alone, and could easily adapt to new situations without having to be reprogrammed. This discovery was in sharp contrast to traditional AI theories, wherein large rule-based systems that had been painstakingly programmed with responses to a certain situation could be outperformed by a simple neural network that had been trained to respond to the same situation. A neural network, like a human, could be taught to recognize and recall without the use of any a priori knowledge of a particular problem—only a training set of typical input/output data was required.

These two branches of AI, i.e. neural networks and traditional AI, were now competing for research supremacy. In the 1960s, a book on *Perceptrons* [1] dealt a harsh blow to the field of neural networks. The basic premise of this book was that a neural network could **not** perform even the simplest of tasks, such as the XOR problem,<sup>2</sup> and that the expert systems developed by the traditional AI theorists were the **only**

<sup>&</sup>lt;sup>1</sup>These interconnected processing elements were called 'neurons' and 'synapses' to stress the fact that the algorithms being implemented came from brain theories in psychology and biology.

<sup>&</sup>lt;sup>2</sup>The XOR problem can be stated as follows: The XOR (exclusive OR) of two inputs is TRUE if either (but not both) of the inputs are TRUE.

systems that could mimic true human-like behavior. For almost the next two decades, most AI research would be guided by traditional rule-based expert systems. Neural network researchers (connectionists) were relegated to the backroom—it appeared as though neural networks had experienced their demise.

However, true and dedicated connectionists were quietly working in their underground laboratories applying discoveries that biologists and psychologists had made about the brain. The neural network revolution was slowly maturing; and, with the publication of Parallel Distributed Processing [2, 3] in the eighties, there was a resurgence of interest in neural networks.

Connectionists were stressing the fact that neural networks possessed 'natural intelligence' as opposed to 'artificial intelligence' — that neural networks contained implementations of the *natural* way in which the brain functions. The notion of a computer that could mimic the human mind, and actually think, had researchers from all disciplines jumping on the proverbial 'bandwagon'. Imagine—a computer that could actually think, reason, make judgements, and make the same decisions that we, as humans, might also make! This excitement was also fueled by the multitude of science fiction writers who envisioned worlds run by computers, and Hollywood movie moguls who instilled in us the visions of futuristic computer technology with human-like qualities—little did they know that they were just 'fueling the fire' for connectionists to showcase their novel ideas and present an enhanced discipline that seemed far superior to traditional AI. Neural networks was once again being considered as a credible research field.

Traditional AI systems have failed when it comes to being able to make intelligent

choices in unanticipated situations; this is where neural networks can excel and should be used to take over from where a traditional AI system leaves off.

Picture the following scenarios:

... You are commissioned with the responsibility for the safety of all passengers on a major commercial airline. You are aware that the latest threat to airlines is plastic explosives concealed in luggage and you know that an x-ray machine to discover weapons being smuggled aboard has been 'pushed to the limit'. A trained dog could be used to sniff all baggage before it is loaded onto the plane; however, most passengers would not appreciate the delays and a trained nose of a dog could be tricked with other overpowering scents. You, yourself, could examine every piece of luggage that is checked, but this would be a very slow and expensive process. Imagine if you could employ a computer (something like a robotic dog) that was trained to 'sniff' every piece of luggage and make an intelligent decision as to the possibility of a concealed bomb, without the use of any type of human operator (which an x-ray machine requires).

... You are driving to the restaurant and you notice that your dinner reservations are not for another hour. You pick up the phone and advise the limousine driver to drive around the city so that you can impress the lady that you are with and get to know her a little better. The car speeds up and takes you past all the hot spots—so that you can impress your friends too. You finally arrive at the restaurant, on time, and you're a big hit with the lady. Out of the kindness of your heart you decide to tip the limousine driver \$50 before you go. As you lean into the front seat, you discover, to your amazement, that the driver is actually a computer that has been trained to drive the car (and all along you thought he was just short). You can't believe the skill with which this machine has negotiated all the hazards of the road. Since you are an educated engineer, you marvel at the reality of such a futuristic machine, pocket the \$50, and enter the restaurant.

... You are engaged in some type of intelligent conversation with a machine that makes human-like decisions and responds through verbal communication, and accepts and executes verbal orders in a quasi-intelligent manner. Imagine the possibilities ... a computer that could actually think and talk.

Does this sound like science fiction? Or does it touch on reality? All of these stories were once in the minds of people with 'wild' imaginations; however, with current advancements in neural network technology, these futuristic idealities have almost become a present-day reality.

In fact, a system that can detect bombs concealed in baggage is already operating at several major international airports in the world. This system, called SNOOPE (System for Nuclear On-line Observation of Potential Explosives), developed by Science Applications International Corp. (SAIC), uses a neural network that makes decisions about baggages that may contain a bomb. SNOOPE is mainly hardwarebased with an expert system and a neural network that complement each other in the decision-making process. The neural network takes over from the point where the rule-based system tends to fail. According to an SAIC sales brochure, the system works by exposing the luggage to "low energy (thermal) neutrons and analyzing the gamma rays resulting from neutron absorption by atomic elements in the luggage. The computer software searches for specific combinations of atomic elements that characterize explosives." The expert system follows rules that are preprogrammed for known explosive compositions while the neural network has been trained to recognize these specific compositions. The neural network can also generalize to other combinations of atomic elements that may characterize explosives—compositions that have not been specified in the expert system. The system does not require a human operator to interpret the data; rather, the system makes an intelligent decision based on its current knowledge.

Real-world problems require neural networks that can generalize in situations not previously encountered. Being able to properly generalize is important for an unmanned vehicle to navigate a territory that is unfamiliar. This is exactly the case with **ALVINN** (Autonomous Land Vehicle In a Neural Network), developed at Carnegie-Mellon University (CMU) by D.A. Pomerleau et al., where the goal is to allow the vehicle to navigate along a winding road. Sensor inputs to the neural

network are through video cameras that act as a "video retina" [4]. The neural network embedded in the computer system of the vehicle is trained to recognize certain features of a typical roadway, such as trees and road edges, and is released on a previously uncharted roadway. The neural network has also been trained to steer the vehicle and to accelerate and decelerate. In order for the vehicle to make a completely autonomous navigation of the roadway, the training set is very important. If not enough information has been provided during training, the vehicle may not respond correctly. If it is given too much information, the vehicle may not be able to adapt to new situations. Presently, the vehicle can accurately drive at  $3\frac{1}{2}$  mph along a short path, under various conditions of weather and lighting. This is double the speed of that achieved by ALVINN using a non-neural network system in attempting to drive the same pathway. While 'unmanned driving' has not yet progressed to the same level of confidence as that of the limousine driver pictured in our scenario, it is definitely a step in the same direction.

One of the classic examples of a neural network that demonstrates impressive potential is NETtalk; a computer program developed by Terence Sejnowski and Charles Rosenberg. The program configures a neural network that learns to read English text aloud without having to use linguistic rules. The neural network is shown a textual conversation that had been transcribed by a linguist into the correct phonemes. The difference between the network's response and the correct response is 'how' the neural network is trained to read the text. Just like children who learn to speak by listening, trying and being corrected, the neural network will 'pick up on' all the regularities and exceptions in the pronunciation of the English text. This flexible learning process is in stark contrast to the rigid requirements of an expert

system, which must have a large database of linguistic rules, words and pronunciation examples stored in memory. The English language is very confusing—we don't always follow the rules or say words as they are noted in the dictionary. It would take an expert system just to program all the rules into another expert system that could handle English speech as well as NETtalk does. However, neural networks, in this extraordinary example of their power, have gotten us a step closer to the talking computer.

The three systems presented are excellent examples of neural networks currently operating in the 'real world'. Granted, they exhibit only some resemblance to the scenarios pictured previously, but the use of neural networks is currently in its infancy. However, the fine line between science fiction and reality is becoming thinner with each new advancement in neural networks.

Although these systems exhibit three very different approaches to neural network implementations, they all utilize the same learning paradigm. A learning paradigm is a rule (or law or algorithm) that a neural network uses to modify its internal structure so that it may exhibit learning characteristics. There are many neural network architectures and many associated learning paradigms that are optimized for certain applications. One of these paradigms is the backpropagation of error learning rule (sometimes referred to as backpropagation, or simply backprop) that is used in each of the above examples to train the network to respond in a human-like manner. Both SNOOPE and ALVINN use dedicated hardware to implement the various equations that are inherent in the backpropagation algorithm. This algorithm requires many multiplications and additions that are performed in parallel—current Von Neumann-style serial computers do not have the power to efficiently execute

this algorithm. Therefore, SAIC and the researchers at CMU have each developed a general purpose digital signal processing hardware board that is used to accelerate most of the calculations required by the backpropagation algorithm. These systems operate mainly in a sequential fashion, and are optimized to do multiplication and addition in much the same way as today's Digital Signal Processing (DSP) integrated circuits. Thus, these systems are deficient of the inherent parallelism which gives neural networks their strength. Software could be partitioned into a parallel structure and run on a parallel computer, such as the Connection Machine; however, parallel computers are not that accessible.

Although these implementation strategies offer flexibility and short-term adequacy, we feel that the ultimate solution to making a computer that mimics the human mind is the implementation of a neural network in silicon. The advancement of Very Large Scale Integration (VLSI) technology has made the implementation of neural network paradigms<sup>3</sup> in a Application Specific Integrated Circuit (ASIC) a reality.

### 1.1 Purpose

The purpose of this thesis is the direct implementation of a neural network that is capable of performing on-chip learning utilizing the Backpropagation Learning Algorithm in a fully-digital VLSI ASIC. This chip is intended to be used as the basis for a neural hardware accelerator board for the purpose of increasing simulation speeds of feedforward neural network models.

<sup>&</sup>lt;sup>3</sup>A neural network paradigm refers to a neural network architecture and its underlying learning paradigm.

Since the current trend in artificial neural network research focuses on analog devices, we also want to look at the role that electronic digital hardware will play in future implementations of neural network models.

#### 1.2 The Problem

Artificial Neural Networks (ANNs) are still in their infancy and until parallel computing architectures become the *norm*, connectionists will have to simulate neural network paradigms on traditional Von Neumann-style serial computers that are conventionally slow for massively parallel problems such as neural networks. The alternative, in the meantime, is to build electronic architectures that *emulate* neuronal behavior with the hope that these structures will form the basis for a parallel computing architecture based on neural networks.

DSP based hardware accelerator boards are the current 'hot topic' of digital neural network designs. These ANNs rely on the DSP to perform learning algorithms in essentially a sequential manner. Neural networks are inherently parallel by nature and attribute their speed to this massive parallelism. Designing parallel architectures using DSPs is not very practical; costs of optimized signal processing chips can be horrendous. Silicon implementations of neural networks can be very cost effective in modelling massive parallelism. However, most neural network ASICs do not include the learning algorithm on-chip; they usually depend on a host computer that is typically serial.

Learning paradigms can be very slow on traditional serial computers. Performing the backpropagation learning algorithm for large networks on a serial computer is just not practical; the learning time increases tremendously with the number of neurons, the problem size, and the training set. The short-term alternative is to implement the algorithm in silicon as an integrated circuit. This will relieve the host computer of the tedious task of arithmetic calculations. If we can optimize hardware to perform this, or any other, learning paradigm, we can obtain results much faster and increase productivity.

The necessity for an ASIC that will perform a neural network paradigm is to create circuits that are direct implementations of biological neurons that will eventually be used to form a human-like brain structure; DSP accelerator boards are nothing more than enhancements to current computing power and will eventually become engulfed by advancements in computer technology. A VLSI implementation will allow the neural network researcher to optimize the algorithm being implemented.

### 1.3 Scope

We begin this thesis with a study of the background of neural networks. A brief history of neural network development is presented — including some major events that shaped the field. A typical neural network model is described and various typologies of neural networks are reviewed. We state some of the more interesting learning paradigms with a major emphasis on Backpropagation learning. We conclude the Background chapter with a thorough examination of ANN implementations.

The next chapter describes a VLSI implementation of the Backpropagation algorithm. We begin this chapter with a discussion on implementation issues regarding the design of the major components within the neural network structure. A section

on a novel VLSI design technique is presented. We also present our implementation of the algorithm in a VLSI ASIC — describing the major components within the design and how they are linked to form the network.

Finally, we present our conclusions and recommendations for further study.

Appendix A offers a mathematical derivation of the Backpropagation algorithm from its roots in the Perceptron Convergence Theory to its current generalization of the Delta Rule.

# Chapter 2

## Background

#### 2.1 Neural Networks

Neural networks can be described as an attempt to create a machine that mimics the thought processes of the human mind; a machine that can, by intuition and inference, make sense out of incomplete, confusing or fuzzy information. Neural networks exhibit characteristics of biological models of brain-like behavior. An artificial human brain? Well, maybe. But current neural network models come no where near the complexity of the human brain. Table 2.1 shows the relationship between biological processes in the brain and current digital computer architectures of neural network models. The human brain contains about 100 billion neurons, each of which connects to about 10,000 other neurons in a massively parallel structure. The brain can perform most cognitive processes in less than 500 ms even though the neuron's speed has been estimated at around only 1 ms, simply by this inherent parallelism. A human can perform simple vision tasks that thousands of super computers can't. But a simple pocket calculator can outperform a human 10-to-1 on explicit arithmetic problems. As you can see, brains and computers do not compute the same.

| ELEMENT      | BRAIN                              | NEURAL NETWORK                       |

|--------------|------------------------------------|--------------------------------------|

| Organization | Network of Neurons                 | Network of Processing Elements (PEs) |

| Architecture | $10^{11}$ neurons                  | < 100 PEs                            |

| Hardware     | Neurons                            | Switching device (transistor)        |

| Structure    | 10 <sup>4</sup> connections/neuron | < 100 connections/PE                 |

| Technology   | Biological                         | Silicon                              |

| Processing   | Analog                             | Digital or analog                    |

| Speed        | $10^{-3}  \sec$                    | $10^{-9} \sec$                       |

Table 2.1: Comparison of the Brain and Neural Network Computing [20]

Neural networks spread the problem into smaller tasks and distribute the processing to its simple parallel processors. The brain uses this parallel distributed processing to perform cognitive tasks such as natural language understanding, abstract reasoning, concept generalization, knowledge processing, pattern classification, computer vision, association and evaluation. Conventional computers are outstanding at arithmetic processing, sorting and logic; all processes that the human brain has the potential to do, but cannot do with any efficiency.

Neural networks are simple systems that are capable of complex behavior. By simplifying the processes of biological neurons, a system that reasons can be developed. This development is an indirect reaction to the failure of traditional artificial intelligence (AI) research into the laws and rules governing cognition. Decades of AI research has not resulted in substantial progress, hence the rebirth of neural networks and natural intelligence (NI).

#### 2.1.1 Chronology of Events

Modern neural network theories can be traced back to ideas first introduced in the 1940s and 1950s. In 1943, McCulloch and Pitts were developing mathematical theories on the nervous system and how neurons might work. [15] A few years later, Hebb introduced a learning rule whereby networks would reinforce response patterns that occurred most often, as though they were learning by experience. [16] This rule stated that a connecting synapse between two simultaneously active neurons should become 'stronger', while inactive neurons would cause a synapse to 'weaken'.

In the late 1950s, Rosenblatt developed networks that could learn to recognize simple patterns. [17] The perceptron, as it was called, could decide whether an input belonged to one of two classes. A single node would compute the weighted sum of binary-type inputs, subtract a threshold, and pass the result through a non-linear hard limiting threshold that classified the input. The perceptron formed a two decision region separated by a hyperplane. The Perceptron Convergence Theory was developed by Rosenblatt as a means for adjusting the weighted connections until a stable state was reached. Rosenblatt proved that if the inputs form two separable classes, then the output of the network will converge to one of these two classes. At around the same time, Widrow and Hoff were developing a theory to reduce the error between the actual output and the desired output of a perceptron-like network, in a least mean squared (LMS) sense. [18] The LMS algorithm is similar to the Perceptron Convergence Theory except for the fact that Widrow and Hoff's LMS algorithm uses a threshold-logic nonlinearity for the transfer function, so that more than two classes of output are formed. These two theories have formed the basis for most learning

Figure 2.1: Difficult Perceptron Convergence Task [1]

algorithms to date. Recently, though, modifications to the Hebbian rule have been successful in the formation of other new learning algorithms.

In what mainstream connectionists might call a catastrophic event, Minsky and Papert 'slashed' the Perceptron Convergence Theory in their book on perceptrons [1]. In fact, though, Minsky and Papert showed that only a 'small' class of perceptrons could not perform certain tasks in pattern recognition. It turns out that some of the tasks the perceptrons could not perform are also extremely difficult for human vision—like discerning which "one of the two spirals [on the cover of their book] is made with a single line...[and which] is actually two lines nested within each other," (shown in Figure 2.1)<sup>1</sup> [56]. Nevertheless, the 1960s and 1970s proved fatal for neural networks. While traditional AI theories of symbolic processing flourished, NI theories vanished into relative obscurity. True connectionists, however, were not discouraged. Pioneers in the field, such as Grossberg and Kohonen, were producing networks and ideas throughout the 1970s [19].

<sup>&</sup>lt;sup>1</sup>It is easy for one to trace the lines by hand, but there are no visionary clues that tell us that the spiral on the right is a fully-connected single line.

In 1982, Hopfield discussed the application of analog non-linear interactions in neural networks and introduced ideas on electronic circuits for these networks [81]. It wasn't until 1986, when Rumelhart and McClelland introduced the concept of Parallel Distributed Processing (PDP) [2, 3], that neural networks regained their popularity. The PDP group of researchers introduced models based on nodes and connections, and the laws that changed the activities in them. The current flood of activity in neural networks is in relation to the concepts of subnetworks and connections analogous to the nature of brain parts. Engineers are currently learning and applying connectionist principles in the design of specific implementations of these subnetworks.

We have presented what we feel are the most influential events of the past five decades. Who knows what the next five decades might bring?

#### 2.1.2 Model of a Neuron

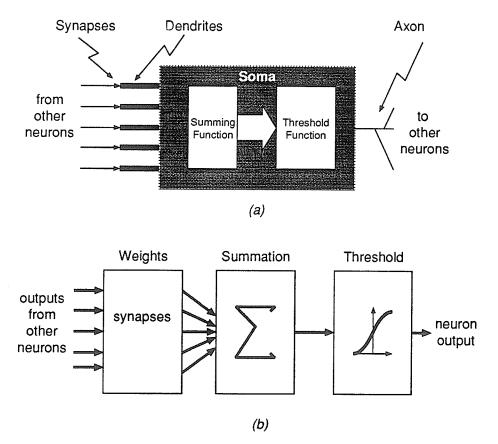

It is important to understand how a biological neuron works in the human brain before attempting to design neural network models. Figure 2.2(a) is a simplified model of the structure of a neuron in the human brain. Basically, the neuron consists of a cell body (soma) whose physical shape seems to partially determine the function that it will perform in the brain. A complex set of interconnections add to this determination. The neuron's input connections (dendrites) accept electrical signals, that are either excitatory (positive) or inhibitory (negative), from other neurons' output connections (axons) through links, called synapses, that modify the axon's potential. It is theorized that the neuron performs a weighted sum of input signals and emits an output signal proportional to some threshold function. Recently, it has been suggested that computation also takes place outside the soma [20].

Figure 2.2: Simplified Neuron Models [20]: (a) biological (b) artificial

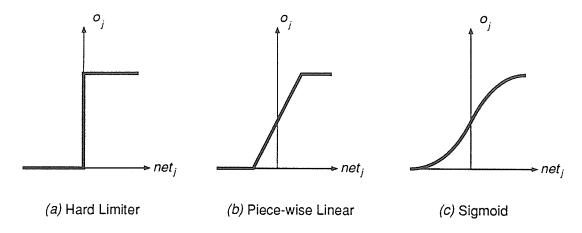

Figure 2.3: Typical Activation Functions

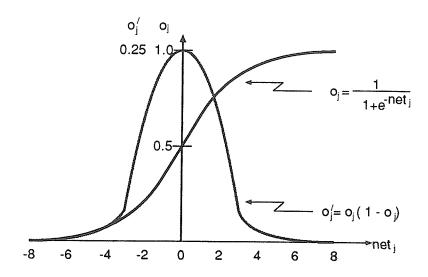

An artificial neuron, or processing element, is shown in Figure 2.2(b). The simplified model consists of weighted input connections (analogous to synapses and dendrites), the summation and activation units (the soma), and the output connection (the axon). The input signals, usually positive, can become either excitatory or inhibitory, by using bipolar weights. The model performs a weighted summation of its inputs, passes this summation through a transfer function (the threshold) and produces an output activation that is sent to other neurons in a network. The transfer function defines the output state of a neuron. Typical transfer functions, of which the sigmoid is the most popular, are shown in Figure 2.3. In this simplified model of an artificial neuron, most of the biology is omitted. Models of neural networks are usually characterized by the topology of the network and its learning rules.

In the next few sections we will show some basic neural network topologies and state some important learning rules.

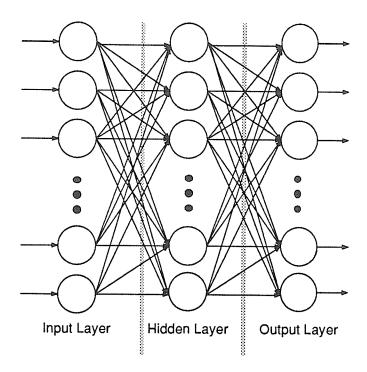

Figure 2.4: Multi-layer Feedforward Network

### 2.1.3 Topologies

Neural network behavior is usually characterized by the way in which neurons are interconnected. There are two major classes of neural network topologies.

The feedforward network usually consists of layers of neurons that are connected such that neurons in one layer can only connect to other neurons in a higher layer (connections to lower layers are forbidden). This type of network, usually called a multi-layer feedforward network, is shown in Figure 2.4. Input signals propagate forward through the network until they reach the output layer. Layers that are neither input nor output are referred to as hidden layers because they contain abstract representations of user-defined input/output values.

Figure 2.5: Single-layer Feedback Network (Hopfield)

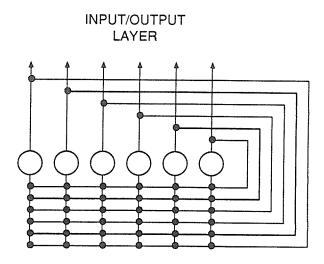

The second class of topologies is the feedback network. Feedback networks can take many forms, such as a multi-layer feedforward network with the output layer connected to the input (sometimes called sequential networks) or neurons connected to each other on the same layer (usually called lateral inhibition or comparative networks). However, the most basic form of a feedback network (and one of the most useful) is the *Hopfield* neural network, shown in **Figure 2.5**.

The Hopfield network is used mainly as an associative memory, and is referred to as self-organizing. In this topology, all neurons are connected to each other in a grid-like structure and the layer of neurons functions as both an input and an output. It is interesting to note that although feedback networks are typically used for associative memories, there is no reason that a feedforward network could not also be used. In fact, it can be shown mathematically that a feedback network has an equivalent feedforward network that can perform an identical task [21].

A typical neural network model has been summarized in [2, 3]. The model includes

processing units, states of activation, an output function, a network pattern of connectivity (topology), propagation rules for propagating patterns of activity through the network, activation rules for combining inputs and current state to create new activities, a learning rule for modification of connection strengths between units, and an environment in which the neural network can operate.

A neural network in its most general form looks like any other parallel processing architecture. In fact, the neural network model consists of processing elements (neurons), connections between processors (synapses) and information that passes passing along these connections. Just as a parallel processing architecture is defined by the topology of its interconnections, so too is the neural model.

### 2.2 Learning Paradigms

Without a program of instructions, a computer is a 'useless' machine. The program usually instructs the computer to perform specific tasks on a set of input data to create some sort of output. Therefore, the program is an essential part in a computer environment. We have seen how a typical neural network is constructed. If these types of networks are to be useful, we must be able to *program* them as well. Neural networks are not programmed in the conventional sense (it would be virtually impossible), they are *taught*.

Teaching a neural network cognitive knowledge is basically a modification of the synaptic weights according to some learning algorithm or rule. Therefore, we often say that the 'knowledge of a neural network is in the weights'. The analogy to human behavior modification is no coincidence, as neural networks try to mimic the human

thought process. Learning rules are usually called paradigms, which simply means "an outstanding, clear and typical example, model or prototype" [22]. Learning paradigms are generally associated with a particular neural network structure. Just as there are many neural network topologies, there are equally as many learning paradigms. This section does not attempt to cover the myriad of approaches to teaching neural networks; rather, it is intended to introduce a few of the more interesting and popular learning paradigms, and to state the Backpropagation of Error learning paradigm or Generalized Delta Rule. Refer to Appendix A for a mathematical derivation of this learning paradigm.

Learning paradigms can be broken down into three classes [23]: (1) supervised learning, where a teacher provides an input and output training pair of vectors to the network; (2) reinforcement learning, which requires a single scalar evaluation of the output; and, (3) unsupervised learning, where only an input vector is supplied. Within each of these classes, learning takes place by modifying the synaptic weights after some type of error measure is performed.

In the case of supervised learning, an a priori knowledge of input/output responses is necessary (for example, the XOR logic problem), and the error between the actual response and the target response is used to correct the network. Reinforcement learning utilizes a global reward strategy whereby credit is assigned to a local decision by measuring the correlation between it and the global reinforcement signal (an example could be the 'Hot & Cold game' where someone is guided by 'hot' and 'cold' verbal signals). Unsupervised learning requires only that an input signal be presented to the network. After a set of trials are presented, a grade or performance measure is taken at the output and a score that tells how well the network is doing is created. Within

each class there are various learning procedures (sub-classes) that are distinguished only by how they treat the error signal; as usual, there are some exceptions. Learning in a neural network occurs as the weights are changed to reduce the errors — in effect, the network gains experience [21]. The learning procedure is usually stopped after a set of training patterns are successfully learned by the network. The final pattern of synaptic weights represents the knowledge of the system and is generally fixed after training.<sup>2</sup>

Unsupervised learning discovers the underlying structure of variables and associates a correct response. A popular unsupervised learning procedure is the Kohonen self-organizing feature maps, as described in [24]. A two-dimensional array of output units approximates the probability density function of a set of input vectors. The output units form an ordered set of clusters of vector centers that sample the input space. The units compete in a modified winner-takes-all manner, such that the unit whose weight vector generates the largest dot-product with the input vector wins.

Competitive learning is also an unsupervised learning procedure. A set of hidden units compete with each other to become active, such that disjoint clusters of similar input vectors are formed [23]. As input vectors are presented, the hidden unit with the greatest total input wins and turns 'on' fully, while all other units turn 'off'. It then increases its weight vector by a small fraction so that in future trials it will continually win the competition for the same input vector. Constraints are placed on weight vectors such that the sum of its components are kept constant so that the same unit can't keep winning. Competitive learning can be modified to perform Kohonen

<sup>&</sup>lt;sup>2</sup>There are times when a certain task requires continuous adaptation of the network, such as a system that changes with time.

feature maps simply by updating the weights of neighboring clusters.

Another unsupervised learning procedure based on competitive learning is called the Adaptive Resonance Theory (ART). This theory, developed by Grossberg and Carpenter [25], is a complex set of training rules for a feedback network; training a feedback network is difficult because adjusting weights affects signals in both the forward and backward paths. ART networks self-organize to stable recognition codes in response to inputs of arbitrary sequences. Suffice it to say that ART uses a complex modification of the competitive learning model; the technical details are beyond the scope of this section.

Modifications to the Hebbian learning rule are resulting in new learning paradigms that are becoming quite popular. Hebbian learning can be described as 'learning by experience' whereby neighboring units strengthen or weaken connections between themselves. The basic equation in this type of learning is  $\Delta w_{ij} = \eta o_i o_j$ , where  $o_i$  and  $o_j$  are the outputs of the  $i^{th}$  and  $j^{th}$  units, respectively,  $\Delta w_{ij}$  is the connection strength between these two units, and  $\eta$  is the learning rate.

A Linsker network [26] is a self-organizing, unsupervised learning paradigm that uses modified Hebbian learning in a linear layered network. This type of learning maximizes the variance at **each** unit's output such that maximum information is preserved at a layer of units, subject to certain constraints.

By combining both Kohonen's and Grossberg's learning rules, Hecht-Nielsen has come up with what he calls *Counterpropagation* [27]. It is not a learning rule in the strict sense, but rather it is a self-organizing network of combined rules. The network functions as a statistically optimal self-programming lookup table.

Reinforcement learning procedures are not as common as (un)supervised learning procedures; we are, therefore, only considering one type of reinforcement procedure here. The Associative Reward-Penalty  $(A_{R-P})$  is an attempt to map automaton theory onto connectionist networks. Each stochastic unit (see Boltzmann below) is treated as an automaton and the state each unit adopts is treated as the automaton's action. If linearly independent input vectors are presented, and the network contains only one unit,  $A_{R-P}$  finds the optimal weight values. A network of these units will develop useful state representations [23].

Supervised learning requires that a teacher present a set of training examples such that the network can learn to recall these examples and make inferences about incomplete or unanticipated examples. A Boltzmann learning procedure, which uses a generalized Hopfield network, utilizes a stochastic decision rule to update the states of units. A probability distribution is 'learned' by adjusting the weights between units. Each unit has an associated probability that it will be in one of two states. Repeated applications of this rule to each unit will cause the network to reach 'thermal equilibrium'. At this point, the probability of a global state is constant and follows a Boltzmann distribution. The network first receives an input/output training pair and simulated annealing (a gradual change from one state to another to reach a global minimum) is used to reach equilibrium. Weights are incremented by Hebbian learning at this stage. This is repeated for the entire training set. A second phase is run with no output values and is again annealed to equilibrium. This time, however, weights are decremented by Hebbian learning (a form of unlearning). Learning halts when the probability distributions of the two phases are the same. A special case of Boltzmann learning, used in an unsupervised capacity, is when no input units are used. The

network learns to model a probability distribution that is specified in the output units. The advantage with this type of network is that it will perform completion of a partial vector that is clamped at the output. Learning in a Boltzmann machine is very slow since reaching thermal equilibrium by simulated annealing is a time-consuming process. An approximation to the Boltzmann statistics, by estimating the network's mean behavior, is a solution. Mean Field Theory (from Physics) replaces each unit's binary state by a deterministic real-value that represents its expected value. Deterministic relaxation is used in place of simulated annealing, to obtain a representation of the equilibrium distribution [23].

We have been necessarily brief in our discussion of learning procedures thus far. Much of the mathematics have been omitted in favor of presenting conceptual ideas. We will now discuss, in more detail, the Generalized Delta Rule or Backpropagation Learning Rule.<sup>3</sup> Refer to **Appendix A** for a complete derivation of this Backpropagation Learning Algorithm. This supervised learning paradigm is, by far, the most common in its class. Backpropagation is the workhorse of all neural network learning paradigms. Backpropagation seems to be the best general-purpose model for generalization in a feedforward network that uses the Generalized Delta Rule [21].

The history of backpropagation is quite amazing. Although McClelland and Rumelhart et al. [2, 3, 85] have been credited with the inception of the backpropagation learning rule in 1986, they cited Parker's work on learning logic [28] from 1985. Later, Parker discovered the 1974 work of Werbos on regression analysis [29]. It turns out that backpropagation is a special case of traditional statistical regression

<sup>&</sup>lt;sup>3</sup>The Generalized Delta Rule is a generalization of the Delta Rule which happens to be similar to the Least-Mean Square (LMS) Learning Rule [18]. Backpropagation seems to be a term coined by the PDP Group [2, 3]. Nevertheless, the two terms are used interchangeably.

techniques [30]. In 1988, LeCun [31] discovered the 1969 work of Bryson and Ho on applied optimal control [32], where similar techniques to backpropagation were apparently introduced. Who knows, "even earlier incarnations may yet emerge." [33]. Nevertheless, McClelland and Rumelhart can be credited with introducing backpropagation into a *usable* form for neural network learning.

Backpropagation learning requires the propagation of error deltas (differences between target and actual output values) backwards through the network. The application of the backpropagation learning rule to neural networks thus forms an apparent paradox. Real neurons cannot run backwards (evidence suggests this), so this learning rule is not biologically plausible. Also, backpropagation learning is generally used by feedforward neural networks—the ultimate contradiction. However, it is only the error signals that are propagated backwards through the network during learning; and those signals propagate down the same connections (synapses) as the forward mode.

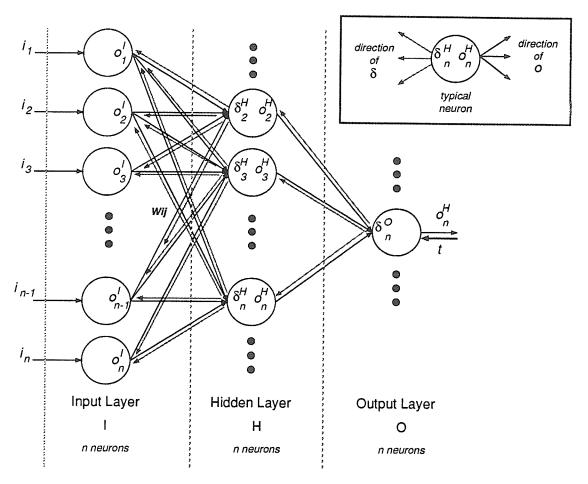

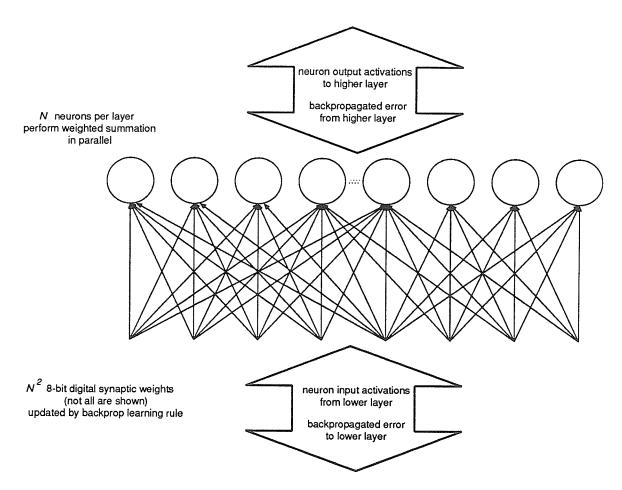

The three-layer feedforward network of Figure 2.6 shows an overview of the backpropagation learning rule. The rule is, however, generalized to operate on any multi-layer network. We will assume the convention that  $o_j$  refers to the output of the  $j^{th}$  neuron and  $w_{ij}$  refers to the connection strength from the  $i^{th}$  to the  $j^{th}$  neuron [a superscript in the equation indicates the associated layer: I (input), H (hidden) and O (output)]. A set of training patterns is presented to the network one at a time. The input vector propagates through the network to form the normal sum of products,  $net_j = \sum_i w_{ij} o_i$ , where  $net_j$  represents the total input to neuron j. The output of neuron j is a function of its total input,  $o_j = f(net_j)$ . This function must be non-linear with a bounded derivative. The most useful transfer function is the sigmoid,

Figure 2.6: Overview of Backpropagation Learning Applied to a 3-layer Network

Figure 2.7: Sigmoid Function (and derivative)

$o_j = \frac{1}{(1+e^{-net_j})}$ , shown in **Figure 2.7**, along with its derivative. The derivative of the sigmoid function is simply  $f'(net_j) = o_j(1-o_j)$ .

The goal of the backpropagation learning algorithm is to reduce the total error,  $E = \frac{1}{2} \sum_{p} \sum_{j} (t_{pj} - o_{pj})^2$ , by adjusting the weights  $w_{ij}$ ; where  $t_{pj}$  represents the target value of the  $j^{th}$  neuron with respect to training pattern p. Usually E is estimated by taking the error after each pattern and is averaged over the entire set of patterns. Presentation of an entire set of training patterns is called an epoch. Error derivatives are propagated back through the network from the output layer. An error vector is created at the output layer by taking the difference between the actual and target output vectors,  $\frac{\partial E}{\partial o_j} = (t_j - o_j)$ , where  $t_j$  represents the target value for the  $j^{th}$  neuron. Thus, the error delta of an output neuron is specified as  $\delta_j^O = \frac{\partial E}{\partial o_j} f'(net_j) = (t_j - o_j)o_j(1-o_j)$ . The error delta traverses the network in reverse through the synapses to lower layers. We recursively define the error delta of a hidden layer neuron to be  $\delta_i^H = f'(net_i) \sum_j \delta_j^O w_{ij}$ . This definition can be used for any number of hidden layers in

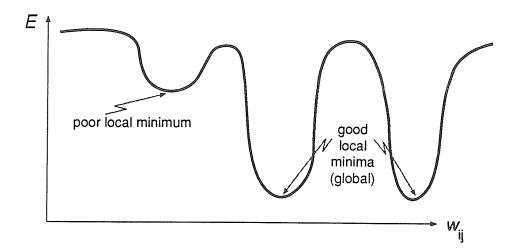

Figure 2.8: Error Surface with Local Minima

a multi-layer network. Learning is accomplished by modifying the weights according to  $\Delta w_{ij} = \eta \delta_j o_i$ , in the direction to decrease E. The process is repeated for the next training pattern and so on. After a number of epochs, a performance measure is taken and training halts when the error is no longer significant; i.e. when the patterns can be recalled adequately. The backpropagation rule is performing a gradient-descent heuristic as it tries to minimize the error function. As long as the training vectors are appropriate for a solution to exist, backpropagation will always find a set of weights that will minimize the error function, E. If the network has hidden layers, however, this might not always be a global minimum. Gradient-descent follows the negative slope of the error derivative. The error surface may contain many local minima; a 2-dimensional cross-section of an error surface is shown in Figure 2.8. If the set of weights finds one of the local minima, it does not mean that the solution is wrong — there could be many solutions to a single problem and the algorithm has just found one of them. Backpropagation learning rarely encounters poor local minima, provided there are more neurons and synapses than the problem requires.

Generally, the most serious problem with the backpropagation learning algorithm is that it takes many epochs, sometimes thousands, to converge. But backpropagation is great at training a neural network to generalize, therefore, much research has been directed into backpropagation speedup techniques. Since the conventional means of executing the backpropagation paradigm has been on sequential computers, the obvious way to speed up learning is to distribute the processing of each neuron (or even each connection) on a separate processing element. It has been shown [23] that the learning time for the backpropagation algorithm is approximately  $O(N^3)$  where N is the number of weights in the network. A parallel distributed processing structure of weights would decrease the learning to approximately  $O(N^2)$ . The improvements will be significant for networks with a small amount of neurons, but not for larger networks. Alternately, we could implement a dedicated array of hardware neurons and synapses that would execute the learning algorithm directly.

By including a term as suggested in [2, 3], such that  $\Delta w_{ij}(n+1) = \eta \delta_j o_i + \alpha \Delta w_{ij}(n)$  (where n indexes the presentation number and  $\alpha$  is a constant), 'momentum' is built up as the weight changes step along short regions of constant gradient in the error surface. This acceleration is cancelled-out as the error derivative increases.

Gradient-descent methods (first derivatives) only give the derivative of the error surface at a point. Knowing the curvature of the surface at that point gives us a better sense of direction. The second derivative  $(\frac{\partial^2 E}{\partial w^2})$  would give us an estimate of the curvature and with this we may estimate the cost of removing some connections [34].

Some training vectors can pull the weights in opposite directions at each cycle thereby cancelling weight updates. In this case, we may speed convergence by constraining weight changes such that new vectors only minimally degrade the response of a previous vector [35]. Alternately, we may preprocess the training data to remove any correlation in the input vectors, i.e. orthogonalize the inputs.

Backpropagation learning specifies that a weight update is proportional to the forward propagated output and the backpropagated error, i.e.  $\Delta w_{ij} = \eta \delta_j o_i$ . But in hidden layers, the modification of weights to lower layers will cause an error in the actual neuron output,  $o_i$ . If we use the expected value of the output, we get a more accurate weight update given by  $\Delta w_{ij} = \eta \delta_j (o_i + \delta_i)$  [36].

As you can see, there is no shortage of ways to improve the backpropagation learning paradigm; however, each of the ideas suggested here are limited with respect to the class of problems that they improve performance on.

#### 2.3 Artificial Neural Networks

There are currently many neural network hardware designs that use traditional electronic circuit components and the more technologically advanced use of VLSI design. Most of these designs simply implement a specific neural network architecture with no real power to execute the learning paradigm that they were destined for. In these circuits, the designer has opted for an *easier* approach to neural network systems, and has allowed a computer to do off-line processing of the data.

Designing a circuit for VLSI implementation requires many decisions that are not necessary in discrete component circuit design. The critical issues are area constraints, speed, and processing technology. Some minor issues are CAD tools and standard cell libraries.

The use of analog processing components in VLSI, in respect to neural networks, has many advantages and disadvantages. A fully analog neural network can closely model the biological processes that are taking place [37] and can exhibit tremendous speed and capabilities in area efficient designs. However, analog VLSI suffers from some major problems. Analog integrated circuits suffer from what can be termed 'processing imperfections', which are due to manufacturing variations. These imperfections can manifest themselves into poor quality integrated circuits with unmatched characteristics not only from different processing runs on completely different pieces of silicon, but all the way down to separate circuits on the same wafer or even individual devices in the same circuit. It is true that large companies with huge budgets can afford to pay for higher accuracy in processing technology and can command special fabrication techniques, but the average researcher does not have access to, or the guarantee of, these kinds of facilities.

Most analog neural networks utilize storage capacitors (analog memories) to implement synaptic weight connections. Recent designs, like [38], that rely on capacitors for weight storage also use the leakage current to emulate the synaptic weight change in training and therefore require highly accurate devices. Similar analog networks, such as [39] and [40], also use capacitors for synaptic weights and require constant refreshing of voltage levels unless the chips are cooled to ridiculous temperatures like that of liquid nitrogen (77K) — even then the storage would only last a few days. Using capacitors is only one possibility for weight storage in analog neural networks. The use of custom programmable resistor chips [41] for the analog synaptic weights can also suffer from variations in device physics. Many other designs are using EEPROM technology [42] with much success; in fact, INTEL Corp. has just

released an analog IC that uses EEPROMs for synapses. In all analog networks the devices must operate in the subthreshold region of the device transfer characteristics and, therefore, with limited supply voltage ranges in certain technologies, the available levels for weight values can diminish to the equivalent of 4-bit digital resolution (i.e. 16 levels) [43]. There are many other analog implementations of neural network paradigms along with hybrid designs that use the accuracy of digital storage with the speed and efficiency of analog arithmetic [44] as well as pulse-stream arithmetic processing [45, 46]; but these usually require fast, accurate, and area-consuming digital-to-analog and analog-to-digital converters.

On the other hand, digital electronics in VLSI is a mature technology that offers high accuracy (more precision), better reliability in functionality, noise immunity, and is easily manufactured. There are many realizations of digital weight storage, including RAM, ROM, EPROM and EEPROM, and shift register/latches. However, digital designs require significant silicon area to implement arithmetic processes, especially in fully parallel designs. Also, the speed with which these processes can be executed can be many orders of magnitude greater than similar analog implementations. Since almost every neural model contains neurons that compute weighted sums, it is advantageous to select an architecture that will reduce the area-time metric to a reasonable level. Ultimately, the architecture chosen will reflect a suitable solution to this metric. There are no shortages of possible digital architectures for neural network paradigm implementations. We will now concentrate mainly on digital VLSI neural network research architectures as reported in the literature. Some interesting digital systems will be mentioned for completeness; however, these architectures are well beyond the scope of this thesis. We also examine some current commercial digital neural network

integrated circuit chips because they contain some interesting architectural ideas.

Digital systems for Artificial Neural Networks (ANNs)<sup>4</sup> can be broken into three broad categories [20, 47]: (1) General-Purpose Parallel Computers for Neural Network Simulations; (2) Special Purpose Processors for Neural Network Simulations (Neurocomputers); and, (3) Dedicated Digital ANN VLSI Circuits. All three categories present some interesting and valid ideas; however, we have set out to design a digital VLSI ASIC, and comparison to current VLSI research is a must. The general-purpose and special-purpose structures can be hierarchically analyzed to gain insight as to their inherent structure, and possibly present us with some ideas for our own design.

General-purpose parallel computers consist of programmable processor arrays for simulating a wide range of neural network paradigms in a framework that is analogous to conventional computers. The parallel processing computers optimize the neural processing by distributing the problem to a large number of simple processors. These types of architectures, although very flexible, can be very difficult to efficiently program and partition a neural network paradigm onto the parallel processors. The consummate pioneer of general-purpose parallel computers is the Connection Machine (CM) [48]. With its simple processing elements (PEs) and local memory, thousands of independent PEs operate concurrently on different segments of the same problem. The architectural concepts for the CM originally came from the connectionist theories, but the CM was destined as a general purpose alternative computing

<sup>&</sup>lt;sup>4</sup>We tend to use the phrases "artificial neural network" and "neural network" interchangeably throughout this thesis even though an *artificial network* implies a man-made electronic architecture and *neural network* implies the biological representation of same. Suffice it to say that the context these terms are used in will make the representation clear.

structure to traditional serial Von Neumann-style architectures. The CM requires a specially designed programming language to distribute the processing power. A relatively similar architecture to the CM, the AAP-2, described in [49], is a massively parallel cellular array processor based on VLSI technology. It contains 65,536 one-bit processors that, like the CM, offer high-speed data processing in a Single Instruction Multiple-Data path (SIMD) architecture. A somewhat different approach to massive parallelism in a general parallel processor can be found in the Warp Machine [50, 51]. Warp's architecture incorporates a systolic array of 10 processing cells. Each cell consists of an adder, multiplier, and ALU, and communicates with its immediate neighbors only. A programming language was also developed to partition the problems that the Warp Machine was to simulate. The NCUBE microprocessor-based supercomputer [52] is also a massively parallel computer with processors configured in a 10-dimensional hypercube; the CM uses a 16-dimensional hypercube. Both the NCUBE and the CM contain the same architecture; however, the NCUBE processes data in a Multiple-Instruction Multiple-Data (MIMD) fashion. There are many other general-purpose parallel computing architectures [20]; we have only mentioned a few for the sake of completeness and because of their inherent similarity to basic neural network structures. These machines are all characterized by a large number of simple processors that are connected in various topologies in a massively parallel fashion.

Architectures such as these are well beyond the scope of this thesis but are worth discussing because the basic concepts used in performing massive parallelism are relevant to any neural network structure. However, these structures suffer from the

$<sup>^5</sup>$ An n-dimensional hypercube connects a single processor to n of its neighbors and has the advantage that the links of the hypercube provide almost the same communication capabilities as a fully connected network that forms a complete graph.

difficulty required in scheduling processors for the high interconnection needs of neural networks. In our opinion, these hardware specific programming languages are an essential and critical part of general purpose parallel computers and unless a design can develop an optimum data partitioning scheme for multiple paradigms, these computers will not be a major neural network hardware influence.

In contrast to general-purpose parallel computers, we present the special-purpose processors designed especially for neural network simulations. These neurocomputers usually consist of special hardware boards optimized to perform neural network paradigms that interface to traditional sequential computers. The hardware involved can range from simple modular processing elements to Digital Signal Processors (DSPs) integrated into serial or parallel structures either dedicated to executing specific paradigms or, more commonly, generally programmable to execute multiple paradigms. There is a vast array of both commercial and research projects that can offer tremendous speed increases for neural network simulation; but these boards are mainly DSP boards optimized to perform the weighted summations inherent in most neural network paradigms. Most of these coprocessor boards are designed to interface to IBM-PCs or Sun workstations through the VMEbus. Also, most of the boards discussed here use industry standard microprocessors such as the MC68020 (Motorola), or DSPs like TMS32020 (Texas Instruments). The virtual processing elements and interconnections established during run-time to implement a paradigm require huge amounts of memory, and the usual multiplexing of processors takes away the processing power inherent in the parallel structure of neural networks. The systems that offer some novel structures or that stray from the norm will be presented in more detail; however, we will mention many systems for the readers who are interested in

simulations of neural network paradigms because some of these are readily available, easily attainable, most adaptable, and highly affordable.

Some commercially available neurocomputers are systems by Hecht-Nielsen Neurocomputers (HNC), Science Applications International Corporation (SAIC), and TRW-to name a few. The Anza Plus/DP from HNC [53] is a neurocomputing co-processor board available for the IBM-PC or Sun. The architecture is based on a 4-stage pipelined Harvard architecture employing separate data and instruction paths. ANZA uses a specialized floating point DSP to achieve speeds of 3 Million interconnections Per Second (MiPS)<sup>6</sup> during training and approaching 12.5 MiPS peak performance with 64 bit accuracy. Software is also available to be used in conjunction with the board to provide a user interface to the extensive set of neural network paradigms that HNC provides. SAIC has developed a set of neural network processing boards, Delta Floating Point Processor, described in [54, 55], that use fast static column mode memory and an ECL (Emitter Coupled Logic) floating-point processor chip (from BIT) that implements a Reduced Instruction Set Computer (RISC) architecture. The Delta also uses a multi-stage pipelined Harvard architecture that claims simulation speeds upwards of 3 MiPS during learning and 11 MiPS without learning. A third commercial neural processor board has been designed by TRW and is called the Mark IV neurocomputer [47]. TRW designers used a Motorola 68020 microprocessor and 68881 floating-point co-processor configured such that virtual PEs are 'swapped in' in the neural processing phase—much the same as the concept of physical memory in virtual memory computers. Large neural networks with many interconnections and speeds approaching 5 MiPS are obtained by this architecture.

<sup>&</sup>lt;sup>6</sup>Not to be confused with Million Instructions Per Second (MIPS).

It is interesting to note that these architectures all use a single, fast special processor with no true parallel processing power.

We now turn our attention to systems developed for research purposes. One of the most interesting and daring projects is Netsim by Garth [57]. The system was designed to accelerate learning in neural network paradigms by using a small instruction set, pipelined operations and large amounts of memory. The computational speed is gained by the use of two custom-designed, specialized co-processors. A communication coprocessor handles all interfacing of Netsim 'cards' into a nearest neighbor set, while the 'solution engine' (basically a vector coprocessor or an optimized DSP) performs mathematical computations optimized to neural network requirements. The network of cards which form a neurocomputer require a host computer acting as a system controller. This system exhibits speeds of nearly 90 MiPS during learning.

Another parallel neurocomputer is described in [58]. A parallel array of processing elements simulate a column of neurons in a multi-layer neural network. Each processor contains a TMS32030 DSP, memory and control. The processors are configured in a 1-dimensional systolic ring architecture that executes vector-matrix multiplication in a SIMD fashion. Again, this system connects to a host computer, such as Sun, via VMEbus, and obtains speeds in excess of 500 MiPS.

A neurocomputer along the lines of Netsim has been developed by Pacheco et al. [59], in which a custom coprocessing element has been designed to ultimately form a parallel MIMD computing structure. The coprocessor is designed under the RISC architecture and is basically a microprocessor (ALU, registers and memory).

In a more abstract design philosophy, the principle of communicating concurrent

processors has been developed into a neurocomputing architecture of multiprocessors by Kraft and Frostrom [60]. The idea here is that processing resources are shared between processing elements, through something called *actors*, with distributed communication. The system acts analogous to a post office in that interprocessor communication guarantees nothing other than *mail delivery*; timing and order of processing is not guaranteed.

The systems developed thus far, are all attempts to increase neural network simulation processing speed by implementing current technology as a traditional co-processor or by custom designs of optimized DSPs configured as neural network systems. We have presented only a few such systems, but more can be found in the literature [20, 47].

A wide and diverse range of digital VLSI neural network ASICs have been developed — from simple logic gates to wafer-scale integration. The main goal in all implementations is to form a massively parallel set of basic electronic neurons and synapses (the biological representations) in a highly efficient structure and place as many of these elements on the silicon as is physically possible. There are no shortages of design strategies in digital neural processing as designers strive to develop the 'microprocessor of neurocomputing'. Although most of these designs have no facility for on-chip learning (all learning is usually done off-line by a host computer), these designs show innovative architectures using state-of-the-art technology in an approach that can rival the speed and cost of analog devices. In reviewing these architectures, we hope to gain knowledge that we can build on and apply to our own design.

The architecture of a neurocomputer microprocessor is described in [61]. The

chip consists of a number of simple processor nodes (similar to DSPs) connected in an SIMD configuration. Each node is a simple arithmetic processor that performs vector-matrix multiplications. Multiple nodes form connection layers that emulate a neural structure. The communication between nodes is via "broadcast" structures to cut down on interconnection area. The processor nodes are 16-bit two's complement multipliers with associated registers, logic-shifters, memory for weights, and an adder.

A general purpose digital architecture for neural networks has been developed by Duranton and Mauduit [62]. The "neuromimetic chip" is a fully parallel design wherein multiplications are serialized by replacing multipliers by AND gates and accumulating the results to form a weighted summation. The designers intended for this chip to be used in a Transputer array for general purpose network simulations.

Hirai et al. [63] designed a digital neuro-chip for large scale neural networks. The chip contains six neurons and 84 synapses with 64 levels of modifiable weight. The designers opted to use impulse density encoding of digital data to obtain signals with the *flavor* of analog (continuous) values.

This encoding scheme is similar to the "pulse stream" arithmetic described by Murray et al. [5, 6, 45]. In this scheme, neural activities are represented by a stream of digital pulses (similar to natural neurons) on excitatory and inhibitory data lines. The data is decoded by using "chopping clocks" that basically integrate the signal to form smooth activation potentials similar to a "ring oscillator".

Murray et al. also describe another architecture for neural networks involving bitserial arithmetic. The bit-serial design involves simple processors communicating with each other via single-bit data lines. This structure exhibits computational efficiency as well as tightly pipelined arithmetic processing. A simplified 5-state activation function allows shifting and adding in place of the silicon-hogging multipliers. Bitserial addition can be utilized to create highly efficient pipelined multipliers. This type of arithmetic processing is desirable in neural network structures of massively parallel processors, since the data is communicated between processors on a single-bit data bus. We will expand more on bit-serial architectures in the development of our own neural network design.

Along the lines of impulse density, there are many VLSI neural network designs that employ stochastic processing. This type of processing involves the use of statistical data structures using probabilities. Basically, the circuits represent digital values as analog probabilities of pulse densities — the number of pulses in a particular time interval. These designs differ in the way in which the probabilities of pulses are summed together to form the mathematical computations of neural processing. All stochastic processing requires the use of random numbers to generate these probabilities and would benefit greatly from the use of pseudo-random number generators such as Hybrid Cellular Automata (HCA); although none use HCAs (all pseudo-random number generation in stochastic processing is currently done by computer). Van den Bout and Miller, along with other colleagues, have developed many stochastic implementations [64, 65, 66, 67, 68], which all use the same basic technology. Synaptic weight shift registers cycle through their values which are compared to a random number to create a stochastic pulse stream with a probability of being 'on' proportional to the digital weight stored. Multiplication is simply performed by AND-ing this stochastic pulse stream with a stream representing the neuron activation, and summation is done by digital counters. Off-line computers are utilized for

neural transfer function processing. Various stages of pipelining are introduced to create bit-level processing.

A very unique approach to stochastic processing has been implemented by Tomlinson et al. of Neural Semiconductor, Inc., and a proprietary architecture is described in [69]. Tomlinson has analyzed the stochastic structure and found that a simple ORing of excitatory and inhibitory pulse trains can simultaneously provide the weighted summation and the non-linear activation function required by some neural network paradigms. The system offers a very high density of digital neurons and synapses with an analog-type performance. However, probabilities that are statistically independent are required for all types of stochastic processing; therefore, good random number generators are required, with long iteration cycles and these systems can be very slow. Another proprietary design of a digital neural network is the neural bit-slice computing element developed by Micro Devices [71]. This bit-slice design utilizes serial adders and multipliers in a highly multiplexed configuration.

A set of digital neuron-type circuit elements has been developed by Habib and Akel [70] that are based on simple logic gates. A neuron-type processor is constructed by cascading a 'cell body', an 'axon base' and an 'axon circuit'. Each of these elements are constructed from simple AND or OR logic gates. Processing is done by spatial and temporal processing of pulsed data values.

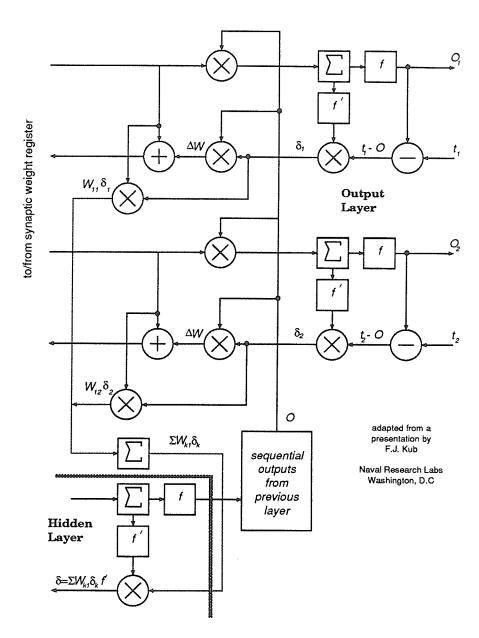

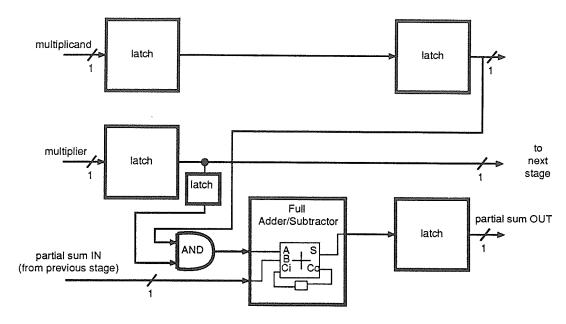

Another simple VLSI structure is a connectionist architecture designed by Cleary [72]. This design uses single-bit data and heavy multiplexing to obtain 1000 input lines (synapses) distributed over 100 output lines (neurons). A host computer cycles the massive array of single-bit weight shift registers (which take up the bulk of the chip)