# A Locally Synchronous Globally Asynchronous Vertex–8 Processing Element for Image Reconstruction on a Mesh

by

Jeffrey W. Fitchett

A thesis

presented to the University of Manitoba

in partial fulfillment of the

requirements for the degree of

**Master of Science**

Department of Electrical and Computer Engineering University of Manitoba Winnipeg, Manitoba

Jeffrey W. Fitchett, July 1993

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive la Bibliothèque permettant à nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à disposition la personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-86005-7

Canada'

## Name <u>Frocessing Element for Image Reconstruction</u> on a Mesh." Dissertation Abstracts International is arranged by broad, general subject categories. Please select the one subject which most

nearly describes the content of your dissertation. Enter the corresponding four-digit code in the spaces provided.

## Electronics t

## **Subject Categories**

#### and social sciences

| THE HUMANITI                                                                                                                                                                                                                                                                                                                            | ES                                                                                             | A                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| COMMUNICATIONS AND THE Architecture Art History Cinema Dance Fine Arts Information Science Journalism Library Science Mass Communications Music Speech Communication Theater                                                                                                                                                            | 072<br>037<br>037<br>035<br>039<br>039<br>041                                                  | 29<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78 |

| EDUCATION General Administration Adult and Continuing Agricultural Art Bilingual and Multicultural Business Community College Curriculum and Instruction Early Childhood Elementary Finance Guidance and Counseling Health Higher History of Home Economics Industrial Language and Literature Mathematics Music Philosophy of Physical | 051<br>051<br>051<br>027<br>068<br>072<br>051<br>052<br>051<br>068<br>074<br>052<br>052<br>052 | 46732857847905081902                                                             |

| THE SCIENCES                                                                                                                                                                                                                                                                                                                            | Ai                                                                                             | V                                                                                |

| Psychology Reading Religious Sciences Secondary Social Sciences Sociology of Special Teacher Training Technology Tests and Measurements Vocational | 0535<br>0527<br>0714<br>0533<br>0534<br>0529<br>0530 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| LANGUAGE, LITERATURE AND                                                                                                                           |                                                      |

| LINGUISTICS                                                                                                                                        |                                                      |

| Language                                                                                                                                           |                                                      |

| General                                                                                                                                            | .0679                                                |

| Ancient                                                                                                                                            | .0289                                                |

| Linguistics                                                                                                                                        | .0290                                                |

| Modern                                                                                                                                             | . 0291                                               |

| Literature                                                                                                                                         |                                                      |

| General                                                                                                                                            | .0401                                                |

| Classical                                                                                                                                          | .0294                                                |

| Classical<br>Comparative<br>Medieval                                                                                                               | .0295                                                |

| Medieval                                                                                                                                           | .0297                                                |

| Modern                                                                                                                                             |                                                      |

| Atrican                                                                                                                                            |                                                      |

| American                                                                                                                                           |                                                      |

| Asian                                                                                                                                              | .0305                                                |

| Canadian (English)                                                                                                                                 | .0352                                                |

| Canadian (French)                                                                                                                                  |                                                      |

| English                                                                                                                                            |                                                      |

| Germanic<br>Latin American                                                                                                                         | 0212                                                 |

| Middle Eastern                                                                                                                                     | 0312                                                 |

| Romance                                                                                                                                            |                                                      |

| Slavic and East European                                                                                                                           | 0314                                                 |

| oravic and Last Lotopean                                                                                                                           | . 0014                                               |

| PHILOSOPHY, RELIGION AND                                                                           |                                                             |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| THEOLOGY Philosophy Religion                                                                       | .0422                                                       |

| General Biblical Studies Clergy History of Philosophy of Theology                                  | .0318<br>.0321<br>.0319<br>.0320<br>.0322<br>.0469          |

| SOCIAL SCIENCES American Studies                                                                   | .0323                                                       |

| Anthropology Archaeology Cultural Physical Business Administration                                 |                                                             |

| General Accounting Banking Management Marketing Canadian Studies Economics                         | .0310                                                       |

| General Agricultural Commerce-Business Finance History Labor Theory Folklore Geography Gerontology | .0503<br>.0505<br>.0508<br>.0509<br>.0510<br>.0511<br>.0358 |

| History<br>General                                                                                 | 0578                                                        |

|                                                                                                    |                                                             |

| Ancient<br>Medieval<br>Modern                                       | 0581<br>0582         |

|---------------------------------------------------------------------|----------------------|

| Black<br>African<br>Asia, Australia and Oceania                     | 0331                 |

| Canadian                                                            | 0334                 |

| Latin American Middle Eastern United States                         | 0336                 |

| History of Science Law                                              | 0337<br>0585<br>0398 |

| Political Science<br>General<br>International Law and               |                      |

| International Law and Relations Public Administration               | 0414                 |

| Recreation Social Work                                              | 0814<br>0452         |

| Sociology<br>General                                                | 0626                 |

| Criminology and Penology<br>Demography<br>Ethnic and Racial Studies | 0627<br>0938         |

| Individual and Family                                               |                      |

| Studies                                                             | 0629                 |

| Social Structure and                                                |                      |

| Development Theory and Methods Transportation                       | 0344                 |

| Transportation                                                      | 0999<br>0453         |

|                                                                     |                      |

#### id engineering

| BIOLOGICAL SCIENCES                               |          |

|---------------------------------------------------|----------|

| Agriculture<br>General                            | 0.472    |

| Agronomy                                          | 0285     |

| Agronomy<br>Animal Culture and                    | .0203    |

| Nutrition                                         | 0475     |

| Animal Pathology                                  | 0476     |

| Animal Pathology<br>Food Science and              | . 0-47 0 |

| Technology                                        | 0359     |

| Technology<br>Forestry and Wildlife               | .0478    |

| Plant Culture                                     | .0479    |

| Plant Culture<br>Plant Pathology                  | .0480    |

| Plant Physiology                                  | .0817    |

| Range Management                                  | .0777    |

| Plant Physiology Range Management Wood Technology | .0746    |

| Biology                                           |          |

| General                                           | .0306    |

| Anatomy                                           | . 0287   |

| Biostatistics                                     | . 0308   |

| Botany                                            | .0309    |

| Cell                                              | .0379    |

| Ecology                                           | .0329    |

| Enfomology                                        | 0353     |

| Genetics                                          | .0369    |

| Limnology                                         | .0/93    |

| Microbiology<br>Molecular                         | .0410    |

| Wolecniar                                         | .030/    |

| Neuroscience                                      | .031/    |

| Oceanography                                      | .0410    |

| Physiology                                        | .0433    |

| Radiation                                         | 0779     |

| Veterinary Science                                | 0//0     |

| Zoology<br>Biophysics                             | .0472    |

| General                                           | 0794     |

| Medical                                           |          |

| Medical                                           | . 07 00  |

| EARTH SCIENCES                                    |          |

| Biogeochemistry                                   | .0425    |

| Geochemistry                                      | 0996     |

| Geology Geophysics Hydrology Mineralogy Paleobotany Paleoecology Paleoacology Paleoacology Palynology Physical Geography Physical Oceanography HEALTH AND ENVIRONMENTAL                                                                                                                                              | 0411<br>0345<br>0426<br>0418<br>0985                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| SCIENCES                                                                                                                                                                                                                                                                                                             |                                                                                                                              |

| Environmental Sciences                                                                                                                                                                                                                                                                                               |                                                                                                                              |

| General Audiology Chemotherapy Dentistry Education Hospital Management Human Development Immunology Medicine and Surgery Mental Health Nursing Nutrition Obstetrics and Gynecology Occupational Health and Therapy Ophthalmology Pathology Pharmacology Pharmacy Physical Therapy Public Health Radiology Recreation | 0300<br>0992<br>0567<br>0350<br>0769<br>0758<br>0982<br>0564<br>0347<br>0570<br>0380<br>0354<br>0381<br>0419<br>0572<br>0382 |

| Speech Pathology<br>Toxicology<br>Home Economics                | 0460<br>0383<br>0386 |

|-----------------------------------------------------------------|----------------------|

| PHYSICAL SCIENCES                                               |                      |

| Pure Sciences Chemistry General                                 | 0485                 |

| Agricultural<br>Analytical<br>Biochemistry                      | 0749<br>0486         |

| Inorganic<br>Nuclear<br>Organic                                 | 0488<br>0738         |

| Pharmaceutical<br>Physical                                      | 0491<br>0494         |

| Polymer                                                         | 0754<br>0405         |

| General                                                         |                      |

| Astrophysics                                                    | 0606<br>0608<br>0748 |

| Elementary Particles and High Energy Fluid and Plasma Molecular | 0798<br>0759<br>0609 |

| Nuclear Optics Radiation Solid State Statistics                 | 0752<br>0756<br>0611 |

|                                                                 |                      |

| Applied Sciences Applied Mechanics                              | 0346<br>0984         |

| Engineering<br>General<br>Aerospace                                                                                     | .0538                            |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Agricultural Automotive Biomedical Chemical                                                                             | .0540<br>.0541<br>.0542          |

| Civil Electronics and Electrical Heat and Thermodynamics Hydraulic                                                      | .0348                            |

| Marine                                                                                                                  | .0546<br>.0547<br>.0794<br>.0548 |

| Metallurgy<br>Mining<br>Nuclear<br>Packaging                                                                            | .0743<br>.0551<br>.0552          |

| Petroleum<br>Sanitary and Municipal<br>System Science                                                                   | .0765                            |

| Geotechnology Operations Research Plastics Technology Textile Technology                                                | .0428<br>.0796<br>.0795<br>.0994 |

| PSYCHOLOGY                                                                                                              |                                  |

| General Behavioral Clinical Developmental Experimental Industrial Personality Physiological Psychobiology Psychometrics | .0384<br>.0622<br>.0620<br>.0623 |

| ٨  | ءا |    | _ |

|----|----|----|---|

| ı١ | ıc | ١r | n |

Dissertation Abstracts International est organisé en catégories de sujets. Veuillez s.v.p. choisir le sujet qui décrit le mieux votre thèse et inscrivez le code numérique approprié dans l'espace réservé ci-dessous.

SUJET

## Catégories par sujets

## **HUMANITÉS ET SCIENCES SOCIALES**

| COMMUNICATIONS ET LES AR' Architecture Beaux-arts Bibliothéconomie Cinéma Communication verbale Communications Danse Histoire de l'art Journalisme Musique Sciences de l'information Théâtre                                                                                                                                                                                                                                                                                                    | 0729<br>0357<br>0399<br>0900<br>0459<br>0708<br>0378<br>0377<br>0391<br>0413                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| ÉDUCATION Généralités Administration Art Collèges communautaires Çommerce Economie domestique Education permanente Education préscolaire Education sanitaire Enseignement agricole Enseignement bilingue et mulficulturel Enseignement industriel Enseignement professionnel Enseignement professionnel Enseignement religieux Enseignement secondaire Enseignement spécial Enseignement supérieur Evaluation Finances Formation des enseignants Histoire de l'éducation Langues et littérature | 0514<br>0273<br>0275<br>0278<br>0688<br>0516<br>0518<br>0680<br>0517<br>0521<br>0521<br>0524<br>0524<br>0533<br>0529<br>0529<br>0528 |

| THEOLOGIE                                                                               |              |

|-----------------------------------------------------------------------------------------|--------------|

| Philosophie                                                                             | 0422         |

| Reliaion                                                                                |              |

| Généralités                                                                             | 0318         |

| Clergé<br>Etudes hibliques                                                              | 0321         |

| Histoire des religions                                                                  | 0320         |

| Études bibliques<br>Histoire des religions<br>Philosophie de la religion .<br>Théologie | 0322         |

| Théologie                                                                               | 0469         |

| SCIENCES SOCIALES                                                                       |              |

| Anthropologie                                                                           |              |

| Archéologie                                                                             | 0324         |

| Culturelle<br>Physique                                                                  | 0326<br>0327 |

| Proif                                                                                   | 0398         |

| Economie                                                                                |              |

| Généralités<br>Commerce-Affaires                                                        | 0501<br>0505 |

| Economie agricole<br>Économie du travail                                                | 0503         |

| Economie du travail                                                                     | 0510         |

| Finances<br>Histoire                                                                    | 0508<br>0500 |

| Théorie                                                                                 | 0511         |

| Etudes américaines                                                                      | 0323         |

| Études canadiennes<br>Études féministes                                                 | 0385         |

| Folklore                                                                                | 0358         |

| Géographie                                                                              | 0366         |

| Géographie<br>Gérontologie<br>Gestion des affaires                                      | 0351         |

| Généralités                                                                             | 0310         |

| Généralités<br>Administration                                                           | 0454         |

| Banaues                                                                                 | 0770         |

| Comptabilité<br>Marketing                                                               | 0272<br>0338 |

| Histoire                                                                                |              |

| Histoire générale                                                                       | 0578         |

|                                                                                         |              |

|                                                                                         |              |

| Ancienne<br>Médiévale<br>Moderne<br>Histoire des noirs<br>Africaine<br>Canadienne<br>Etats-Unis                                | 0581<br>0582<br>0328<br>0331<br>0334 |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Européenne Moyen-orientale Latino-américaine Asie, Australie et Océanie Histoire des sciences Loisirs Planification urbaine et | 0336<br>0332<br>0585                 |

| régionale                                                                                                                      |                                      |

| Généralités                                                                                                                    |                                      |

| internationales                                                                                                                | 0616                                 |

| Sociologie Généralités Aide et bien-àtre social Criminologie et établissements                                                 | 0626<br>0630                         |

| pénitentiaires<br>Démographie<br>Études de l' individu et                                                                      | 0627<br>0938                         |

| de la famille<br>Études des relations                                                                                          | 0628                                 |

| interethniques et<br>des relations raciales<br>Structure et développement                                                      | 0631                                 |

| social                                                                                                                         | 0700<br>0344                         |

| industrielles<br>Transports<br>Travail social                                                                                  |                                      |

|                                                                                                                                |                                      |

## SCIENCES ET INGÉNIERIE

| SCIENCES BIOLOGIQUES Agriculture                                                          |

|-------------------------------------------------------------------------------------------|

| Généralités                                                                               |

|                                                                                           |

| Culture                                                                                   |

| Pathologie animale                                                                        |

| Physiologie végétale 0817<br>Sylviculture et laune 0478                                   |

| biologie                                                                                  |

| Généralités 0306                                                                          |

| Anatomie 0287 Biologie (Statistiques) 0308 Biologie moléculaire 0307                      |

| Botanique 0309<br>Çellule 0379                                                            |

| Ecologie 0329<br>Entomologie 0353                                                         |

| Genetique                                                                                 |

| Limnologie                                                                                |

| Nourologie (1317                                                                          |

| Physiologie                                                                               |

| Océanographie 0416 Physiologie 0433 Radiation 0821 Science vétérinaire 0778 Zoologie 0472 |

| Zoologie                                                                                  |

| Biophysique Généralités                                                                   |

| SCIENCES DE LA TERRE                                                                      |

| Biogéochimie                                                                              |

| Géodésie                                                                                  |

| Ocograpine priyarque                                                                      |

| Géologie                                                                                                                                                                                                    | .0388<br>.0411<br>.0415<br>.0345                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| SCIENCES DE LA SANTÉ ET DE L'ENVIRONNEMENT                                                                                                                                                                  |                                                                                        |

| Économie domestique<br>Sciences de l'environnement                                                                                                                                                          | .0386<br>.0768                                                                         |

| Sciences de la santé Généralités Administration des hipitaux . Alimentation et nutrition Audiologie Chimiothérapie Dentisterie Développement humain Enseignement Immunologie Loisirs Médecine du travail et | .0300                                                                                  |

| Médecine du travail et thérapie                                                                                                                                                                             | .0354<br>.0564<br>.0380<br>.0381<br>.0460<br>.0571<br>.0572<br>.0419<br>.0382<br>.0574 |

| SCIENCES PHYSIQUES                                                   |        |

|----------------------------------------------------------------------|--------|

| Sciences Pures                                                       |        |

| Chimie                                                               |        |

| Genéralités                                                          |        |

| Biochimie                                                            |        |

| Chimie agricole                                                      |        |

| Chimie analytique                                                    | 0486   |

| Chimie minérale                                                      | 0488   |

| Chimie nucléaire                                                     | 0738   |

| Chimie organique                                                     | 0490   |

| Chimie pharmaceutique                                                | 0491   |

| Physique                                                             | 0494   |

| PolymCres                                                            |        |

| Radiation                                                            | 0/ 54  |

| Mathématiques<br>Physique                                            | 0403   |

| Généralités                                                          | 0405   |

| Acoustique                                                           |        |

| Astronomie et                                                        | 0700   |

| astrophysique                                                        | 0606   |

| Electronique et électricité                                          | 0607   |

| Fluides et plasma                                                    | 0759   |

| Météorologie                                                         | 0608   |

| Fluides et plasma<br>Météorologie<br>Optique<br>Particules (Physique | 0752   |

| Particules (Physique                                                 |        |

| nucleatrel                                                           | (1/VX  |

| Physique atomique<br>Physique de l'état solide                       | 0748   |

| Physique de l'état solide                                            | 0611   |

| Physique moléculaire<br>Physique nucléaire                           | 0609   |

| Physique nucleaire                                                   | .0610  |

| Radiation                                                            |        |

| Statistiques                                                         | 0463   |

| Sciences Appliqués Et                                                |        |

| Tochnologio                                                          |        |

| Informatique                                                         | . 0984 |

| Ingénierie                                                           |        |

| Ğénéralités                                                          | . 0537 |

| Agricole                                                             | 0539   |

| Automobile                                                           | 0540   |

| sructure et aeveloppement<br>social                                                                                                                                                                                                             | .0629                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Biomédicale                                                                                                                                                                                                                                     | .0541                                                                |

| Chaleur et ther modynamique                                                                                                                                                                                                                     | . 0348                                                               |

| Conditionnement (Emballage) Génie aérospatial Génie chimique Génie civil                                                                                                                                                                        | .0549<br>.0538<br>.0542                                              |

| Génie électronique et électrique Génie industriel Génie mécanique Génie nucléaire Ingénierie des systämes Mécanique navale Métallurgie Science des matériaux Technique du pétrole Technique minière Techniques sanitaires et                    | .0546<br>.0548<br>.0552<br>.0790<br>.0547<br>.0743<br>.0794<br>.0765 |

| municipales                                                                                                                                                                                                                                     | .0428                                                                |

| (Technologie)<br>Recherche opérationnelle<br>Textiles et tissus (Technologie)                                                                                                                                                                   | .0/96                                                                |

| PSYCHOLOGIE  Généralités Personnalité Psychobiologie Psychologie dinique Psychologie du comportement Psychologie du développement Psychologie expérimentale Psychologie industrielle Psychologie physiologique Psychologie sociale Psychometrie | .0625<br>.0349<br>.0622<br>.0384<br>.0620<br>.0623<br>.0624<br>.0989 |

## A LOCALLY SYNCHRONOUS GLOBALLY ASYNCHRONOUS VERTEX-8 PROCESSING ELEMENT FOR IMAGE RECONSTRUCTION ON A MESH

ΒY

#### JEFFREY W. FITCHETT

A Thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

© 1993

Permission has been granted to the LIBRARY OF THE UNIVERSITY OF MANITOBA to lend or sell copies of this thesis, to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publications rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's permission.

I hereby declare that I am the sole author of this thesis.

I authorize the University of Manitoba to lend this thesis to other institutions or individuals for the purpose of scholarly research.

## Jeffrey W. Fitchett

I further authorize the University of Manitoba to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Jeffrey W. Fitchett

## **ABSTRACT**

## A Locally Synchronous Globally Asynchronous Vertex–8 Processing Element for Image Reconstruction on a Mesh

Abstract. Image or field reconstruction problems from non–invasive measurements are a class of signal processing applications that demand parallel processing to achieve real–time operation. Image reconstruction from parallel beam projections, an example of which is the CAT (Computerized Axial Tomography) scan, falls within this class. This thesis considers a novel architecture suitable for WSI (Wafer Scale Integration) on which algorithms for image reconstruction from parallel beam projections or other cyclic image processing algorithms could be embedded, namely the mesh of vertex–8 processors. We will show how to map iterative reconstruction algorithms onto a fine–grained mesh of custom processors and allow the reader to infer mappings for other image transform (such as the Hough transform) and pattern recognition problems. The focus is on the hardware design of a locally synchronous globally asynchronous vertex–8 processing element (PE) that is suitable for implementation in a WSI array with one PE per pixel. The PE has several unique features, including self–timed handshaking elements for inter–processor communications and a novel asynchronous scan test structure. Test chips have been sent for fabrication.

Acknowledgements

I would like to thank my advisor, Professor R.D. McLeod, who unintimidating approach to

academics and research was highly motivating and greatly appreciated. The assistance of

many, if not all, graduate students was indispensable. In particular, thanks to Martin Meier,

Dean McNeill, and David Blight for their skill and patience while helping me with many

computer problems.

Financial support from the Natural Sciences and Engineering Council of Canada and

equipment loans from the Canadian Microelectronics Corporation (CMC) are gratefully ac-

knowledged. Access to manufacturing technology was donated by Northern Telecom Elec-

tronics Incorporated through the CMC. The Manitoba Telephone System allowed a leave

of absence for me to complete my degree and provided financial support and equipment

loans.

**Dedication**

Lastly, I would like to thank my wife Sher, for her continued support in my self indulgent

endeavors. I dedicate this thesis to her and to our daughter Ariel Dawn.

Jettrey w. Fitchett June 18, 1993

-iii-

## **Table of Contents**

| Abstract                                   | i        |

|--------------------------------------------|----------|

| Acknowledgements                           | ii       |

| Table of Contents                          | iv       |

| List of Figures                            | ,        |

| List of Tables                             | v        |

| List of Charts                             | v        |

|                                            | Y        |

| CHAPTER 1                                  |          |

| Introduction                               | 1        |

| 1.1 THEORY                                 | 4        |

|                                            |          |

| CHAPTER 2                                  |          |

| Array Architecture                         |          |

| and Algorithm Simulations                  | 16       |

| 2.1 SEQUENTIAL SIMULATIONS                 | 16       |

| 2.2 ARRAY ARCHITECTURE                     | 29       |

| 2.3 PARALLEL SIMULATIONS                   | 31       |

|                                            |          |

| CHAPTER 3                                  |          |

| Processing Element Hardware Design         | 39       |

| 3.1 PREAMBLE: ASYNCHRONOUS BUILDING BLOCKS | 43       |

| 3.2 C & DELAY ELEMENTS                     | 54       |

| 3.3 PIPELINE                               | 57       |

| 3.4 ASYNCHRONOUS SCAN TEST                 | 62       |

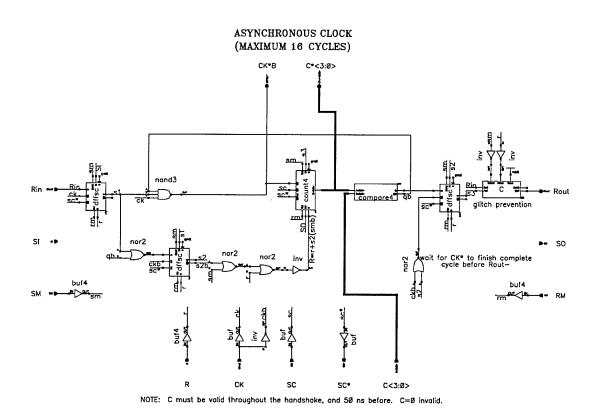

| 3.5 ASYNCHRONOUS CLOCK                     | 69       |

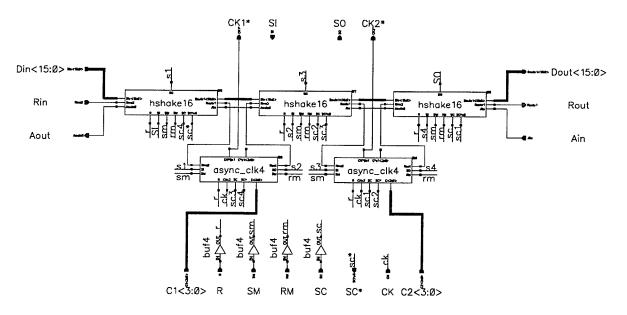

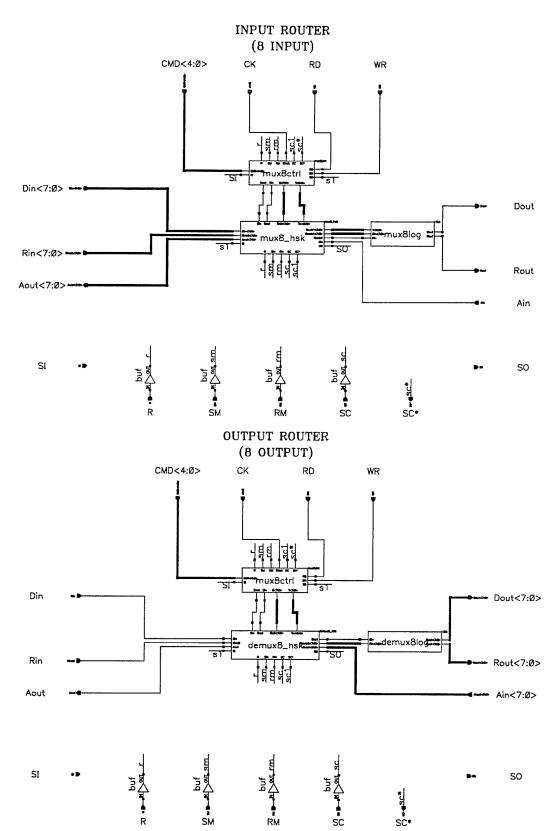

| 3.6 I/O ROUTERS                            | 71       |

| 3.7 SERIAL TO PARALLEL/PARALLEL TO SERIAL  | 83       |

| 3.8 ALU                                    | 85       |

| 3.9 PROCESSING ELEMENT                     | 88       |

| 3.10 I/O BUFFER                            | 91<br>91 |

| 3.12 AREA AND PERFORMANCE CONSIDERATIONS   | 100      |

| 3.12 Auch And Leid Oldwarec Condidenations | 100      |

| CHAPTER 4                                  |          |

| Conclusions                                | 103      |

| 4.1 FUTURE WORK                            | 105      |

| 4.2 CLOSING COMMENTS                       | 106      |

|                                            |          |

| REFERENCES                                 | 107      |

| ADDENITY A                                 |          |

| APPENDIX A                                 | 100      |

| Acronyms and Abbreviations                 | 109      |

| APPENDIX B                                 |          |

| Technical Reference Addendum Contents      | 111      |

## **List of Figures**

| FIGURE 1 Parallel rays projected through an unknown image[30]                       | 2  |

|-------------------------------------------------------------------------------------|----|

| FIGURE 2 The Kaczmarz method of solving algebraic equations.[30]                    | 8  |

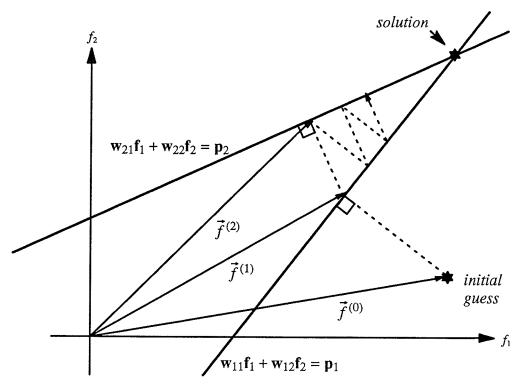

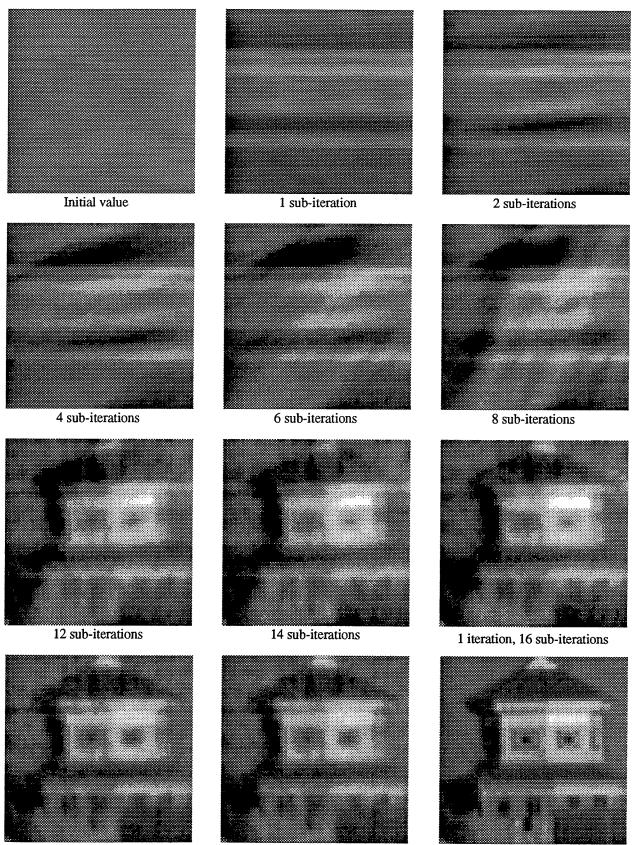

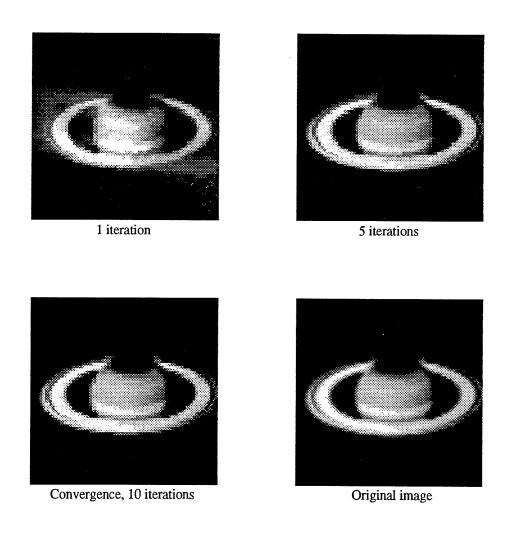

| FIGURE 3 Saturn reconstructed from 4 projections using the ART algorithm            | 20 |

| FIGURE 4 The U of M Administration Building reconstructed from 4 projections,       |    |

| showing the first 16 sub-iterations.                                                | 21 |

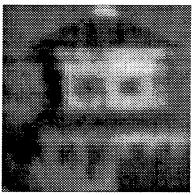

| FIGURE 5 The U of M Administration Building reconstructed from 16 projections,      | 00 |

| showing the ART algorithm converging and SBP and FBP reconstructions                | 22 |

| FIGURE 6 The U of M Administration Building reconstructed from 32 projections,.     | 23 |

| FIGURE 7 Saturn reconstructed from 64 projections.                                  | 24 |

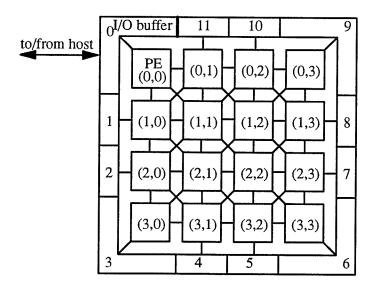

| FIGURE 8 The proposed array, shown for a 4x4 image.                                 | 29 |

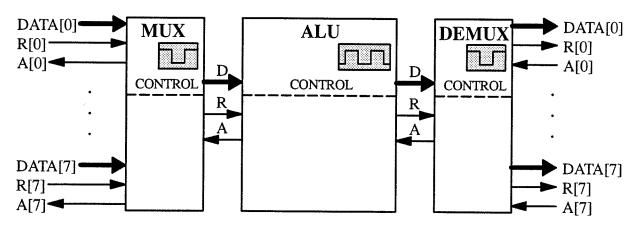

| FIGURE 9 The processing element for the proposed array.                             | 29 |

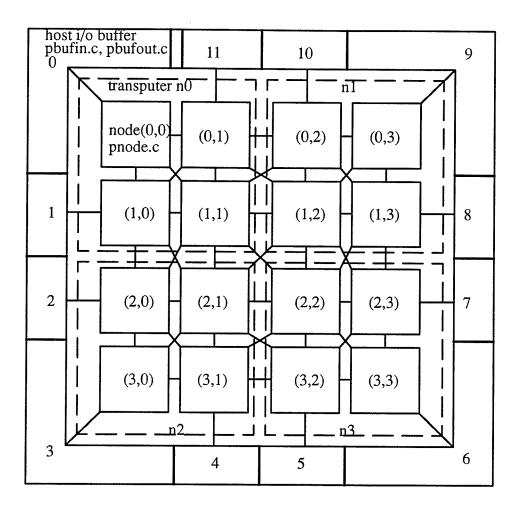

| FIGURE 10 Typical software embedding in the transputer array                        | 33 |

| FIGURE 11 A parallel reconstruction using SIRT from 2 angles                        | 37 |

| FIGURE 12 A parallel reconstruction from 4 angles.                                  | 37 |

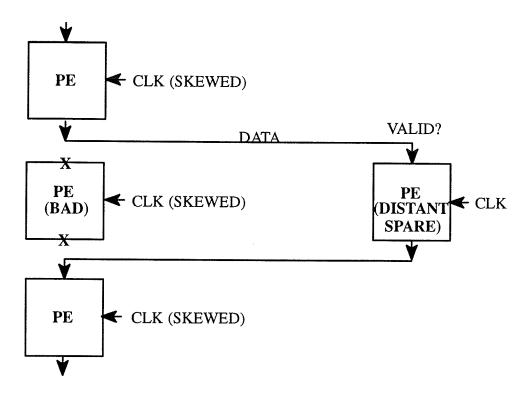

| FIGURE 13 Problems with clock skew and fault tolerance.                             | 40 |

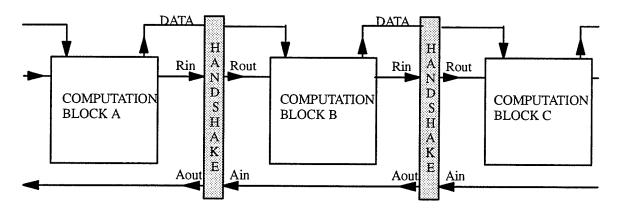

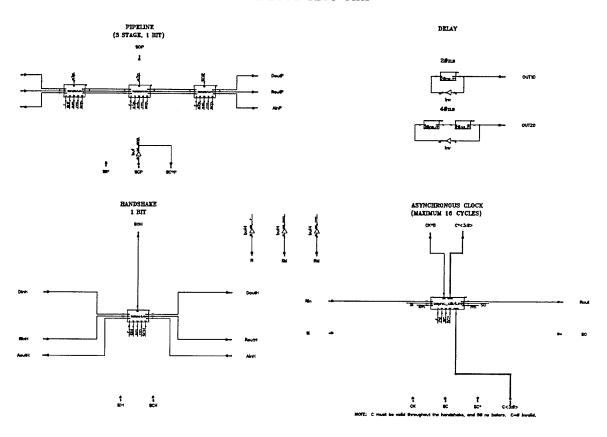

| FIGURE 14 A pipeline.                                                               | 43 |

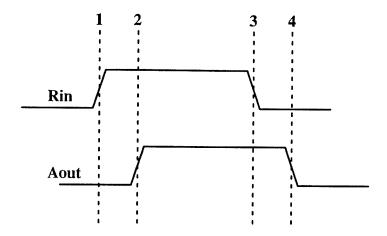

| FIGURE 15 Typical 4—phase handshaking cycle.                                        | 44 |

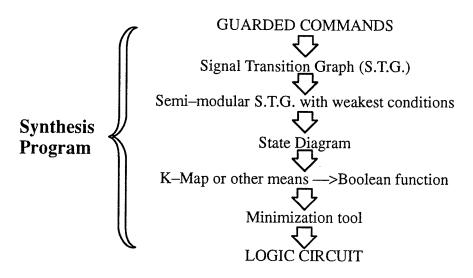

| FIGURE 16 Meng et al.'s synthesis methodology.                                      | 45 |

| FIGURE 17 Signal transition graphs.[24]                                             | 47 |

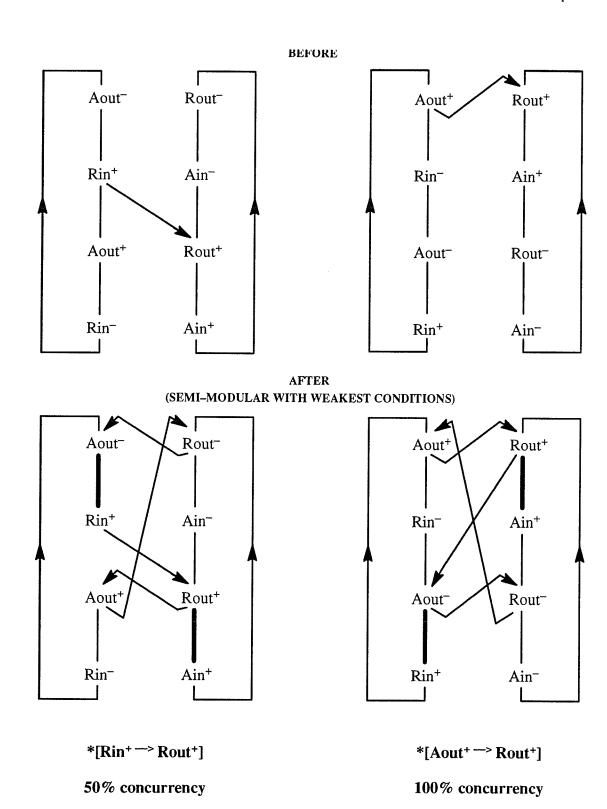

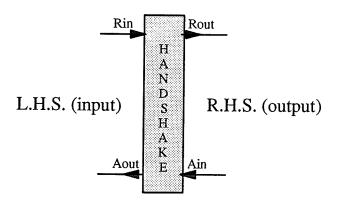

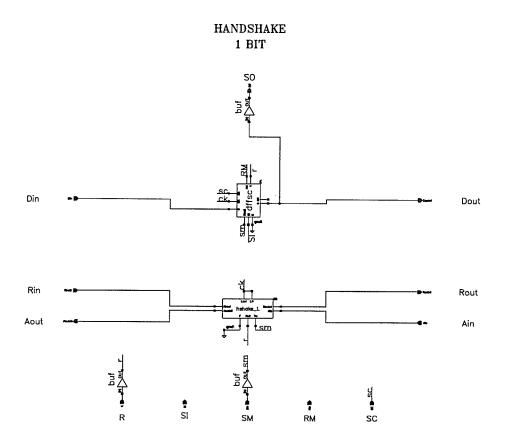

| FIGURE 18 Handshake circuit for a pipeline.                                         | 48 |

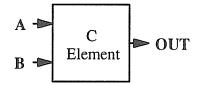

| FIGURE 19 C element implemented with SR latches.                                    | 49 |

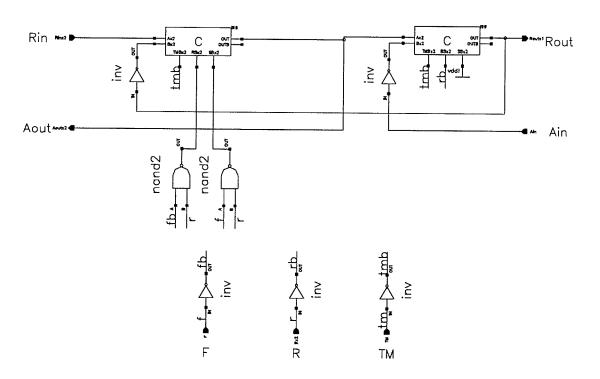

| FIGURE 20 The handshake element schematic.                                          | 51 |

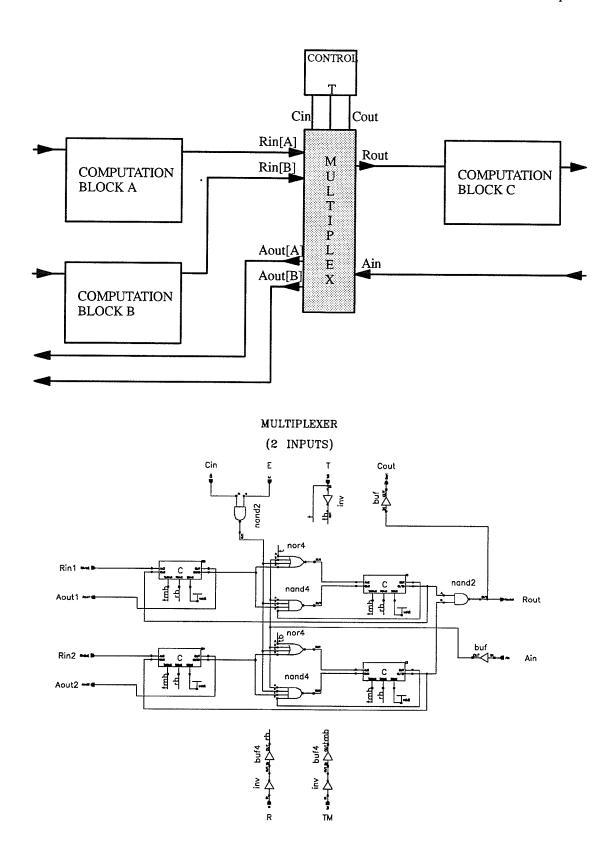

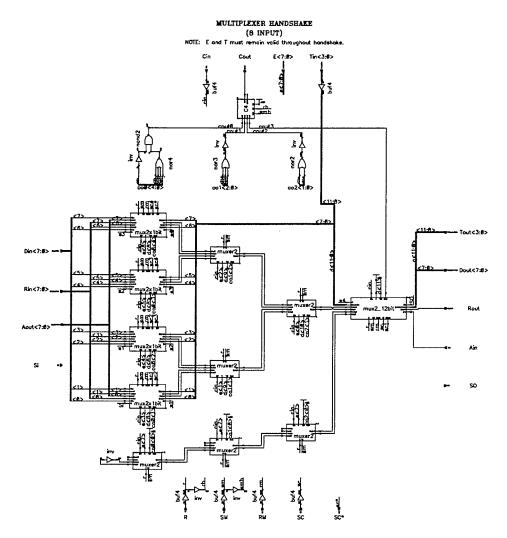

| FIGURE 21 The multiplexer.                                                          | 52 |

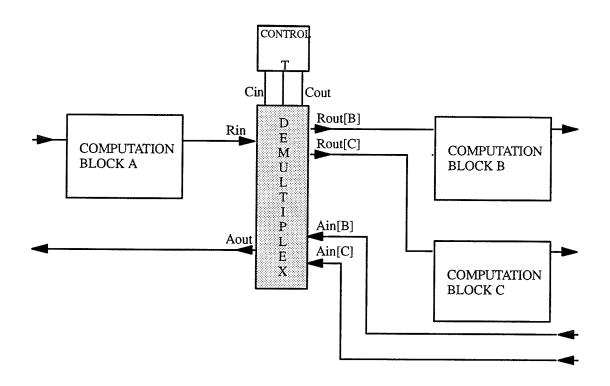

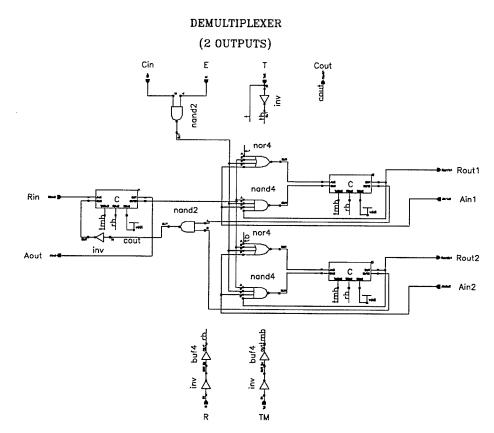

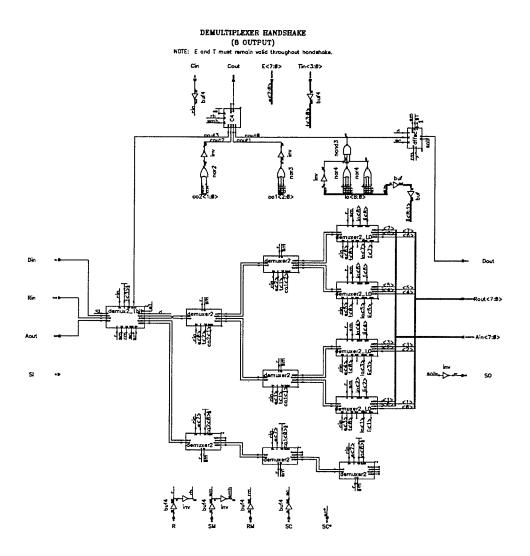

| FIGURE 22 The demultiplexer.                                                        | 53 |

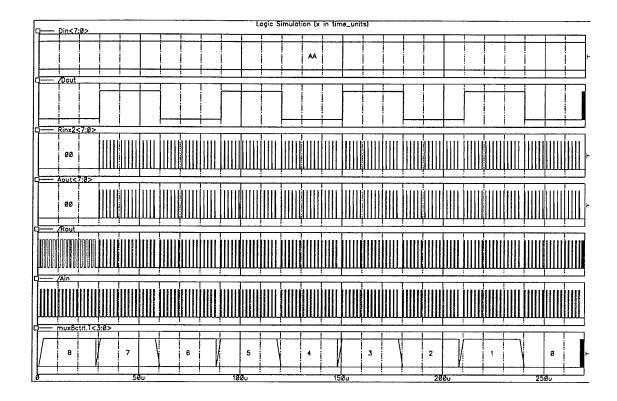

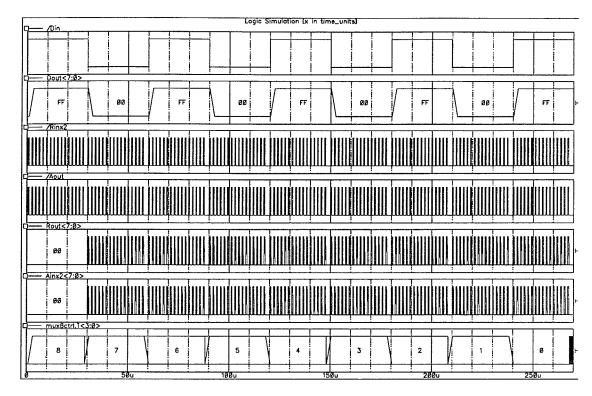

| FIGURE 23 A simulation for the 2 input multiplexer handshake circuit                | 54 |

| FIGURE 24 Clock stealing circuit.                                                   | 56 |

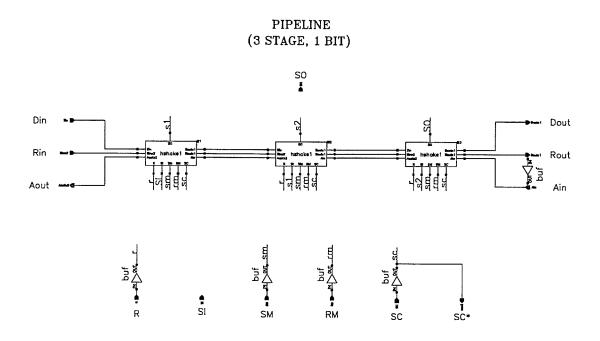

| FIGURE 25 A 3 stage by 1 bit test pipeline.                                         | 58 |

| FIGURE 26 The handshake block for the 3x1 bit pipeline                              | 59 |

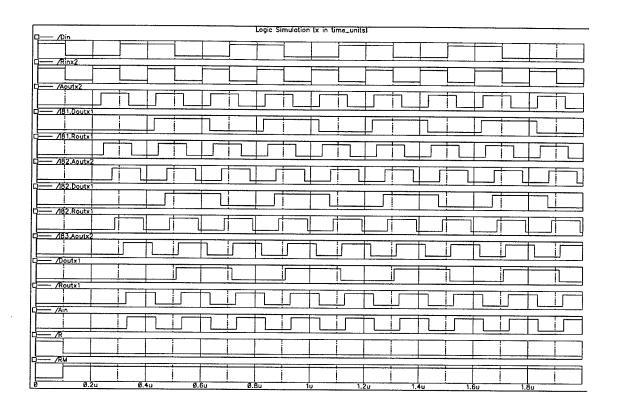

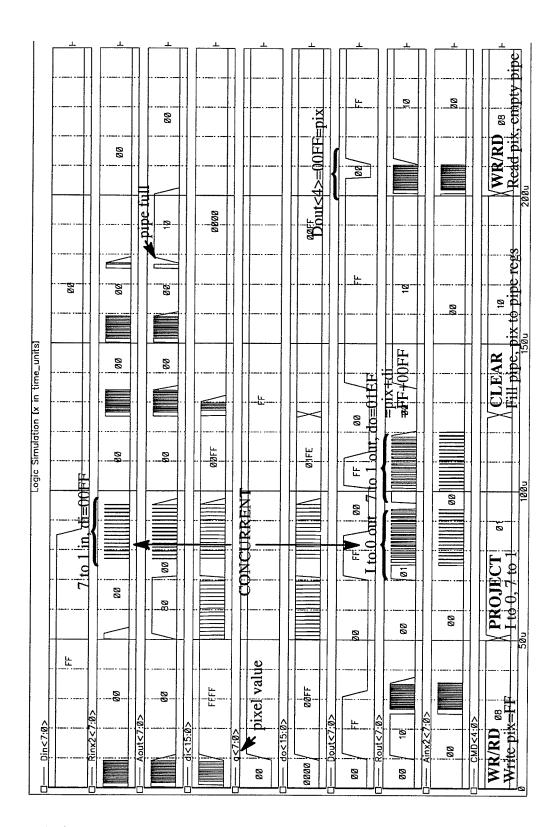

| FIGURE 27 A simulation of the 3x1 pipeline with 20ns delay elements                 | 60 |

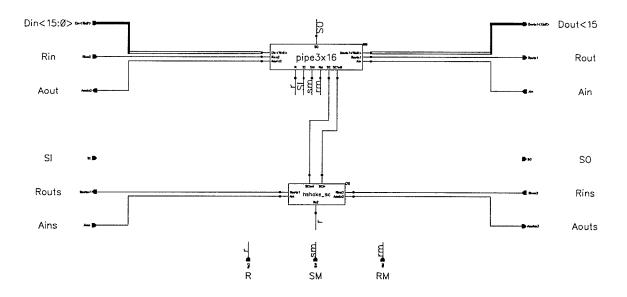

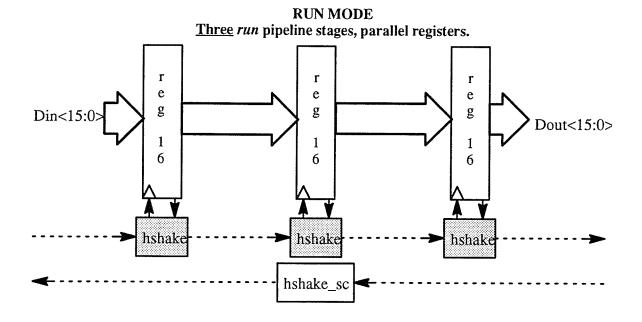

| FIGURE 28 A 3 stage 16 bit pipeline with scan test.                                 | 62 |

| FIGURE 29 The internal registers of a 3 stage 16 bit pipeline in run and scan mode. | 63 |

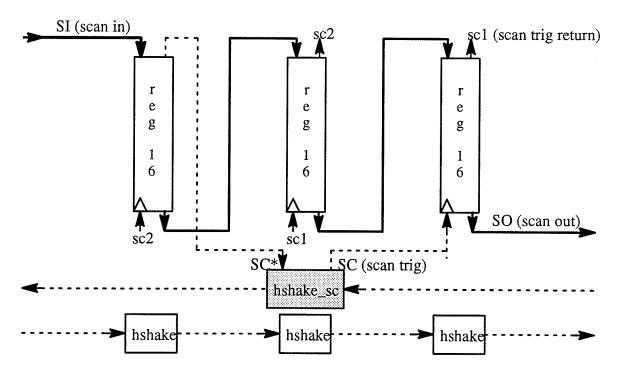

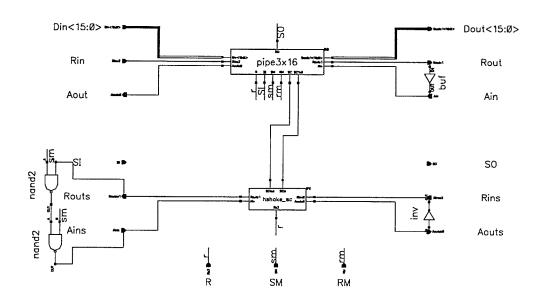

| FIGURE 30 The test setup for the 3 stage by 16 bit scannable pipeline               | 64 |

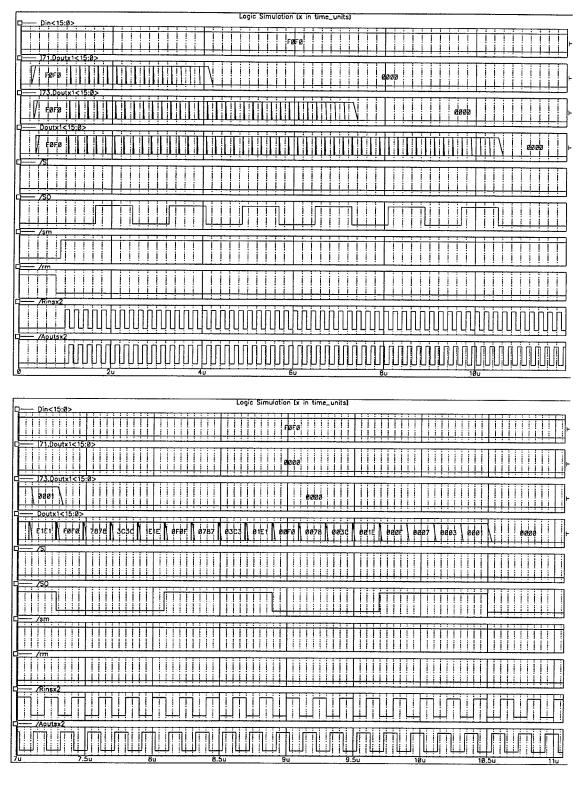

| FIGURE 31 Waveforms from a simulation run performing scan test pipeline             | 65 |

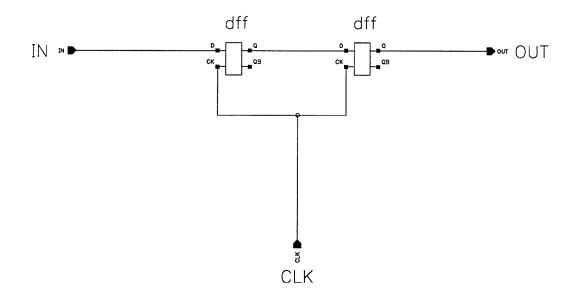

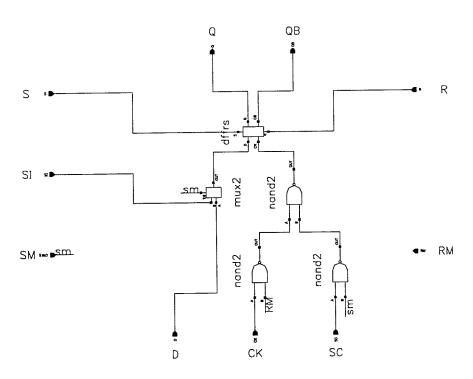

| FIGURE 32 A asynchronously scannable D flip flop.                                   | 67 |

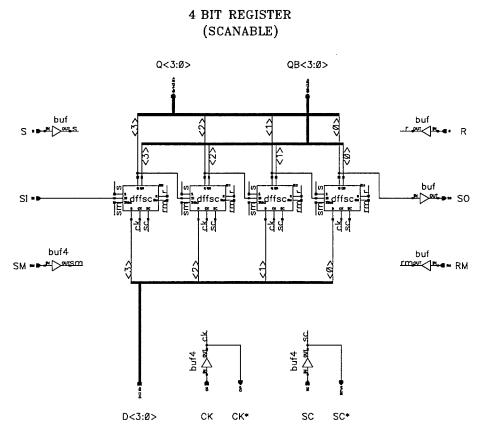

| FIGURE 33 A scannable 4 bit register.                                               | 69 |

| FIGURE 34 An asynchronous clock circuit.                                            | 70 |

| FIGURE 35 A pipeline with clocked computation blocks                                | 71 |

| FIGURE 36 The input and output routers.                                             | 72 |

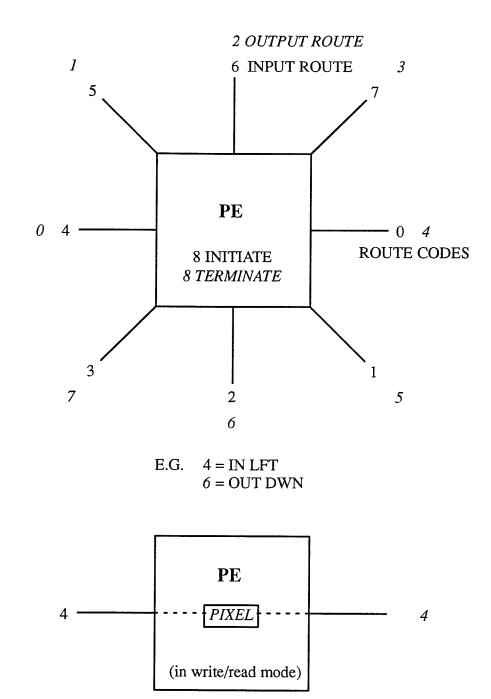

| FIGURE 37 Processing element routing scheme.                                        | 75 |

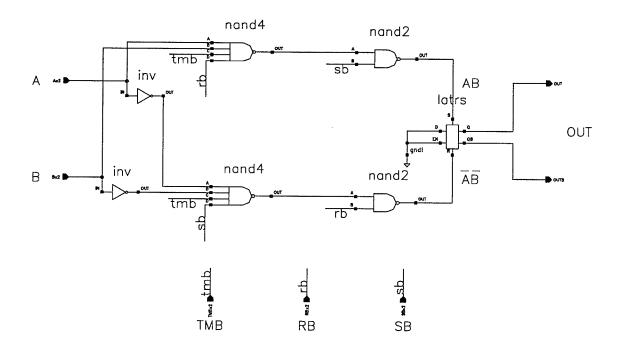

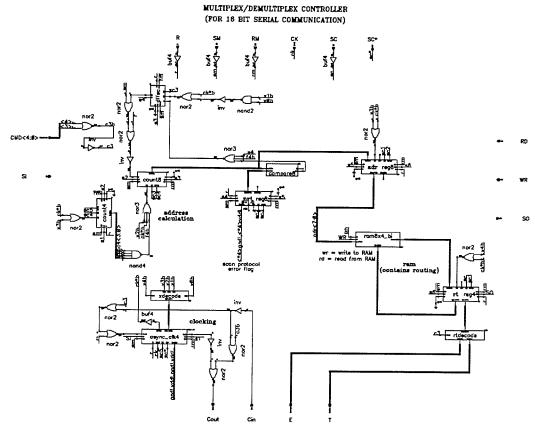

| FIGURE 38 The multiplex and demultiplex controller.                                 | 76 |

| FIGURE 39 The multiplex handshake circuit.                                          | 79 |

| FIGURE 40 The demultiplex handshake circuit.                                        | 80 |

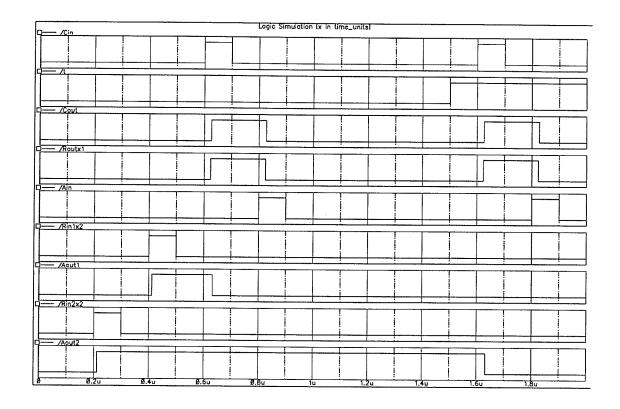

| FIGURE 41 Input router simulation.                                                  | 82 |

| FIGURE 42 Output router simulation, dual of the input router                        | 83 |

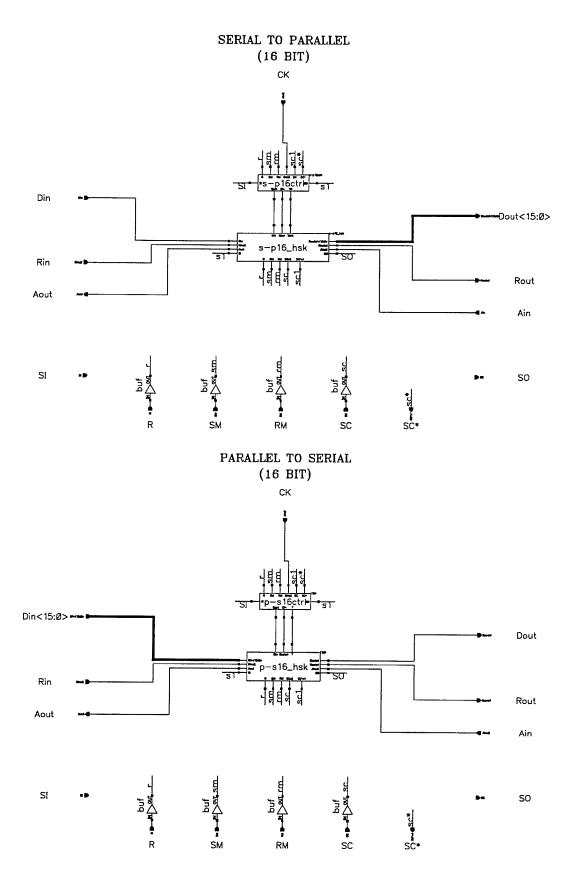

| FIGURE 43 The serial to parallel and parallel to serial converter                   | 84 |

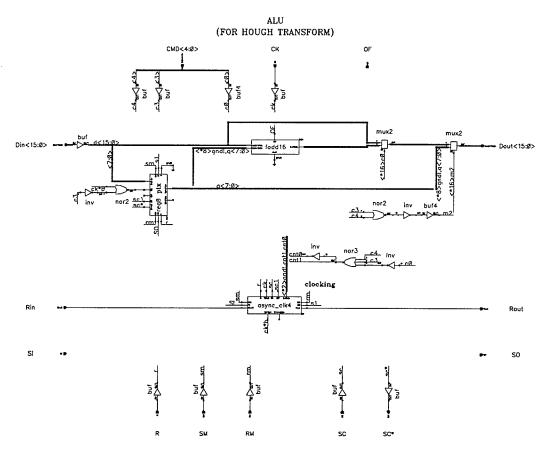

| FIGURE 44 The ALII                                                                  | 85 |

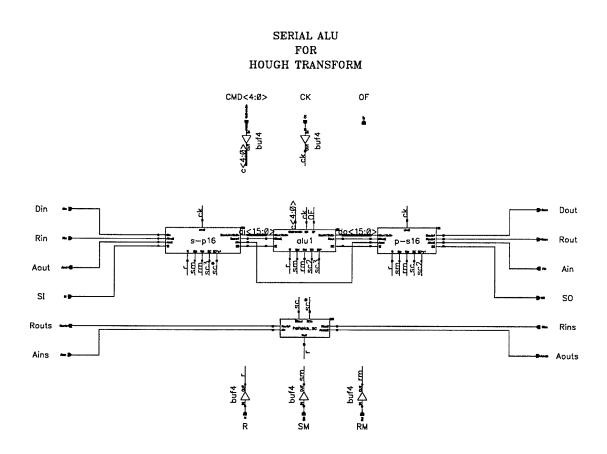

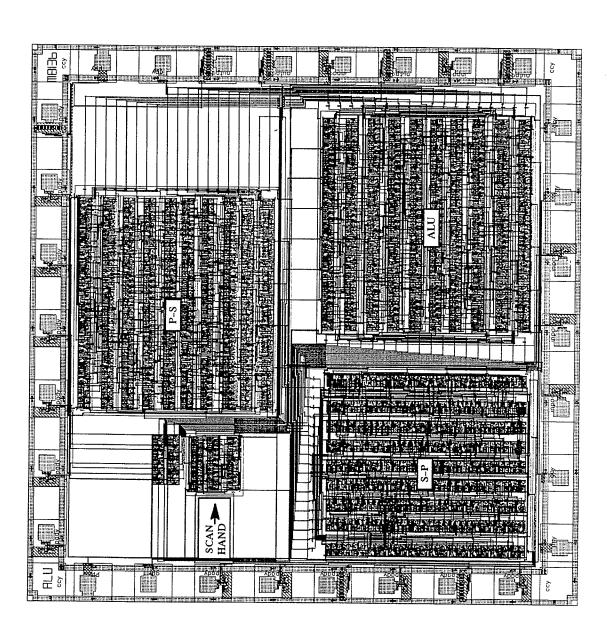

| FIGURE 45 | The ALU and serial to parallel converters as on the test chip     | 87 |

|-----------|-------------------------------------------------------------------|----|

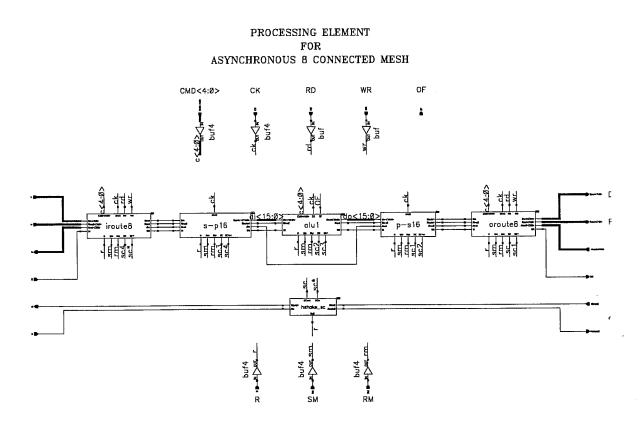

| FIGURE 46 | The processing element or PE                                      | 88 |

| FIGURE 47 | A simulation showing operation of the commands                    | 90 |

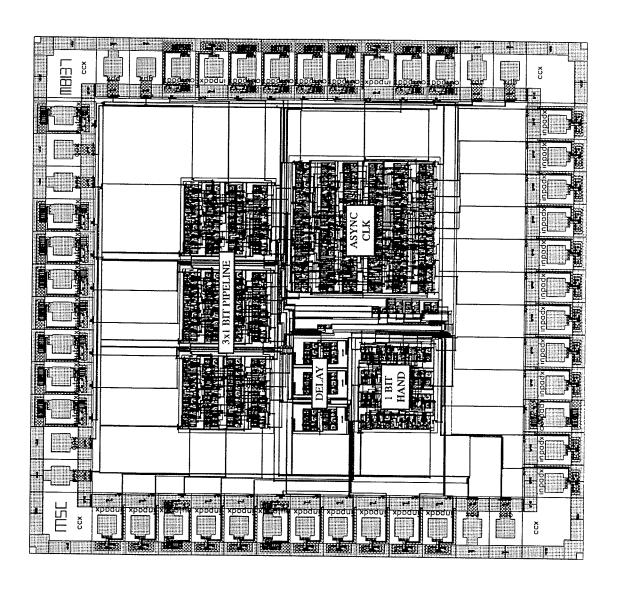

| FIGURE 48 | The miscellaneous test chip schematic                             | 93 |

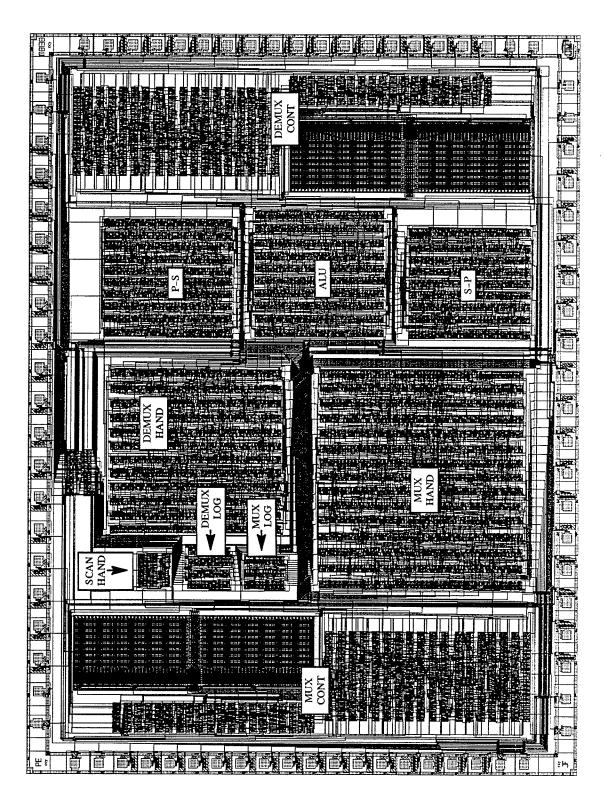

| FIGURE 49 | Processing element layout, showing the metal1 and metal2 layers   | 95 |

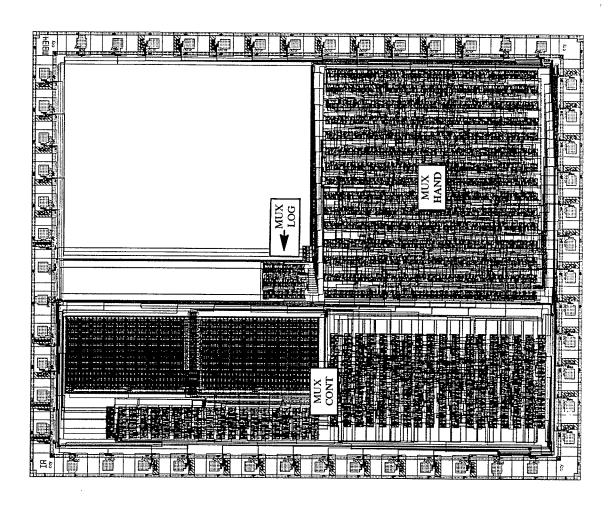

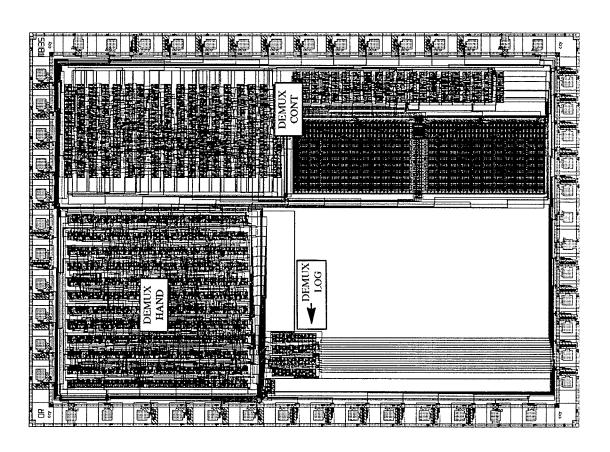

| FIGURE 50 | Input router layout                                               | 96 |

| FIGURE 51 | Output router layout                                              | 97 |

| FIGURE 52 | ALU layout, with serial to parallel/parallel to serial conversion | 98 |

| FIGURE 53 | Miscellaneous chip layout                                         | 99 |

|           |                                                                   |    |

## **List of Tables**

| TABLE 1 C element truth table                          | 55 |

|--------------------------------------------------------|----|

| TABLE 2 Control signal sequence to enter scan mode     | 68 |

| TABLE 3 Control signal sequence to exit scan mode      | 68 |

| TABLE 4 Enable and select patterns for each route code | 79 |

| TABLE 5 Chip specifications.                           | 94 |

## **List of Charts**

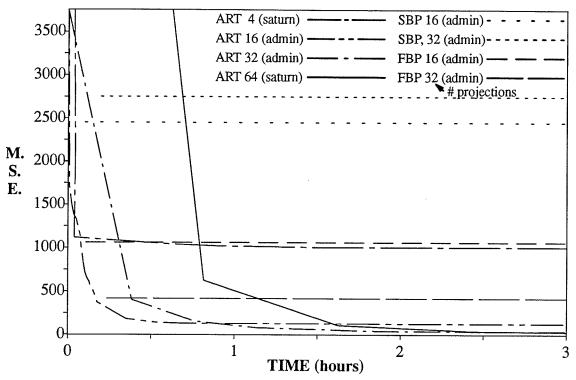

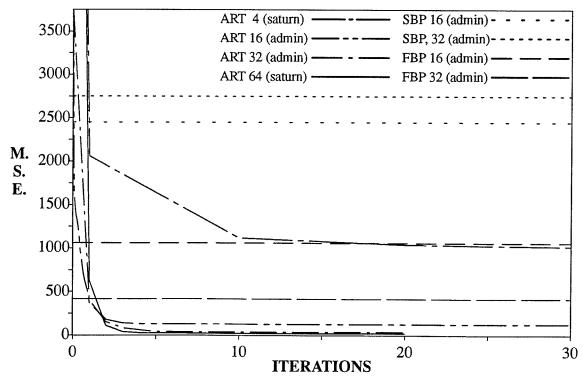

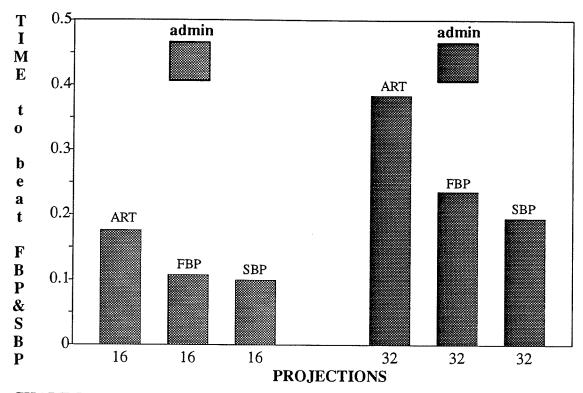

| CHART 1 The mean squared error vs. time for the algorithms                       | 26 |

|----------------------------------------------------------------------------------|----|

| CHART 2 The mean squared error vs. the number of iterations                      | 26 |

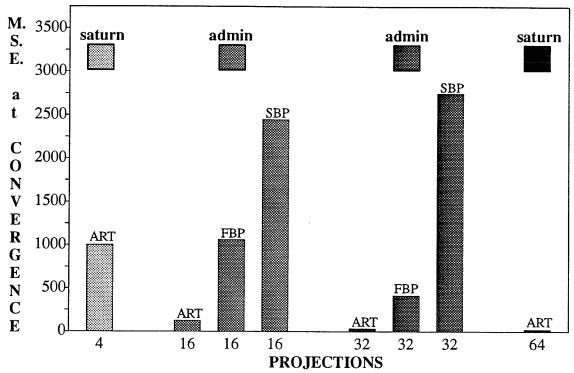

| CHART 3 The mean squared error at convergence vs. the number of projections      | 27 |

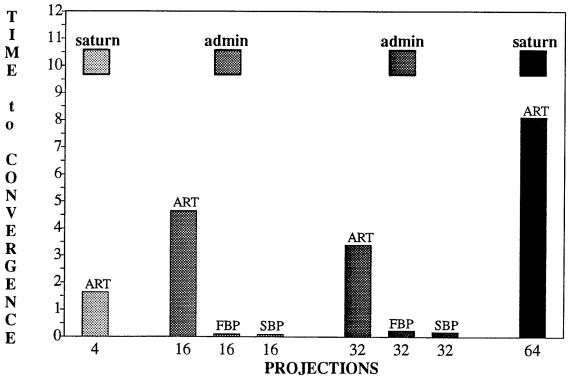

| CHART 4 The time to convergence vs. the number of projections                    | 27 |

| CHART 5 The time required for the ART algorithm to give a better reconstruction. | 28 |

## CHAPTER 1

## Introduction

Multi-processor application specific integrated circuits (ASIC's) that make use of an entire silicon or gallium-arsenide wafer are an area of much current research because of their potential to speed up computationally intensive algorithms to real time. Real time operation is often needed in signal and image processing applications, applications where the amount of data per unit time to be processed may be too large for a conventional Von Neumann machine. One such application is image reconstruction. In particular, image reconstruction from parallel beam projections is an application that has important uses in medicine, biology, and astronomy. One example in medicine is the CAT (Computerized Axial Tomography) scan. Iterative algebraic reconstruction techniques have been shown to give superior reconstructions to the common commercial technique of Fourier filtered back projection[6], but commercial implementation of improved algorithms has been limited because of computational cost. The processing power needed and the large number of nearest-neighbor communications in the iterative algorithms make them likely candidates for parallel computing multi-processor ASIC arrays; this thesis studies an architecture suitable for image reconstruction from parallel beam projections, namely the mesh of vertex-8 processors. The focus is on the hardware implementation of a globally asynchronous locally synchronous processing element (PE) for such an array, which has several unique features that make it suitable for WSI (Wafer Scale Integration) including the locally synchronous globally asynchronous architecture, self-timed handshake components for inter-processor communications, and asynchronous scan test. These features would be useful for a fault tolerant WSI array. A

processing element for the proposed array was designed in VLSI (Very Large Scale Integration) and sent for fabrication.

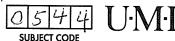

In the reconstruction from parallel beams problem, parallel rays are projected thought an unknown image plane and their intensities detected on the other side, as in Figure 1. The difference between the transmitted and received intensities is the ray integral, the sum

FIGURE 1 Parallel rays projected through an unknown image. [30]

of the image densities that it has passed through. By rotating the image plane or the transmitter and detector arrays, enough projection data can be obtained to reconstruct the image. Various techniques have been proposed to accomplish the reconstruction, the most popular of which is a Fourier method known as Filtered Back Projection (FBP). Other techniques such as direct matrix inversion, constraint optimization, and iterative algebraic methods can give better results but are more computationally expensive. The iterative techniques we will

study are called ART (Algebraic Reconstruction Techniques).[12][13] We have performed simulated reconstructions for small images on a personal computer that have taken hours to converge using a basic ART method. A typical acquisition time for a CAT Scan machine is 1 milli–second per 1000 element projection vector, which means we must reconstruct a 1000x1000 pixel image in 1 second to do it in real time. Robotic vision applications will required even faster speeds. The reconstruction problem clearly is a candidate for application specific and/or parallel computing, such as in our proposed array.

Our array is a square mesh with one processor per pixel. The array is able to handle the bulk of the calculations in parallel, using pipelining to acheive a high degree of concurrency. Each processing element (PE) has vertex-8 connections and programmable routing tables. It is able to communicate with each of its 8 nearest neighbors and is controlled by a global command, in an SIMD (single instruction multiple data) arrangement. The large number of fine-grained processors required make it unlikely that the entire array could be manufactured on a single chip in VLSI. There are many VLSI micro-chips on the original silicon or gallium-arsenide wafer, of which a percentage are faulty; the process of trying to make use of the entire wafer is called WSI or Wafer Scale Integration. For our array, the yield of a WSI process with current technology would be unacceptable, implying that fault tolerance would have to be incorporated. Implementing a fault tolerant scheme is a synchronous WSI system would be very difficult, given that clock distribution alone in large synchronous systems is a formidable problem that has not been overcome. A globally asynchronous locally synchronous array rather than a clocked systolic one would therefore have greater potential for practical use in a WSI implementation, and that is the design philosophy we follow.

The sequential form of the iterative solutions that we wish to embed on the array will be described in the remainder of Chapter 1. In Chapter 2, *Array Architecture and Algorithm*

Simulations, we describe how the algorithms can be parallelized on our proposed vertex—8 mesh of processors. We discuss the time complexity implications for the case of one PE per pixel. Parallel simulations were done on a transputer array to verify the validity of the proposed architecture. The transputer simulations were made to closely model the envisioned hardware to provide a functional test of the PE before implementing it in VLSI. Chapter 3, Processing Element Hardware Design, contains details of the hardware design of the PE including a description of self—timed building blocks and major integrated components. Conclusions and recommendations for future work will be discussed in Chapter 4.

Although the array architecture we will propose can have very general uses depending on the design of the ALU (Arithmetic Logic Unit) within the PE, we have chosen to concentrate on a particular set of algorithms for reasons of succinctness and clarity. These are the iterative algorithms for image reconstruction from parallel beam projections. The reader can infer many other applications that could be embedded into our proposed array that retain the communications infrastructure used by our PE and would require only simple, if any, modifications of the PE's ALU. Our implementation differs from those in the literature[20]. Our array is fine grained and globally asynchronous with locally synchronous computing. Other implementations have used complex off the shelf processors or transputers. Our design has programmable routes, making it useful for non–algorithmic path mappings and thus suitable for many other applications such as pattern recognition. The use of programmable routing tables is a reasonable approach for cyclic algorithms. Other implementations calculate the routes dynamically, which places limits on flexibility of the paths through the array and the speed with which the array can operate.

Image and field reconstruction problems on a digital computer are currently becoming as common as they are computationally expensive. In this thesis we will examine a parallel algorithm and WSI architecture for a particular reconstruction problem, reconstruction

of 2-dimensional images from parallel beam projections. The architecture could find application in other reconstruction problems as well.

## 1.1 THEORY

After a model for the image space is described, an iterative technique based on theory developed by Kaczmarz[30] will be developed and then approximated in a form more suitable for implementation in a digital computer. The approximated form, devised by Gordon et al.,[12][13] is called ART for Algebraic Reconstruction Technique. A modification to the algorithm proposed by Gilbert[11] called SIRT (Simultaneous Iterative Reconstruction Technique) that will improve noise performance will be explained.

#### 1.1.1 The Problem

Image space is represented as in Figure 1. Here f(x,y), the unknown image in region R, is split into a grid of N square elements denoted  $f_j$ . Parallel rays of width  $\tau$  pass through the image resulting in M measured rays sums  $p_i$ . Both  $f_j$  and  $p_i$  have one—index representations. The weighting factor  $w_{ij}$  represents the intersection of the  $j^{th}$  cell with the  $i^{th}$  ray, or the contribution of the  $j^{th}$  cell to the  $i^{th}$  ray sum. This geometry gives M equations in N unknowns:

$$\sum_{j=1}^{N} w_{ij} f_j = p_{i,} i = 1, 2, 3, \dots M$$

or

$$w_{11}f_1 + w_{12}f_2 + \dots w_{1N}f_N = p_1$$

$$w_{21}f_1 + w_{22}f_2 + \dots w_{2N}f_N = p_2$$

$$w_{M1}f_1 + w_{M2}f_2 + \dots + w_{MN}f_N = p_M$$

(1)

Gordon[13] points out some interesting features of equations (1), some of which must be noted if we are to optimize a solution process, i.e.:

- 1. The matrix  $\{w_{ij}\}$  is sparse, which will ease calculations.

- 2. The matrix  $\{w_{ii}\}$  can be huge.

- 3. Elements  $w_{ij}$ ,  $f_i$ ,  $p_i$  are always positive.

- 4. The data is often inconsistent. It can contain noise or errors.

Before we can begin developing the technique, we must determine how to best choose M and N in the computer's representation of the problem. M and N are dependent on the size of the projection elements and the desired resolution of the reconstructed image. The fineness of the discrete projection elements is limited by the resolution of the measured projection data, which depends on the physics of the radiation and measurement devices used. If we wish to get the maximum possible resolution in the reconstructed image with the minimum of calculations, we want the projection elements to be as large as possible without degrading the reconstructed image. Typically the projection element spacing is chosen to be half of the presumed resolution to fulfill the Nyquist criteria. A coarser choice for projection element width is limited only by the desired degree of resolution in the reconstructed image. One may want the division of R to be as fine as possible, but finer elements in the division of R(or in the projection elements) will increase calculations. One the other hand, the coarseness of the division of R is limited by the size of the projection elements. This is especially true when certain approximations to equations (1) are used; more will be said about the coarseness limitation on R after the approximations are developed in Section 1.1.3 on Gordon's appoximation.

#### 1.1.2 The Kaczmarz method

The Kaczmarz method is an iterative procedure that can be used to solve simulaneous equations. References [30] and [12] give excellent descriptions of the development and implementation of the algorithm. The approach taken here is similar to that in [30], with a few refinements.

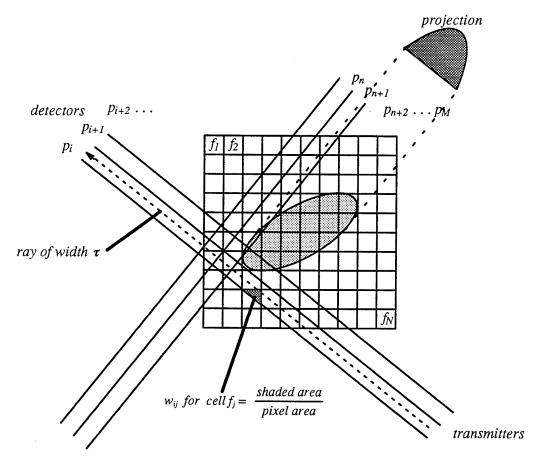

To begin, one must realize that the N unknown grid elements in equations (1) give an image N degrees of freedom. An image can therefore be represented as a single point in an N-dimensional space. Each individual equation in (1) would represent a hyperplane in such a space. If a unique solution exists, the intersection of these hyperplanes is a single point representing the solution. The Kaczmarz method uses successive projections of a proposed solution onto adjacent hyperplanes to iterate closer and closer to the solution. This is best illustrated by a simple 2 variable example with unknowns  $f_1$  and  $f_2$ , written:

$$w_{11}f_1 + w_{12}f_2 = p_1, \ w_{21}f_1 + w_{22}f_2 = p_2 \tag{2}$$

Figure 2 gives a conceptual view of how the iteration process evolves. It can be shown via vector analysis (see [30]) that an iterative equation for a projection from the  $(j-1)^{th}$  to the  $j^{th}$  hypeplane can be written

$$\vec{f}^{(j)} = \vec{f}^{(j-1)} - \frac{\vec{w}_j \cdot \vec{f}^{(j-1)} - p_j}{\vec{w}_j \cdot \vec{w}_j} \vec{w}_j$$

(3)

where

$$\vec{f} = \{f_1 f_2, \dots f_N\},\,$$

$$\vec{w}_j = \{w_{j1}, w_{j2}, \dots w_{jN}\},\,$$

and j ranges from 1 to M. We will forgo the derivation. Equation (3) will iteratively move the initial estimate  $\vec{f}^{(0)}$  towards the solution at the intersection of the hyperplanes. After a complete pass thru all M projections the process can be repeated starting from the first pro-

FIGURE 2 The Kaczmarz method of solving algebraic equations for 2 unknowns. From the initial guess, perpendicular projections onto adjacent hyperplanes (lines for the 2–d case) for each equation iterate closer and closer to the solution.[30]

jection using the new estimate of the solution  $\vec{f}^{(M)}$ , then again starting with  $\vec{f}^{(2M)}$ ,  $\vec{f}^{(3M)}$ , . . .  $\vec{f}^{(kM)}$  where k can be at convergence or as large as required to get the desired results.

But does the process converge? It is obvious for the 2-d example but not for systems with many more equations. Tanabe[34] has proved for the general case of equation (3) that if a unique solution to (1) exists,

$$\lim_{k \to \infty} \vec{f}^{(kM)} = \vec{f}_{s} \tag{4}$$

This is true if equations (1) are overdetermined and consistent, i.e. M>N with no noise or distortions in the data. If they underdetermined, then (3) will converge to a solution (one of the many possible solutions) that is closest to the initial estimate.

$$\lim_{n \to \infty} \vec{f}^{(kM)} = \vec{f}_{s}' \quad \text{such that } |\vec{f}^{(0)} - \vec{f}_{s}'| \quad \text{is minimized}$$

(5)

If the data in equations (1) is noisy or distorted, then (3) will oscillate in the neighborhood of the actual solution. This attribute makes the Kaczmarz method somewhat, but not completely, noise tolerant.

## 1.1.3 Gordon's Approximation

Equation (3), being iterative, is reasonably easy to implement in a computer program. However, the storage of and floating point calculations on what could be an enormous number of weights  $w_{ij}$  makes it cumbersome for digital computers. For example, for a 16 projection 64x64, the size of the  $w_{ij}$  matrix would be:

$$(64x64) \times (16x128) = 4096 \times 2048 = 4.2 \times 10^6 \text{ elements}$$

(6)

Even a small image with a limited number of projections is too big for matrix inversion methods. About 1/100 of these elements will be non-zero, which still leaves a large amount of numbers considering the many floating point calculations that must be performed.

Many methods to overcome these difficulties have been proposed; one efficient method is Gordon's approximation, which drastically reduces the number of non-zero weights and eliminates much floating point calculation and storage. The approach is simply that the weight is assigned a one if the centroid of the grid element is within the ray and a zero if it is not. Using this approximation, we can develop a form of (3) that can be run more easily and faster on a digital computer. Applying the approximation and again forgoing the details of the derivation, we arrive at the simple and intuitive equation below for the update of the  $m^{th}$  cell from the  $j^{th}$  ray sum.

$$\Delta f_m^{(j)} = \frac{p_j - q_j}{N_j} \tag{7}$$

where

$p_j$  is the measured projection for a ray,

$$q_j = \sum_{k=1}^{N} f_k^{(j-1)} w_{jk}$$

is the calculated projection, and

$$N_j = \sum_{k=1}^{N} w_{jk}^2$$

is the number of pixels in the ray.

Recall that the weight  $w_{jk}$  or  $w_{jm}$  will be 1 if the cell centroid is in the ray and zero elsewhere if we apply Gordon's approximation. One iteration for the  $m^{th}$  cell would be

$$f_m^{(j)} = f_m^{(j-1)} + \Delta f_m^{(j)} \tag{8}$$

Equations (7) and (8) were the equations implemented in our simulations, with some of the enhancements forthcoming. An intuitive interpretation of them is that the average error for each pixel in a ray is calculated by taking the difference between the measured and calculated pseudo projections and dividing by the number of pixels in the ray. This 'average error' is then backprojected to each pixel in the ray. We will dub this implementation of the Kaczmarz method combined with Gordon's approximation as ART, for Algebraic Reconstruction Technique. This solution has been shown to be a good approximation [30] to the constrained least squares approach.

For our application, an improvement to ART would be to use a priori knowledge about the image to speed convergence. For example, we know that the image intensities are greater than zero so we can apply that to the  $f_m^{(j)}$  's before proceeding to the next iteration.

<sup>1.</sup> Now that equations (7) and (8) and Gordon's approximation have been developed, it is more appropriate to discuss the limits in coarseness on the representation of space. If a calculated ray sum is to provide any representation of the image, number of cell centroid  $N_j$  must be non-zero. This limits the coarseness of the grid. Further restrictions on coarseness are required to provide an accurate representation of the density along the ray. The centroids should be evenly distributed along the ray's length. Gordon has estimated that this requirement will be sufficiently met if  $N_j > n^{1/d}$  for rays that are about the diameter of R, for a grid on n elements in d-dimensional space. Here  $n^{1/d}$  is the average ray length in units the same size as the cell width. A grid element size of no greater than the width of the projection elements will guarantee this condition. For this reason, we chose the pixel width equal to the ray width.

We can do the same thing with the upper limit. This has been dubbed *fully constrained* ART by Gordon.

$$f_{m}^{(j)} = min[MAXPIX, max[0, f_{m}^{(j-1)} + \Delta f_{m}^{(j)}]$$

(9)

For the purposes of this paper we will call the algorithm described thus far ART, although the term can have generic connotations in the literature. This form of ART is the most basic in a family of ART algorithms.

#### 1.1.4 Initialization Value

Since the Kaczmarz/ART method will converge to the solution closest to  $f^{(0)}$  for underdetermined equations, the starting value should be a best guess of the solution. The better a starting value chosen, the faster the algorithm will converge and the smaller unwanted artifacts will be. The mean density of f is one possibility, which is approximately

$$f_{kmean} = \frac{\sum p_j \text{ such that } p_j \text{ belongs to a single projection}}{\text{area of } \mathbf{R} \text{ normalized to } p_j \text{ widths}}$$

(10)

or even better

$$f_{mean} = \frac{1}{K} \sum_{k=1}^{K} f_{kmean} \tag{11}$$

where K is the number of projections. A *projection* is the set of ray sums taken over one discrete projection angle. These equations are true since the parallel rays fully partition the scanned space.

Usually the initial value is chosen as zero since the result after iterating through the first projection is roughly the same as  $f_{mean}$ . Another alternative is to use a SBP (Simple Back Projection) result as an initialization value. The problem with this is that distortions intro-

duced by the initial estimate may be retained as ghosts. For these reasons, zero was chosen as the initialization value in our implementation.

#### 1.1.5 Convergence criteria

Gordon, Bender, and Herman[13] suggested 3 possible measures for convergence.

1. The difference between the measured and calculated projection values: (goes to zero)

$$D^{(t)} = \sqrt{\frac{1}{M} \sum_{i=1}^{M} \frac{(p_j - q_j^{(t)})^2}{N_j}}$$

(12)

where *t* is the iteration number.

2. The non–uniformity or variance: (goes to a minimum)

$$V^{(t)} = \sum_{i=1}^{N} (f_i^{(t)} - f_{mean})^2$$

(13)

3. The entropy: (goes to a minimum)

$$S^{(t)} = \frac{-1}{\ln N} \sum_{i=1}^{N} \frac{f_i^{(t)}}{f_{mean}} \ln \frac{f_i^{(t)}}{f_{mean}}$$

(14)

One could suggest that a form of method 1 would be the most efficient since most of these calculations must be done anyway. If noise is present there will be a problem with detecting convergence since the algorithm will oscillate near the solution. Thresholding must be used appropriately in the programming to watch for divergence and terminate execution at a satisfactory time. Another important measurement of convergence when an original test image  $f_i$  is used for simulations is the Euclidean distance:

$$\boldsymbol{\delta}^{(t)} = \sqrt{\frac{1}{N} \sum_{i=1}^{N} (f_i^{(t)} - f_i)^2}$$

(15)

The Euclidean distance from the original image is a measure of the degree of accuracy of the reconstruction.

In our programs, a minimum {maximum  $\Delta f$ } was chosen for a convergence criteria. This is a factor in calculating most of the above values, and is accurate enough for our purposes since only clean projection data was used. As an option, we can stop the simulation after a certain number of iterations and calculate the Euclidean distance to check the degree of convergence.

## 1.1.6 Variations

The ART technique developed so far has been shown to perform poorly when compared to Fourier techniques when the projection data is noisy and/or inconsistent. This is mainly because it only looks at one projection at a time before performing an iteration. A plethora of variations have been proposed to reduce the effects of bad projection data and to eliminate artifacts inherent in the algorithm.

To reduce artifacts from geometric distortions caused by the discrepancy between the actual ray integral and the centriod technique, Gilbert[11] replaced equation (7) with

$$\Delta f_m^{(j)} = \frac{p_j}{L_i} - \frac{q_j}{N_i} \tag{16}$$

where  $L_j$  is the length of the  $j^{th}$  ray through the reconstruction region, normalized to the cell width. Gordon et al. have applied similar modifications to ART.

Another modification proposed by Gilbert is SIRT, or Simultaneous Iterative Reconstruction Technique, which makes the algorithm more noise tolerant. In this technique, an iteration is performed using the data from all projections simultaneously rather than one by one. Only at the end of each complete pass through all projection elements for the K projection angles are cell values changed, by the average value of the K  $\Delta f$ 's belonging to a pixel. The SIRT variation will average out bad projections:

$$\Delta f_{m_{av}}^{(j=nK)} = \frac{\sum_{j=(n-1)K}^{nK} \Delta f_{m}^{(j)}}{K} \text{ where } n = 1, 2, 3....$$

(17)

$$f_{m}^{(nK)} = f_{m}^{((n-1)K)} + \Delta f_{m_{av}}^{(nK)}$$

(18)

With ART some pre-filtering of projection data must be done or modifications to the algorithm must be incorporated to enhance noise performance. The drawback with SIRT is that it would require more memory; with the improvements that have been made to ART, the performance of ART and SIRT would be comparable. In algorithm tests of Chapter 2, the PC simulations implement ART and the parallel transputer simulations implement a form of SIRT.

In [12] Gordon reviews numerous other improvements to the basic ART technique which include:

- 1. ART2, which uses an intermediate unconstrained estimator to calculate the next iteration in constrained ART. This speeds convergence.

- 2. ART3, which uses a preset error threshold that makes the iterative procedure more tolerant to noise and inconsistent data.

- 3. ART with a damping factor. This slows convergence but improves noise performance.

Some of these improvements must be applied if algebraic techniques are to compete with Fourier techniques, especially with real rather than simulated data. One must carefully select those to be implemented since they all have some computational cost. Although our simulations were done using the basic constrained ART algorithm and the SIRT modification, the architecture that we will propose can accommodate many of the aforementioned improvements since they can be performed by the host or a complementary chip set. The ASIC array

performs the ray summing and update, or projection and backprojection, portions of the algorithms. These are the most computationally intense parts of the algorithms.

## CHAPTER 2

## Array Architecture and Algorithm Simulations

Before committing to a hardware architecture, simulations were done with the sequential reconstruction algorithms and with a parallel implementation of an ART. The serial simulations were necessary to ensure that the ART or SIRT algorithms could out–perform the other techniques in reconstruction quality, to show the need for parallelization of the iterative algorithms, and to gain an understanding of the image reconstruction algorithms. Our results confirm the first two items. The parallel simulations were done on a transputer array to test a novel parallel version of the ART algorithm, including improvements and modifications such as SIRT, and to verify that the algorithms could be mapped onto our proposed array architecture. The proposed architecture and mapping will be discussed after the results of the sequential simulations are presented, followed by a description of the parallel simulation results at the end of the chapter.

## 2.1 SEQUENTIAL SIMULATIONS

For the sequential simulations, three reconstruction algorithms were programmed and tested using pseudo-projections generated artificially from a test image. They include:

1. Simple Back Projection (SBP). The ray sums for each projection angles are backprojected, summed, and scaled with no further correction. This is a very crude reconstruction technique.