#### Exploiting Parallelism of Irregular Problems and Performance Evaluation on Heterogeneous Multi-core Architectures

by

Meilian Xu

A thesis submitted to

The Faculty of Graduate Studies of

The University of Manitoba

in partial fulfillment of the requirements

of the degree of

Doctor of Philosophy

Department of Computer Science

The University of Manitoba

Winnipeg, Manitoba, Canada

May 2012

© Copyright by Meilian Xu, 2012

# Exploiting Parallelism of Irregular Problems and Performance Evaluation on Heterogeneous Multi-core Architectures

#### Abstract

In this thesis, we design, develop and implement parallel algorithms for irregular problems on heterogeneous multi-core architectures. Irregular problems exhibit random and unpredictable memory access patterns, poor spatial locality and input dependent control flow. Heterogeneous multi-core processors vary in: clock frequency, power dissipation, programming model (MIMD vs. SIMD), memory design and computing units, scalar versus vector units. The heterogeneity of the processors makes designing efficient parallel algorithms for irregular problems on heterogeneous multi-core processors challenging. Techniques of mapping tasks or data on traditional parallel computers can not be used as is on heterogeneous multi-core processors due to the varying hardware. In an attempt to understand the efficiency of futuristic heterogeneous multi-core architectures on applications we study several computation and bandwidth oriented irregular problems on one heterogeneous multi-core architecture, the IBM Cell Broadband Engine (Cell BE). The Cell BE consists of a general processor and eight specialized processors and addresses vector/data-level parallelism and instruction-level parallelism simultaneously. Through these studies on the Cell BE,

Abstract

we provide some discussions and insight on the performance of the applications on heterogeneous multi-core architectures.

Verifying these experimental results require some performance modeling. Due to the diversity of heterogeneous multi-core architectures, theoretical performance models used for homogeneous multi-core architectures do not provide accurate results. Therefore, in this thesis we propose an analytical performance prediction model that considers the multitude architectural features of heterogeneous multi-cores (such as DMA transfers, number of instructions and operations, the processor frequency and DMA bandwidth). We show that the execution time from our prediction model is comparable to the execution time of the experimental results for a complex medical imaging application.

#### List of Publications

- Meilian Xu, Parimala Thulasiraman and Sima Noghanian, "Microwave tomography for breast cancer detection on cell broadband engine processors", Elsevier, Journal of Parallel and Distributed Computing, Vol. 72, Issue 9, September 2012, Pages 1106-1116.

- Meilian Xu and Parimala Thulasiraman, "Mapping Iterative Medical Imaging Algorithm on Cell Accelerator", Hindawi Publishing Corporation, International Journal of Biomedical Imaging (Special Issue on Parallel Computation in Medical Imaging Applications), Volume 11, 2011, doi:10.1155/2011/843924.

- Cameron Melvin, Meilian Xu and Parimala Thulasiraman, "Preserving Image Quality with Reduced Radiation Dosage in Computed Tomography by Parallel Computing", Serials Publications, India, International Journal of Computer Science and System Analysis, Vol. 2, No. 2, pp. 121-131, July-Dec 2008.

- Meilian Xu, Parimala Thulasiraman and Ruppa K. Thulasiram, "Cell Processing for Two Scientific Computing Kernels", in Handbook of Research on Scalable Computing Technologies, IGI Global, (25 pages), 2009, Editors: Kuan-Ching Li, Ching-Hsien Hsu, Laurence Yang, Jack Dongarra and Hans Zima.

- Meilian Xu and Parimala Thulasiraman, Rotation based Algorithm for parallelizing OS-SART for CT on homogeneous multicore architecture, The 12th IASTED International Conference on Signal and Image Processing, Maui, Hawaii, 2010.

- Meilian Xu, Parimala Thulasiraman and Ruppa K. Thulasiram, Exploiting Data

Locality in FFT using Indirect Swap Network on Cell/B.E., High Performance Computing Symposium, Quebec City, QC, June 2008.

- Cameron Melvin, Meilian Xu and Parimala Thulasiraman, HPC for Iterative Image Reconstruction in CT, The ACM Canadian Conference on Computer Science and Software Engineering (C3S2E), Montreal, Quebec, May 2008.

- Meilian Xu and Parimala Thulasiraman, Finite-Difference Time-Domain on the Cell/B.E. Processor, The 9th IEEE International Workshop on Parallel and Distributed Scientific and Engineering Computing, Miami, US, April 2008.

- Meilian Xu, Abas Sabouni, Parimala Thulasiraman, Sima Naghonian, Stephen Pistorius, Image Reconstruction using microwave tomography for breast cancer detection on distributed memory machine, The 36th International Conference on Parallel Processing, Xian, China, September 10-14, 2007, pp. 36-43.

- Abas Sabouni, Meilian Xu, Sima Noghanian, Parimala, Thulasiraman, Stephen Pistorius, Efficient Microwave Breast Imaging Technique Using Parallel Finite Difference Time Domain and Parallel Genetic Algorithms, 2007 IEEE AP-S International Symposium on Antennas and Propagation in Honolulu, Hawaii, USA on June 10-15, 2007.

- Meilian Xu, Abas Sabouni, Parimala Thulasiraman, Sima Noghanian and Stephen Pistorius, A Parallel Algorithmic Approach to Microwave Tomography in Breast Cancer Detection, The 8th IEEE International Workshop on Parallel and Distributed Scientific and Engineering Computing, Long Beach, CA, March 26-30 2007.

### Acknowledgments

I would like to thank all the people who have helped and inspired me during my doctoral study and made this thesis possible.

Foremost, I would like to express my sincere gratitude to my supervisor Prof. Parimala Thulasiraman for the continuous support of my Ph.D. study and research, for her patience, inspiration, and enthusiasm. It has been an honor to be her first Ph.D. student. Her understanding, encouragement and personal guidance have provided a good basis for the thesis. I appreciate all her contributions of time and ideas to make my Ph.D. experience productive and stimulating. I am also thankful for the excellent example she has provided as a successful woman scientist and professor.

I would like to thank my committee members Prof. Sima Noghanian, Prof. Ben Pak Ching Li, Prof. Udaya D. Annakkage and Prof. Laurence T. Yang. I would like to thank Prof. Noghanian for introducing me to the microwave tomography project and for her valuable comments and ideas on related publications. I would also like to thank Prof. Li for his questions and comments from theoretic point of view, which brings about the proposed performance model in the thesis. I would like to express my thanks to Prof. Annakkage and Prof. Yang for spending time in reading the thesis and providing valuable comments.

I wish to thank Dr. Michel Toulouse for his continuous support during my graduate program at University of Manitoba. I wish to thank Prof. Ruppa (Tulsi) Thulasiram for his help on the research of FFT. I also want to thank Abas Sabouni for the collaboration and help on microwave tomography project. My warm thanks also go to Jonatan Aronsson and Gilbert Detillieux for their help on simulation environments. I would also like to thank Lynne Hermiston for her help on administrative Acknowledgments vii

issues during the long journey.

My deepest gratitude goes to my family for their unflagging love and support throughout my life. This thesis is simply impossible without them. I am indebted to my father Dezhi Xu for his support on my decision to go abroad and study. As a typical father in a Chinese family, he worked industriously to support the family and spare no effort to provide the best possible environment for me to grow up and attend school. Although he is no longer with us, he is forever remembered. I am sure he shares our joy and happiness in the heaven. I cannot ask for more from my mother Lanying Li for her everlasting love and understanding. I owe my loving thanks to my husband Zhihui Zhu and my lovely son Hongyuan Zhu. They have lost a lot due to my research abroad. Without their encouragement, patience and understanding it would have been impossible for me to finish this work. My parents-in-law deserve my sincere gratitude to help me take care of my son. I also want to thank my sisters and brothers-in-law to take care of my parents all the years I am abroad.

Without all the helps and support, the thesis is impossible!

This thesis is dedicated to my parents Dezhi Xu and Lanying Li who taught me the joy and power of reading from childhood, enabling such a study to take place today.

# Contents

|   | Abst | ${ m cract}$                                 |

|---|------|----------------------------------------------|

|   |      | of Publications                              |

|   |      | nowledgments                                 |

|   |      | ication                                      |

|   |      | e of Contents                                |

|   |      | of Tables                                    |

|   |      | of Figures xii                               |

| 1 | Intr | oduction 1                                   |

|   | 1.1  | Motivation and Goal of the thesis            |

|   |      | 1.1.1 Finite Difference Time Domain          |

|   |      | 1.1.2 Fast Fourier Transform                 |

|   |      | 1.1.3 Iterative CT Reconstruction Techniques |

|   |      | 1.1.4 Microwave Tomography                   |

|   | 1.2  | Contributions                                |

|   | 1.3  | Organization of the thesis                   |

| 2 | Par  | allel Architectures and Cell BE              |

|   | 2.1  | Parallel Architectures                       |

|   | 2.2  | Cell BE Processor                            |

|   | 2.3  | Applications on Cell BE Processor            |

|   | 2.4  | Summary                                      |

| 3 | Fini | te Difference Time Domain 45                 |

|   | 3.1  | Introduction                                 |

|   | 3.2  | FDTD on Distributed-Memory Machines          |

|   | 3.3  | FDTD on homogeneous Multi-core Architecture  |

|   | 3.4  | FDTD on Cell BE Processor                    |

|   | 3.5  | Experiment Results                           |

|   | 3.6  | Summary                                      |

Contents

| 4  | Fast                 | Fourier Transform                                | 73         |  |  |

|----|----------------------|--------------------------------------------------|------------|--|--|

|    | 4.1                  | Introduction                                     | 74         |  |  |

|    | 4.2                  | Cooley-Tukey Butterfly Network and ISN           | 76         |  |  |

|    | 4.3                  | Parallel FFT Based on ISN on Cell BE             | 80         |  |  |

|    | 4.4                  | Experiment Results                               | 84         |  |  |

|    | 4.5                  | Summary                                          | 88         |  |  |

| 5  | Iter                 | ative CT Reconstruction Technique                | 92         |  |  |

|    | 5.1                  | Introduction                                     | 93         |  |  |

|    | 5.2                  | Iterative Reconstruction Techniques              | 98         |  |  |

|    | 5.3                  | Parallel Computing for Reconstruction Techniques | 105        |  |  |

|    | 5.4                  | OS-SART                                          | 109        |  |  |

|    | 5.5                  | OS-SART on Cell BE                               | 113        |  |  |

|    | 5.6                  | Experiment Results                               | 117        |  |  |

|    | 5.7                  | Summary                                          | 126        |  |  |

| 6  | Microwave Tomography |                                                  |            |  |  |

|    | 6.1                  | Introduction                                     | 128<br>129 |  |  |

|    | 6.2                  | Microwave Tomography                             | 133        |  |  |

|    | 0.2                  | 6.2.1 FDTD for MT                                | 137        |  |  |

|    |                      | 6.2.2 GA for MT                                  | 139        |  |  |

|    | 6.3                  | Microwave Tomography on Cell BE                  | 141        |  |  |

|    | 0.0                  | 6.3.1 FDTD on SPEs                               | 141        |  |  |

|    |                      | 6.3.2 Coordination between PPE and SPEs          | 146        |  |  |

|    | 6.4                  | Experiment Results                               | 140 $147$  |  |  |

|    | 6.5                  | Summary                                          | 151        |  |  |

| 7  | Per                  | formance Prediction Model                        | 153        |  |  |

| •  | 7.1                  | Performance Prediction for FDTD                  | 153        |  |  |

|    | $7.1 \\ 7.2$         | Summary                                          | 159        |  |  |

| 0  |                      |                                                  |            |  |  |

| 8  | Con                  | aclusions                                        | 161        |  |  |

| Bi | bliog                | rraphy                                           | 185        |  |  |

# List of Tables

| 1.1 | Characteristics Comparison between four problems                      | 12  |

|-----|-----------------------------------------------------------------------|-----|

| 5.1 | Execution time for different combinations of subset number and itera- |     |

|     | tion number                                                           | 120 |

# List of Figures

| 2.1  | SMP architecture                                                           | 17 |

|------|----------------------------------------------------------------------------|----|

| 2.2  | nonuniform memory access (NUMA) architecture                               | 18 |

| 2.3  | distributed memory architecture                                            | 19 |

| 2.4  | MIMD division                                                              | 20 |

| 2.5  | Gap between required performance and delivered performance. (Banton, 2008) | 21 |

| 2.6  | ton, 2008)                                                                 | 21 |

| 2.0  | via accelerator. (Banton, 2008)                                            | 22 |

| 2.7  | Cell Broadband Engine Processor Block Diagram                              | 25 |

| 2.8  | EIB data flow illustration. (Kistler et al., 2006)                         | 28 |

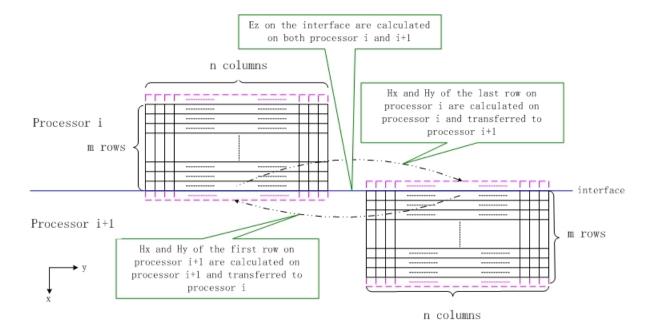

| 3.1  | Communication Scheme in Parallel FDTD                                      | 52 |

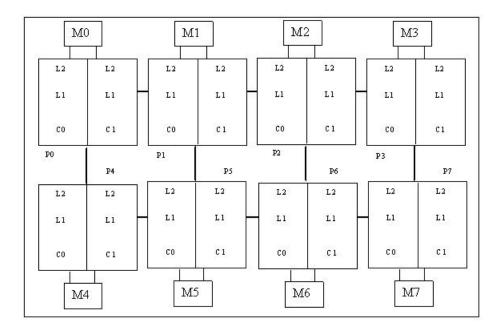

| 3.2  | Simplified block diagram of Sun Fire X4600 server                          | 54 |

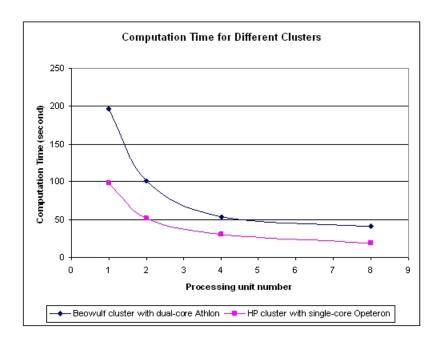

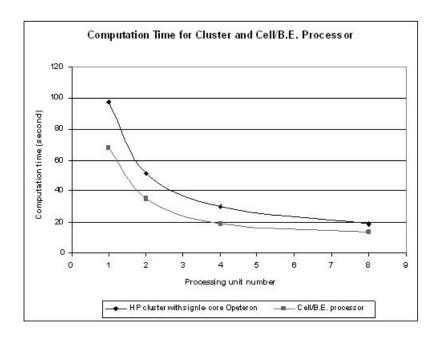

| 3.3  | Computation Time for Different Clusters                                    | 62 |

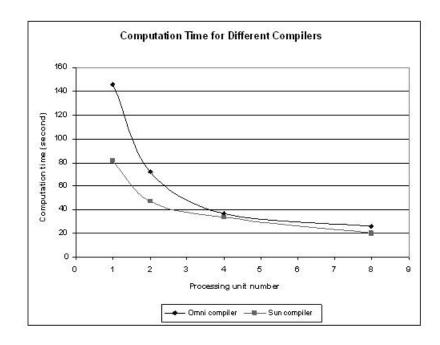

| 3.4  | Computation Time for Different Compilers                                   | 63 |

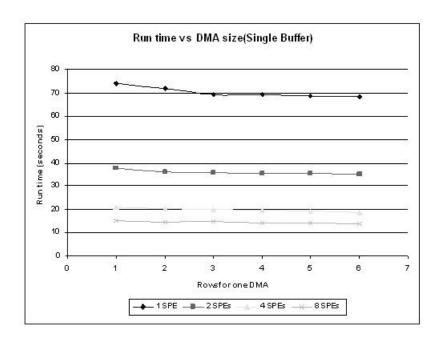

| 3.5  | Computation Time for Different DMA Size                                    | 64 |

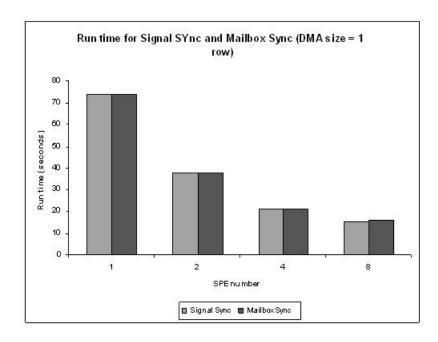

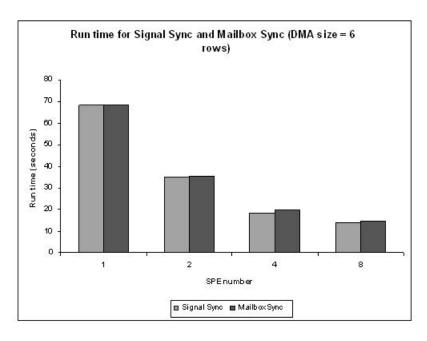

| 3.6  | Performance comparison between two synchronization mechanisms              | 65 |

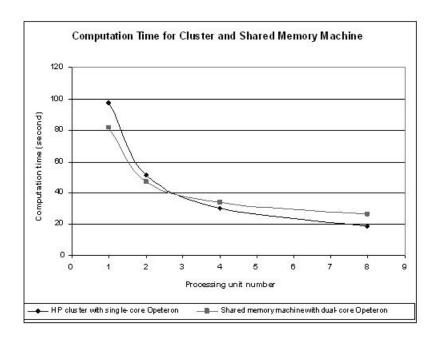

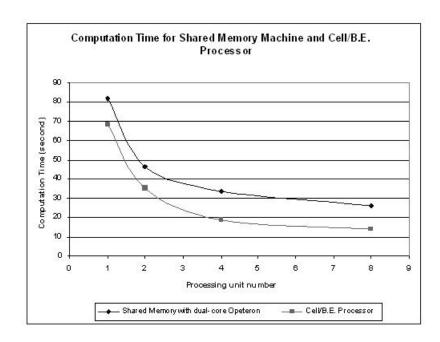

| 3.7  | Computation Time Comparison between Shared Memory Machine and              |    |

|      | Cluster                                                                    | 67 |

| 3.8  | Computation Time Comparison between Cell BE Processor and Cluster          | 68 |

| 3.9  | Computation Time Comparison between Cell BE Processor and Shared           |    |

|      | Memory Machine                                                             | 69 |

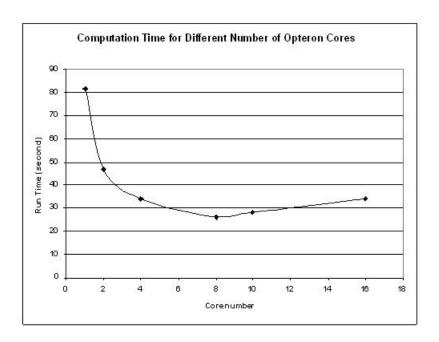

| 3.10 | Computation Time for Different AMD Cores                                   | 70 |

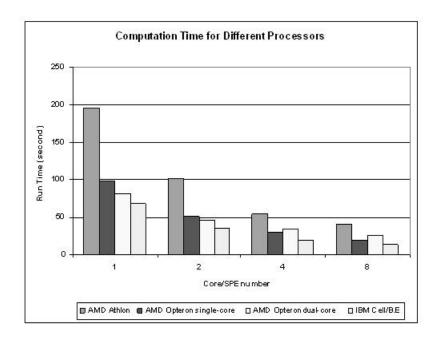

| 3.11 | Computation Time for Different Processors                                  | 71 |

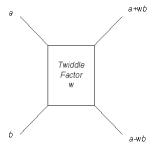

| 4.1  | Butterfly computation                                                      | 76 |

| 4.2  | Cooley-Tukey butterfly network with bit-reversed input and ordered         |    |

|      | output (Grama et al., 2003)                                                | 78 |

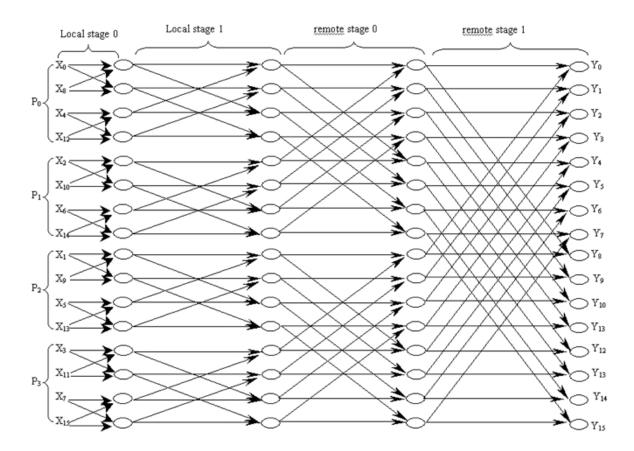

| 4.3  | Indirect swap network with bit-reversed input and scrambled output.        | 79 |

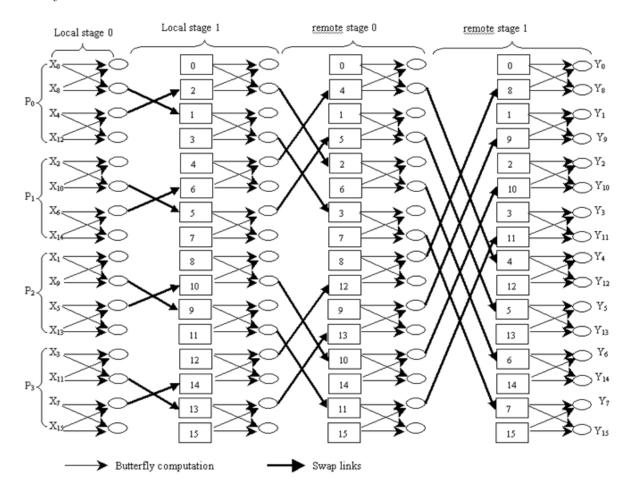

| 4.4  | Data migration between main memory and SPEs on Cell BE                     | 83 |

List of Figures xiii

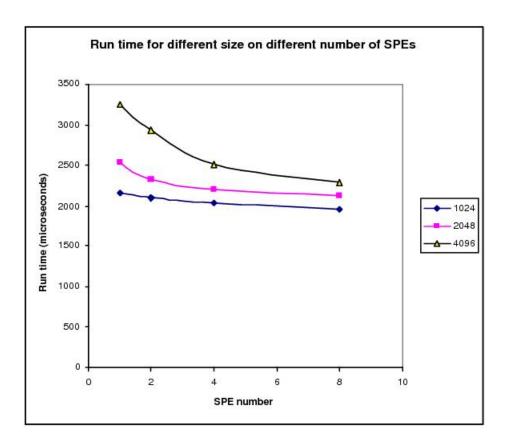

| 4.5  | Computation time and speedup for different problem size on different number of SPEs       | 85       |

|------|-------------------------------------------------------------------------------------------|----------|

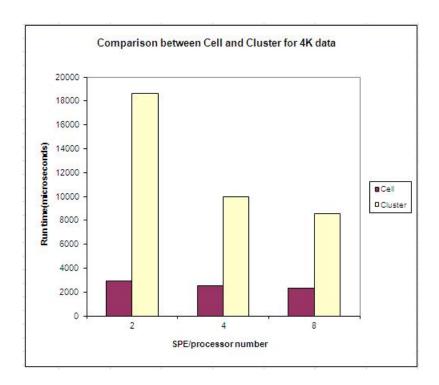

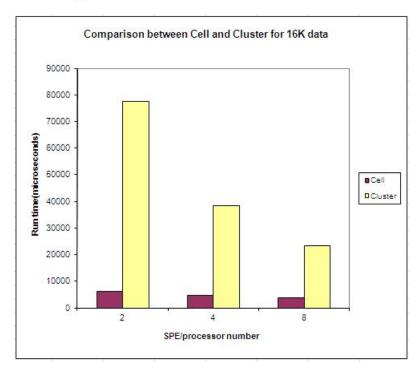

| 4.6  | Comparison between Cell BE and cluster for 4K and 16K complex numbers                     | 87       |

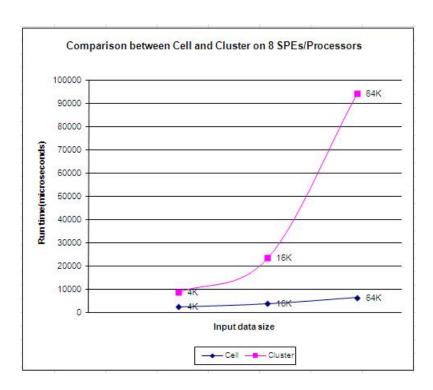

| 4.7  | Comparison between Cell BE and cluster for different input data size on 8 SPEs/processors | 88       |

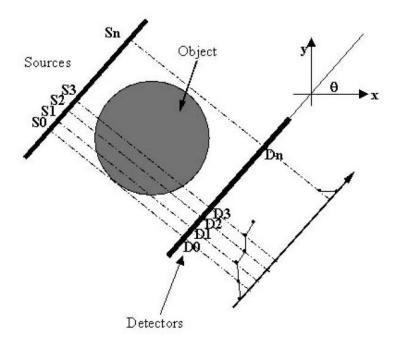

| 5.1  | Schematic diagram of X-ray projection acquisition (Herman, 1980)                          | 95       |

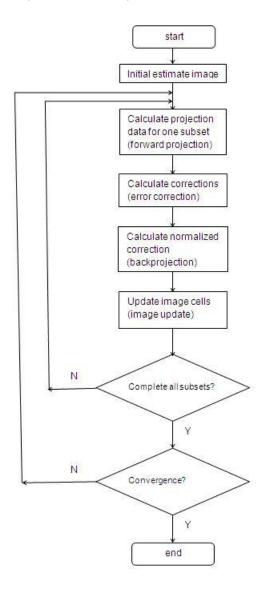

| 5.2  | Framework of Iterative Reconstruction Techniques                                          | 99       |

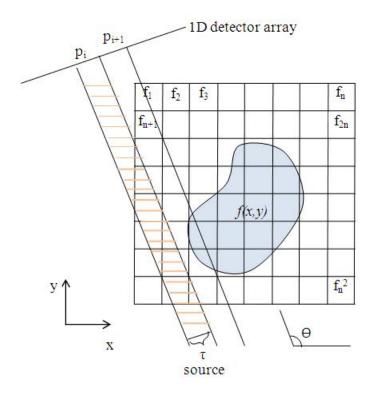

| 5.3  | Illustration of Iterative Methods                                                         | 100      |

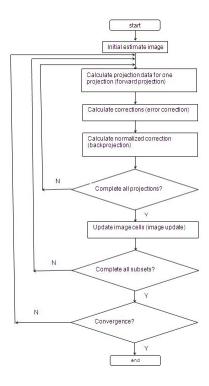

| 5.4  | Framework of OS-SART Reconstruction Technique                                             | 111      |

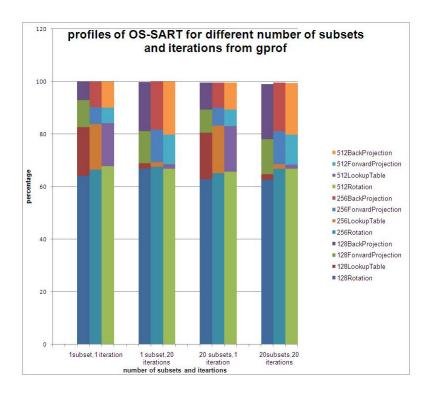

| 5.5  | Profile Results of OS-SART                                                                | 115      |

| 5.6  | Computation time vs Number of subsets on AMD. The curve shows                             | 440      |

|      | the time for different number of subsets for one iteration                                | 119      |

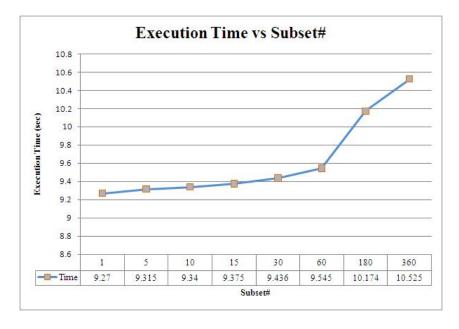

| 5.7  | Computation time vs Number of subsets on AMD and Cell BE. The                             | 101      |

| E 0  | curve shows the time for different number of subsets for one iteration.                   | 121      |

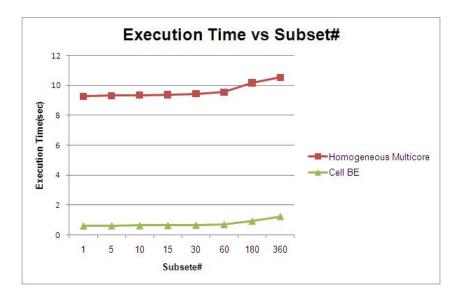

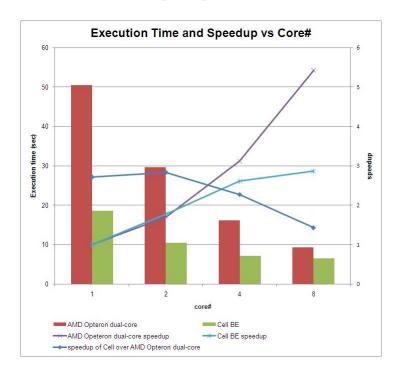

| 5.8  | Computation time and speedup vs number of SPEs/cores for 20 subsets and 10 iterations     | 123      |

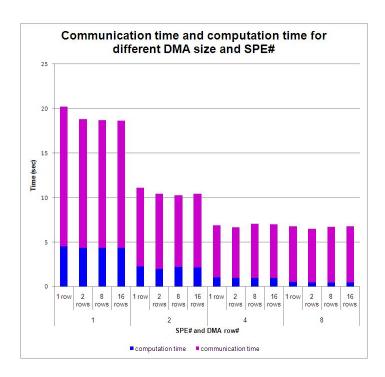

| 5.9  | Computation time and communication time vs number of SPEs and                             | 120      |

| 0.5  | number of image rows per DMA transfer for 20 subsets and 10 iterations                    | s. 124   |

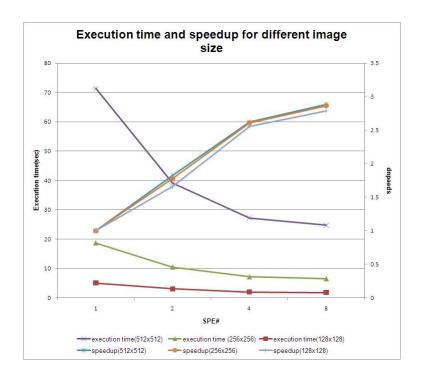

| 5.10 | Computation time and speedup vs number of SPEs for different image                        | J. 1 = 1 |

| 0.20 | sizes using 20 subsets and 10 iterations.                                                 | 125      |

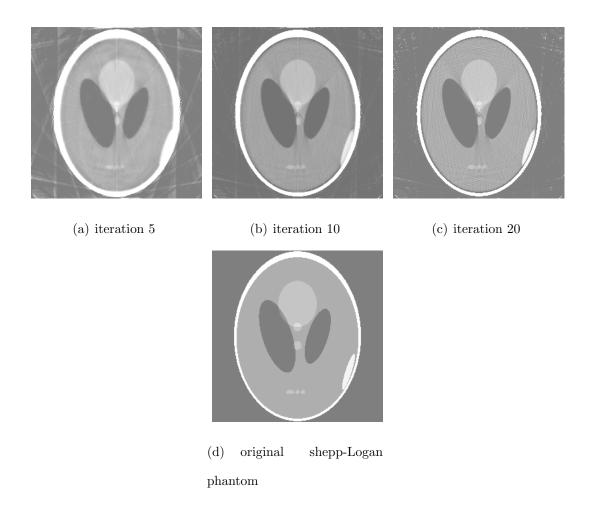

| 5.11 | Reconstructed images at different iterations for 20 subsets                               | 126      |

|      |                                                                                           |          |

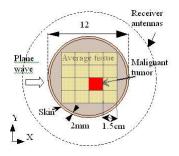

| 6.1  | Microwave Tomography Illustration                                                         | 135      |

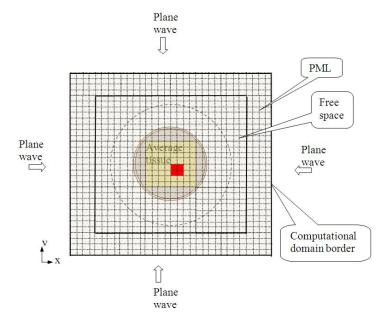

| 6.2  | Simulation Settings (Xu et al., 2007a)                                                    | 136      |

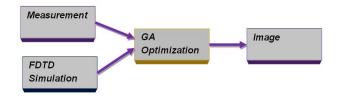

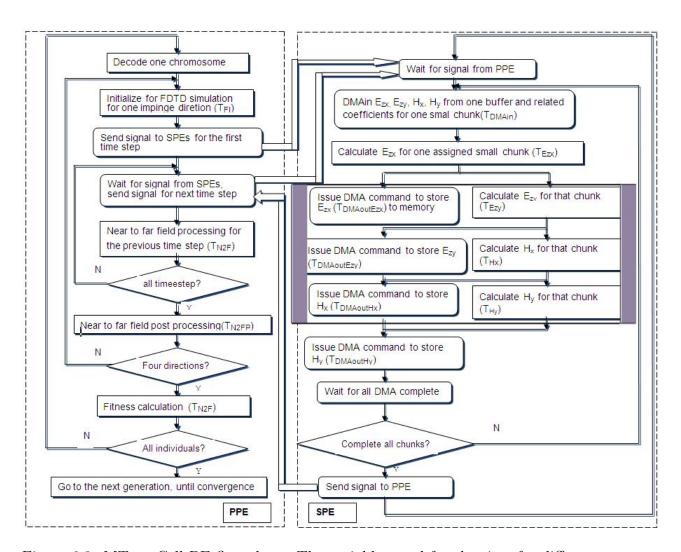

| 6.3  | MT on Cell BE flow chart. The variables used for the time for different part are included | 143      |

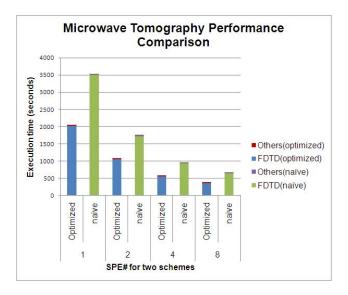

| 6.4  | Comparison between two mapping schemes for FDTD. The straightfor-                         | 140      |

| 0.1  | ward mapping is the one without overlapping computation with com-                         |          |

|      | munication, while the optimized mapping is the one with the overlap-                      |          |

|      | ping technique.                                                                           | 149      |

| 6.5  | Performance comparison between two versions of MT, which integrate                        |          |

|      | GA and with two different FDTD simulation                                                 | 150      |

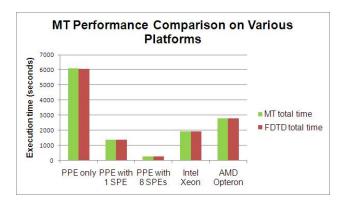

| 6.6  | Performance comparison of MT on different platforms                                       | 152      |

| 7.1  | Analysis results vs experiment results of FDTD simulation. The legend                     |          |

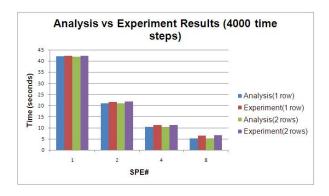

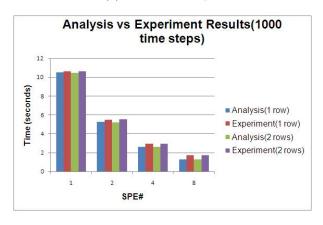

| 1.1  | of 1 row means 1 row for each DMA transfer.                                               | 159      |

# Chapter 1

# Introduction

A parallel machine is made up of many independent processors. Clusters and NOWs (network of workstations) which paved the way in parallel processing are still considered to be cost effective, scalable, easy to program and could be built using off-the-shelf RISC processors. High performance computing (HPC) clusters provide increased performance by splitting the computational tasks among the nodes in the cluster and have been commonly used to study data-intensive and computation-intensive applications. These clusters are cost effective, scalable and run standard software libraries such as MPI which are specifically designed to develop scientific application programs on HPC. They are also comparable in performance and availability to supercomputers (Bader and Pennington, 2001). A typical example is the Beowulf cluster which uses commercial off-the-shelf computers to produce a cost-effective alternative to a traditional supercomputer. Many of the fastest computers or supercomputers in the top500.org list are clusters. One of the crucial issues in clusters is the communication bandwidth. High speed interconnection networks such as

Infiniband have paved the way for increased performance gain in clusters (Pentakalos, 2002).

However, the development trend in clusters has been greatly influenced by hardware constraints leading to three brick walls (Asanovic et al., 2009). According to Moore's law, the number of transistors on the chip will double approximately every 18 months (Moore, 1965). However, the speed of processor clocks has not kept up with the increased transistor design (known as Moore's Gap) (Sutter and Larus, 2005). This is due to the physical constraints imposed on clock speed increase. For example, too much heat dissipation leads to complicated cooling techniques to prevent the hardware from deteriorating. And, too much power consumption daunts the customers from adopting new hardware, increasing the cost of commodity applications. Power consumption doubles with the doubling of operating frequency leading to the first of the three walls, known as the power wall. On the other hand, even with the increased processor frequency achieved so far, the system performance has not improved significantly in comparison to the increased clock speeds. In many applications, the data size operated on by each processor changes dynamically, which in turn, affects the computational requirements of the problem leading to communication/synchronization latencies and load imbalance. Multithreading is one way of tolerating latencies. However, previous research (Thulasiram and P.Thulasiraman, 2003; Thulasiraman et al., 2004) has indicated that though multithreading solves the latency problem to some extent by keeping all processors busy exploiting parallelism in an application, it has not been enough. Accessing data in such applications greatly affects memory access efficiency due to the non-uniform memory access patterns that

are unknown until runtime. In addition, the gap between the processor speed and the memory speed is widening as the processor speed increases more rapidly than the memory speed leading to the second wall, memory wall (Wulf and Mckee, 1995). To solve this problem, many memory levels are incorporated which requires exotic management strategies. However, the time and effort required to extract the full benefits of these features detracts from the effort exerted on real coding and optimization. Furthermore, it has become a very difficult task for algorithm designers to fully exploit instruction level parallelism (ILP) to utilize the processor resources effectively to keep the processors busy. Solutions to this problem have been in using deep pipelines with out-of-order execution. However, this approach impacts the performance of the algorithm due to the high penalty paid on wrong branch predictions. This leads to the third wall, ILP wall. These three walls force architecture designers to develop solutions that can sustain the requirements imposed by applications and provide solutions to some of the problems imposed by hardware in traditional multiprocessors.

A multi-core architecture is one of the solutions to tackle the three walls. This architecture is driven by the need for decreased power consumption, increased operations/watt and Moore's Gap. A multi-core architecture consists of a multi-core processor, which is also called a chip-level multiprocessor (CMP). A multi-core processor combines two or more (less than ten) independent cores on a single die. Some cores on the same processor die run at a comparatively lower clock speed which decreases heat. The heat dissipation of the die will improve since workloads can be balanced across various cores to evenly distribute the generated heat. Industry ven-

dors such as Intel, AMD, IBM and Sun Microsystems have designed homogeneous multi-core or many-core (with tens, hundreds, or even thousand of cores on a single die) processor chips where all the cores are exactly the same and have the same instruction set. A multi-core architecture is a new architecture and cannot be regarded as a new SMP (Symmetric MultiProcessor) architecture since all cores in this architecture share on-chip resources whereas separate processors in the conventional SMP do not (Dongarra et al., 2007). For example, each core of an AMD Opteron dual-core processor has its own L2 cache, but the two cores still share other interconnect to the rest of the system such as the memory controller. These dual-core processors belong to homogeneous multi-core processors because the resources and execution units (or cores) are mere replications of each other. The number of cores on a single die is still growing. Quad-Core Intel Xeon processor and Quad-Core AMD Opteron processor are already available. Cyclops64 has as many as 64 homogeneous cores on a single chip (Denneau and Warren, 2005), which is usually known as a many-core architecture. Homogeneous multi-core architectures increase parallelism and provide performance improvement for many real-time, data-intensive applications. They provide thread-level parallelism and can support OpenMP and MPI (Message Passing Interface) standard programming languages. Therefore, existing parallel algorithms implemented using OpenMP or MPI can be ported onto these machines with little difficulty. In general, homogeneous multi-core systems do not require much, if any, code modification to make existing software work. Code for these systems often requires refinement and tweaking when performance is not as expected. However, as the number of cores per chip increases, so does the power consumption and heat dissipation generated from these cores. This leads to higher costs for thermal packaging, fans, electricity, and even air conditioning. There is a greater chance of failures due to higher-power systems.

Although homogeneous multi-core processors have become mainstream, heterogeneous multi-core architectures have gained their recognition and popularity gradually due to their unique features for HPC. The concept of heterogeneous multi-core computing is not new. It has existed since the mid-80's where a problem's workload is split between a general-purpose processor and one or more specialized, problem-specific processors. Notable examples include Floating Point Systems' array processors, the Inmos "Transpute" and the Connection Machine (Eatherton, 2005). Today we have such heterogeneous multi-core computing in hardware designs such as GPU (Graphics Processing Unit) and recent GPGPU (General Purpose GPU), FPGA (Field Programmable Gate Array), and network processors (Cisco's 188 Reduced Instruction Set Computer (RISC) cores on a single chip in a 130nm process). Heterogeneous multi-core architectures such as IBM Cell Broadband Engine (Cell BE) (Kahle et al., 2005), or multi-core system with GPUs (Graphic Processing Units) or any hardware specialized accelerators have a better performance/power ratio. Due to their heterogeneity, these architectures support diverse applications. However, programming these architectures is very difficult. The conventional high level programming languages for the conventional single-core systems encapsulate the underlying hardware from software programmers. On the contrary, the heterogeneity of cores on heterogeneous systems indicates different architectures and instruction sets on different kinds of cores on the same system. These architectures provide a concrete programming paradigm which exposes the programmers to much of the underlying hardware for optimal performance. For example, CUDA is the language used for Nvidia's GPG-PUs<sup>1</sup>. Programmers have to use CUDA to manipulate the memory on GPGPUs. The Cell BE processor has one conventional microprocessor, Power Processor Element (PPE), and eight SIMD (Single Instruction Multiple Data) co-processing elements called Synergistic Processor Elements(SPEs). PPE and SPEs use different Instruction Set Architecture (ISAs). With the recent introduction to OpenCL, some of the problems pertaining to the portability of the algorithms on heterogeneous multicore architectures would be resolved.

#### 1.1 Motivation and Goal of the thesis

High performance computing is moving towards exascale computing. Heterogeneous parallel machines with accelerators such as Graphical Processing Units (GPU) and the recent architecture (at the time of this writing, AMD Accelerated Processing Unit(APU)) have demonstrated their capabilities beyond graphics rendering or general purpose computing and are proved to be well suited for data intensive applications. However, heterogeneous multicore architectures pose new challenges. First, algorithms have to be redesigned to take advantage of the architecture. In addition, the programming models differ between vendors, lacking portability of algorithms across various heterogeneous platforms. Hopefully, with OpenCL, this problem can be resolved. With the future of general purpose computing moving towards heterogeneous multicore architectures, it is important to understand the behaviour of these

<sup>&</sup>lt;sup>1</sup>http://www.nvidia.com/object/cuda\_home\_new.html

architectures on high performance computing applications.

As a stepping stone to understand the applications that can be studied on these machines, we have designed, developed and implemented several computation and bandwidth oriented algorithms on on-chip accelerator, the Cell BE. Cell BE has features similar to modern general purpose heterogeneous multicore computers such as APU. Therefore, our algorithm design will remain intact without any modifications if the same algorithms were implemented on futuristic machines. Moreover, we develop a general performance prediction model for heterogeneous multicore architectures.

We focus on four different problems in this thesis. Some of these problems are kernels to medical imaging modalities which we feel will benefit from the sustained peak performance of Cell BE. We develop parallel algorithms for these problems and implement the algorithms on the Cell BE by fully utilizing the various features of the Cell BE. Through these studies on the Cell BE, we provide some discussions on the performance of such applications on heterogeneous multicore architectures in general and provide some insight into the performance of these applications.

The problems considered have different characteristics and features. The complexity of the algorithm design and implementation increases for each of these problems. They range from regular to irregular problems, synchronous to asynchronous computations, static to dynamic execution and structured or unstructured problem domain. An irregular problem has irregular memory access pattern. Unstructured problems cannot be represented by a regular data structure such as an array. In a dynamic problem, communication pattern changes over time, data size increases or decreases, and load imbalance may result. An asynchronous problem has its own challenges

especially in termination detection.

#### 1.1.1 Finite Difference Time Domain

Finite Difference Time Domain (FDTD) is a popular simulation method and a regular scientific computing problem which is a kernel to many applications such as Electromagnetic theory in (Taflove and Hagness, 2000) and medical imaging (Xu et al., 2007a; Xu and Thulasiraman, 2008a).

FDTD is an inherently data-intensive and computation-intensive algorithm which exhibits nearest neighbor communication patterns categorizing it as a regular problem. Since it is usually a kernel in many applications, its performance is crucially important to the overall performance of the entire application. The field updates in FDTD are stencil updates which consist of a discrete set of cells and a computational kernel that is invoked for each cell to calculate the new cell values. This characteristic of FDTD makes it a data intensive problem.

Although there exist many FDTD algorithms designed for different conventional parallel architectures, the performance of those parallel FDTD is still an issue to the underlying applications. The Cell BE exhibits several levels of parallelism at the architecture and hardware level, which may be suitable for data intensive problems such as FDTD. Therefore, in this thesis we investigate and design parallel FDTD for Cell BE. For the purpose of comparison, we also design parallel FDTD on conventional distributed memory machines and shared memory machines.

We propose to incorporate the GA together with the FDTD and implement the algorithm on the Cell BE. We will study the Cell BE's intrinsic features for this im-

portant application and provide a comprehensive analysis of the performance results.

#### 1.1.2 Fast Fourier Transform

The Fast Fourier Transform (FFT) algorithm is a well-known kernel in many applications such as computed tomography (CT) and option pricing in finance. The Fourier back projection (based on FFT) algorithm is commonly used in CT (Herman, 1980). The FFT is a data intensive, semi-regular problem. The algorithm follows a butterfly computation with regular synchronization and communication at each level of the iteration. The communication patterns change at each iteration although it is very easy to determine the identification of the partners.

Iterative FFT algorithm has been intensively studied on distributed memory machines. Unlike the fixed nearest-neighbor communication inherent in FDTD algorithm, the FFT exhibits dynamic communication patterns, which makes it a semi-irregular algorithm since the communication patterns can only be decided at run time. The changing patterns incur two main latency issues for FFT on distributed memory machines: communication and synchronization.

These two latencies can be tolerated or hidden by either multithreading technique or data locality improvement technique. The former technique tries to overlap computation with communication, while the latter tries to map data in a way such that the number of communication can be reduced. Simultaneous multithreading (SMT) with large number of threads (over hundreds or thousands) is not supported in the hardware of Cell BE. Therefore, we reduce the communication latency by using an indirect swap network (Yeh and Parhami, 1996) instead of the traditional Cooley-

Tukey butterfly network to compute FFT (Cooley and Tukey, 1965). We design an iterative FFT algorithm on Cell BE by partitioning the swap network and mapping the sub-network to the Cell processors.

#### 1.1.3 Iterative CT Reconstruction Techniques

X-ray computed tomography (CT) is an imaging modality which reconstructs an image from projection data (Herman, 1980). With acquired data through CT scanners, CT can reconstruct images using either analytical methods (also known as transform-based methods) or iterative methods. Analytical methods are faster than iterative methods for the same amount of projection data. However, the problem with analytical methods is that they need larger number of projections than iterative methods, which exposes patients to large dosage of X-ray radiation. Although iterative methods are safer, they are computationally intensive requiring long processing time. Furthermore, they are also communication intensive and provide lots of asynchronicity.

We have developed two parallel algorithms on distributed memory machines and shared memory machines, with little improvement in performance (Melvin et al., 2008a,b). These two algorithms are variants of Algebraic Reconstruction Technique (ART) methods for CT (Gordon et al., 1970). ART is one category of iterative reconstruction techniques. One of the reasons for limited performance improvement is that the chosen variants incur too much synchronicity due to frequent memory access on shared memory machines or inter-processor communications on distributed memory machines. Therefore, in this thesis we re-investigate the variants of iterative

reconstruction techniques, focusing on one variant, Ordered Subset Simultaneous Algebraic Reconstruction Technique (OS-SART) (Hudson and Larkin, 1994), which is more suited for Cell BE.

#### 1.1.4 Microwave Tomography

As mentioned in subsection 1.1.1, FDTD is a kernel to microwave imaging applications. One of such applications is microwave tomography (MT). Microwave tomography is a safe screening modality that can be used for breast cancer detection (Noghanian et al., 2006; Ashtari et al., 2010; Sabouni et al., 2011). The technique uses the dielectric property contrasts between different breast tissues at microwave frequencies to determine the existence of abnormalities. The proposed MT approach is an iterative process that involves two algorithms: Finite-Difference Time-Domain (FDTD) and Genetic Algorithm (GA). It is a computation intensive problem: (i) the number of iterations can be quite large to detect small tumours; (ii) many fine-grained computations and discretizations of the object under screening are required for accuracy.

We developed a parallel algorithm for microwave tomography on CPU-based homogeneous, multi-core, distributed memory machines (Xu et al., 2007a). The performance improvement was limited due to communication and synchronization latencies inherent in the algorithm. Therefore, we exploit the parallelism of microwave tomography on Cell BE processor. Since FDTD is a numerical technique with regular memory accesses, intensive floating point operations, SIMD type operations, the algorithm can be efficiently mapped on Cell BE achieving significant performance.

Finally, we propose a performance prediction model based on DMA transfers, number of instructions and operations, the processor frequency and DMA bandwidth. Since, microwave tomography is a complex problem that uses the SIMD units, SPEs and PPE for calculating FDTD and GA respectively, and all the other Cell BE architectural features, we used this problem as an example to obtain a general performance prediction model applicable to heterogeneous multi-core architectures.

In summary, the following Table 1.1 lists the four problems to be considered with their specific characteristics.

|               | FDTD          | FFT            | iterative re- | microwave     |

|---------------|---------------|----------------|---------------|---------------|

|               |               |                | construction  | tomography    |

|               |               |                |               | (MT)          |

| applications/ | microwave to- | CT             | CT            | medical imag- |

| kernels       | mography      |                |               | ing           |

| regular/      | regular       | semi-irregular | irregular     | irregular     |

| irregular     |               |                |               |               |

| structured/   | structured    | structured     | unstructured  | unstructured  |

| unstructured  |               |                |               |               |

| static/       | static        | dynamic        | dynamic       | dynamic       |

| dynamic       |               |                |               |               |

| synchronous/  | synchronous   | synchronous    | asynchronous  | asynchronous  |

| asynchronous  |               |                |               |               |

Table 1.1: Characteristics Comparison between four problems

The four problems are categorized as applications/kernels, regular/irregular, structured/unstructured, dynamic/static, synchronous/asynchronous. An irregular problem has irregular memory access pattern. Unstructured problems cannot be represented by a regular data structure such as an array. In a dynamic problem, communication pattern changes over time, data size increases or decreases, and load imbalance

may result. An asynchronous problem has its own challenges especially in termination detection.

#### 1.2 Contributions

The main contributions of the thesis is in mapping irregular computations on heterogeneous multi-core architectures, in particular Cell BE. In this thesis we consider four problems, with increasing complexity, thereby increasing the use of advanced features in the Cell BE architecture. We propose a general performance prediction model which can be used as a basis for evaluation in future heterogeneous multi-core architectures.

#### 1.3 Organization of the thesis

The remainder of this thesis is organized as follows. Chapter 2 briefly discusses parallel architectures and the recent accelerator architectures, focusing on Cell BE and various applications on the Cell BE. Chapter 3 investigates different parallel architectures for FDTD and the corresponding parallel algorithms, including parallel FDTD on distributed memory machines, homogeneous multi-core machines and the Cell BE processor. Chapter 4 presents the communication and synchronization overhead in traditional Cooley-Tukey butterfly network for FFT and introduces a modified network, indirect swap network (ISN), which was proposed in VLSI circuit design to reduce the overhead from improved locality. Chapter 5 describes iterative reconstruction techniques and investigates OS-SART technique on Cell BE, including

parallel OS-SART on homogeneous multi-core machines and the Cell BE processor. Chapter 6 illustrates microwave tomography technique and designs parallel microwave tomography algorithm on Cell BE processor, followed with a performance prediction model using microwave tomography as an example on Cell BE in chapter 7. Finally, chapter 8 presents our conclusions and future work.

# Chapter 2

# Parallel Architectures and Cell BE

This chapter briefly introduces parallel architectures, with a focus on Cell BE. It also reviews different applications on Cell BE.

#### 2.1 Parallel Architectures

The last few years has been dominated by teraflop (10<sup>12</sup> floating point operations per second) computers. Applications such as drug development to combat serious diseases, simulations of natural phenomena such as earthquakes, hurricanes and understanding the molecular dynamics of the universe or body cell structure have successfully used teraflop computers. High performance computing is now reaching the petaflop era and moving towards exascale computing. To sustain petaflop computing, thousands of processor cores will be needed. Hardware, programming languages, and software environment all play a significant role in designing parallel algorithms for these computers. Currently, very few parallel algorithms are scalable to petaflop

computers. Computer architectures are becoming more and more complicated and efficiently using these architectures to fully exploit scalability and high performance for many applications is a challenge.

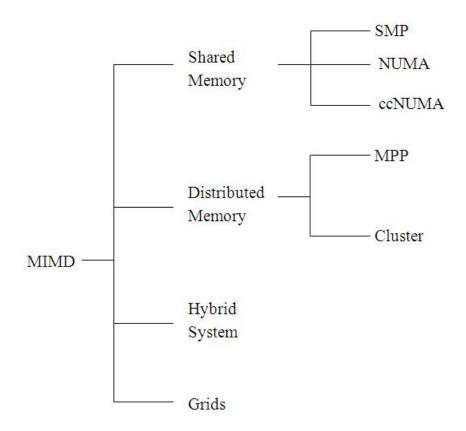

In the 1970's, Flynn (Flynn, 1972) categorized parallel systems into four models according to the number of instruction streams and data streams. Though, we are in the multi-core era, Flynn's taxonomy still applies. The four groups are single instruction single data (SISD) model, single instruction multiple data (SIMD) model, multiple instruction single data (MISD) model, and multiple instruction multiple data (MIMD) model. An SISD system is the common von Neumann model used in all single processor computers where one stream of instruction processes a single stream of data. An SIMD architecture has one control unit and many processing elements (PE). Each of the PE's perform the same instruction dictated by the control unit on different data sets. The processors compute in a synchronous manner. Vector processors, which operate on vector data in a pipelined fashion, can also be categorized as SIMD. SIMD systems exploit fine-grained parallelism. Systolic arrays fall under the MISD model. MISD architectures are obsolete. An MIMD system consists of multiple processing elements, each with its own stream of instructions operating on its own data. A vast majority of modern parallel systems such as clusters, network of workstations and multi-core machines fall into this group.

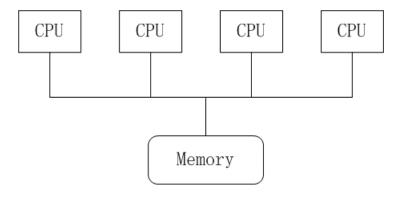

The MIMD system can be further subdivided according to the memory organization: shared memory and distributed memory architectures. In a shared-memory system, all processing elements share a single address space and communicate with each other by reading and writing to shared variables. Symmetric multiprocessor (SMP) or uniform memory access (UMA) systems, non-uniform memory access (NUMA) systems, and cache-coherent NUMA (ccNUMA) systems belong to shared memory systems. In an SMP system, all processors have access to a global memory and access all memory locations at equal speeds. This is illustrated in Figure 2.1.

Figure 2.1: SMP architecture

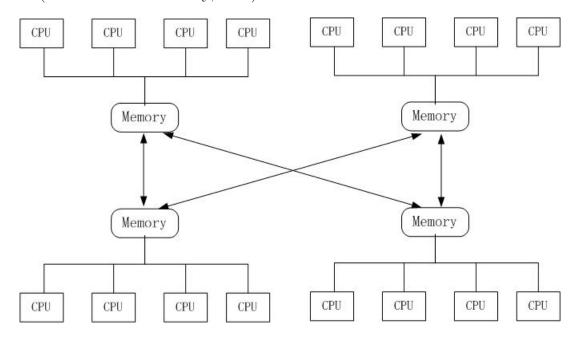

Although an SMP system is easy to program, it does not scale well. The interconnection network is usually a bus or a crossbar switch. In NUMA systems as shown in Figure 2.2, the memory is distributed among the various processors, each with its own address space but all processors have equal access to all the memory. In essence, NUMA machines are also called as distributed shared memory machines. In these architectures, some blocks of memory may be physically more closely associated with some processors than others. This reduces the memory bandwidth bottleneck and scales well. However, as a result, the access time from a processor to a memory location can be significantly different depending on how close the memory location is to the processor. In these systems, data locality is very important. Both SMP and NUMA machines have cache coherency problems. There are techniques

such as snooping and distributed directory protocols to alleviate the cache coherency issue (Patterson and Hennessy, 2007).

Figure 2.2: nonuniform memory access (NUMA) architecture

To mitigate the effects of nonuniform access, each processor has a cache, together with a cache-coherent protocol called cache-coherent NUMA (ccNUMA) systems. Logically, programming a ccNUMA system is the same as programming an SMP, but to obtain the best performance, the programmer needs to pay particular attention to data locality and cache effects. On the other hand, a distributed memory system is harder to program but scales well. Each processor of a distributed memory system has its own address space and communicates with other processors by message passing (sending and receiving messages via interconnect network) as shown in Figure 2.3.

The distributed memory systems are traditionally divided into two classes: massively parallel processors (MPP) and clusters. In an MPP, the processors and the

Figure 2.3: distributed memory architecture

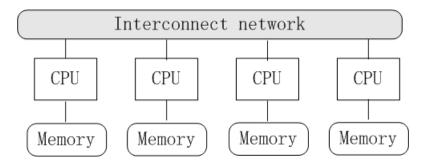

network are tightly coupled and have specialized hardware for special use. Clusters are composed of off-the-shelf computers connected by an off-the-shelf network. A well-known example of clusters is Beowulf clusters which connect PCs running the Linux operating system. Hybrid systems are clusters of nodes with separate address space in which each node contains several processors that share memory. Grids are systems that are distributed, heterogeneous resources (such as computation servers, storage application servers, etc) connected by LAN or WANS (Foster and Kesselman, 2003), which is often the Internet. The resources in the grids are owned by different individuals/organizations and there is no centre administration of the resources. The division of MIMD can be summarized in Figure 2.4.

With these parallel architectures and their corresponding parallel programming environments, such as OpenMP<sup>1</sup> for shared memory systems and MPI (Message Passing Interface)<sup>2</sup> for message passing systems, the HPC community has witnessed the boom in HPC applications. Recently, computational science applications which are interdisciplinary in nature have attracted the HPC community. However, the growth

<sup>&</sup>lt;sup>1</sup>http://openmp.org/wp/

<sup>&</sup>lt;sup>2</sup>http://www.open-mpi.org/

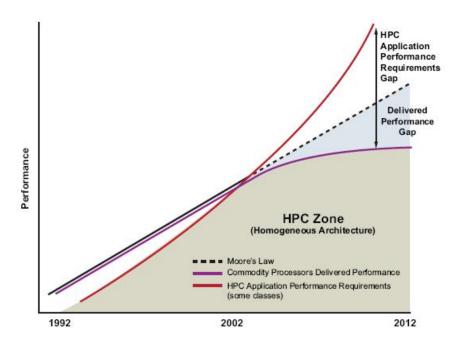

Figure 2.4: MIMD division

trend has been impaired due to the increasing gap between the exponentially growing requirements of high bandwidth, low latency, data intensive applications and the performance delivered by commodity processors and parallel systems as shown in Figure 2.5 (Banton, 2008). Moore's law has hit the limitation to improve performance at the increased rate of power consumption and frequency. At about 3GHz, the power requirements rise rapidly and the performance has reached a limit, largely due to pipelining as deep as thirty stages. In 2001, Pat Gelsinger, Intel's first CTO, developed a law that discusses the dilemma of widening gap between the required and delivered performance of commodity processors in Gelsinger's law. It states that

as the number of transistors doubles, the performance increases by only 40%, but the power consumption increases out of control (Banton, 2008).

Figure 2.5: Gap between required performance and delivered performance. (Banton, 2008)

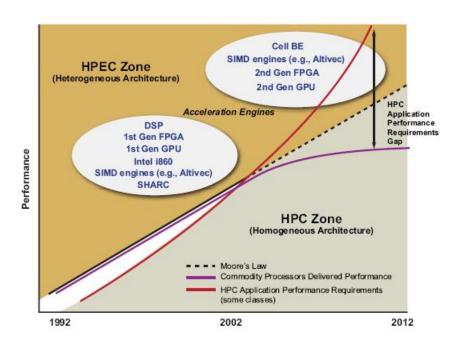

Gelsinger's law and the widening gap has driven chip makers to migrate towards adoption of multi-core architectures and accelerators (co-processors) instead of continuing to increase the number of transistors and processor frequency in order to narrow the gap, as shown in Figure 2.6.

Furthermore, in the last few years, power consumption, cooling infrastructure, physical size, and carbon footprint have become more important than ever for some HPC applications, which has driven the HPC community into green computing<sup>3</sup>. A new metric, SWaP, is proposed to measure the power consumption of parallel

<sup>&</sup>lt;sup>3</sup>http://www.green500.org

Figure 2.6: Narrowed gap between required performance and delivered performance via accelerator. (Banton, 2008)

architectures<sup>4</sup>. SWaP, Size (in rack units (RU)), Watts (power consumption during benchmark operation), and Performance (using industry standard benchmarks), is defined as follows:

$$SWaP = \frac{performance}{space \times power} \tag{2.1}$$

SWap is more favorable to new parallel architectures using multi-cores or accelerators, such as Cell BE and GPGPUs. Cell BE has the capabilities of running both fine and coarse grained computations. The drawback of this architecture is the low level assembly-style language which of course allows a programmer to draw the computing power of the hardware that only a knowledgeable programmer would benefit. The General Purpose Graphics Processing Units (GPGPU), an easily attachable GPU chip

<sup>&</sup>lt;sup>4</sup>http://www.sun.com/servers/coolthreads/swap/index.jsp

to any general purpose computer, includes large number of cores, provides fine-grained computations and efficiently implements data parallel applications. The drawback in this architecture is the slow global memory access latency and its high network bandwidth between the GPU and the CPU. All these systems have one common feature: they have higher SWaP values compared to conventional parallel systems. It's more difficult to fully exploit parallelism on these architectures compared to conventional parallel systems due to architectural restrictions in the type of applications that can be designed.

Due to the high SWaP values, architects considered designing high performance supercomputers using conventional processors with accelerators. For example, the Cell BE processor was a building block of the Roadrunner, once the fastest supercomputer in the list of top500.org<sup>5</sup>. Roadrunner was built using 6,912 dual-core AMD Opteron processors and 12,960 PowerXCell 8i processors (enhanced Cell BE processors with improved double-precision floating-point performance). Initial tests indicated that the Cell BE processors reached 1.33 petaflops while Opterons reached 49.8 teraflops, implying that twice as many Cell BE processors produce 26.7 times more computing power compared to the dual-core Opterons. Recently, this idea of hybrid systems (CPU and GPU on same chip) has been adopted in the general purpose computers market. Accelerated Processing Units (APU) has gained special attention in the PC market with its on-chip CPU and GPU. However, with less number of GPU cores, but with capabilities of conserving power built within the hardware, the benefits of this architecture is yet to be seen and will be the research focus for future studies in the HPC community.

<sup>&</sup>lt;sup>5</sup>http://www.top500.org

#### 2.2 Cell BE Processor

The Cell BE processor is the first implementation of the Cell Broadband Engine Architecture (CBEA) (Chen et al., 2007). Although the Cell BE processor was initially intended for applications in media-rich consumer-electronics devices such as game consoles (Sony Play Station 3, PS3) and high-definition television, the architecture has been enabling fundamental advances in processor performance. These advances are expected to support a broadband range of applications in both commercial and scientific fields.

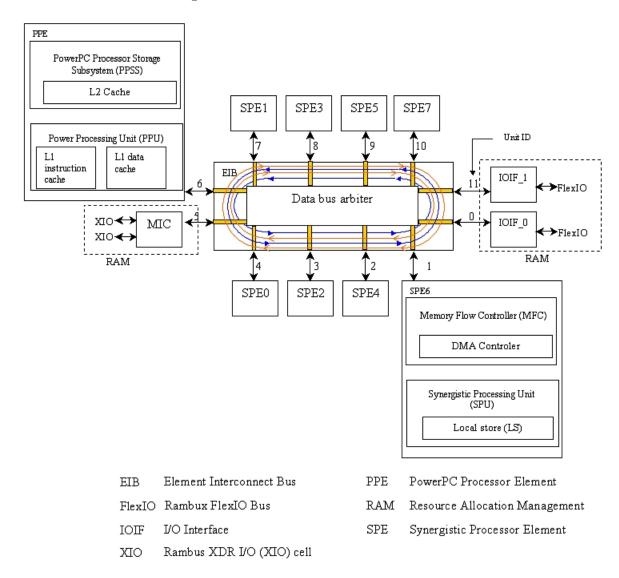

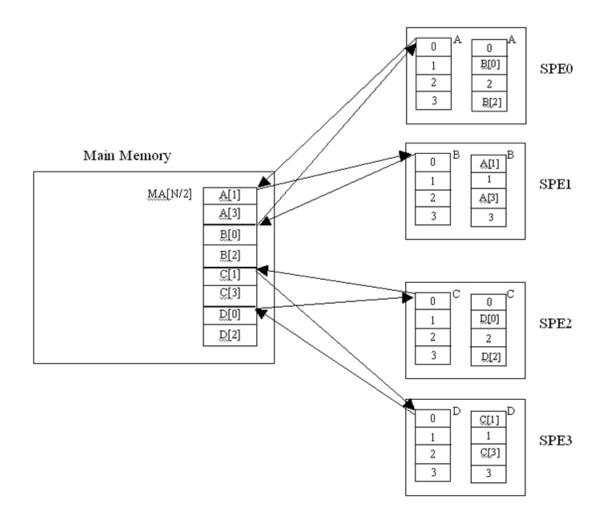

The first generation of the Cell BE processor is a single-chip processor with nine processor elements operating on a modified shared memory model, as shown in Figure 2.7 (Arevalo et al., 2007). The Cell BE processor is a heterogeneous multi-core processor. The nine processor elements consist of one Power Processor Element (PPE) that is compatible with 64-bit PowerPC Architecture with operating system support and eight Synergistic Processor Elements (SPEs) optimized for computation intensive SIMD applications. Other important architectural parts include a memory controller, an I/O controller, and an on-chip coherent bus EIB (Element Interconnect Bus) which connects all elements on the single chip. The SPU (synergistic processing unit) in an SPE is a RISC-style processing unit with an instruction set and a microarchitecture. The eight SPEs are purposefully designed for high performance data-streaming and data-intensive computation via large number of wide uniform registers (128-entry 128-bit registers) and 256KB local store for each SPE. The Memory Flow Controller (MFC) on each SPE and the high bandwidth EIB (with a peak bandwidth of 204.8 GBytes/s) enable SPEs to interact with PPE, with other SPEs, and with the main

memory efficiently. The EIB has separate communication paths for data and commands which request data transfers to and from other elements on the bus. The EIB data network consists of four 16-byte wide data rings as shown in Figure 2.7: two rings clockwise and the other two counterclockwise. The EIB data bus arbiter always selects one of the two rings that travel in the direction of the shortest transfer.

Figure 2.7: Cell Broadband Engine Processor Block Diagram

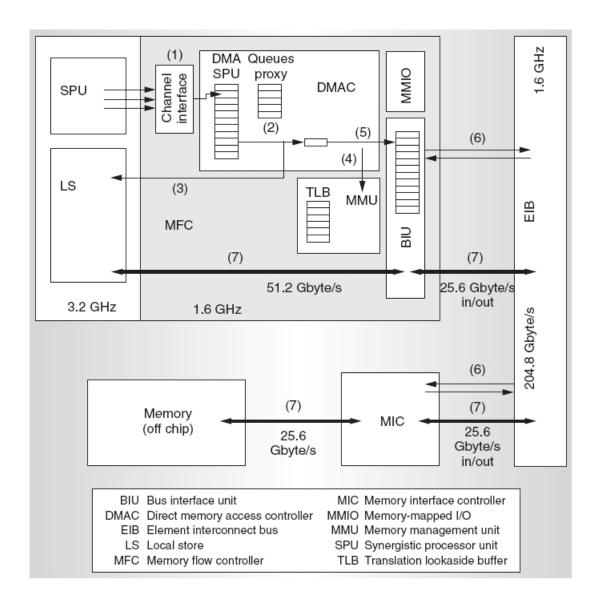

One of the most salient differences between the PPE and SPEs is the way they access the main memory. PPE accesses the main memory directly with load and store instructions that move data between the main memory and a private register file, similar to the way that conventional processors access the main memory. On the other hand, SPEs cannot access the main memory directly. They issue direct memory access (DMA) commands to move data and instructions between the main memory and a private local memory called a local store (LS). However, DMA transfers can be done without interrupting the SIMD operations on SPEs if the operands of SIMD operations are available in the LS. This 3-level organization of storage (register file, local store, main memory), with asynchronous DMA transfers between LS and main memory, is radically different from conventional architectures and programming models. It explicitly parallelizes computation with the transfers of data and instructions and is the main factor that the Cell BE processor brings significant performance improvement over contemporary microprocessors. But the 3-level organization complicates the programming effort by requiring explicit orchestration of data movements. An example of a DMA transfer initiated by a SPU to access the main memory is shown in Figure 2.8 (Kistler et al., 2006). Step 1 to step 7 are explained as follows.

- 1. The DMA command issued by the SPU is put to the MFC SPU command queue via channel interface. If the DMA command is issued by other SPUs or the PPE, the command will be put to the MFC proxy command queue via the MMIO register.

- 2. The DMA controller (DMAC) will select a command for processing.

- 3. This step works for a DMA list command which is an array in the SPU's local

store. Each element in the array consists of DMA source/destination addresses and transfer lengths for each addresses pair. The DMAC queues a request for the list element to the local store interface and puts the returned list elements to the MFC SPU command queue as resolved DMA commands as in step 1.

- 4. This step translates the source/destination addresses in the DMA command using MMU and TLB (translate look-aside buffer).

- 5. The DMAC creates a bus request to transfer data for the command and queues the bus request to the bus interface unit (BIU).

- 6. The BIU selects the request from its queue and issues the command to the EIB. The EIB orders the command with other outstanding requests and broadcasts the command to all bus elements. Since the example is to access main memory, the memory interface controller (MIC) will acknowledge the command to the EIB. The EIB then informs the BIU that the command is accepted and data transfer between the local store and the main memory can begin.

- 7. The BIU performs reads/writes for the data transfer. The EIB transfers the data for the request between the BIU and the MIC. The MIC transfers data to or from the off-chip main memory. One bus request can transfer up to 128 bytes. If the DMA command requests more than 128 bytes, it will be unrolled to a sequence of bus requests and remains in the MFC SPU command queue until all bus requests have completed. At the same time, DMAC will accept other DMA commands and starts again from the step 1. When all bus requests for a command have completed, the DMAC will signal command completion to

the SPU and remove the command from the queue.

Figure 2.8: EIB data flow illustration. (Kistler et al., 2006)

The Cell BE processor was designed to address some of the issues related to the three walls which limit the performance of contemporary microprocessors and widen the gap between required performance and delivered performance (Kahle et al.,

2005). The three walls are power wall, memory wall, and processor frequency as mentioned in Chapter 1. For power wall, the Cell BE processor aims to improve power efficiency at about the same rate as the performance increase by differentiating control tasks and computation-intensive tasks to different processor elements. The PPE is responsible for control tasks. Intensive computation tasks are offloaded to SPEs which have simpler hardware implementations and save the transistors for controls to be used for computations. Hence, some control tasks are missing in SPEs such as branch prediction, out-of-order execution, speculative execution, shadow registers and register renaming, extensive pipeline interlocks, etc. For memory wall, as mentioned above, the Cell BE processor uses 3-level memory hierarchy and asynchronous DMA transfers between main memory and LS to mitigate or hide the several hundreds cycles of DRAM memory latency in conventional microprocessors. For processor frequency, PPE supports two threads simultaneously in hardware and each SPE has a large register file which supports many simultaneous in-process instructions without the overhead of register-renaming or out-of-order processing. In summary, the Cell BE alleviates the problems posed by three walls via optimizing control plane processor (PPE) and data plane processors (SPEs) separately.

The Cell BE processor exhibits several levels of parallelism. Coarse-grained parallelism exists between the PPE and SPEs, and between different SPEs. The PPE and SPEs can work on different tasks concurrently. Each SPE can also perform different tasks simultaneously. Fine-grained parallelism can be implemented both on the PPE and on the SPE. Both the PPE and the SPEs have their own SIMD instruction sets, each capable of executing two instructions per clock cycle. The PPE has a two-way

multi-threaded hardware support and is a dual-issue in-order processor. The SPE does not support multi-threading on the hardware level. However, it is also a dual-issue in-order processor because of its two pipelines. Also, the MFC of each SPE can move data around without interrupting the ongoing tasks on the PPE and SPEs. The nature of parallelism on the Cell BE processor is expected to produce significant performance improvement if fully explored and utilized (Brokenshire, 2006).

All these features make the Cell BE processor attractive for computation intensive applications in various areas (Williams et al., 2006). A detailed introduction of some applications follows in section 2.3.

# 2.3 Applications on Cell BE Processor

Although the Cell BE processor's initial target was game/multimedia applications, it has been a research topic in a growing number of other areas and applications due to its potential for high performance. Therefore, this section will review the research of different applications/algorithms on Cell BE.

Numerical kernels are usually time consuming. Their performances are critical to the applications. Hence, several kernels have been investigated on Cell BE and results have shown significant performance improvement on Cell BE for those kernels over conventional microprocessors. FFT (Fast Fourier Transform) is a kernel for a variety of applications such as image processing (Oppenheim and Willsky, 1983), computed tomography (Basu and Bresler, 2000) and computational finance (Barua et al., 2005). Chow et al. (Chow et al., 2005) investigate the performance of Cell BE for a modified stride-by-1 algorithm proposed by Bailey (Bailey, 1990) based

on Stockham Self-sorting FFT. They fix the input sampling size to 16 million  $(2^{24})$ single precision complex elements and achieve 46.8 Gflop/s on a 3.2GHz Cell BE. Williams et al. (Williams et al., 2006) investigate 1D/2D FFT on Cell BE on one SPE. FFTW<sup>6</sup> adds various benchmarks of FFT on IBM Cell Blade and PlayStation 3 for different combination among single precision, double precision, real number inputs, complex number inputs, 1D, 2D, and 3D transforms. Bader et al. (Bader and Agarwal, 2007) investigate the naive Cooley-Tukey radix-2 Decimate in Frequency (DIF) algorithm and design an iterative out-of-place FFT called FFTC on Cell BE. FFTC takes ordered input and produces ordered transformed output. The input (array of size N) is divided into 2P chunks, each of size  $\frac{N}{2P}$  (P is the number of SPEs). For each iteration (log N iterations in total), SPE i is assigned chunk i and i + Pfrom the data set to achieve load balance between all SPEs. Although they manually vectorize (SIMDize) the Gentleman-Sande butterfly computations and achieve high performance, the performance is still deteriorated by two factors. One is that for each iteration in the butterfly network, each SPE needs to DMAin (transfer data from main memory to local store) and DMAout (transfer data from local store to main memory)  $\frac{N}{P}$  data elements. This requirement puts non-trivial communication burden on EIB for large N. The second factor is the comparatively large number of synchronization, which is  $2 \log N \log P$  stages in total. In order to mitigate the (Xu et al., 2008) study an improved FFT synchronization overhead, Xu et al. algorithm based on Indirect Swap Network (ISN) on the Cell BE. ISN originates from the Cooley-Tukey radix-2 Decimate in Time (DIT) butterfly network. It only has log Piterations which need to communicate and synchronize between SPEs. The downside

<sup>&</sup>lt;sup>6</sup>http://www.fftw.org

is the dynamically changing partnership between SPEs implies the requirement of dynamic branch operations which is not supported on SPEs due to its simple design and shortage of chip area for the branch prediction unit after more cores are integrated on the single chip. Details about FFT based on ISN for Cell BE are explained in Chapter 4.

Several graph-related algorithms have also been investigated on Cell BE. Villa et al. (Villa et al., 2007) design a parallel Breadth-First-Search (BFS) algorithm inspired by the Bulk-Synchronous Parallel (BSP) model for general multi-core architectures. The parallel BFS algorithm is implemented on Cell BE and uses performance optimization techniques available on Cell BE. These techniques include inherent SIMD on SPEs, double buffering, explicit data orchestration between the hierarchy of working sets, and multi-dimensional parallelism space on chip. The BFS on Cell BE virtually scales linearly for graphs having high average degrees of vertices. For graphs with small average degrees, the performance saturates when more SPEs are involved. For a graph with average degrees of vertices of 200, Cell BE is 22 times faster than Intel Pentium and Woodcrest, 26 times faster than AMD Opteron, and at the same level of performance of 128 BlueGene/L processors and an MTA-2 system with 23 processors.

Sorting is one of the most important and also fundamental problem in large-scale data intensive applications in different fields such as databases. Gedik et al. design a high performance sorting for Cell BE, called CellSort (Gedik et al., 2007). CellSort is based on distributed bitonic merge with a SIMDized bitonic sorting kernel. It is a three-tiered algorithm. The three-tiered approach can best use the several levels

of parallelism on Cell BE and best conquer the constraint of different bandwidth for accesses between local store and main memory. Among the three tiers, the innermost first tier, single-SPE local sort, is an effecient bitonic sorting kernel to sort data items fitting in the limited local store of an SPE. Although bitonic sort does not have optimal asymptotic complexity, it is more suitable for SPE. It shows contiguous memory access pattern which can provide SIMD acceleration. It has a straightforward non-recursive implementation when the number of data items is a power of 2. Furthermore, it is an in-place sort which can save memory space during the compare-and-swap operations. This is critical to SPEs since each SPE only has very limited local store. The second tier, distributed in-core sort, sorts data items fitting into the collective space provided by the local stores of participant SPEs. This tier can benefit from the high bandwidth for cross-SPE local store transfer via EIB bus. This tier is responsible for the in-core bitonic merge based on the result of the first tier. It consists of two stages. During the first stage, all SPEs perform the local bitonic sort in parallel. For the second stage, all SPEs have to go through  $\log P$ number of k-merge phases (P is the number of SPEs, k=2m to  $k=P\times m, m$  is the number of data items that the first tier sorts). The outermost tier, distributed out-ofcore sort, happens when the set of data items need larger memory than cumulative space of all SPEs and SPEs have to transfer data back and forth between the local stores and main memory via comparatively lower bandwidth. This tier uses out-ofcore bitonic merge over the results of the second-tier. With manual SIMDization and low level optimization such as loop unrolling and branch avoidance, CellSort on one SPE achieves 1.7 times faster for the first tier than on 3.2GHz Intel Xeon, 10 times faster for the second tier on two Cell BE processors than dual-3.2GHz Intel Xeon, and four times faster for 0.5GB data with 16 SPEs than dual-3.2GHz Intel Xeon. Compared with the ABiSort algorithm on GPU (GeForce 7800) (Greb and Sachmann, 2006), CellSort is seven times faster to sort 1 million (float, point) pairs. ABiSort and other sort algorithms on GPU suffer from two factors. One is cache memory latencies which have to be designed by using appropriate data layout and tiling. The second factor is the non-trivial mapping of basic data types into pixels in GPU's texture memory (Govindaraju et al., 2006). The authors also mention that the ability of SIMDizing bitonic sort kernel in CellSort is the key to its high performance. Other sort kernels such as Radix and Postman's sort degrade the overall performance because they involve extensive scalar updates which are hard to be SIMDized.

Database is an essential part in many applications. Hence, an efficient RDBMS (Relational DataBase Management System) is important. Heman et al. investigate and port a vectorized query processing model of MonetDB/X100 on Cell BE (Heman et al., 2007). MonetDB/X100<sup>7</sup> is an open-source DBMS using vertical fragmented storage supporting both SQL and XQuery. One port effort is manual loading which adds code management to the list of database tasks such as select and join. It borrows the idea in Octopiler research<sup>8</sup> compiler which is developed by IBM and tries to hide code size limitations of SPE local store by automatically partitioning code into small enough chunks. For manual loading, each SPE runs a small runtime system that waits for code and data requests from the PPE. When a request comes in, SPE loads the data and code (if not in local store) and executes the required operation. In this way,

<sup>&</sup>lt;sup>7</sup>http://monetdb.cwi.nl

<sup>8</sup> http://arstechnica.com/uncategorized/2006/02/6265-2/

SPE can deal with late binding dynamically, which is critical for interactive database queries. A limited set of relational operators (scan, select, aggregate) has been ported on PPE and the computational primitives on SPEs. The primitives are responsible for computing core functions such as addition and multiplication. With porting this portion only, Cell BE achieves 20 times faster than a 1.3GHz Itanium2 (16 seconds on Cell BE versus 311 seconds on Itanium) for 6 million records. The reason for this improvement relies on several factors. The first factor is that ManetDB/X100 allows for Volcano-style (once-a-tuple) pipelining which are suitable for SIMD operation on SPE. The record is organized via columns rather than rows. The second factor is that the intermediate results are kept in local store rather than in main memory to avoid EIB and main memory channels contention.

Data mining is another area of interest. The exponentially growing cost for extracting knowledge from information and short response time for interactive process of data mining has attracted researchers in this area to investigate the potential of Cell BE for data mining. Buehrer et al. (Buehrer and Parthasarathy, 2007) investigate three key kernels in data mining, namely clustering, classification, and outlier detection on Cell BE. Clustering is a process by which data points are grouped together based on similarity. kMeans, a popular distance-based clustering algorithm, is examined on Cell BE. Classification is a data mining task which predicts the label or class of a data object. A classification algorithm based on analogy, k Nearest Neighbors algorithm (kNN), is investigated on Cell BE. Outlier detection is important in many areas such as network intrusions detection and noise in data set etc.. A distance-based outlier detection algorithm, ORCA<sup>9</sup>, is ported to Cell BE. These

<sup>&</sup>lt;sup>9</sup>http://www.isle.org/ sbay/software/orca/

algorithms are embarrassingly parallel. Hence, the multi-level parallelism inherent in Cell BE may bring benefit to these algorithms. The authors emphasize that Cell BE is superior to other commodity processors as to power efficiency. For example, one Cell BE SPU uses only four watts per core at 3.2GHz, while a 2.8GHz Intel Pentium D 2 needs 95 watts (Buehrer and Parthasarathy, 2007). Even with low power consumption, Cell BE achieves significant performance improvement for the three kernels. As to kMeans for clustering, Cell BE using only 6 SPEs available on a PS3 uses 1.25 seconds compared to 9 seconds on Pentium D 2. The simulation setting includes 100K data points, 60 dimensions and 24 centres. For kNN, Cell BE uses 0.25 seconds compared to 4.64 seconds on Pentium D 2 for 20K training points, 2K test points, 24 dimensions and 10 neighbors. For ORCA, Cell BE uses only 7.1 seconds compared to 71 seconds on Pentium D 2 for 200K data points, 32 dimensions, 10 outliers and 40 neighbors.

Note that the Cell BE has not only been investigated for traditional problems in computer science. It has gained attention from the growing computational science communities such as computational physics, computational biology, and biomedical areas. These areas have huge amount of computations for simulation. Power efficiency and computation power are two of the most important factors when researchers choose hardware facilities. Cell BE has exhibited such favorable properties as discussed so far. Therefore, what follows will cover the investigation and experience of Cell BE in computational science.

Sweep3D is an algorithm to solve a 3D neutron transport problem from a scattering source (Koch et al., 1992). It can be used to simulate and analyze fires,

explosions and even nuclear reactions by simulation rather than by experiments. Its discrete analysis starts with dividing the domain into a finite mesh of cells such that the particles such as photons flow along fixed number of waves and occupy fixed energy levels. The analysis result shows the flux of photons or other particles through the domain. It is time-consuming for a large domain. Hence, Petrini et al. (Petrini et al., 2007) investigate the problem on Cell BE by fully using five levels of parallelism available on Cell BE. The five levels of parallelism are process level parallelism shown on different Cell BE processors via MPI, thread level parallelism across SPEs, data streaming parallelism via asynchronous DMA and double buffering, vector parallelism by SIMD operation on SPU via 128-bit wide registers, and pipeline parallelism through the two pipelines on SPU. The authors investigate the performance in detail by adding different levels of optimization. For a  $50 \times 50 \times 50$  input set, Sweep3D uses 22.3 seconds when it is ported to PPE with no code changes. IBM XLC compiler instead of GNU C compiler can reduce the time to 19.9 seconds. With porting the computation intensive nested loops to 8 SPEs, the run time drops dramatically to 3.55 seconds. Manual SIMDization and double buffering helps Sweep3D to achieve a performance of 1.68 seconds only. Cell BE is about 4.5 times faster than IBM Power5, which is specifically designed for scientific computing. The improvement can reach to a factor of 20 over other general processors such as Intel Xeon. Therefore, porting and optimizing Sweep3D on Cell BE is worth the effort. The authors also expect that the optimization techniques by application developers now can eventually migrate into parallelizing tools and compilers. These supports can relieve the burden on software developers who are required to manage low level processor components such as memories and communications via DMA, which is in turn the consequence of the architecture evolution to simpler and more streamlined paradigms.