Real Time Linear Predictive Coder of Speech

Ъу

Kenneth Charles Walter Mikolajek

A thesis

presented to the University of Manitoba

in partial fulfillment of the

requirements for the degree of

Master of Science

in

Electrical Engineering

Winnipeg, Manitoba, 1981

(c) Kenneth Charles Walter Mikolajek, 1981

#### REAL TIME LINEAR PREDICTIVE CODER OF SPEECH

BY

#### KENNETH CHARLES WALTER MIKOLAJEK

A thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements of the degree of

#### MASTER OF SCIENCE

## © 1981

Permission has been granted to the LIBRARY OF THE UNIVER-SITY OF MANITOBA to lend or sell copies of this thesis, to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

I hereby declare that I am the sole author of this thesis.

I authorize the University of Manitoba to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Ken Mikolajeh

Kenneth Charles Walter Mikolajek

I further authorize the University of Manitoba to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Kenneth Charles Walter Mikolajek

Ka Miholajek

The University of Manitoba requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

#### ABSTRACT

A speech research facility based on bit-slice arcitecture has been developed and tested. The processor was successfully programmed to produce autocorrelation values, reflection coefficients, prediction coefficients, and the frame error of a speech signal in real time. The software is written on a program and a microprogram level.

### ACKNOWLEDGEMENTS

The author wishes to express his appreciation to the individuals who have contributed to this research. The author extends his appreciation to Dr. W. Kinsner for suggesting the topic of Linear Predictive Coding and for arranging financial support from the Natural Sciences and Engineering Research Council and the Industrial Applications of Microelectronics Center. Also, Dr. Kinsner offered guidance in directing the field of study which led to an understanding of the topic.

The numerous technical discussions about LPC and the speech signal with Luc Mahieu, Andreas Weirich, and Victor Shkawrytko were invaluable to completion of this work. I also would like express appreciation to Jim Reimer, Greg Smith, Jack Sill and Balraj Joll for many ideas which were implemented relating to hardware.

The author would also like to thank Debbie Strachan for the care taken in typing the manuscript and finally, Leona Kalra for her moral support.

# CONTENTS

| ABSTRAC | ACT                                              | • | • • | • | • | • | e  | 0  | ¢  | e  | ¢   | iv |

|---------|--------------------------------------------------|---|-----|---|---|---|----|----|----|----|-----|----|

| ACKNOW  | JLEDGEMENTS                                      | • | c 0 |   | 0 | G | •  | ¢  | •  | c  | e   | v  |

| Chapte  | er                                               |   |     |   |   |   |    |    |    |    | D 2 | 47 |

|         |                                                  |   |     |   |   |   |    |    |    |    | Ро  | ge |

| I.      | INTRODUCTION                                     | • | • • | • | ¢ | e | ¢  | ٠  | .• | ¢  | •   | 1  |

| II.     | LINEAR PREDICTION CODING THEORY OF SPEEC         | Н |     | ۰ | e | • | e. |    | ۰  | ¢  | •   | 2  |

|         | The Speech Signal                                |   | ٥ . | • |   | • | ·  |    | ٠  | c  | e   | 2  |

|         | Speech Production                                |   |     | • | o | c | ¢  | c  | e  | 6  | e   | 2  |

|         | Excitation • • • • • • • • • • • • • • • • • • • | • |     |   | 6 | • | •  | ¢. | e  | •  | •   | 4  |

|         | Vocal Tract Model                                | • | ۰ . |   | • | • | •  | •  | e. | 6. | e.  | 6  |

|         | Speech Perception                                |   | o • |   | • | • | 4. | ٠  | e. | •  | e   | 12 |

|         | Linear Predictive Coding Theory                  |   |     |   |   | e | 6  | e  | ٠  | e  | c   | 18 |

|         | The LPC Model                                    |   |     | • | ۰ | • | •  | ٠  | e  | ٠  | •   | 18 |

|         | LPC Parameter Generation                         |   |     |   |   | • | •  | e  | ۰  | •  | 6   | 20 |

|         | Autocorrelation Method                           |   |     |   |   |   | c  |    | •  | •  | ٥   | 22 |

|         | Covariance Method                                |   |     |   |   | ٠ | •  | •  |    | •  | •   | 23 |

|         | Lattice Formulations                             |   |     |   | ۰ |   | ¢  | 6  | •  | 6  | ۰   | 24 |

|         | Comparison of Methods                            |   |     | • | • | • | •  | •  | ٠  | 6  | •   | 24 |

| III.    | ALGORITHM DESCRIPTION                            |   |     |   | ٠ | • | e  | •  | •  | e  | ٠   | 26 |

|         | Hindorring                                       |   |     |   |   |   | _  |    |    | _  | _   | 26 |

|         | Windowing                                        |   |     |   |   |   |    |    | ٠  | ·  |     | 30 |

|         | Predictor Solution • • • • • • • •               |   |     |   |   |   |    |    |    |    |     | 33 |

|         |                                                  |   |     |   |   |   |    |    |    |    |     |    |

|         | Computational Considerations                     |   | -0  | • | ٠ | c | ۰  | •  | •  | ٠  | ¢   | 33 |

| IV.     | SYSTEM OVERVIEW                                  | • | • ( | • | • | ٠ | a  | ٠  | •  | •  | e   | 36 |

|         | The Bit Slice Approach                           |   |     |   | ۰ | ٠ | ۰  |    |    |    |     | 36 |

|         | System Hardware                                  |   |     |   |   |   |    |    |    | e  |     | 37 |

|         | Components                                       |   |     |   |   |   |    |    |    |    |     | 37 |

|         | System Hardware Operation                        |   |     |   |   |   |    |    |    |    |     |    |

|         | System Software Operation • • • • •              |   |     |   |   |   |    |    |    |    |     |    |

|         |                                                  |   |     |   |   |   |    |    |    |    |     |    |

| V •     | HARDWARE DESCRIPTION                             | • | e ( | • | • | ٠ | e  | •  | ٠  | ٠  | ۰   | 41 |

|         | Preprocessor and A/D Converter                   |   |     |   |   |   |    |    |    | ٠  | •   | 41 |

|         | Preprocessor · · · · · · · · ·                   |   |     |   |   | e | ٠  |    |    |    | ٠   | 41 |

|         | Sampling                                         |   |     |   |   |   | e  | ۰  |    |    |     | 44 |

|         | Program Memory                                   |   |     |   |   |   |    |    |    |    |     | 47 |

|         | The I PCMK                                       |   |     |   |   |   |    | •  |    |    | •   | 49 |

|        | Bit Slice Processor Operation 5    |

|--------|------------------------------------|

|        | Pipeline Register                  |

|        | Microinstruction Sequencer 5       |

|        | ALU and Register Set 6             |

|        | Status                             |

|        | I/O Registers 6                    |

|        | Mapping Prom and Vector Register 6 |

|        | External Bus                       |

| VI.    | SOFTWARE / FIRMWARE 6              |

|        | Program Instructions 6             |

|        | Program vs. Microprogram 6         |

|        | Register Allocation                |

|        | Instruction Description            |

|        | Microprogram Software              |

|        | Development                        |

|        | Instruction/Microprogram Interface |

|        | Data Acquisition                   |

|        | Major Microprogram Routines        |

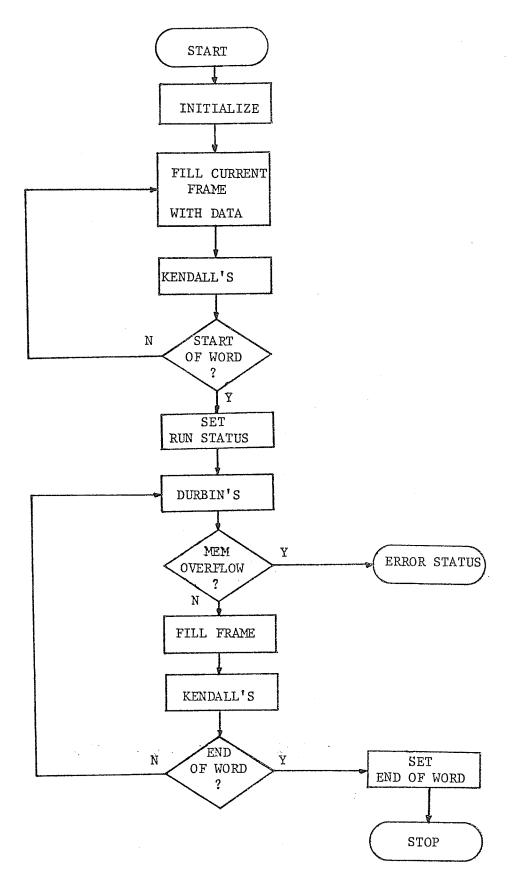

|        | Main Program                       |

| VII.   | RESULTS                            |

|        | Autocorrelation Values             |

|        | Reflection Coefficients            |

|        | Predictor Coefficients             |

|        | Framing Error                      |

| VIII.  | CONCLUSIONS                        |

| IX.    | RECOMMENDATIONS                    |

| BTBLIO | GRAPHY                             |

|        |                                    |

| Append | <u>ix</u> page                     |

|        |                                    |

| Α.     | LPCMK AND ASSOCIATED HARDWARE      |

| В.     | LPCMK MICROPROGRAM LISTINGS        |

| С.     | PROGRAM MEMORY TESTING LISTINGS    |

| D.     | AMDAHL SIMULATION PROGRAM          |

# LIST OF FIGURES

| Fig | ure                                               |

|-----|---------------------------------------------------|

|     | page .                                            |

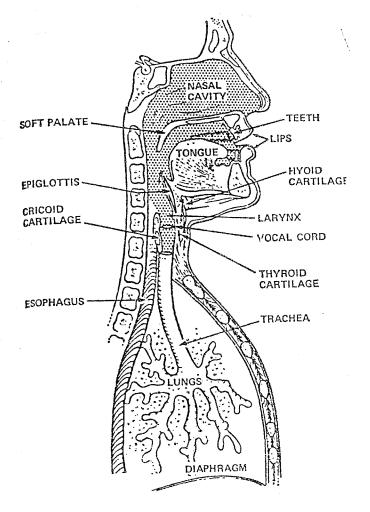

| 1.  | Speech Organs                                     |

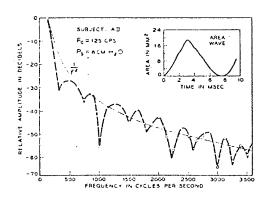

| 2.  | Glottal Pulse Spectrum                            |

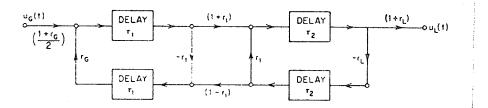

| 3.  | Lossless Tube Model of the Vocal Tract            |

| 4.  | Two Tube model of the Vocal Tract                 |

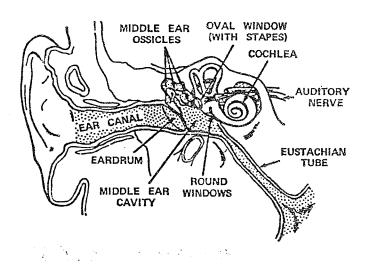

| 5.  | Hearing Organs                                    |

| 6.  | Subjective Perception                             |

| 7.  | Schematic Illustration of the Cochlea Unrolled 16 |

| 8.  | Basilar Displacement                              |

| 9.  | LPC Model                                         |

| 10. | 200 Point Hamming Window                          |

| 11. | System Hardware Configuration                     |

| 12. | Preprocessor and A/D Block Diagram                |

| 13. | Preprocessor Frequency Response                   |

| 14. | A/D Conversion Timing Diagram                     |

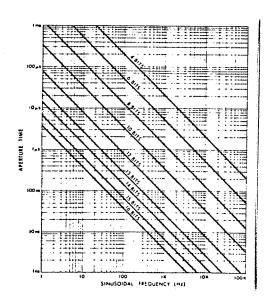

| 15. | Aperture Time                                     |

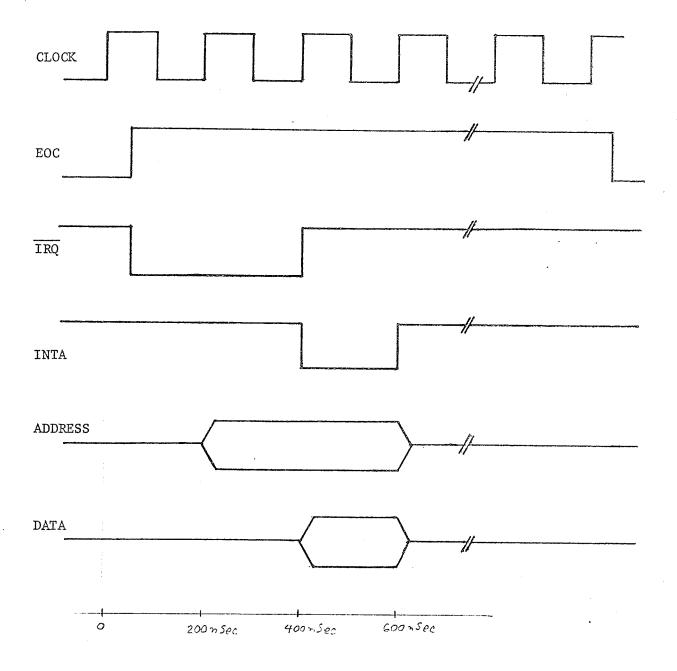

| 16. | Interrupt Response Timing                         |

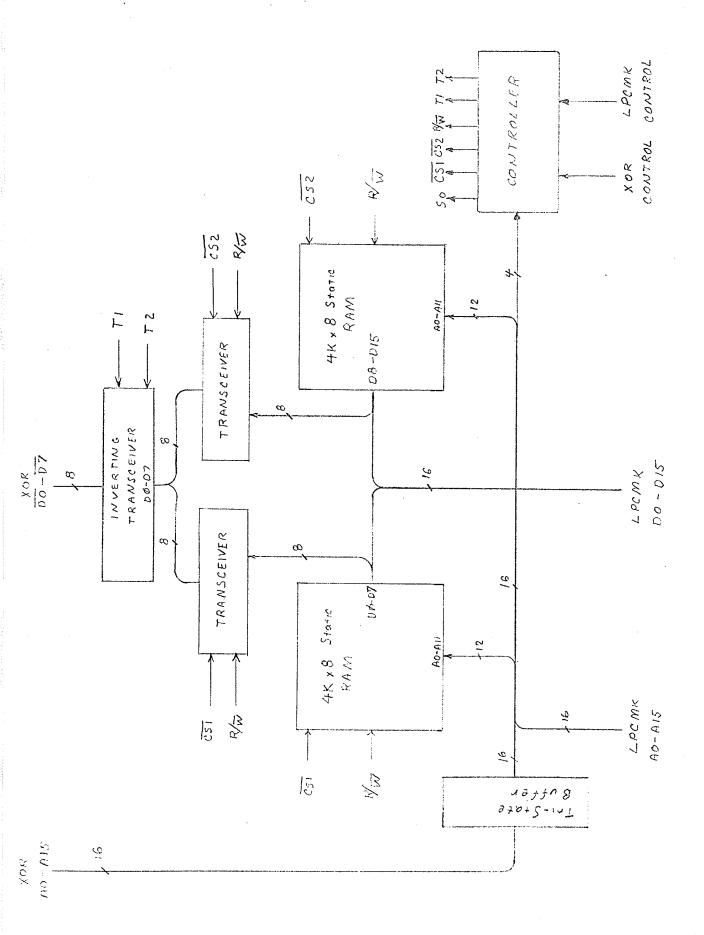

| 17. | Program Memory Block Diagram                      |

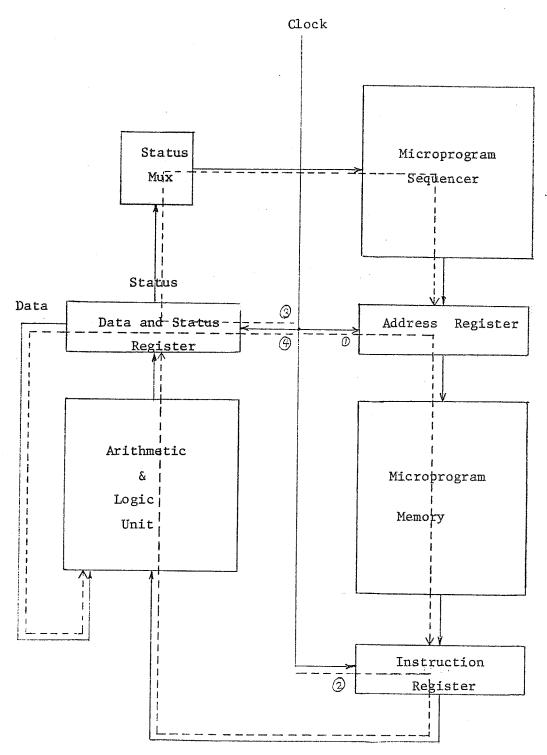

| 18. | A Typical Bit-Slice System Block Diagram 51       |

| 19. | The LPCMK Block Diagram                           |

| 20. | Microinstruction Sequencer Block Diagram          |

| 21. | Internal Bit-slice Block Diagram 61               |

| 22. | I/O Timing Diagram                                |

| Table | <u>.e</u>                                |     |     |   |   |   |   |   |   |   |   |   | Da | age |

|-------|------------------------------------------|-----|-----|---|---|---|---|---|---|---|---|---|----|-----|

| 1.    | Allocation of Microinstruction Bits      |     | ۰   | • |   |   | • |   | ď |   | _ |   |    |     |

|       |                                          |     |     |   |   |   |   |   |   |   |   |   |    |     |

| 2.    | Rotate and Shift Destinations            | • • | o   | ۰ | ۰ | • | 0 | • | ۰ | s | 0 | e | •  | 63  |

| 3.    | Condition Codes                          |     | o   | • | • | e | • | ٠ | ۰ | ۰ | 6 | ٠ | e  | 64  |

| 4.    | Microprogram vs. Program Tradeoffs       | , . | ٠   | • | • | ۰ | • | • | n | • | 0 | • |    | 70  |

| 5.    | LPCMK Internal Register Allocation       |     | . 6 |   | • | • | • | 0 | • | ۰ | ۰ |   | ۰  | 71  |

| 6.    | FLAG Register Bit Assignment             |     |     | • | • | 0 | • |   | • | • | • | ٥ | •  | 72  |

| 7.    | LPCMK Instructions                       | •   | 0   | ٠ | • | 0 | 6 |   | • | • | 0 |   |    | 74  |

| 8.    | LPCMK Real Time LPC Generation Program . | •   | •   | ۰ | 0 | e | • | o | ۰ | ۰ | • | • | •  | 87  |

| 9.    | LPCMK Results                            |     | •   | ٥ | ۰ |   |   | • | • | a | • |   | 9  | 90  |

LIST OF TABLES

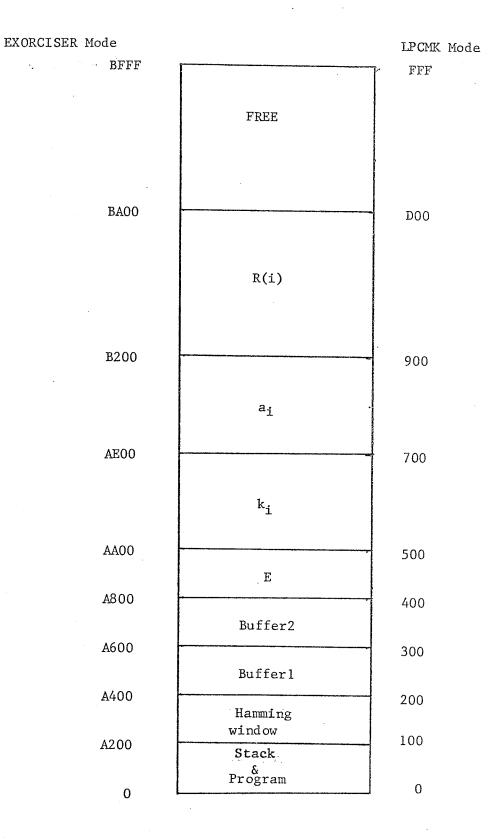

LPCMK Memory Map . . . . .

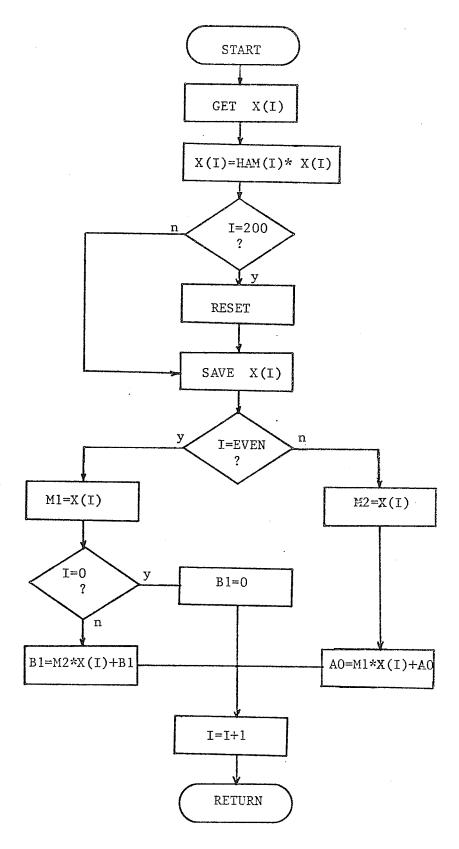

Main Program Flowchart . .

Data Acquisition Microroutine Flowchart . . .

23.

24.

25.

#### Chapter I

#### INTRODUCTION

The characteristics of the human speech signal have been vigorously studied since the 1950s. The results of work done in speech analysis have successfully been applied to telecommunications, speech synthesis, speech recognition, speaker recognition, and biomedical applications. In this work a speech research facility has been developed that enables the experimental study of linear predictive coding (LPC) of the speech signal.

The LPC data compression technique permits a reduction of the data rate of speech by a ratio of more than 30:1 [1]. This is discussed in detail in Chapter 2. This coding is performed in real time on a sampled speech signal with a specially designed bit slice processor. The algorithms chosen yield ten predictor and reflection coefficients, eleven autocorrelation values and the prediction error for every frame processed. The prediction coefficients are then used for specific purposes such as speech recognition, speech synthesis or sensitivity studies.

This document starts with a brief review of the speech signal and the LPC of speech. The pertinent algorithms are described, followed by the hardware and software description. Finally, the results of the LPC parameter generation are presented and evaluated.

### Chapter II

# LINEAR PREDICTION CODING THEORY OF SPEECH

## 2.1 THE SPEECH SIGNAL

To provide a comprehensive description of the speech signal, it is necessary to describe the production of speech and also to look at the human perception of sound. Knowledge of the physical limitations and qualities in the organs responsible for hearing and speaking yield valuable clues about modelling the system and also determine the useful information in the speech signal.

The descriptions are brief and are concerned with the organs on a physical level only.

## 2.1.1 Speech Production

The vocal organs are illustrated in Fig. 1. The lungs provide a relatively constant pressure which is 1% greater than the atmospheric pressure when a person is talking [2]. During conversation only 15% of the breathing time is typically devoted to inhaling. This contributes to the continuity of speech.

Air from the lungs passes through the larynx, where the vocal cords are located, and then out the mouth and nose. The opening created when the cords are open is known as the glottis. The portion of the vocal system between the glottis and lips, including the nose, is called the vocal tract.

Figure 1: Speech Organs

Figure 2: Glottal Pulse Spectrum from [3]

A detailed acoustic theory of the vocal tract must consider the following effects:

- a) Time variation of the local tract shape;

- b) Losses due to heat conduction and viscous friction at the vocal tract walls;

- c) Softness of the vocal tract walls;

- d) Radiation of sound at the lips;

- e) Nasal coupling; and

- f) Excitation of sound in the vocal tract.

The complete theory including all these effects is not yet available and is beyond the scope of this work. Simplifications will be made as required.

The vocal cords are responsible for modifying the air flow from the lungs before it enters the vocal tract. Here, the flow of air is modulated by articulators to produce speech. The vocal tract is approximately 17 cm long in the adult male and is deformed in cross-sectional area by the articulators; i.e., the tongue, lips, jaw, teeth and velum.

#### 2.1.1.1 Excitation

The primary source of excitation to the vocal tract are the vocal cords. Three basic types of excitation are possible; voiced, unvoiced, and plosive.

Voiced excitation is the best understood since the physical source, (the vocal cords) can be more easily monitored and measured during excitation. Voiced excitation is produced by the vocal cords vibrating at various frequencies. Sufficient air pressure is built up when the glot-

tis is closed to force the cords open. The opened vocal cords form a venturi allowing air from the lungs to flow through the glottis and then the vocal tract. Bernoulli's Law states that when a fluid (air) flows through an orifice, in this case the glottis, the pressure is lower in the constriction than on either side. Consequently when the pressure is adjusted properly on the vocal cords, a sustained vibration is created. Thus the cords will open when there is sufficient pressure and will close completely once the air flow has begun.

A sustained air oscillation can be maintained. Its period depends on the following three factors:

- a) Air pressure in the lungs;

- b) Tension and stiffness of the vocal cords; and

- c) Area of the glottis under rest conditions.

Figure 2 shows a typical glottal pulse as a triangular wave, along with its associated frequency amplitude spectrum [3]. In reality the energy in the pulse is not symmetrically distributed. In normal speech, the periodic glottal pulse frequency, also known as pitch, extends from 60 to 350 Hz. Speech sounds associated with voiced excitations include vowels such as 'e' in beet, and voiced consonants such as 'r' in zebra.

One source for unvoiced excitation is a constriction in the vocal tract or turbulent air flow around a sharp edge, such as the teeth. The resulting speech sound is a hiss-like noise, called a fricative sound. Another type of unvoiced excitation is caused by aspiration or or free flow of the air from the lung through the vocal tract. In this case, all the articulators in the vocal tract are used to shape the sound. Whispering is a common example of this excitation source. Un-

voiced excitation is noted for having a lower energy and flatter frequency spectrum than voiced excitation. These characteristics are used to distinguish between the two types of excitations.

Although unvoiced excitation could occur anywhere in the vocal tract it is assumed that all excitation is applied at the vocal cords. Another er simplification made for the sake of a reasonable speech model is that of a single excitation source. At any time, the excitation provided to the system is either voiced or unvoiced. In reality, however, there are numerous examples of mixed-source excitation models [4].

#### 2.1.1.2 Vocal Tract Model

With the above assumptions, the vocal tract is seen as the system under excitation at the vocal cords. As mentioned earlier, the articulators of the vocal tract are used to adjust its cross-sectional area and hardness to provide the speech sound. The system is time-varying and is assumed as linear to aid in speech analysis. The articulators used to alter the system are limited by their inertia in their rate of change. The vocal tract is therefore assumed stationary for 10-30 msec.

Figure 3 shows a simple model of the vocal tract as a concatenation of lossless tubes of different diameters. This model has been investigated [5] by looking at the boundary conditions and junctions between tubes of differing diameters in terms of reflected waves. The k-th reflection coefficient  $(r_k)$  is given by

$$r_{k} = \frac{A_{k+1} - A_{k}}{A_{k+1} + A_{k}} \tag{1}$$

Figure 3: Lossless Tube Model of the Vocal Tract

Figure 4: Two Tube Model of the Vocal Tract

where  $A_k$  is the cross-sectional area of the k-th tube. Since all  $A_k > 0$ , all the reflection coefficients are confined to the following range

$$-1 \leqslant r_{k} \leqslant 1 \tag{2}$$

At the acoustic frequencies under consideration the wavelengths of the sound waves are comparable to the length of the vocal tract. For the following analysis, only the frequencies between  $f = 0-4000 \, \text{Hz}$  are considered so that wave propagation can be assumed to occur in a lengthwise direction, along the vocal tract. The shortest sound wavelength  $(1_w)$  is given by

$$1_{w} = \frac{c}{f} = \frac{35000}{4000} = 8.75 \text{ cm.} \approx \frac{1}{2} 1_{v}$$

(3)

where  $\frac{1}{v}$  is the vocal tract length and c, the speed of sound is given as 35000 cm/sec.

A complete 2 tube model is shown in Fig. 4 with the frequency response  $\mathbb{V}_a$  ( $\Omega$ ) given by [5]

$$\begin{split} \mathbf{V}_{\mathbf{a}}(\Omega) &= \frac{\mathbf{V}_{\mathbf{L}}(\Omega)}{\mathbf{V}_{\mathbf{G}}(\Omega)} \\ &= \frac{.5(1+\mathbf{r}_{\mathbf{G}}) \cdot (1+\mathbf{r}_{\mathbf{L}}) \cdot \{1+\mathbf{r}_{\mathbf{1}}\mathbf{e}^{-\mathbf{j}\Omega(\mathbf{T}_{\mathbf{1}}+\mathbf{T}_{\mathbf{2}})}\}}{1+\mathbf{r}_{\mathbf{1}}\mathbf{r}_{\mathbf{G}}\mathbf{e}^{-\mathbf{j}\Omega\mathbf{2}\mathbf{T}_{\mathbf{1}}} + \mathbf{r}_{\mathbf{1}}\mathbf{r}_{\mathbf{2}}\mathbf{e}^{-\mathbf{j}\Omega\mathbf{2}\mathbf{T}_{\mathbf{2}}} + \mathbf{r}_{\mathbf{2}}\mathbf{r}_{\mathbf{G}}\mathbf{e}^{-\mathbf{j}\Omega(\mathbf{T}_{\mathbf{1}}+\mathbf{T}_{\mathbf{2}})}} \end{split}$$

Where  ${\rm V_L}$  and  ${\rm V_G}$  are the transforms of the volume velocity at the lips and the glottis, respectively,  ${\rm R_L}$  and  ${\rm R_G}$  are the reflection coefficients at the lips and glottis, respectively, and  ${\rm T_1}$  and  ${\rm T_2}$  are the times required for sound to travel through sections 1 and 2.

In the signal flow graph model to be considered all sections are assumed to be of equal length. This is valid if an adequate number of sections are used to represent the vocal tract. Thus the propagation delays in each section T are the same and the system can be modelled with an infinite impulse response (IIR) digital filter.

The lossless tube model is the same as that of Fig. 4 except that the delays  $T_1$  and  $T_2$  are the same T'. When an impluse is supplied at the glottis, the volume velocity at the lips  $(v_a(t))$  is given by

$$v_a(t) = a_0 \delta(t-NT') + \sum_{k=1}^{\infty} a_k \delta(t-NT'-2kT')$$

(5)

The soonest an impulse can reach the output is NT', where T' is the propagation time for one section and N is the number of sections. The successive reflected waves will reach the output 'ad infinitum' 2T' apart. The frequency response is

$$V_{a}(s) = \sum_{k=0}^{\infty} a_{k}e^{-s(N+2k)T'}$$

$$= e^{-sNT}\sum_{s=0}^{\infty} a_{k}e^{-s2T'k}$$

(6)

The factor

$$V_a'(s) = \sum_{k=0}^{\infty} a_k e^{-s2T'k}$$

(7)

represents the resonance properties of the system. The frequency response is obtained by replacing s with  $j\Omega$  to get

$$V_{a}'(\Omega) = \sum_{k=0}^{\infty} a_{k} e^{j\Omega k 2T'}$$

(8)

with

$$V_{a}'(\Omega + \frac{2\Pi}{2T'}) = V_{a}'(\Omega)$$

(9)

The response is periodic and, by Shannon's theorem, aliasing is avoided when sampling is done with period 2T' and all excitation is less than 1/2T' Hz.

The sampling period of 2T' makes sense intuitively since a change in the output volume velocity should only occur after a wave has undergone a backwards and then a forward reflection. This corresponds to a time of 2T'.

All information regarding the system is contained in the reflection coefficients  $r_k$  of the individual boundaries. The boundary condition at the lips  $(r_L=0)$  and glottis  $(r_G=1)$  are assumed the same as for the previous model of Fig. 4.

The choice of number of sections depends on the length of the vocal tract and the sampling rate chosen. Since the frequency response of the lossless tube is periodic, only a band of frequencies can be approximated in the model. These frequencies are given by

$$|F| < \frac{1}{(2T)}$$

T-Sampling period (10)

This requires T=2T' where T' is the one-way propagation time of a single section. With N sections giving total length 1, T'=1/cN, where c is the speed of sound.

The denominator representing the transfer function is similar to that in Eq. (4) except  $T_1 = T_2$ . The order of this denominator is N with N/2 complex conjugate poles necessary to provide the resonances in the above mentioned frequency band.

The following relationship describes the highest frequency component from the vocal tract

$$\frac{1}{2T} = \frac{1}{4T} = \frac{Nc}{4L} = \frac{N}{2} (1000 \text{ Hz})$$

(11)

This implies that there is one resonance for each 1000 Hz in a vocal tract of length 17.5 cm. A resonance of the vocal tract is known as a formant. Shorter vocal tract lengths have wider formant spacing.

In summary, the vocal tract is modelled as a linear, quasi-stationary system. The excitation is assumed to be provided at the vocal cords and the response of the vocal tract results in speech sounds. The existence of formants are successfully predicted by the theory of lossless acoustic tubes and are an important feature of the speech signal.

### 2.1.2 Speech Perception

Some understanding of the human perception of sound in general and speech in particular is important for the successful analysis of speech. Only the relevant information of the speech signal need be retained in the model. This refers directly to that which can be perceived by the ear. With better understanding of the perceptual process, speech research effort, including analysis, can be optimized. Because of the complexity of the topic, this discussion of speech perception is necessarily limited to the physical function of the hearing organs, not including the auditory nerve and detailed interpretation of sound. The hearing organs are organized into three groups depending on their location in the head. These are the outer ear, the middle ear and the inner ear. A schematic diagram of the ear is show in Fig. 5.

The outer ear is that portion outside the head to the point where the ear canal meets the eardrum. In man the ear canal is about 2.7 cm in length and is an acoustic resonator that amplifies sound waves near its resonance frequencies, usually 3-4 kHz.

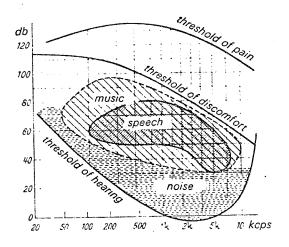

The effect of the ear canal on perception can be seen clearly in Fig. 6. The threshold of hearing shows a global minimum at about 3 kHz when subjective loudness is plotted against frequency. Zero dB is defined as the threshold of hearing for a sinusoid of 1000 Hz. At 3-4 kHz frequencies the sound pressure at the eardrum is two to four times greater than the sound pressure entering the ear canal.

The middle ear consists of the malleus (hammer), incus (anvil) and stapes (stirrup), also called the auditory ossicles. These are three small bones that mechanically link the ear drum to the inner ear. The two major functions performed by the middle ear are:

Figure 5: Hearing Organs

Figure 6: Subjective Perception

- a) Impedance transformation from the outer ear air medium to the inner ear's fluid medium; and

- b) Protection for the inner ear against sudden loud sounds.

The air-filled cavity of the middle ear is connected to the mouth cavity by the eustachian tube, which is normally closed. The pressure difference that can build up between the middle ear and surrounding air is particularily noticeable if the outside air pressure changes rapidly. Swallowing will momentarily open the tube to equalize the pressure.

The auditory ossicles are suspended by ligaments in the cavity walls. The hammer is rigidly attached on one side and covers more than one-half the eardrum area. It transmits the energy of eardrum motion to the anvil which causes a displacement in the stirrup. The total force on the stirrup acts only on the oval window, which interfaces the middle ear to the inner ear. The middle ear system acts as a lever that produces pressure on the oval window about 35 times greater than it would be otherwise.

The protective function of the middle ear prevents damage by loud noises to the inner ear, and also performs some initial processing on the signal. One mechanism is provided by two muscles reacting together in a reflex response to loud sounds. The middle of the eardrum is connected by one of the so-called tympanic muscles to the inner region of the head while another is connected to the stirrup. In response to loud sounds the eardrum is pulled in while the stirrup is pulled away from the oval window slightly. Thus the efficiency of the middle ear is reduced for louder sounds.

Contraction of the middle ear muscles increases with sound intensity so the ossicles stay in contact with each other, even at high levels. This controls distortion that might otherwise result.

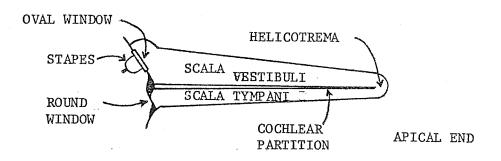

The inner ear consists of the cochlea, vestibular apparatus (not normally used for detecting audio vibrations) and the auditory nerve termination. The cochlea is normally coiled like a snail shell in a flat spiral of 2 1/2 turns. The cochlea is schematically shown in Fig. 7 as if it were stretched out. The chamber is filled with a colorless liquid and the length of the canal in the spiral conch is about 35 mm. The cross-sectional area at the stirrup end is about 4 mm<sup>2</sup> and the area decreases to about 1 mm<sup>2</sup> at the tip. The partition in the center is filled with a different liquid and is bounded by a bony shelf, a geletinous membrane called the Basilar membrane and another membrane known as Peissner's membrane.

The inner ear is connected to the stirrup at the oval window. When vibrating, the stirrup acts as a piston producing a volume displacement of the cochlea fluid. Since the cochlea is essentially rigid and the fluid is incompressable, the round window serves to absorb the fluid displacement. Among the cells residing in the Basilar membrane partition are approximately 3000 sensory (hair) cells on which the auditory nerve endings terminate. Since the Basilar membrane is stiffer and less massive at its narrow basal end and more compliant and more massive at the broad end, its resonant properties vary continuously along its length.

Very slow vibrations of the stapes (less than 20 Hz) result in a back-and-forth motion of the fluid of the scala vestibuli and the scala

Figure 7: Schematic Illustration of the Cochlea Unrolled

Figure 8: Basilar Displacement

tympani through the opening at the helicoptrema. At higher frequencies, vibrations are transmitted through the yielding cochlea at points which depend on the frequency content of the signal.

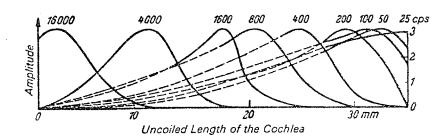

The relative displacements of the Basilar membrane, normalized to one, are shown graphically in Fig. 8 for different sinusoidal frequencies. It should be noted that the displacements for the Basilar membrane at the different frequencies have roughly the same Q. This explains why frequency differentiation is more selective for lower frquencies and time resolution is better at higher frequencies. More recent measurements [3] suggest that the mechanical response is somewhat dependant on sound intensity.

The range of frequencies perceived by the ear are depicted in Fig. 6 Typically frequency perception extends from 50-16,000 Hz. It is interesting to note that the lowest frequency heard has a period very close to the pseudostationary period of the vocal tract, 20 msec. Events that happen slower than 20 msec apart appear to the listener as time-separated while those which are quicker are distinguished in the frequency domain.

When white noise is applied to a subject's ear the uncertainty of frequency differentiation is greater than that for sinusoids. The maximum information content in terms of frequency and loudness is found between 700 and 5,000 Hz and does not increase with loudness as it does for sinusoids. Perception tests done with noise are more applicable to speech because a pure sine wave is almost never encountered in speech.

The basic assumptions of the speech model which have been justified from the point of view of both the ear and vocal organs are:

- a) Pseudostationary for 20 msec; and

- b) Bandlimited to 1/2T < 4 kHz.

### 2.2 LINEAR PREDICTIVE CODING THEORY

Linear Predictive Coding is widely used as an efficient means of representing a complex speech signal by a small number of parameters. Typically the reduction in data using LPC is about 30:1. A typical LPC vocoder [6] reduces the data rate necessary for speech transmission to 2400 BPS (Bit Per Second). This is a source coding method where only the parameters for the model of the vocal tract are calculated. The excitation, voiced or unvoiced, and the gain must be calculated separately for the reconstruction of speech from the parameters.

## 2.2.1 The LPC Model

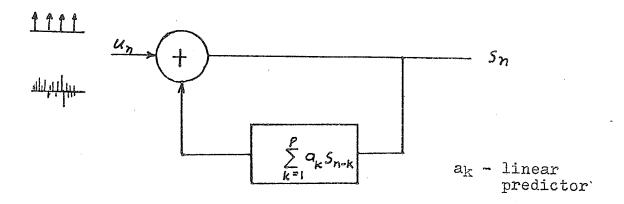

The justification for the use of LPC is that a linear combination of past samples of the speech signal can be used to predict the next value. In the most general case for linear prediction, the past and present inputs are also used to predict the next value. This is a time domain method which depends on the pseudostationary linear model of the vocal tract shown in Fig. 9.

The all-pole model which is used is also known as the autoregressive model. It can be justified on the basis of perceptual effects of removing the zeros or anti-resonances from the speech signal.

With non-nasal sounds the vocal tract transfer function has no zeros. For these sounds, therefore, zeros are not necessary. With unvoiced and nasal sounds, the zeros lie within the unit circle in the z-plane.

Figure 9: LPC Model

Thus, they can be approximated with arbitrary accuracy by multiple poles in the transfer function denominator [5]. In most cases the zeros contribute only to spectral balance by affecting the formant bandwidth or energy distribution. The formant locations are determined solely by the poles.

It was noted in Sec. 2.1.2 that one resonance will exist per 1000 Hz in a vocal tract of length 17.5 cm. As a rough measurement, it is sufficient to obtain two poles to represent the influence of the glottal flow and radiation of the speech wave and two poles for each resonance. The effect of zeros is not normally considered here. Therefore, if the signal is bandlimited to 4 kHz, approximately 10 predictor coefficients are needed.

### 2.2.2 LPC Parameter Generation

The signal s can be described at any time as a linear combination of P past values and the present input u for the all-pole model. This is shown by

$$s_n = \sum_{k=1}^{P} a_k s_{n-k} + Gu_n$$

(12)

where  $\mathbf{a}_{\mathbf{k}}$  are the predictor coefficients and G is the gain. The system transfer function reduces to

$$H(z) = \frac{G}{P + \sum_{k=1}^{p} a_k z^{-k}}$$

(13)

which can be realized by a digital infinite impulse response (IIR) filter.

The approximated signal s' is obtained by a linearly weighted sum of the past values and is shown as follows

$$s_n' = \sum_{k=1}^{P} a_k s_{n-k}$$

(14)

The resulting error  $e_n$  known as the residual is described by

$$e_n = s_n - s_n' = s_n + \sum_{k=1}^{p} a_k s_{n-k}$$

(15)

The residual must be minimized to get the LPC coefficients.

A deterministic instead of a random signal is assumed, allowing results to be expressed in terms of actual rather than expected values. The method of least squares is almost universally used for minimizing the error. This method is expressed as

$$E = \sum_{n} e_{n}^{2} = \sum_{n} (s_{n} + \sum_{k=1}^{p} a_{k} s_{n-k})^{2}$$

(16)

$$\frac{\partial E}{\partial a_i} = 0 \qquad 1 \le i \le P \tag{17}$$

where E is known as the error signal energy. The solution yields the normal equations shown below, in which the range of summation has not yet been defined.

$$E_{p} = \sum_{n} s_{n}^{2} + \sum_{k=1}^{P} (a_{k} \sum_{n} s_{n}s_{n-k})$$

(19)

For any set of signals  $s_n$ , there will be P equations in P unknowns that can be solved for the predictor coefficients  $(a_k)$ . The range of summation is specified for two cases, which yield two distinct methods for estimating the parameters.

#### 2.2.2.1 Autocorrelation Method

With this method the error is minimized over all time, -  $\infty <$  n <  $\infty$  . The solution for the normal equation is

$$\begin{array}{ccc}

P & & & \\

\Sigma & a_k R(i-k) = -R(i) & & 1 \leqslant i \leqslant P

\end{array}$$

(20)

$$E_{p} = R(0) + \sum_{k=1}^{p} a_{k}R(k)$$

(21)

where

$$R(i) = \sum_{n=-\infty}^{\infty} s_n s_{n+i}$$

(22)

is the autocorrelation function of  $s_n$ . We can see that R(i) = R(-i), is an even function of i.

The autocorrelation matrix formed by the R(i-k) in Eq. (20) is a symmetric Toeplitz matrix. All terms along each diagonal are the same. This is important when considering solutions for the predictor coefficients.

Since the signal is generally known only over a finite interval, 0 to N-1, a window function multiplies the signal so it is zero outside the known interval. This can be expressed by

$$S_{n}' = \begin{cases} s_{n}^{w} & 0 \leq n \leq N-1 \\ 0 & \text{otherwise} \end{cases}$$

(23)

where s' is the windowed signal and w is the window function. The autocorrelation then becomes

$$R(i) = \sum_{n=0}^{N-1-i} s_n \cdot s_{n+i}^{\ell} \quad i \geqslant 0$$

(24)

#### 2.2.2.2 Covariance Method

With this method error is minimized over the finite interval  $0 \leqslant n \leqslant N-1$ , giving the normal equations

$$\begin{array}{c|cccc}

P & & & & \\

\Sigma & a_k \zeta_{ki} &= \zeta_{0i} & & & 1 \leqslant i \leqslant P

\end{array}$$

(25)

$$E_{p} = \zeta_{00} + \sum_{k=1}^{p} a_{k} \zeta_{0k}$$

(26)

where

$$\zeta_{ik} = \sum_{n=0}^{N-1} s_{n-i} s_{n-k}$$

(27)

which is the covariance of the signal  $s_n$  over the given interval. Note that the P samples preceding the frame under consideration are necessary to compute the covariance. The  $f_k$  in Eq. (25) form the covariance matrix which is symmetric, but not Toeplitz.

The covariance method reduces to the autocorrelation method as N goes to infinity. Also note that windowing is not necessary over the frame since error is minimized only over the interval considered.

### 2.2.2.3 Lattice Formulations

This class of methods combine the autocorrelation and covariance methods. With these methods the predictor coefficients are obtained directly from the speech sample. There is no need for an intermediate correlation matrix to be calculated. Also, stability of the filter yielded is guaranteed without use of a window.

## 2.2.3 Comparison of Methods

The number of multiplications required for computation of the autocorrelation and covariance methods are similar if N >> P where N is the

number of samples considered in the frame and P is the number of predictor coefficients. A modified lattice method exists that obtains the

partial correlation coefficients, also called PARCOR or reflection coefficients, with the same computational efficiency as the covariance method [5]. However, this method requires more calculation to obtain the

parameters. Therefore, to obtain the predictor parameters it is less

efficient.

Stability is also an important criterion in the choice of a method.

The LPC model can be described in the z-plane as

$$H(z) = \frac{G}{A(z)} \tag{28}$$

where

$$A(z) = 1 - \sum_{k=1}^{P} a_k z^{-k}$$

(29)

This system is stable if the zeros of A(z) are inside the unit circle in the z-plane.

The parameters obtained by the covariance method could result in an unstable filter; i.e. stability is not guaranteed by this method. The

poles, which are located outside the unit circle for an unstable filter, could be reflected inside to obtain a stable filter with the same frequency response. This approach, however, results in increased computation time.

For the lattice method the filter obtained by the resulting predictor polynomial is guaranteed to be stable since the predictor coefficients are obtained from the PARCOR coefficients which, by definition, are stable.

The autocorrelation method was chosen because of its efficient calculation and the fact that the resulting filter is theoretically guaranteed to be stable. Care must be taken in the calculation since finite register length effects might cause an unstable filter. When the speech signal is spectrally flattened these undesirable effects are minimized. Therefore, with spectral pre-emphasis, a stable filter will result with smaller register lengths. This is discussed in more detail in Chapter 5.

The test of the PARCOR coefficients to ascertain the following relation

$$-1 \leqslant k_{i} \leqslant 1 \tag{30}$$

is necessary and sufficient to ensure stability [5]. It will be shown that PARCOR coefficients are a byproduct of the recursive relation, known as Durbin's algorithm, used to calculate the LPC coefficients.

#### Chapter III

#### ALGORITHM DESCRIPTION

Meeting the objective of using the autocorrelation method in real time requires that all calculations be done within the time period of a single frame. Algorithm selection is based on efficiency of calculation and the information provided at completion. The following three main transformations are performed on the data, as required by the autocorrelation method:

- a) Windowing;

- b) Autocorrelation matrix calculation; and

- c) Parameter generation.

These are discussed in some detail below, with justification given for the method used.

#### 3.1 WINDOWING

It was shown in Sec. 2.2.2.1 that since the signal is known only for samples 0 to N-1, windowing in the form of Eq. (23) is necessary. The simplest window considered is the rectangular window, given by

$$W_{n} = \begin{cases} 1 & 0 \le n \le N-1 \\ 0 & \text{otherwise} \end{cases}$$

(31)

Use of this window to obtain predictor coefficients results in a very large prediction error at the start of and immediately following the frame. This can be seen by looking at Eq. (14) repeated below.

$$s_{n}' = \sum_{k=1}^{P} a_{k} s_{n-k}' -\infty < n < \infty$$

(14)

For n=0 the  $s_n$  are predicted using the past P values which have been set to zero by  $w_n$ . The estimated value is zero, but it is very unlikely that the actual value will be zero, resulting in a large prediction error. After the first P values are predicted the error will generally become smaller since the actual signal values are used to predict the next value.

A similar argument is used for prediction of samples past N-1. According to the window these values should be predicted to be zero, but this is unlikely since the preceding P values are used to predict them.

The rectangular window yields large errors at the beginning of the speech frame and is considered unsuitable for use with the autocorrelation method. Effects of the edges can be minimized by de-emphasizing samples near the edges with the use of a different window. A Hamming window was chosen with its mathematical expression as follows

$$W_{n} = \begin{cases} 0.54 - 0.46 \cos(\frac{2\pi n}{N-1}) & 0 \le n \le N-1 \\ 0 & \text{otherwise} \end{cases}$$

(32)

The use of this window gradually reduces the weight applied to the samples as the edge of the frame is approached.

The frame length N chosen is an important consideration. If the window doesn't encompass at least one pitch period the error can vary dramatically, depending on the position of the window with respect to the pitch period. A window which is too long will cause variations in the voice signal to be lost. It is good practice to include 2-3 pitch periods in the frame but this is a difficult estimation to make.

For a female voice the period can be 2 msec and for a low-pitched male 25 msec. A 20 msec frame was chosen resulting in 200 samples per frame at 10 kHz sampling rate. Therefore, a 200 point Hamming window will be used and is illustrated in Fig. 10. Other reasons for choosing this sampling rate are discussed in Chapter 6.

Figure 10: 200 Point Hamming Window

## 3.2 AUTOCORRELATION CALCULATION

The short time autocorrelation R(k) is calculated using the Hamming windowed samples. This is defined by

$$R(k) = \sum_{m=0}^{N-1-k} \{x(m) \ w'(m)\} \{x(m+k) \ w'(m+k)\}$$

(33)

The values for R(k),  $0 \le k \le P$  are necessary for the autocorrelation method. Using the above definition, approximately (P+1)N multiplications are required for P << N, not including windowing. R(k) has some useful properties, some of which can be exploited in the calculation. These properties are:

- a) It is an even function, R(k) = R(-k);

- b) Maximum value is at k=0 i.e.  $|R(k)| \le R(0)$ ; and

- c) R(0) is the energy in the frame.

For each lag m=0 it was noted by Blankenship [5] that most of the input samples appear twice as multiplicands in the calculation. For k=1 this is illustrated as follows

$$R(1) = x(0)x(1) + x(1)x(2) + x(2)x(3) + x(3) x(4) + ...$$

$$= x(1)(x(0) + x(2)) + x(3) (x(2) + x(4)) + \dots$$

(34)

Except for k=0 the number of multiplications are reduced by approximately 1/2 resulting in about (1+P/2)N multiplications where P << N.

Kendall modified Blankenship's algorithm for use, recursively, with the unmodified short time autocorrelation defined by

$$R(k) = \sum_{m=0}^{N-1-k} x(m)x(m+k)$$

(35)

where x is the windowed signal. N is required to be even for this algorithm and so was previously set to be 200.

Kendall's algorithm is used for its computational efficiency and is expressed below

$$R(k) = \sum_{m=0}^{(N-k)/2-1} \{x(2m) + x(2m+k+1)\} \{x(2m+k) + x(2m+1)\}$$

$$-A(k) - B(k)$$

for even k (36)

$$R(k) = \sum_{m=0}^{(N-k-1)/2-1} \{x(2m) + x(2m+k+1)\} \{x(2m+k) + x(2m+1)\}$$

$$-A(k) - B(k) - x(N-1-k)x(N-1) \text{ for odd } k$$

where A(k) and B(k) are obtained recursively, (37)

$$A(k) = A(k+2) + x(N-2-k)x(N-1-k)$$

for even k (38)

$$B(k) = B(k+2) + x(k)x(k+1)$$

for even k (39)

$$A(k) = A(k+1)$$

for odd k (40)

$$B(k) = B(k+2) + x(k)x(k+1)$$

for odd k (41)

It is convenient to evaluate R(k) from k=0 to k=P to ascertain the need for and to perform normalization. This is used to prevent overflow

and will be discussed later. When starting the algorithm at k=0, A(0) and B(0) are needed first. The expansion of the recursive relation is shown as

$$A(0) = x(0)x(1) + x(2)x(3) + ... + x(N-2)x(N-1)$$

(42)

$$B(0) = x(N-2)x(N-1) + x(N-3)x(N-4) + ... + x(1)x(0)$$

(43)

Thus A(0) = B(0) will be the initial condition for a modified recursive relation where k is even. This is shown as

$$A(k) = A(k-2) - x(k-2)x(k-1)$$

k is even (44)

$$B(k) = B(k-2) - x(N-k+1)x(N-1)$$

k is even (45)

For k=1, we have

$$A(1) = A(0) \tag{46}$$

$$B(1) = x(N-3)x(N-2) + x(N-5)x(N-4) + \cdots + x(1)x(2)$$

(47)

For k odd the modified relation is

$$A(k) = A(k-1) \quad \text{for } k \text{ odd}$$

(48)

$$B(k) = B(k-2) - x(N-k+1)x(N-k)$$

for k odd (49)

#### 3.3 PREDICTOR SOLUTION

The normal equations are presented below in matrix form for the autocorrelation method.

The autocorrelation matrix and the right hand side are known using Kendall's algorithm to solve for the first P lags. The matrix' being symmetric Toeplitz led to the development of Durbin's recursive solution [5]. To date this is the most efficient algorithm known for solution of the predictor coefficients  $a_k$ . Although the primary objective of solving for the  $a_k$  is met, other valuable information is obtained with this algorithm. The PARCOR, prediction coefficients and the total mean squared error E are yielded. Durbin's algorithm is expressed below as

$$E^{(0)} = R(0) \tag{51}$$

$$k_1 = \frac{R(1)}{E(0)} \tag{52}$$

$$E_1 = (1-k_1^2) E^{(0)}$$

(53)

$$k_{i} = \frac{\begin{cases} R(i) - \sum_{j=1}^{i-1} (i-1) \\ j=1 \end{cases}}{(i-1)}$$

(54)

$$a_{i}^{(i)} = k_{i}$$

(55)

$$a_{j}^{(i)} = a_{j}^{(i-1)} -k_{i}a_{i-j}^{(i-1)} \qquad 1 \le j \le P$$

(56)

$$E^{(i)} = (1-k_i^2) E^{(i-1)}$$

(57)

These equations are solved recursively for i=2,3,...P with the final solution given by

$$a_{j} = a_{j}$$

$$1 \le j \le P$$

(58)

It can be seen that the solution for predictor coefficients of all orders less than P have been obtained.

System stability can be easily monitored by checking the PARCOR coefficients  ${\bf k_i}$  as they are calculated, so that  $-1{\leqslant}k_{\dot{\bf i}}{\leqslant}1$  holds.

The following data are saved for each frame processed:

- a) Predictor coefficients for order P;

- b) PARCOR coefficients  $k_1$ ,  $k_2$ , ...  $k_p$ ; and

- c) Total mean squared error for frame  $\hbox{E.}$

# 3.4 COMPUTATIONAL CONSIDERATIONS

The number of calculations are considered on the basis of using the autocorrelation method with 10 predictor coefficients. For large N the number of multiplications required for the autocorrelation solution far exceeds that of the predictor coefficient solution, even when Kendall's algorithm is used. Subtractions are considered computationally the same as additions and divisions the same as multiplications.

With N=200, about 1500 multiplications per frame must be done requiring the performance of 75,000 multiplications per second. A very important aspect of the computational procedure is that of data shuffling. This is optimized as described later to reduce the time required.

#### Chapter IV

#### SYSTEM OVERVIEW

Implementation of the algorithms is done with a specially designed processor which will henceforth be called the LPCMK. The system has been designed so as to achieve the following two objectives:

- a) Speed of operation; and

- b) Flexibility.

Speed is important because of the amount of calculation and data shuffling required for real time operation. Sufficient flexibility must exist to meet the objective of a speech research facility. If the LPCMK were dedicated to a single task the research potential would be too limited.

## 4.1 THE BIT SLICE APPROACH

To meet the speed requirements, the use of standard microprocessors would require the implementation of parallel processing. An alternative approach was chosen with the design of a special purpose processor.

Bit slice components are used which have the following major advantages over standard microcomputers:

- a) The processor architecture can be tailored to meet the user's needs;

- b) The instruction set is defined by the user; and

- c) Instruction execution is much faster.

Any standard microprocessor will have a fixed instruction set, fixed architecture, and be slower than a bit slice processor. The major disadvantage of the bit slice approach is the higher cost in terms of power consumption, development time, and component cost.

In a typical bit slice processor, including the LPCMK, there are two levels of instructions. The most primitive are microinstructions, each of which is 48-bits wide in LPCMK. A program using a series of microinstructions is referred to as a microprogram. A program level instruction is used to call a microprogram. Access to operands is controlled by the microprogram, whose function and length depend totally on the users definition.

#### 4.2 SYSTEM HARDWARE

## 4.2.1 Components

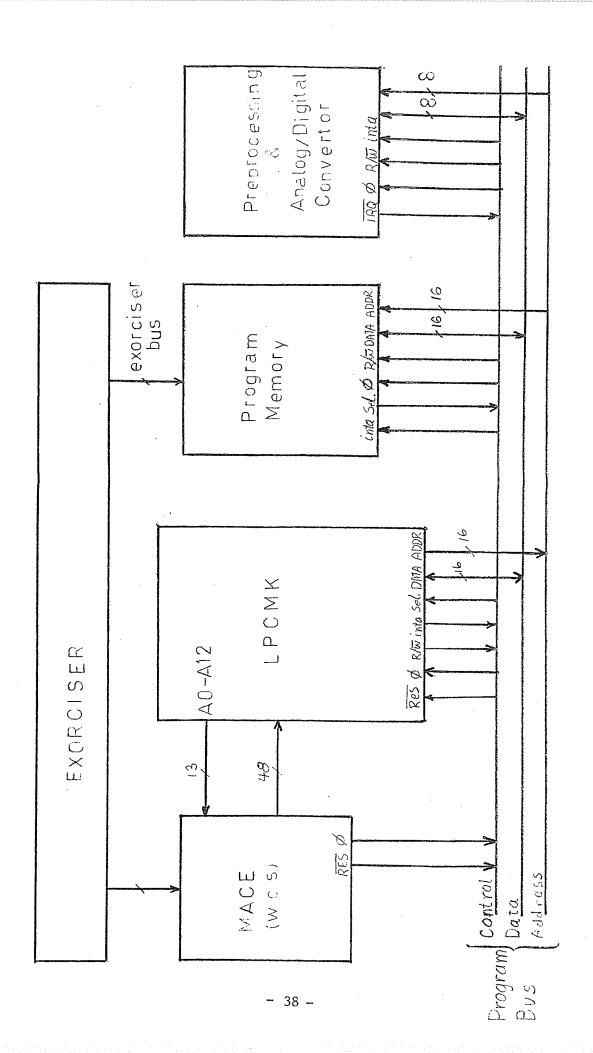

A block diagram of the system configuration is shown in Fig. 11. It consists of the Motorola Mace development system, including the EXORcisor, the LPCMK, the program memory, and the preprocessor with analog to digital converter (A/D). The latter three items each occupy one standard S-100 wirewrap protoboard.

The Mace functions as a very fast (50 nsec access time) writeable control store (WCS) for the LPCMK's microinstructions. After program development the Mace can be replaced with PROM memory, which is normally just as fast.

The LPCMK is the complete bit slice processor. When operating, it supplies addresses to the Mace to access the microinstructions. These microinstructions determine the operation of the LPCMK, which include

Figure 11: System Hardware Configuration

fetching data and instructions from the program memory. Also, the LPCMK fetches data from the A/D converter and processes it.

The program for the LPCMK and results of the computations are stored in the program memory. Various buffers used during program and microprogram execution are also located in the program memory. This memory is accessed by the EXORciser as well for the purpose of loading the program and data input and output (I/O).

The preprocessor with A/D converter supplies speech samples to the LPCMK. When the analog speech signal has been converted to digital form, an interrupt request is sent to the LPCMK indicating the data is ready. One sample of speech data can then be accessed by the LPCMK.

#### 4.2.2 System Hardware Operation

There are two operational modes for the system. They are the EXOR and the LPCMK mode. These modes are selected by the combination of a switch setting on the program memory card and the MBUG software, which is discussed in Sec. 4.3.

The EXOR mode allows the Motorola EXORcisor to access the program memory and the Mace WCS. During microprogram development, the Mace is loaded with microinstructions and the program memory is loaded with the program, including constants, from the EXORciser. After the LPCMK program has been executed, the results are read from the program memory in this mode.

While in the EXOR mode the LPCMK data bus and address bus lines are tri-stated. The EXORciser then has control over the program memory since the LPCMK address is disabled.

The LPCMK is the bus master when the LPCMK mode is chosen. The EXOR-ciser bus is tri-stated and the LPCMK accesses the program memory, pre-processor and A/D. The LPCMK address is enabled allowing microprogram operation. Data is acquired and processed to yield LPC coefficients in this mode.

## 4.3 SYSTEM SOFTWARE OPERATION

Microprogram development is facilitated by use of the Motorola microassembler called MASM [7]. The first step requires the creation of a

definition file in which the desired bit fields are assigned to mnemonics or labels defined by the user. These mnemonics are then used in microprogram development to build the microinstruction. In assembly of

the microprogram reference must be made to the appropriate definition

table, which is created by assembly of the definition file.

The assembled program is then loaded into the Mace and operated by the Motorola program MBUG [7]. MBUG controls the system clock and reset and enables the LPCMK address to the Mace WCS.

## Chapter V

#### HARDWARE DESCRIPTION

The system described in Chapter 5 consists of the following components:

- a) Preprocessor with A/D converter;

- b) Program memory;

- c) LPCMK bit-slice processor; and

- d) EXORciser with Mace development system.

In this Chapter the first 3 items are described in detail. The Mace is considered in [7].

## 5.1 PREPROCESSOR AND A/D CONVERTER

## 5.1.1 Preprocessor

The preprocessor is responsible for converting the approximately 10 mV peak-to-peak analog signal from the microphone into a useable form for the A/D converter. The three aspects which must be considered in the analog processing are:

- a) A sufficient signal voltage must be applied to the A/D converter;

- b) Bandlimiting of the signal to |F| < 1/|2T|, where T is the sampling period, is necessary to avoid aliasing; and

- c) Spectral pre-emphasis is desireable to spectrally flatten the signal spectrum.

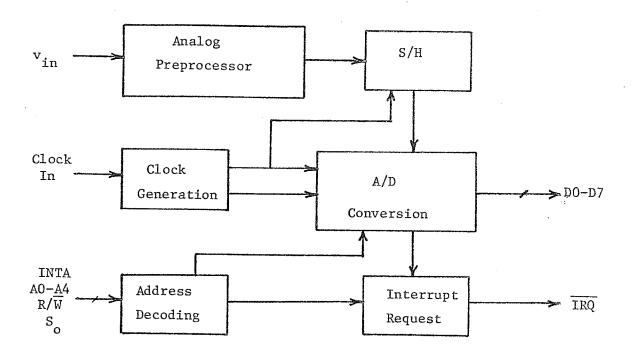

A block diagram of the entire preprocessor and A/D conversion is shown in Fig. 12 and the circuit schematic can be found in Appendix 1.

The first stage consists of an amplifier with a gain Av=Vo/Vi=1000. This supplies the antialiasing filter with a  $\pm 5$  V maximum input signal.

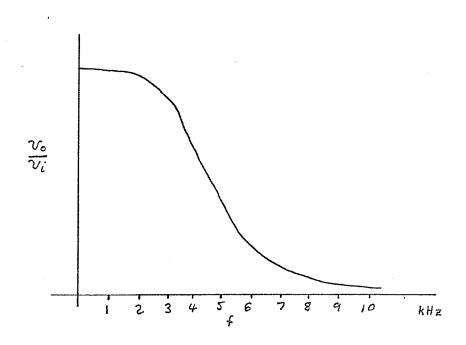

A VCVS two stage, four pole Butterworth Salient-Key filter was chosen for the antialiasing filter. This is suitable for use with speech processing because it has no ripple in the pass band. The 3 dB point is set at 3.5 kHz to assure sufficient band limiting. To avoid aliasing an insignificant amount of signal energy must exist above 5kHz. The spectrum amplitude obtained is shown in Fig. 13. It was shown in Sec. 2.1.1 that there is approximately one formant for each 1000 Hz in the vocal tract. The signal used will therefore contain about 4 formants.

It was previously stated in Sec. 2.3.4 that spectral pre-emphasis aids in reducing roundoff error when computing the autocorrelation [5]. This was found to be unnecessary with the word lengths used when the results were examined. These are presented in Chapter 8. The study of these effects is not included in the scope of this work, but will be mentioned in Sec. 6.1 when the software implementation is considered.

Figure 12: Preprocessor and A/D Block Diagram

Figure 13: Preprocessor Frequency Response

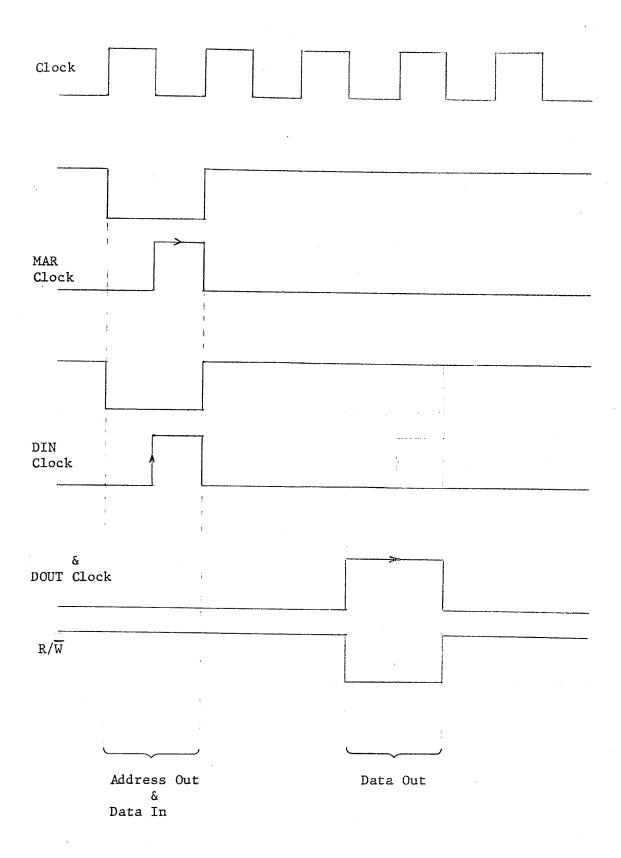

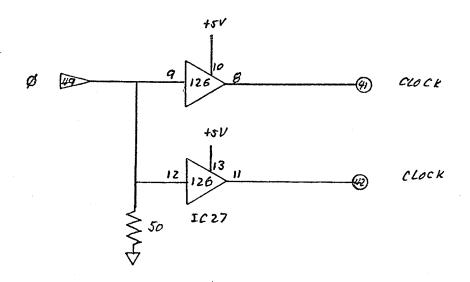

#### 5.1.2 Sampling

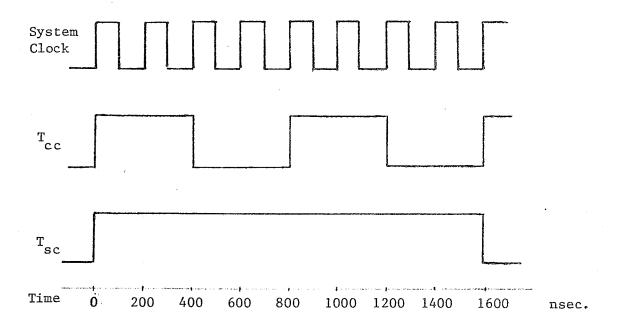

Although the signal is band limited to f<4000 Hz, a sampling rate of approximately 10kHz was chosen. At this rate, aliasing is avoided with a safety margin. Also, as a matter of convenience, the conversion clock Tcc is obtained from the system clock Tsy which has a period of 200 nsec. A conversion clock of 625 kHz was used. This is obtained by Tcc=Tsy/8, implemented with a simple frequency divider. The start-of-conversion clock Tsc resulted from the following relation.

Tsc = Tcc/4 · Tcc/8 · Tcc/10 · Tcc/32 · Tcc/64 (59)

This was implemented with a logical AND gate and resulted in a start-ofconversion pulse Tsc lasting 2Tcc sec every 102.4 usec. This relation

is shown in Fig. 14. The timing is required for the A/D converter chosen. The actual sampling rate is 9,766 Hz.

According to Fig. 15, a sample and hold (S/H) is required for the 4 kHz signal since the conversion time is 64 usec at the chosen conversion clock period. The aperture time of a 4 kHz signal is 300 nsec. Sample acquisition is triggered by Tsc.

The leading edge of the end-of-conversion signal  $\overline{EOC}$ , from the A/D converter triggers the interrupt request circuitry  $\overline{IRQ}$ . This signal is applied to the LPCMK program bus. When the LPCMK system is operating, the  $\overline{IRQ}$  is responded to with an interrupt acknowledge, INTA. This procedure is illustrated in Fig. 16. The A/D is port-mapped, so the converter's address is provided with the INTA, enabling the tri-state output buffer. Digital speech data is then read by the LPCMK at the same time the  $\overline{IRQ}$  is reset.

Figure 14: A/D Conversion Timing Diagram

Figure 15: Aperture Time from [18]

Figure 16: Interrupt Response Timing

A digital to analog D/A converter is provided and is used for testing the A/D converter.

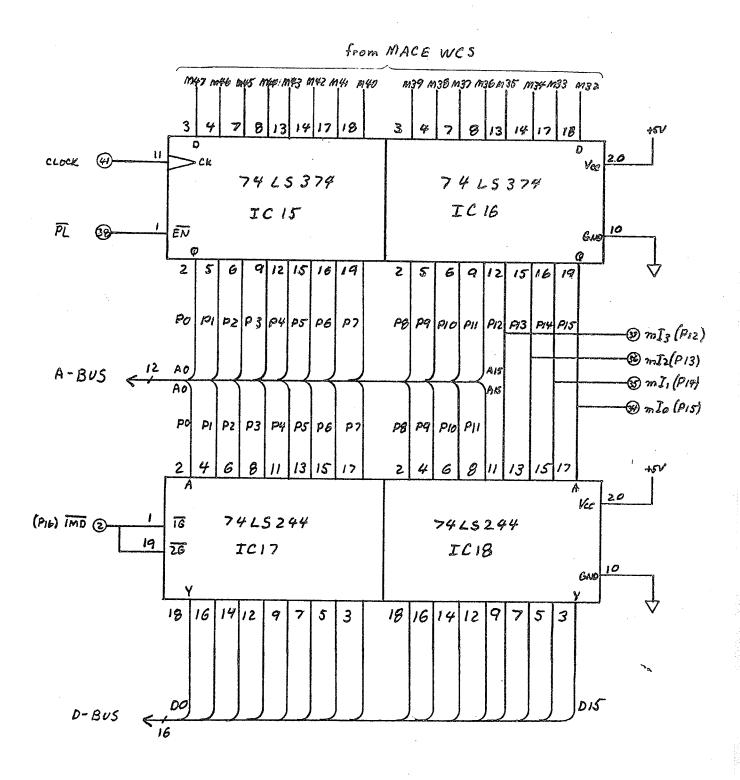

#### 5.2 PROGRAM MEMORY

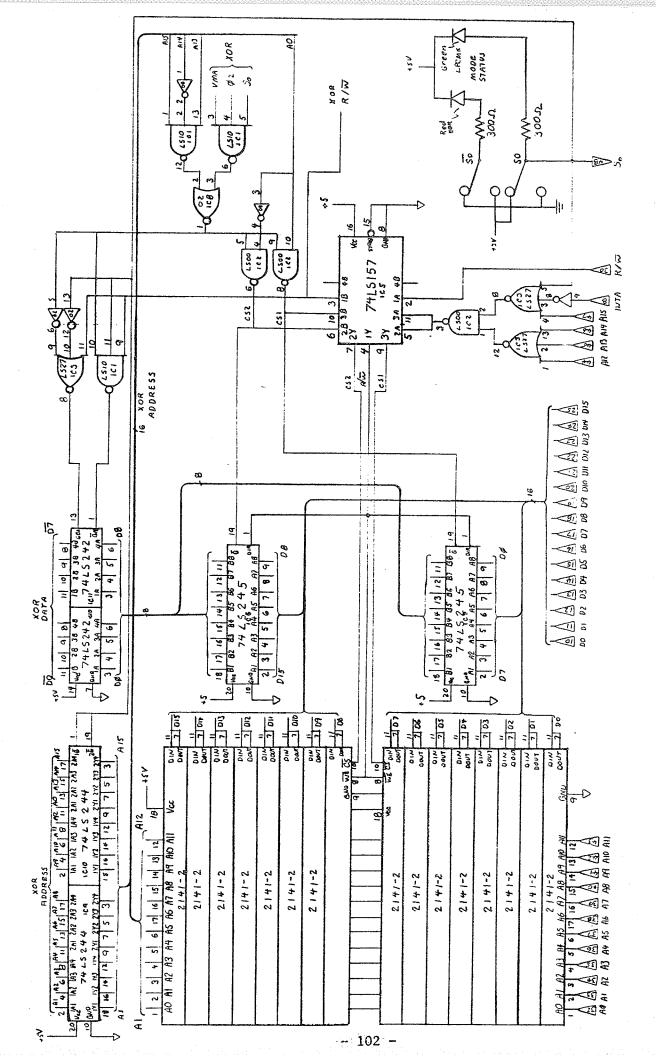

The program memory is accessable from both the EXORciser microcomputer and the LPCMK. A switch is provided on the memory board to chose its mode of operation. This select signal is applied to the LPCMK program bus and serves to tri-state the LPCMK address and data bus when the EXOR mode is selected. A block diagram of the memory is shown in Fig. 17 and its schematic diagram is located in Appendix 1.

An important consideration is the data bus size difference between the EXORciser and the LPCMK. The former uses a standard microprocessor, the M6800, that requires an 8 bit data word and the LPCMK has a 16 bit data word. This disparity is resolved by use of tri-state bus transceivers for the EXORciser interface. The program memory is divided into two 4K x 8 bit banks which are alternately chosen by the EXORciser. The data bus of the LPCMK is tied directly to the memory data pins.

The memories used were 4K X l static RAMs with 120 nsec access times. This speed is sufficient to enable data access in one clock cycle of the LPCMK. To get the required 16 bit data width, 16 devices are needed. When the EXOR mode is chosen the LSB (Least Significant Bit) of the EXORciser's address is used with the chip select circuitry. This allows a 16 bit word accessed by the LPCMK to appear as two consequtive 8-bit words in the EXORciser's address space for ease in interpreting data.

The EXORciser bus is used directly by the memory, which is mapped to A000 - BFFF hexadecimal for the EXORciser. For the LPCMK the memory ap-

Figure 17: Program Memory Block Diagram

pears from 000-FFF hex, representing 4K words. This is adequate for storing over 2 seconds of predictor coefficients, autocorrelation values, PARCOR coefficients and error values.

The memory write and read timing is described in Sec. 5.3. A memory test program was written for EXORciser operation which requires 10 hours to run. A similar memory test program was written for the LPCMK that has a 4 minute execution time illustrating the speed advantage of the bit-slice approach. These test programs can be seen in Appendix 3 with accompanying flow charts.

## 5.3 THE LPCMK

The processor is the heart of the LPC research facility. Because of the advantages with the bit-slice approach, real time parameter generation is possible. The specially designed processor, called the LPCMK, is described here. One of the advantages mentioned for the bit-slice approach is the flexibility in architecture design. The following features are included in the LPCMK:

- a) A 48 bit wide microinstruction word;

- b) A 16 bit internal and external data bus;

- c) A 16 bit external address bus; and

- d) Single level interrupt servicing.

The major sections of the LPCMK are as follows:

- a) Pipeline Registers;

- b) Microinstruction Sequencer with immediate data buffers;

- c) Bit-slice ALU and register set (also called the bit-slice unit) with shift logic;

- d) Status register;

- e) I/O registers; and

- f) Mapping PROM and Vector Register.

The components are discussed in detail following a description of bitslice processor operation. The circuit schematic for each section is

shown in Appendix 1.

## 5.3.1 Bit Slice Processor Operation

All events in the bit-slice processor are triggered by the leading edge of the system clock. This clock is provided by the Mace and was chosen to be 5MHz with a 50% duty cycle. A single clock period is the time required for the execution of one microinstruction. The devices used are static and so will not lose their state if the clock is stopped. This is valuable for program or hardware debugging. The standard procedure of inserting software interrupts where breakpoints are desired need not be applied.

A block diagram of a typical system is shown in Fig. 18. Since all events are started at the rising clock edges it is necessary for the combinational actions of the processor to settle before the next clock pulse arrives. Therefore the longest combinational signal path determines the maximum clock rate and hence the time required for each microinstruction.

Pipelining refers to the overlapping of events in time to reduce the total execution times. The location of pipelining registers determine the processor operating characteristics. In Fig. 18, the Instruction, Data and Address pipeline registers are shown at typical locations. If

1 , 2 , 3 , 4 Combinational delay paths.

Figure 18: A Typical Bit-Slice System Block Diagram

all three were used, the shortest clock period would depend on the longest delay path, possibly the microinstruction memory access time. Any combination of these three could be used providing different characteristics for operation [8].

An Instruction-Data architecture is used requiring the following two sets of registers:

- a) Instruction registers which receive and hold the microinstruction from the microinstruction memory; and

- b) Data Registers having the two purposes listed below;

- i) Registers holding data from the previous operation are located in the AMD2901 ALU; and

- ii) Status Registers that contain the status of the previous ALU operation or other information available at the previous clock edge.

The architecture chosen effectively causes an increase in the maximum clock speed permitted. The actual increase depends on the specific microinstruction being executed since not all propogation delay paths are The major limitation in speed is that of the Mace WCS which has a 50 nsec access time. The memory is emitter coupled logic which is very fast. This, plus the delay of the microinstruction sequencer gives a minimum delay of about 120 nsec. The Mace provides the system clock in increments of 25 nsec with a 50 % duty cycle. Operation at periods of 175 nsec was possible before system failure. The processor was observed to fail with a 150 nsec clock period when performing the memory test program.

A clock period of 200 nsec was chosen to avoid electromagnetic noise problems on the LPCMK program bus. This is adequate for performing LPC in real time and allows program memory access in one microinstruction period.

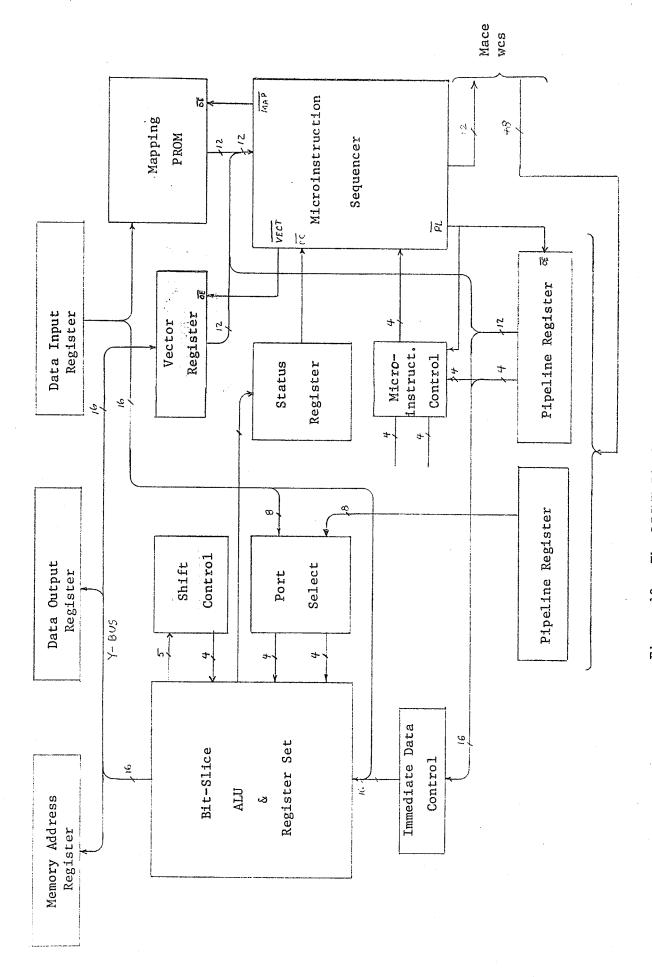

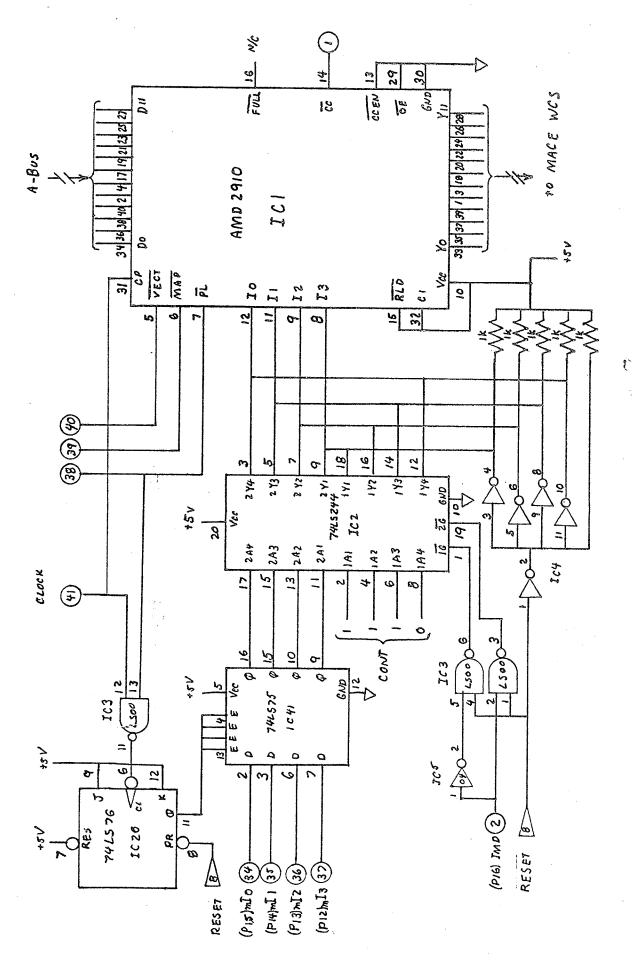

A block diagram for the LPCMK is shown in Fig. 19. Microcoding considerations are presented in the following sections and in Chapter 6.

Figure 19: The LPCMK Block Diagram

#### 5.3.2 Pipeline Register

The pipeline register refers specifically to the register that is loaded with the microinstruction. The address to the microinstruction memory is supplied by the sequencer which is discussed in Sec. 5.3.3. The 48-bit wide microinstructions are loaded into the pipeline registers on the rising clock edge. Sufficient settling time is allowed for the microinstruction memory after applying the address. There are 8 of the registers shown schematically in Appendix 1. The specific microinstruction fields are listed in Table 1.

The microinstruction bits are used throughout the LPCMK to control the sequencer, bit-slice unit, other combinational elements of the LPCMK, or as strobes for triggering events such as loading the I/O or status registers.

There are 2K x 48-bits of microinstruction memory in the Mace WCS. Occasionally it is desireable to have immediate data in the microinstruction. It is wasteful in most cases to devote 16 microinstruction bits to the task at all times, therefore the immediate data field is multiplexed with the sequencer field. The 12 next address bits and 4 sequencer instruction bits are also used for 16 immediate data bits. Another bit called the IMD (Immediate Data control) selects between the two modes. When the IMD is low the following changes occur in the microinstruction operation:

a) Immediate data is supplied to the LPCMK ALU from the pipeline register; and

b) A continue (CONT) instruction is given to the sequencer through hardware control.

TABLE 1

Allocation of Microinstruction Bits

| BIT | MNEMONIO | FUNCTION ( | S)        | BIT  | MNEMONIC | FUNCTION(S)        |

|-----|----------|------------|-----------|------|----------|--------------------|

| 0   | BRO      |            |           | 27   | A0       |                    |

| 1   | BR1      |            |           | 28   | Al       | ALU                |

| 2   | BR2      |            |           | 29   | A2       | PORTA              |

| 3   | BR3      |            |           | 30   | A3 ·     | IMMEDIATE          |

| 4   | BR4      | MICROPROG. |           | 31   | В0       |                    |

| 5   | BR5      | BRANCH     |           | 32   | B1       | ALU                |

| 6   | BR6      |            |           | 33   | B2       | PORTB              |

| 7   | BR7      |            | IMMED.    | 1 34 | В3       | IMMEDIATE          |

| 8   | BR8      |            | DATA      | 35   | ABM0     | PORT ADDRESS       |

| 9   | BR9      |            |           | 36   | ABMI     | SELECT MUX.        |

| 10  | BR10     |            |           | 37   | LADD     | LATCH ADDRESS      |

| 1   | BR11     |            |           | 38   | LDV/INTA | INT.ACK./VECT LOAD |

| 12  | mIO      |            |           | 39   | LDI      | LOAD DATA IN       |

| 13  | mI1      | MICROPROG. |           | 40   | LDO      | LOAD DATA OUT      |

| 14  | mI2      | CONTROL    |           | 41   | SS0      |                    |

| 15  | mI3      |            |           | 42   | SSI      | STATUS             |

| 16  | IMD      | IMMEDIATE  | DATA CNT. | 43   | SS2      | SELECT             |

| 17  | 10       |            |           | 44   | ROTO     | ROTATE             |

| 18  | 11       | ALU        |           | 45   | ROT1     | SELECT             |

| 19  | 12       | SOURCE     | ×         | 46   | STAT     | STATUS CONTROL     |

| 20  | 13       |            |           | 47   | R∕₩      | READ/WRITE         |

| 21  | 14       | ALU        | ALU       | 1    |          |                    |

| 22  | 15       | FUNCTION   | CONTROL   | 1    |          |                    |

| 23  | 16       |            |           |      |          |                    |

| 24  | 17       | ALU        |           |      |          |                    |

| 25  | 18       | DESTIN.    |           |      |          |                    |

| 26  | CO       | ALU CARRY- | IN        | 1    |          |                    |

The price paid for multiplexing the microinstruction bits is in the IMD control bit and the limitation of the CONT instruction imposed upon microprogram development. The LPCMK block diagram is shown in Fig. 19.

Another consideration is that of system reset or power-up microinstruction address generation. This is done through hardware by supplying the sequencer instruction ZERO when the RESET pulse goes low. This

sets the microinstruction address to location zero to begin execution of

the required initialization routines. The reset pulse must be at least

one complete clock period and is supplied by the Mace Development system.

## 5.3.3 <u>Microinstruction Sequencer</u>

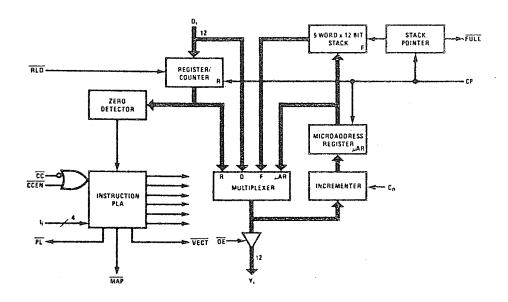

The sequencer is responsible for supplying the present address and preparing the next microcomputer address for the program memory. A complete 12 bit sequencer, the AMD2910, is used for program control. It has an addresss space of 4K words, although there are only 2K words available from the existing configuration of the Mace WCS. This is an enormous amount of memory when the power of each microinstruction is considered.

The microinstruction sequencer, which is illustrated in block diagram form in Fig. 20, has three internal registers which are clocked by the rising clock edge.

The microaddress register is loaded with the results of the incrementer which, from the chosen configuration, will always be the next sequential instruction address. The stack pointer and register/counter actions depend on the sequencer instruction being executed.

The sequencer requires a four bit control code giving it a repetoire of 10 conditional and 6 unconditional next addresses. A condition is assumed to be met if the  $\overline{\text{CC}}$  and  $\overline{\text{CCEN}}$  is low. The sequencer [9] [10]

# IDM2910A Block Diagram

Figure 20: Microinstruction Sequencer Block Diagram

provides the powerful microprogram control required for high processing throughput.

The next microinstruction address will come from one of the following four sources:

- a) The microprogram address registers;

- b) The external direct input lines;

- c) The register/counter containing a previously loaded address; or

- d) The LIFO (last in first out) stack.

When the microinstruction bit allocation is described in Sec. 5.3.3 it is shown that there is almost no overhead in time for program control. There is a cost in space, however, of the microinstruction bits which must be dedicated to the device.

The PL,MAP, and VECT enable bits are supplied for next direct address control. Only one of these lines is low at any one time. They are controlled by the sequencer control code and simplify the hardware interface to be discussed in Sec. 5.6. The following inputs are tied to ground potential or V since their capabilities are not required:

- CCEN condition code input is always enabled.

- RLD the register counter can only be loaded by an instruction.

- $\overline{\text{OE}}$  the address output is always enabled.

The FULL output goes low one microinstruction after the 5 word stack is full. Since nesting of subroutines is not permitted past 5 levels, including interrupt service, this pin is ignored by the LPCMK.

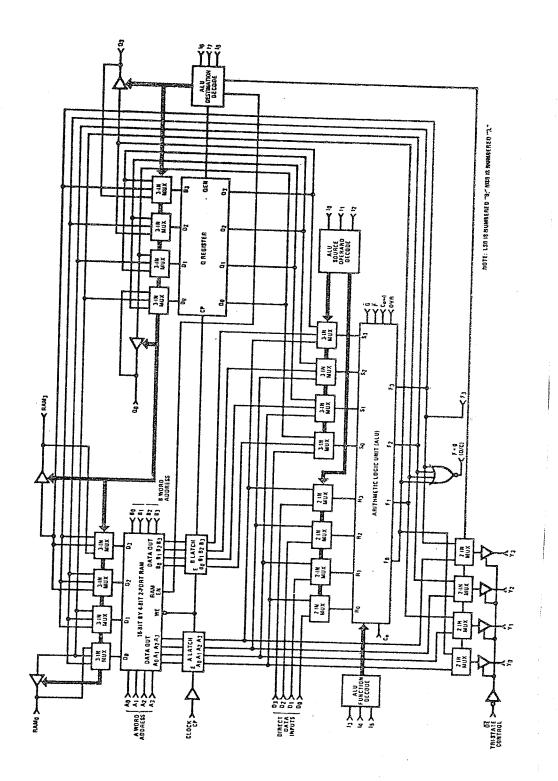

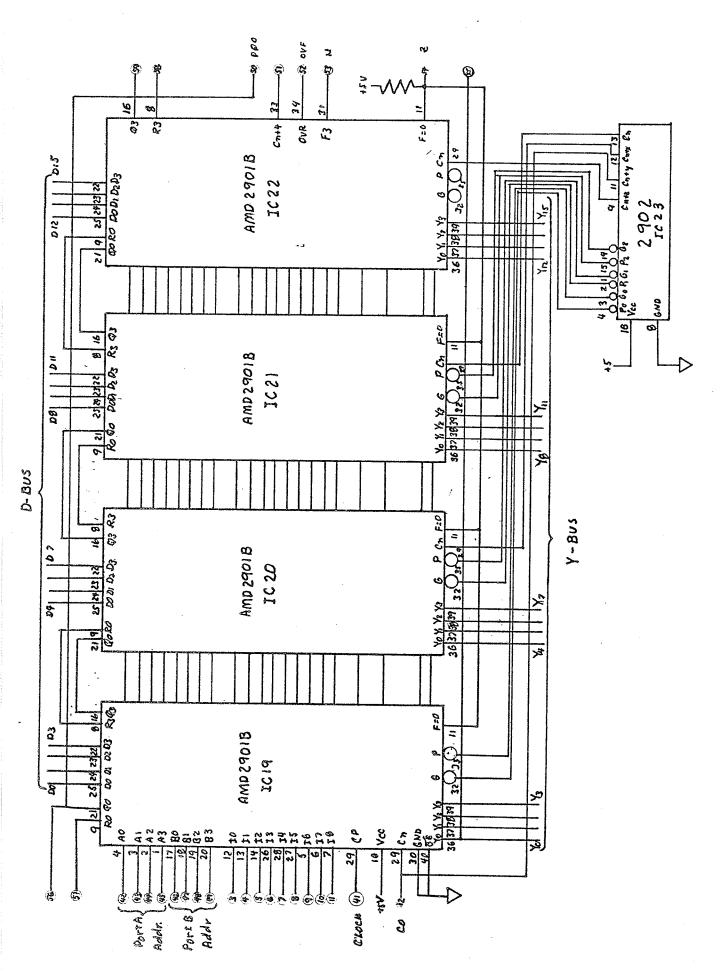

# 5.3.4 ALU and Register Set

The AMD 2901B was chosen for use as the ALU (arithmetic logic unit) and internal register set [9] [10]. All data paths in this device are 4 bits wide. A block diagram is shown in Fig. 21. The 4-bit-slice can be cascaded to the number of bits required for the application. In the case of the LPCMK, a 16 bit data bus proved sufficient so four bit-slices were cascaded.

A 9-bit instruction is required by the AMD 2901B, which can be divided ed into three fields as follows:

- a) ALU source operand control;

- b) ALU function control; and

- c) ALU destination control.

Each is a 3-bit field and a carry-in input for the ALU is also required.

A 16-word two port RAM is available as a register set allowing two registers to be accessed simultaneously. Only the register addressed with the port B address can be written into. When the clock pulse is high the data addressed by port A and B addresses are read into their respective latches. The data are latched when the clock pulse goes low avoiding race conditions. Data is also written into the port B register while the clock pulse is low.

The Q-register is most useful for divide or multiply operations. Data is loaded to the Q-register on the low clock level as for the RAM.

The ALU is capable of performing three binary arithmetic and five logic functions. A look-ahead carry generator is used to increase the ALU speed of the cascaded bit-slices. The carry-in to the 16 bit ALU is provided by a microinstruction bit, and will alter the add and subtract

Figure 21: Internal Bit-slice Block Diagram

operations. The status of the ALU is indicated by the zero, carry-out, sign and overflow outputs from the ALU. These are used in the status register which is described in Sec. 6.3.4.

The ALU results appear at the output F and have one of the following possible destinations:

- a) ALU data is output to the Y-bus;

- b) ALU data is output to the Y-bus and stored in Q-register;

- c) ALU data is output to the Y-bus and stored in Port B location;

- d) Port A data is output to the Y-bus and ALU data is input to Port B register; or

- e) ALU data is output to the Y-bus and shifted once, up or down to the Port B register. The Q-register can be shifted up or down as well in the same operation.

The maximum clock speed allowed for the AMD 2901B is approximately 15 MHz. A 5 MHz system was implemented, which is well within the AMD 2901B operating specifications. Other propogation delay contributions must be considered when calculating the maximum system clock frequency.

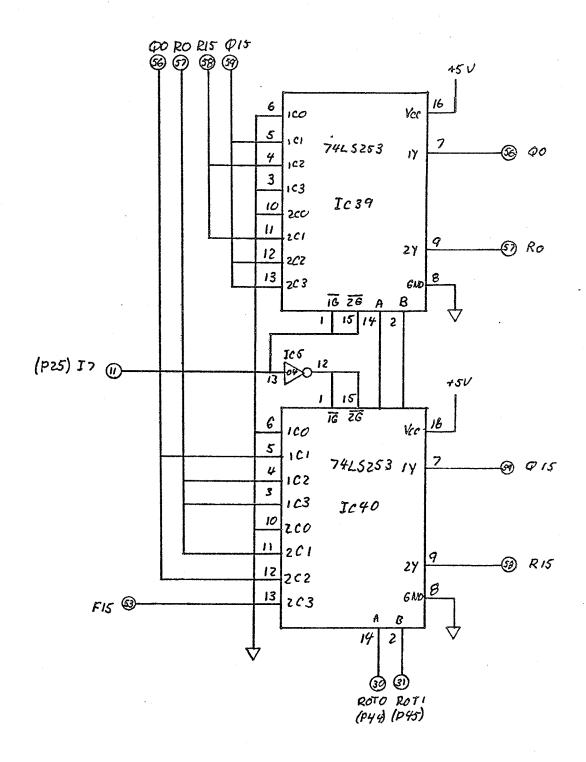

The shift outputs of the AMD 2901B's are tri-stated unless a shift is selected by the destination field of the microinstruction. Shifting circuitry is necessary to supply these inputs which are the most and least significant bits of the Q-register and RAM addressed by Port B. This is implemented in the form of two tri-stateable dual 4-bit multiplexers. The schematic is given in Appendix 1. Two microinstruction bits are allocated to the multiplexers allowing the choice of shifts shown in Table 2 In this table RAMO, RAM15, and Q0, Q15 are the least and most significant bits of the Port B register and Q-register respectively.

TABLE 2

Rotate and Shift Destinations

| MNEMONIC | FUNCTION              | 1 | MNEMONIC | FUNCTION                |

|----------|-----------------------|---|----------|-------------------------|

| RZD      | 0 > RAM15             |   | RDRD     | Q0 > RAM15              |

| RQZD     | 0 > RAM15, 0 > Q15    |   | RQDRD    | Q0 > RAM15, RAM0 > Q15  |

| RZU      | RAM0 < 0,             |   | RDRU     | Q15 > RAM0              |

| RQZU     | RAM0 < 0, Q0 < 0      |   | RQDRU    | Q15 > RAM0, RAM15 > Q0  |

| RDRD     | Q0 < RAM15            | İ | SRA      | F15 > RAM15 ARITH.      |

| RQDRD    | RAM0 > RAM15,Q0 > Q15 |   | DSRA     | F15 > RAM15, RAM0 > Q15 |

| RSRU     | RAM15 > RAM0          |   | SLA      | Q15 > RAM0              |

| RQSU     | RAM15 > RAM0,Q15 > Q0 |   | DSLA     | Q15 > RAM0, 0 > Q0      |

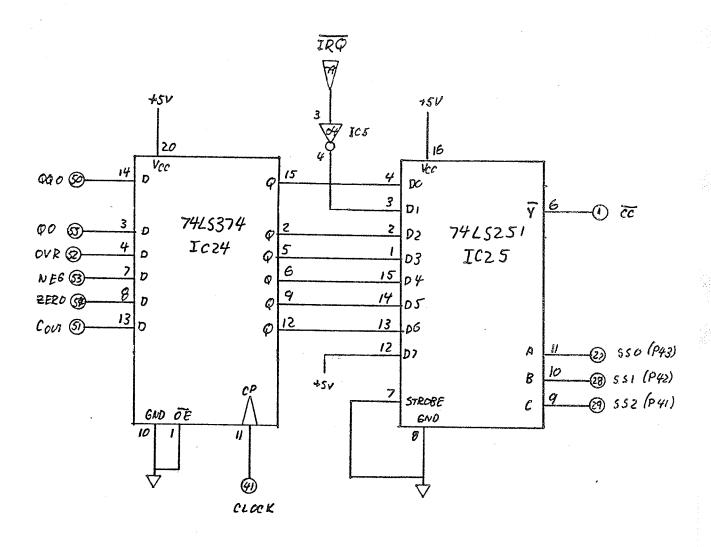

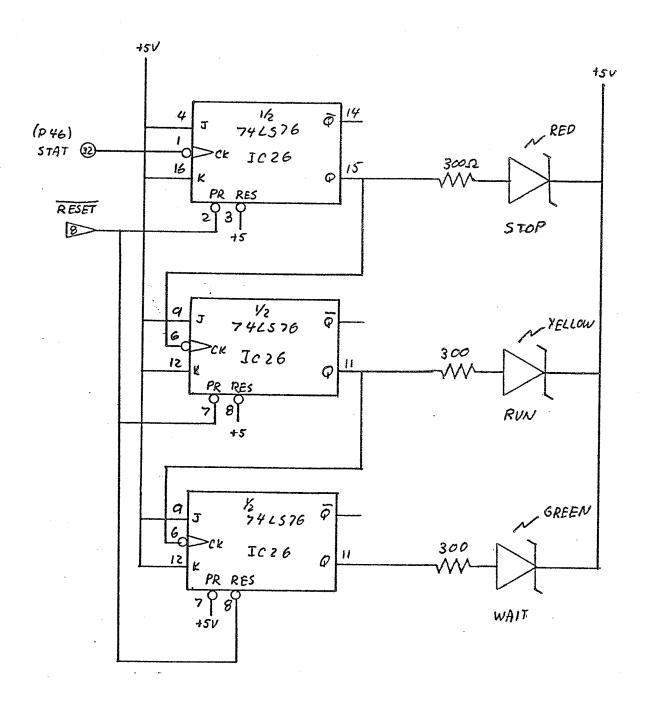

# 5.3.5 <u>Status</u>

Status of the previous microinstruction results is required due to the architecture chosen. Status of the ALU operation, interrupt status or unconditional status met is supplied to the CC pin of the sequencer for conditional branch instruction execution. Table 3 shows the status field allocation. Three microinstruction bits are allocated to the status select control allowing 8 different events to be monitored. The status function is implemented with an 8-bit edge triggered register and an 8:1 digital multiplexer.

TABLE 3

Condition Codes

| STATUS INEMONICS | 1 | FUNCTION             |

|------------------|---|----------------------|

| QQ0              |   | LSB of Q-Register    |

| IRQ              | i | External interrupt   |

| Q0               | i | LSB of ALU output    |

| OVR              | i | Overflow             |

| И                | i | Sign                 |

| Z                | i | Zero                 |

| С                | İ | Carry                |

| MET              | Ì | Condition always met |

|                  |   |                      |

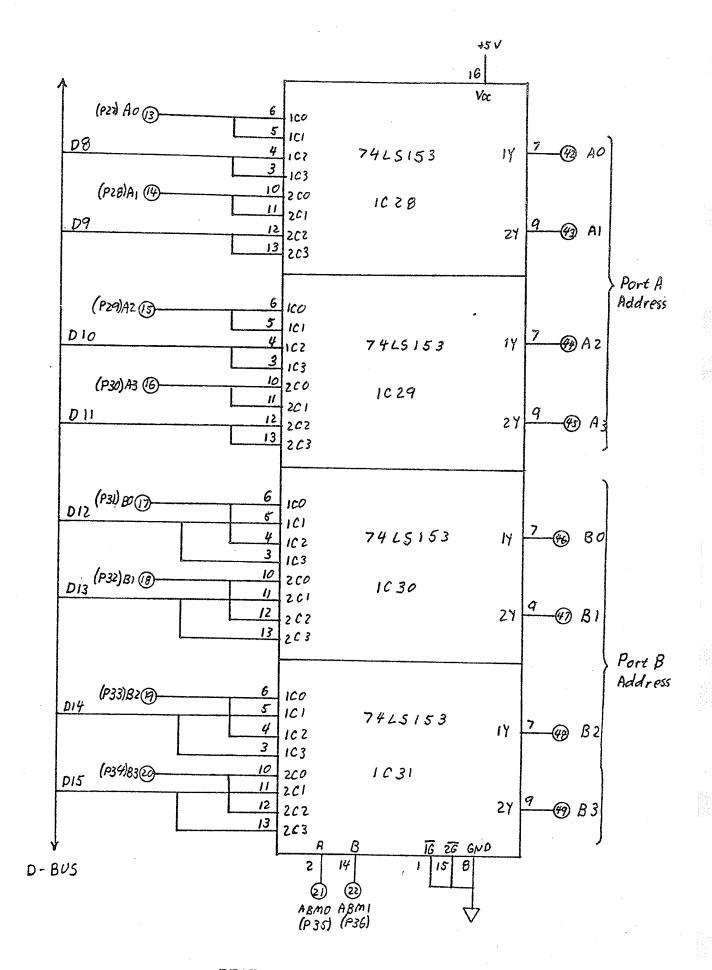

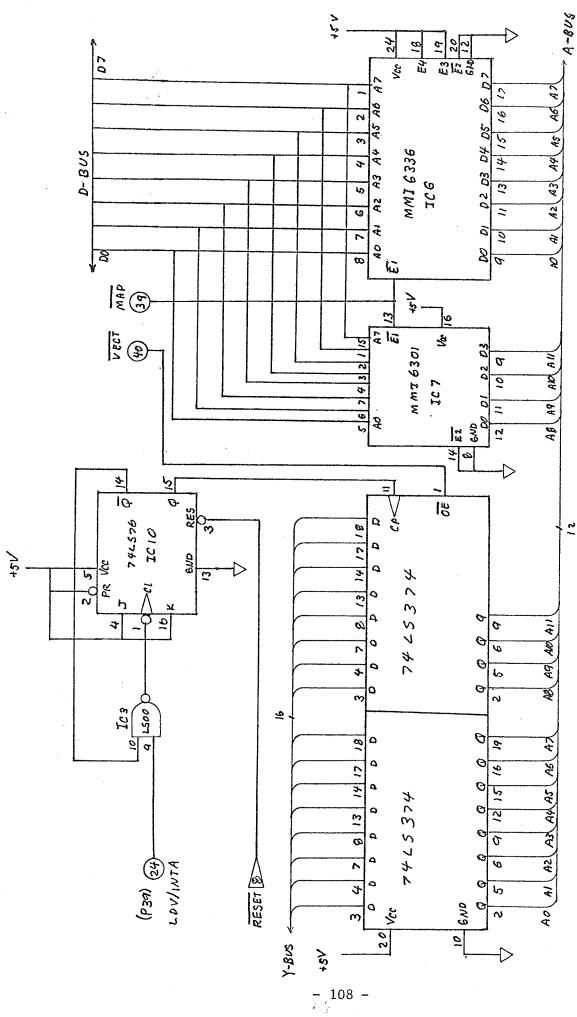

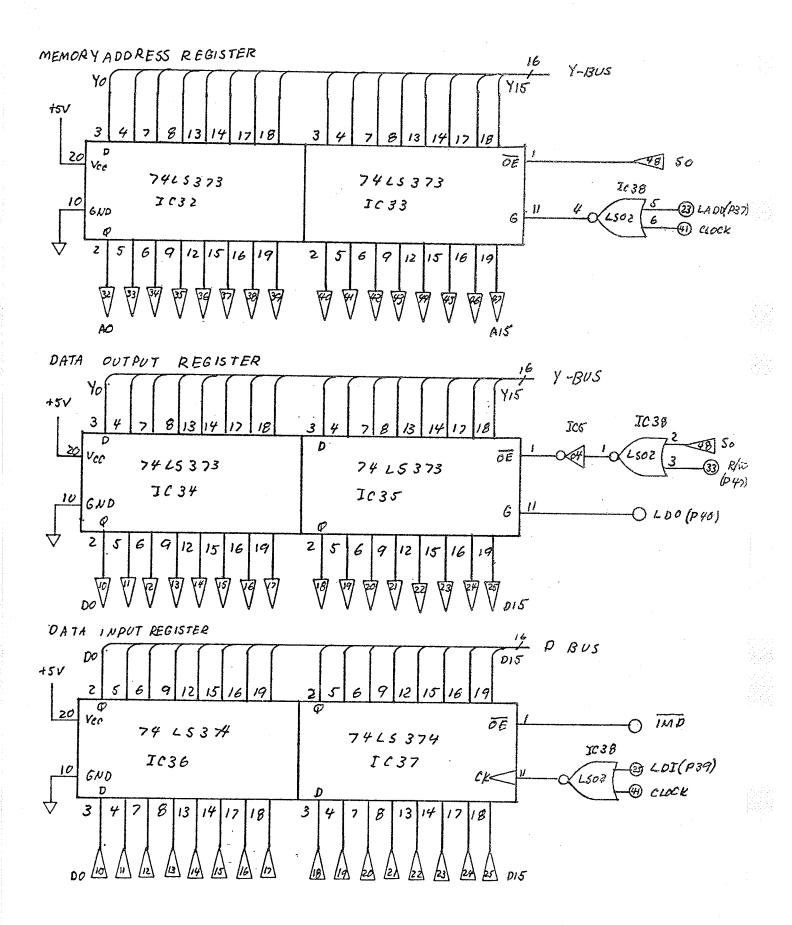

#### 5.3.6 I/O Registers

An external interface is required for communicating with the Program Memory and Data Acquisition unit. The following three register sets, each consisting of two 8-bit registers, are used for the address and data interface to the external bus:

- a) Memory Address Register (MAR) supplies a 16-bit address;