# Apparatus for Asynchronously Linking a Variable–Speed Self–Excited Induction Generator to an Isolated ac Electrical Load

by Trevor L. Maguire

A Thesis

Submitted to the Faculty of Graduate Studies

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

The Department of Electrical and Computer Engineering

The University of Manitoba Winnipeg, Manitoba, Canada

January 1992

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et exclusive non permettant Bibliothèque à la nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-77974-8

# APPARATUS FOR ASYNCHRONOUSLY LINKING A VARIABLESPEED SELF-EXCITED INDUCTION GENERATOR TO AN ISOLATED ac ELECTRICAL LOAD

BY

TREVOR L. MAGUIRE

A Thesis submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

© 1992

Permission has been granted to the LIBRARY OF THE UNIVERSITY OF MANITOBA to lend or sell copies of this thesis, to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this thesis.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's permission.

#### **Abstract**

This thesis describes the development of a novel apparatus for supplying an isolated ac load through a dc link from a self—excited induction generator. The generator is operable at variable speed. Machine voltage magnitude, load voltage magnitude, and load voltage frequency are simultaneously regulated to rated values during steady running and during changes in both load power and machine speed.

The self-excited induction machine supplies a controlled Graetz bridge rectifier in the dc link. A voltage-sourced inverter is used to supply the ac load. A voltage-boost converter interfaces the variable dc output voltage which is produced by the rectifier to the relatively fixed dc input voltage which is required by the voltage-sourced inverter.

A prototype electromagnetic transients program is described which is based on a modified Dommel algorithm. The prototype program is used to study the apparatus and associated controls. The program is particularly adapted for the simulation of power electronic apparatus at a system level. Individual switching devices are represented according to simple characteristic curves. The modified algorithm includes iteration of a time—step when required to provide solutions on the curves. Two time—step sizes are used in the program to permit events to be located to within the resolution of the small time—step. A technique is described for suppressing numerical oscillations in the solutions for currents in capacitive loops and voltages at inductive nodes. Modifications to the induction machine model are implemented in the prototype program in order to more accurately simulate the dynamics of self—excitation.

A control system for the apparatus was developed using the prototype simulation program. The control system is mainly feed—forward in nature but in-

cludes slower-acting feed-back control loops which provide correction of the feed-forward control error.

A test apparatus has been built and tested in the laboratory. The test apparatus includes a control system based on a digital signal processor. The apparatus is observed to operate generally as predicted by the electromagnetic transients simulation program. The apparatus operates well during both transient and steady—running conditions.

### Acknowledgements

The author thanks Professor A.M. Gole, the author's thesis supervisor, for advice and support which were always given and in particular for the many useful discussions which took place on the topic of electromagnetic transients simulation.

The author also thanks Technologist E. Dirks for his advice on the selection of digital electronic components and Professor R.W. Menzies for useful discussions on the topic of induction machines.

The author is also grateful to the University of Manitoba for financial support from the University of Manitoba Fellowship program; to the Natural Sciences and Engineering Research Council for financial support from the Post Graduate Scholarship program; and to the Manitoba HVDC Research Centre for a grant toward the purchase of components for the laboratory apparatus.

# **Table of Contents**

|                 |         |                                                  | <u>Page</u> |  |

|-----------------|---------|--------------------------------------------------|-------------|--|

| Abstr           | ract    |                                                  | i           |  |

| Ackn            | owledge | ements                                           | iii         |  |

| Table           | of Con  | tents                                            | iv          |  |

| Table           | of Figu | ires                                             | ix          |  |

| List of Symbols |         |                                                  |             |  |

|                 |         |                                                  |             |  |

| CHA             | PTER    |                                                  |             |  |

| 1.              | INTR    | RODUCTION                                        | 1           |  |

|                 | 1.1     | General Introduction                             | 1           |  |

|                 | 1.2     | Background and Scope of the Thesis               | 1           |  |

|                 | 1.3     | The Choice of Apparatus Configuration            | 3           |  |

|                 | 1.4     | Outline of the Thesis                            | 7           |  |

|                 |         |                                                  |             |  |

| 2.              | STEA    | ADY STATE CHARACTERIZATION OF                    |             |  |

|                 |         | THE APPARATUS                                    | 10          |  |

|                 | 2.1     | Description of the Steady State Characterization | 10          |  |

|                 | 2.2     | The Steady-state Equivalent Circuit of the       |             |  |

|                 |         | Induction Machine                                | 11          |  |

|                 | 2.3     | The Non–linear Search Procedure                  | 12          |  |

|                 | 2.4     | Calculation of the Self–excitation Capacitance   | 15          |  |

|                 | 2.5     | Obtaining Characteristic Curves for              |             |  |

|                 |         | Operation of the Apparatus                       | 18          |  |

| 3. | TRA | NSIENTS SIMULATION TECHNIQUES FOR           |    |

|----|-----|---------------------------------------------|----|

|    |     | POWER ELECTRONIC APPARATUS                  | 21 |

|    | 3.1 | Outline of the Chapter                      | 21 |

|    | 3.2 | Motivating Factors for Modification of the  |    |

|    |     | Transients Simulation Algorithm             | 22 |

|    | 3.3 | Representation of Switching Devices in      |    |

|    |     | the Prototype Program                       | 25 |

|    | 3.4 | Modification of the Conventional Algorithm  |    |

|    |     | for Suppression of Numerical Oscillations   | 35 |

|    | 3.5 | Structure of the Overall Program            | 39 |

|    | 3.6 | Modelling Interaction of d and q Axis       |    |

|    |     | Mutual Fluxes in Round Rotor                |    |

|    |     | Induction Machines Due to Saturation        | 45 |

| 4. | THE | CONTROL SYSTEM DESIGN                       | 59 |

|    | 4.1 | Introduction                                | 59 |

|    | 4.2 | A General Description of the Control System | 64 |

|    | 4.3 | The Power Order Control Block               | 75 |

|    | 4.4 | The Look-up Tables and Voltage-boost        |    |

|    |     | Converter Control                           | 82 |

|    | 4.5 | The Rectifier Current Controller            | 86 |

|    | 4   | .5.1 Multiplication of the Basic Current    |    |

|    |     | Order by p.u. Machine Voltage               | 88 |

|    | 4   | .5.2 The PI Controller in the Rectifier     |    |

|    |     | Current Controller                          | 94 |

the second of Marketine and Second

|    |     | 4.5.3 | The Phase–Locked–Oscillator                      | 98  |

|----|-----|-------|--------------------------------------------------|-----|

|    | 4.6 | Su    | mmary of the Control System                      | 103 |

|    |     |       |                                                  |     |

| 5. | SY  | STEM: | PERFORMANCE DEMONSTRATED                         |     |

|    |     |       | THROUGH TRANSIENTS SIMULATION                    | 104 |

|    | 5.1 | Int   | roduction                                        | 104 |

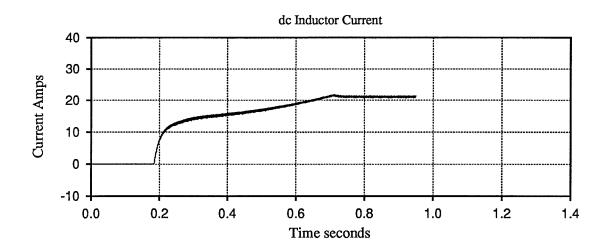

|    | 5.2 | Ca    | se 1 – Simulated Performance at 1.0 p.u. Machine |     |

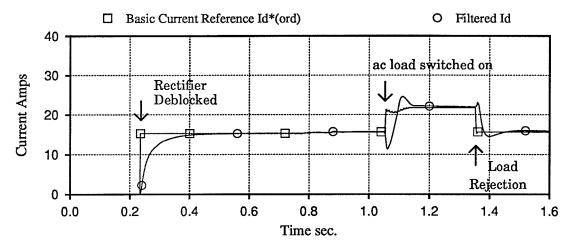

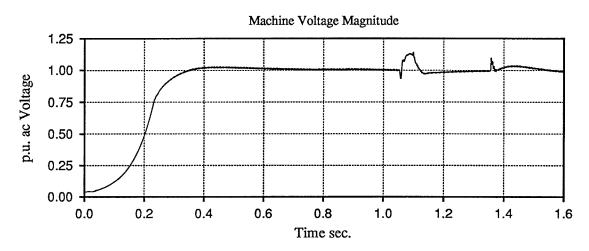

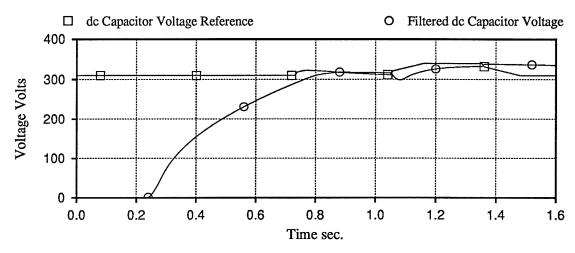

|    |     |       | Speed with ac Load Applied after Start-up        | 105 |

|    |     | 5.2.1 | Case 1 – Prior to Deblocking the Rectifier       | 106 |

|    |     | 5.2.2 | Case 1 – Between Deblocking the Rectifier        |     |

|    |     |       | and Application of the Load                      | 113 |

|    |     | 5.2.3 | Case 1 – Between Application of Load             |     |

|    |     |       | and Load Rejection                               | 119 |

|    |     | 5.2.4 | Case 1 – After Load Rejection                    | 122 |

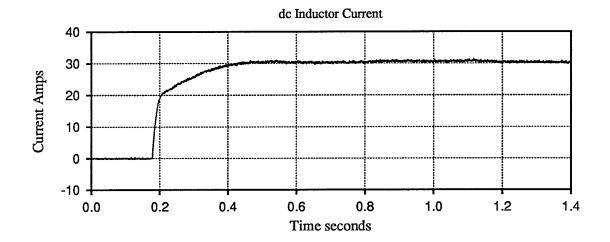

|    | 5.3 | Cas   | se 2 – Simulated Performance at 1.4 p.u. Machine |     |

|    |     |       | Speed with ac Load Applied after Start-up        | 123 |

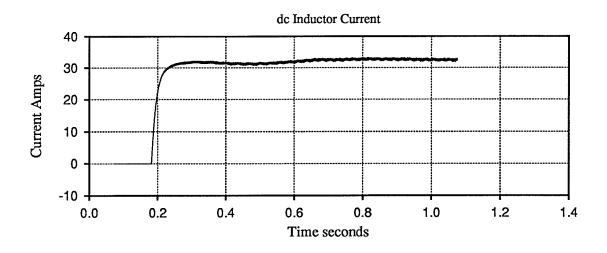

|    | 5.4 | Cas   | se 3 – Simulated Performance at 1.0 p.u. Machine |     |

|    |     |       | Speed during Start-up with Pre-connected ac Load | 127 |

|    |     | 5.4.1 | Numerical Oscillation Suppression in the         |     |

|    |     |       | Simulations                                      | 135 |

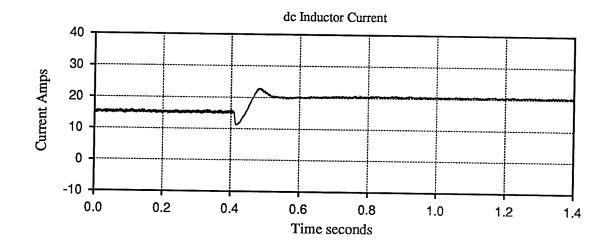

|    | 5.5 | Cas   | se 4 – Simulated Performance at 1.4 p.u. Machine |     |

|    |     |       | Speed during Start-up with Pre-connected ac Load | 136 |

|    | 5.6 | Cor   | nclusions                                        | 136 |

| 6. | SYS | STEM I | PERFORMANCE DEMONSTRATED                            |     |

|----|-----|--------|-----------------------------------------------------|-----|

|    |     |        | THROUGH LABORATORY TESTING                          | 140 |

|    | 6.1 | Int    | roduction                                           | 140 |

|    | 6.2 | De     | monstration of the Apparatus during Start–up        | 146 |

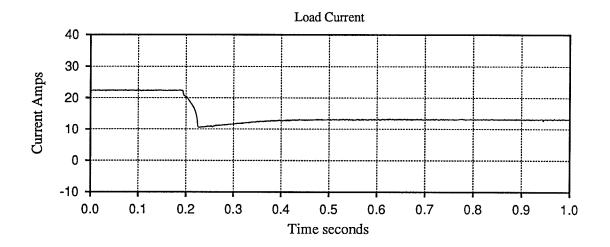

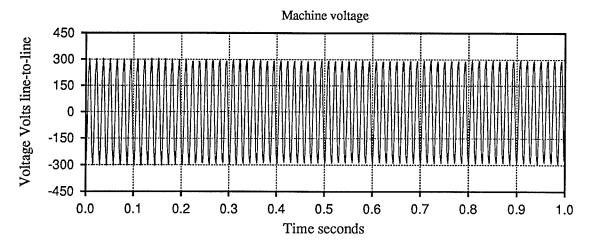

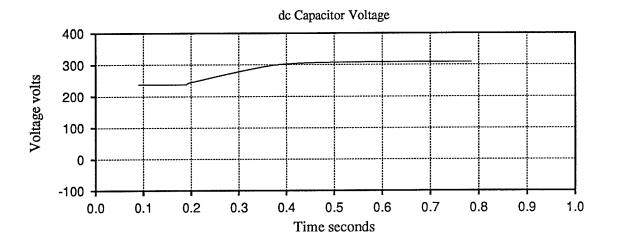

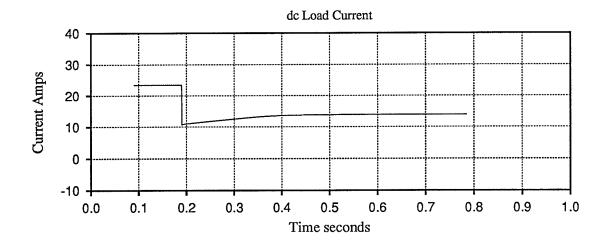

|    |     | 6.2.1  | Test 1 – No Load Start at 1.0 p.u. Speed            | 146 |

|    |     | 6.2.2  | Test 2 – No Load Start at 1.38 p.u. Speed           | 150 |

|    |     | 6.2.3  | Test 3 – Start Under Load at 1.0 p.u. Speed         | 156 |

|    |     | 6.2.4  | Test 4 – Start Under Load at 1.38 p.u. Speed        | 156 |

|    | 6.3 | De     | monstration of Application of Load                  |     |

|    |     |        | during Steady Running                               | 159 |

|    |     | 6.3.1  | Test 5 – Applying 0.95 p.u. Load at 1.0 p.u. Speed  | 159 |

|    |     | 6.3.2  | Test 6 – Applying 0.95 p.u. Load at 1.38 p.u. Speed | 159 |

|    | 6.4 | Illu   | strations of Waveshapes during Steady Running       | 164 |

|    |     | 6.4.1  | Test 7 – Steady Running with                        |     |

|    |     |        | 0.95 p.u. Load at 1.0 p.u. Speed                    | 164 |

|    |     | 6.4.2  | Test 8 – Steady Running with                        |     |

|    |     |        | No Load at 1.0 p.u. Speed                           | 169 |

|    |     | 6.4.3  | Test 9 – Steady Running with                        |     |

|    |     |        | 0.95 p.u. Load at 1.38 p.u. Speed                   | 164 |

|    |     | 6.4.4  | Test 10 - Steady Running with                       |     |

|    |     |        | No Load at 1.38 p.u. Speed                          | 169 |

|    | 6.5 | De     | monstration of Load Rejection Performance           | 174 |

|    |     | 6.5.1  | Test 11 – Load Rejection of                         |     |

|    |     |        | 0.95 n u Load at 1.0 n u Speed                      | 174 |

|              | 6.5.2    | Test 12 – Load Rejection of                        |     |

|--------------|----------|----------------------------------------------------|-----|

|              |          | 0.95 p.u. Load at 1.38 p.u. Speed                  | 174 |

| 6.6          | De       | monstration of Application and Removal of Overload | 179 |

|              | 6.6.1    | Test 13 – Application of Overload                  | 179 |

|              | 6.6.2    | Test 14 – Recovery from Overload                   | 182 |

| 6.7          | Coi      | nclusions from Laboratory Testing                  | 182 |

| 7. <b>CO</b> | NCLUS    | SIONS AND CONTRIBUTIONS                            | 186 |

| 7.1          | Coı      | nclusions from Chapter 1 – Introduction            | 186 |

| 7.2          | Cor      | nclusions from Chapter 2 – Steady State            |     |

|              |          | Characterization of the Apparatus                  | 186 |

| 7.3          | Cor      | nclusions from Chapter 3 –                         |     |

|              |          | Electromagnetic Transients Simulation              | 187 |

| 7.4          | Cor      | nclusions from Chapter 4 – Control System Design   | 189 |

| 7.5          | Cor      | nclusions from Chapter 5 —                         |     |

|              |          | Simulated Performance of the Apparatus             | 190 |

| 7.6          | Cor      | nclusions from Chapter 6 –                         |     |

|              |          | Performance of the Laboratory Apparatus            | 191 |

| 7.7          | Sur      | mmary                                              | 193 |

| Appendix l   | [ – Indu | ction Machine Data                                 | 194 |

| Appendix I   | I – Rep  | resentation of a Simple Characteristic Curve       | 197 |

| Appendix I   | II – Da  | ta for the Voltage–sourced Inverter and            |     |

|              |          | Shunt Filtering                                    | 201 |

| References   | ı        |                                                    | 208 |

# **Table of Figures**

| CII  | ٨ | סיגויים | 1 |

|------|---|---------|---|

| UII. | М |         | 3 |

| Figure N | <u>fumber</u>                                            | <u>Page</u> |

|----------|----------------------------------------------------------|-------------|

| 1        | Configuration of Developed Apparatus                     | 3           |

| 2        | Voltage-sourced Inverter                                 | 5           |

| 3        | Voltage-boost Converter                                  | 6           |

| CHAPTI   | ER 2                                                     |             |

| Figure N | <u>Jumber</u>                                            | <u>Page</u> |

| 4        | Induction Machine Equivalent Circuit                     | 11          |

| 5        | V <sub>g</sub> /f versus X <sub>m</sub> Saturation Curve | 12          |

| 6        | Controlled Graetz Bridge Rectifier                       | 16          |

| 7        | Required Rectifier Operating Current Id*(ord)            | 20          |

| 8        | Required Rectifier Operating Voltage $V_d^*(ord)$        | 20          |

| CHAPT    | ER 3                                                     |             |

| Figure N | <u>Jumber</u>                                            | Page        |

| 9        | Inductive Nodes and Capacitive Loops                     | 22          |

| 10       | Modifying a Device Characteristic Using Small Time-steps | 25          |

| 11       | Typical Diode Characteristic                             | 26          |

| 12       | Explanatory Illustration of an Iteration                 | 28          |

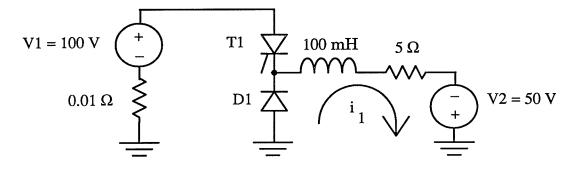

| 13       | Circuit for Describing Switching Operation               | 30          |

| 14       | Device Currents During a Simple Switching Operation      | 32          |

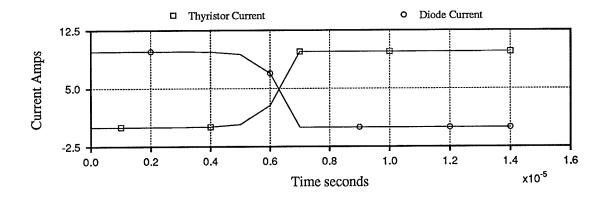

| 15       | Circuit for Demonstrating GTO Device                     |             |

|          | Turn-off Switching Operation                             | 33          |

| 16       | Node 1 Voltage Impulse for Figure 15 Circuit             | 34          |

| Figure N | <u>[umber</u>                                             | Page |

|----------|-----------------------------------------------------------|------|

| 17       | The Branch Equivalent in the Dommel Algorithm             | 35   |

| 18       | Circuit for Illustration of Numerical Oscillation         | 37   |

| 19       | Numerical Oscillation of Node 1 voltage in Figure 18      | 38   |

| 20       | Effect of the Numerical Oscillation Elimination Technique | 39   |

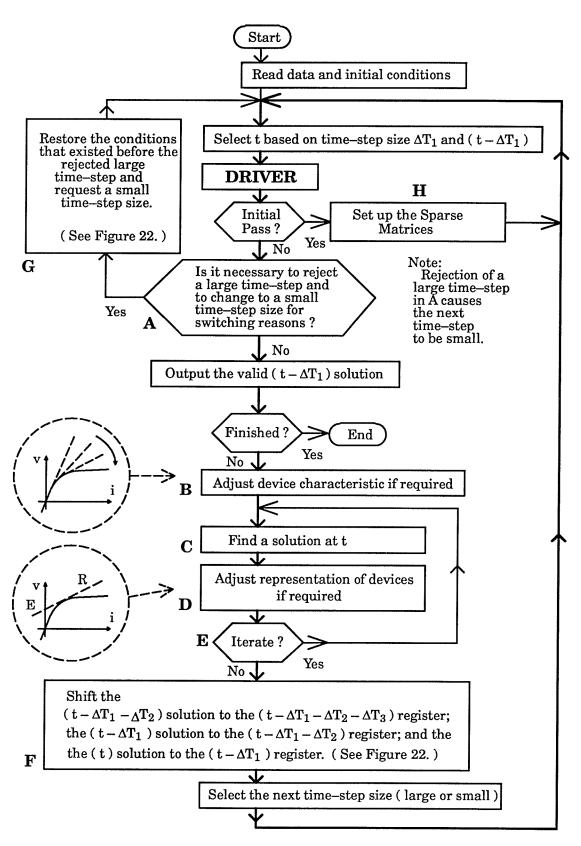

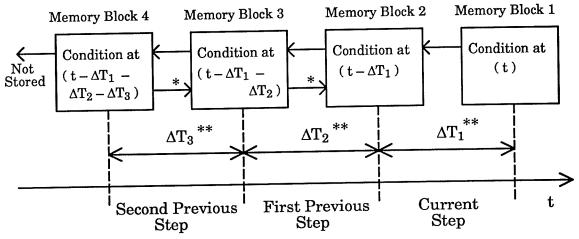

| 21       | Flow Chart for the Prototype Simulation Program           | 40   |

| 22       | Storage of a Sequence of Solutions in the Program         | 42   |

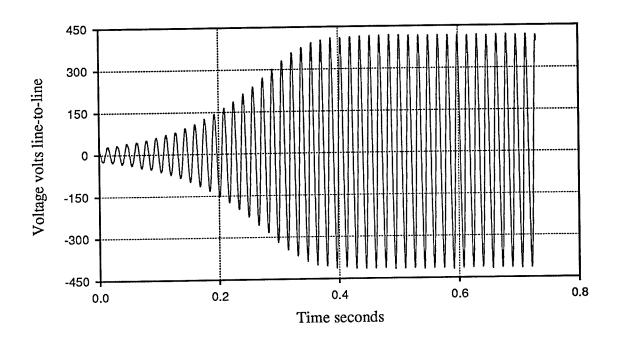

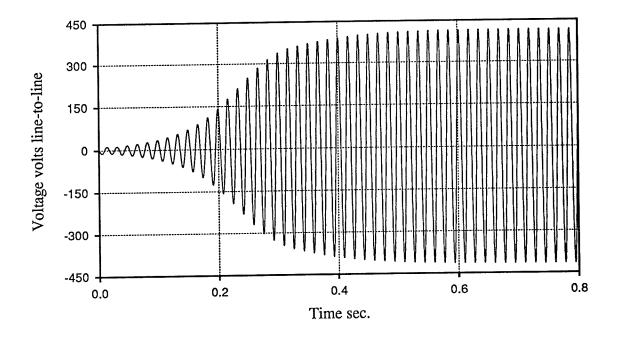

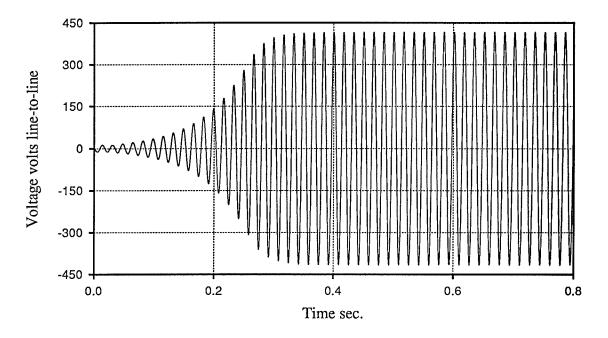

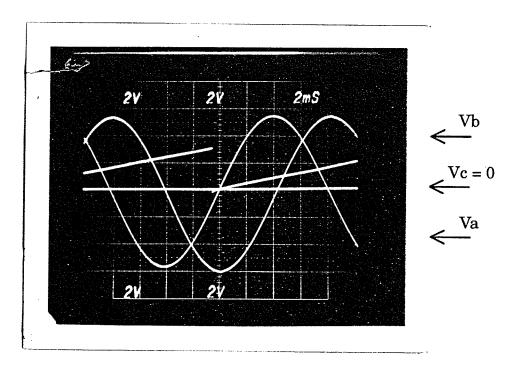

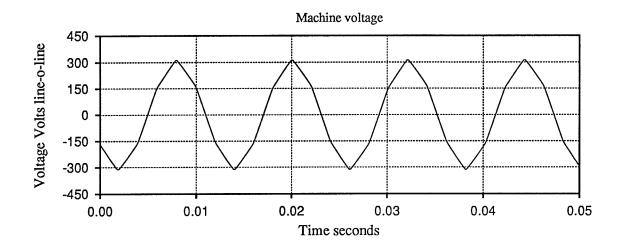

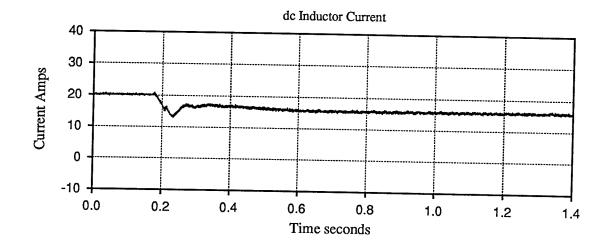

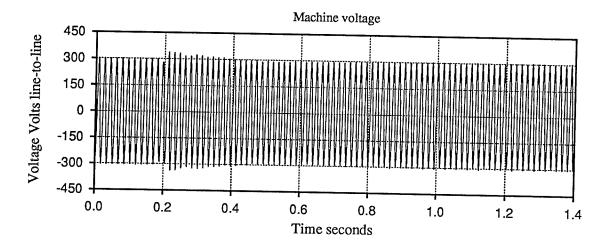

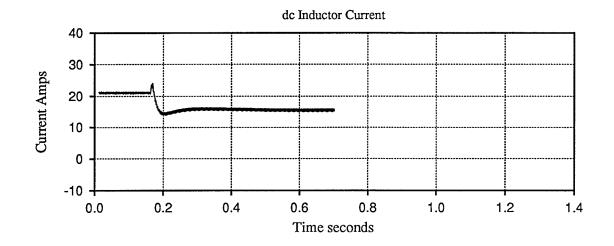

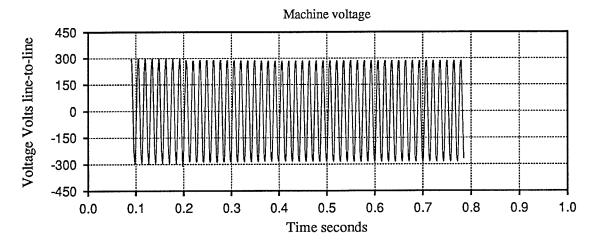

| 23       | Laboratory Self–Excitation of the Appendix I Machine      | 46   |

| 24       | Self-Excitation According to the Original Machine Model   | 46   |

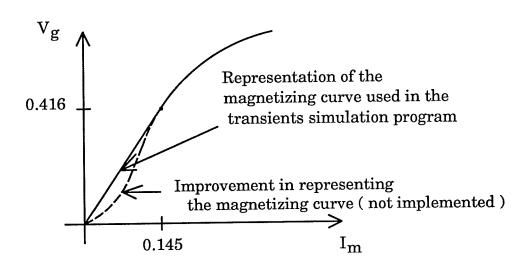

| 25       | A Detail of a Magnetizing Curve at Low Voltage            | 47   |

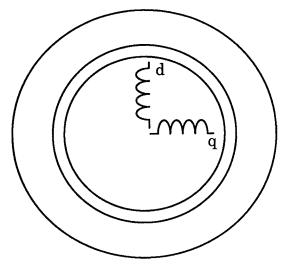

| 26       | Perpendicular D and Q Axis Windings on a Core             | 53   |

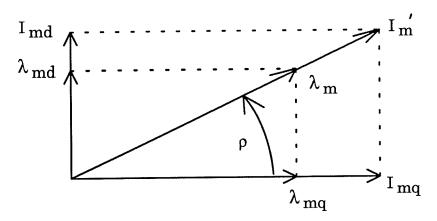

| 27       | Alignment of the Main Flux and Net Magnetizing Current    | 53   |

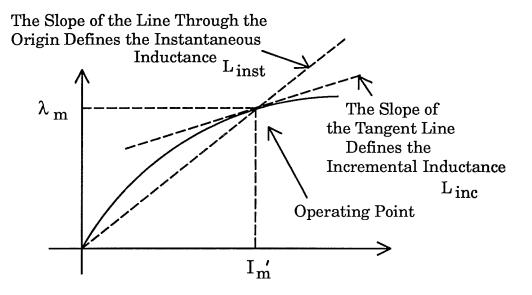

| 28       | Inductances Defined on a Saturation Curve                 | 55   |

| 29       | Self-Excitation According to the Modified Machine Model   | 57   |

| CHAPTE   | ER 4                                                      |      |

| Figure N | <u>umber</u>                                              | Page |

| 30       | A Single–Line Diagram of Apparatus for                    |      |

|          | Supplying Isolated ac Load                                | 60   |

| 31       | A Condensed Schematic of the Apparatus                    |      |

|          | with Associated Controls                                  | 61   |

| 32       | The Main Control Schematic                                | 65   |

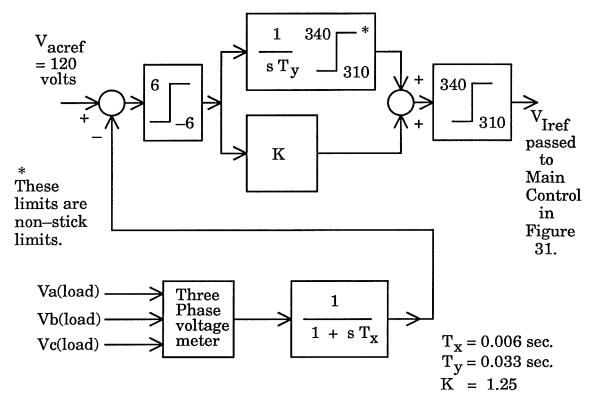

| 33       | The ac Load Voltage PI Controller                         | 66   |

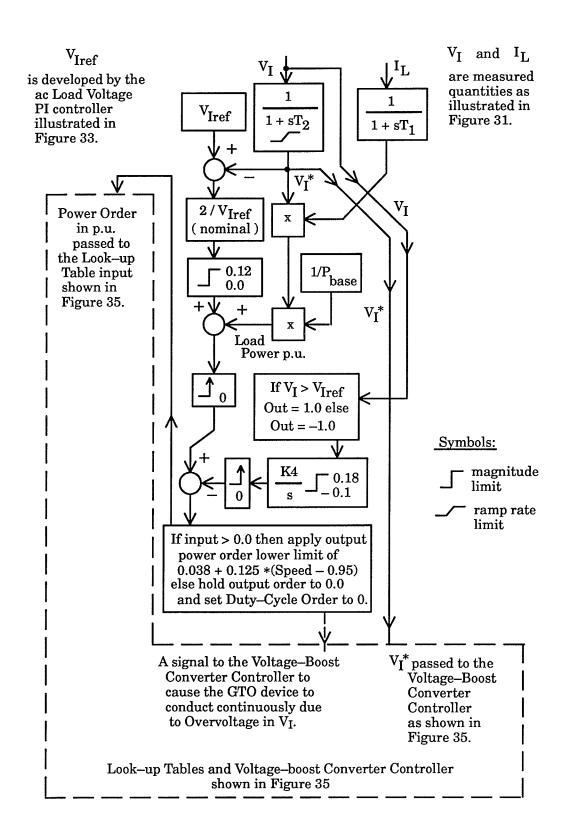

| 34       | The Power Order Control Block                             | 67   |

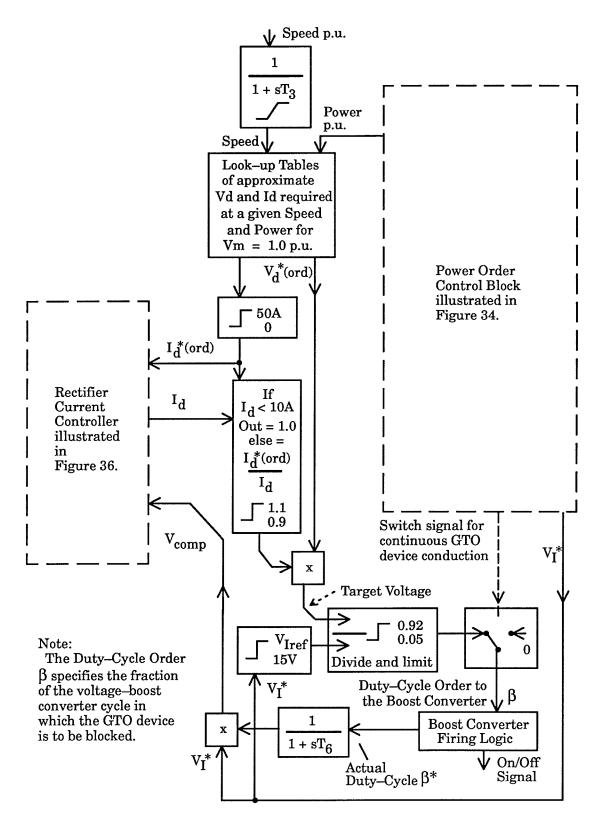

| 35       | The Look–up Tables                                        |      |

|          | and Voltage-boost Converter Controller                    | 68   |

| Figure l | Number                                                    | Page |

|----------|-----------------------------------------------------------|------|

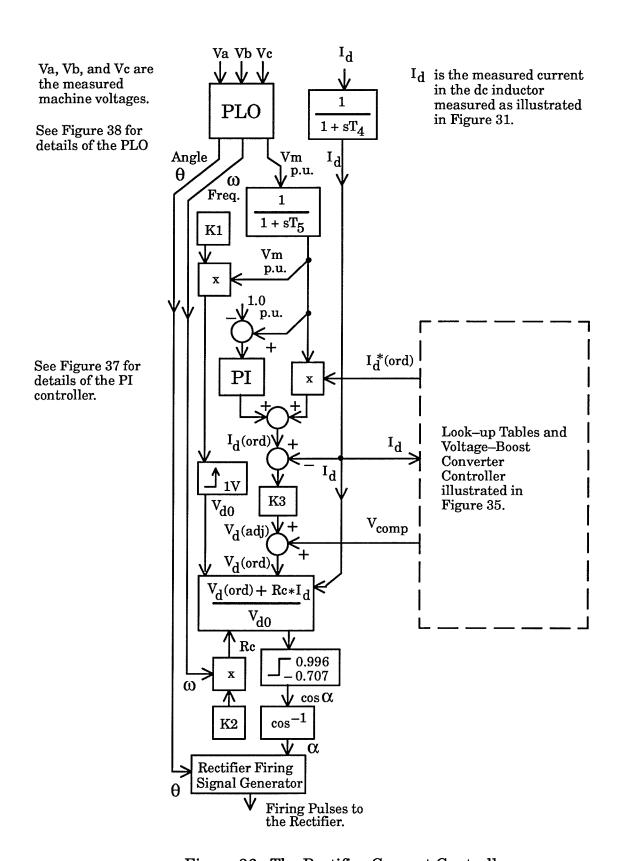

| 36       | The Rectifier Current Controller                          | 69   |

| 37       | The Machine Voltage PI Control Loop                       | 73   |

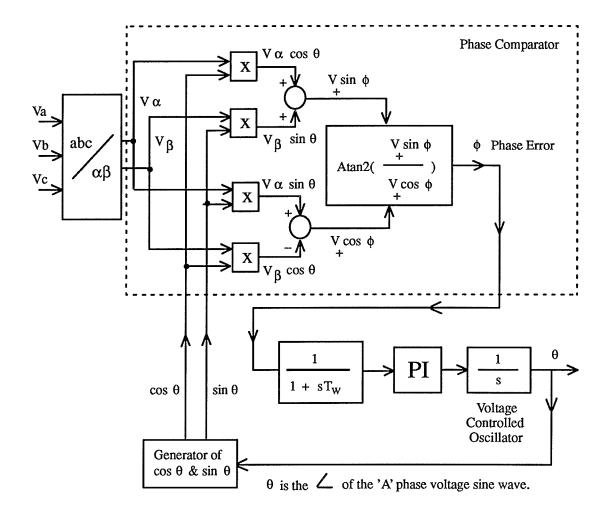

| 38       | Flow Diagram for the Phase Locked Oscillator              | 74   |

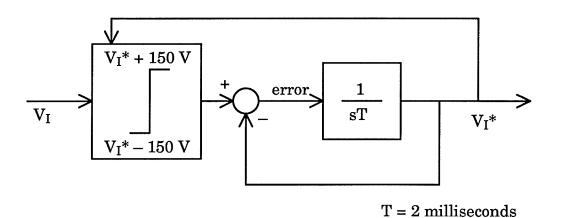

| 39       | The $V_I$ Filter with a Ramp–Rate Limit                   | 76   |

| 40       | Required Rectifier Operating Voltages at Low Power Levels | 79   |

| 41       | Minimum Desired Power Order versus Speed                  | 80   |

| 42       | Curves for an Induction Machine Excited by Capacitors     | 89   |

| 43       | Curves for an Induction Machine Excited by Capacitors     |      |

|          | and Loaded with a Constant Reactive Load Current          | 90   |

| 44       | A Rectifier Providing Constant Magnitude                  |      |

|          | ac Current Loading                                        | 90   |

| 45       | Curves for an Induction Machine Excited by Capacitors     |      |

|          | and with a Voltage Scaled Reactive Load Current           | 91   |

| 46       | The Effect of Scaling dc Current by a Factor K for        |      |

|          | Constant Real Load                                        | 92   |

| 47       | The Qualitative Change to the Effective Reactive          |      |

|          | Current Supply Line due to Constant Real Load             | 93   |

| 48       | The Effect of the Limited Proportional Control on the     |      |

|          | Effective Reactive Current Supply Characteristic          | 95   |

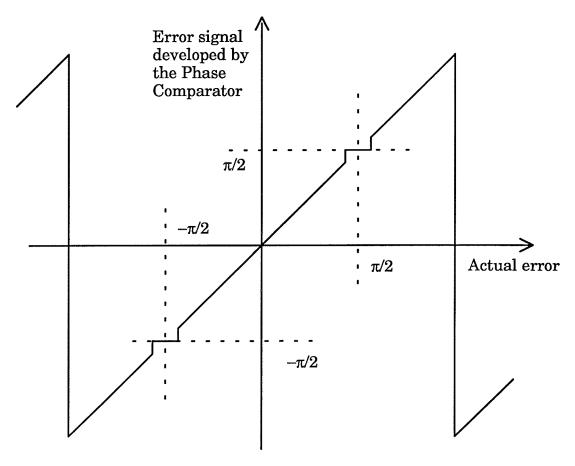

| 49       | Phase Comparator Output versus Actual Phase Error         | 100  |

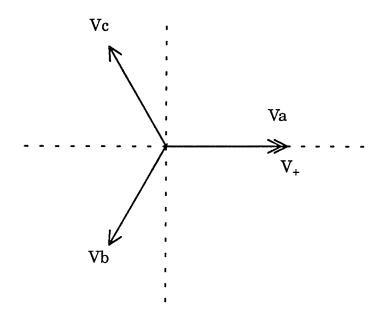

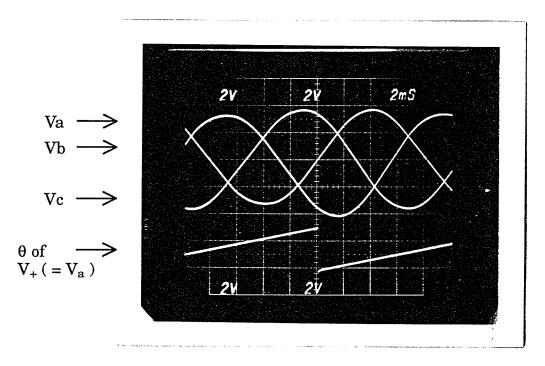

| 50       | PLO Response to Approximately Balanced                    |      |

|          | Three Phase Voltages                                      | 101  |

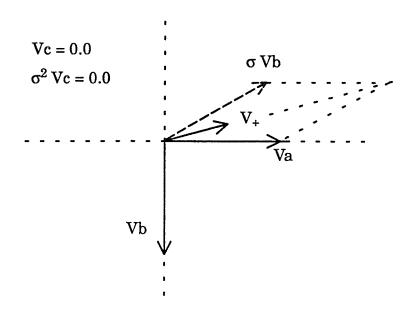

| 51       | PLO Response to Very Unbalanced Three Phase Voltages      | 102  |

## CHAPTER 5

| Figure     | <u>Number</u>                                                 | Page |

|------------|---------------------------------------------------------------|------|

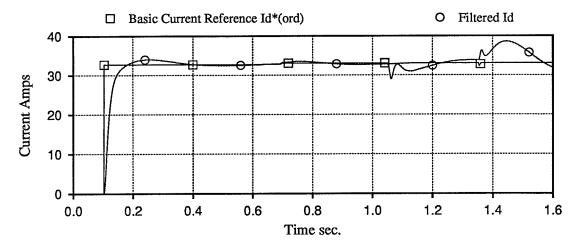

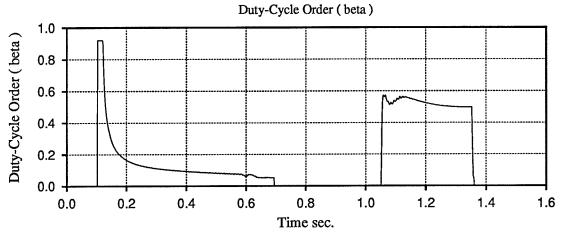

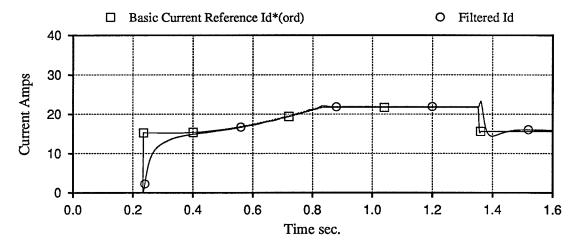

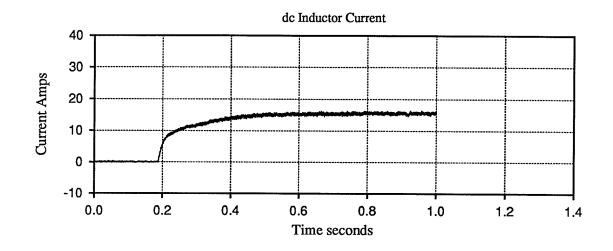

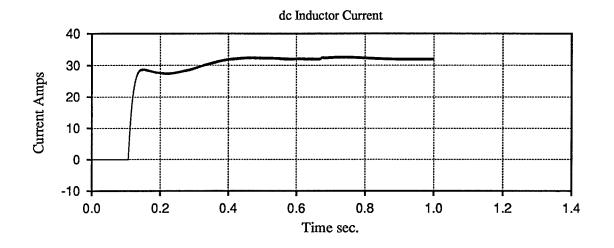

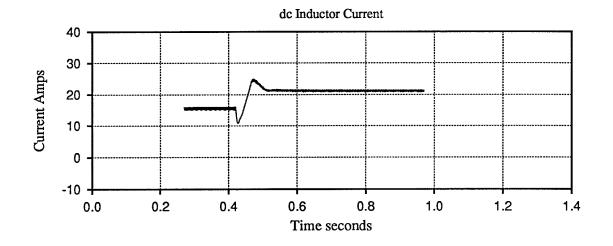

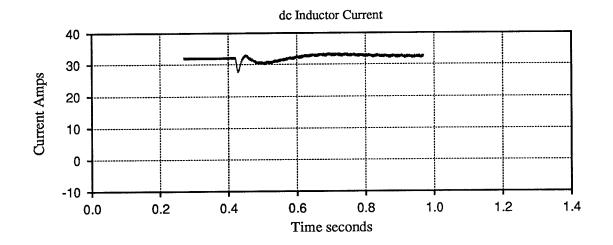

| 52         | Case 1 – dc Currents $I_d$ *(ord) and $I_d$                   | 107  |

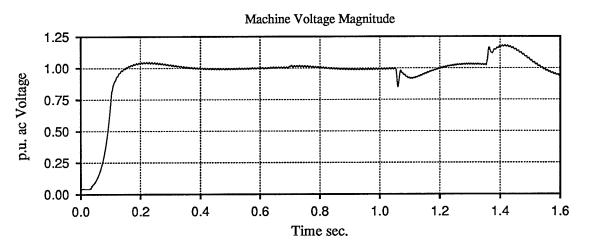

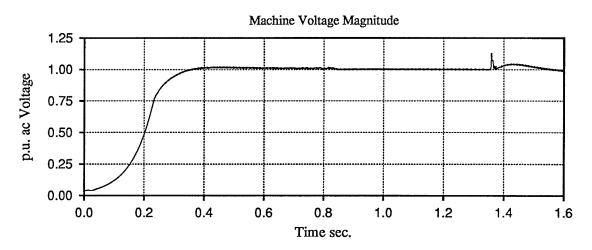

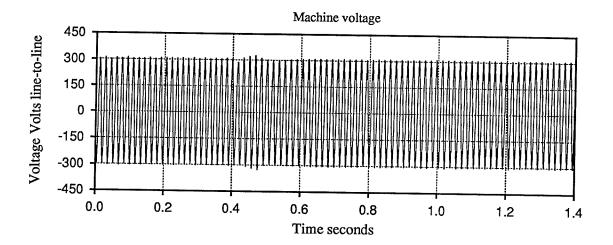

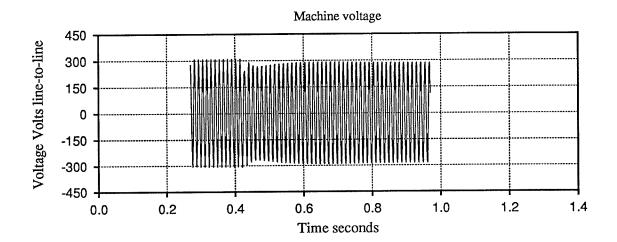

| 53         | Case 1 – Machine Voltage $V_m$                                | 107  |

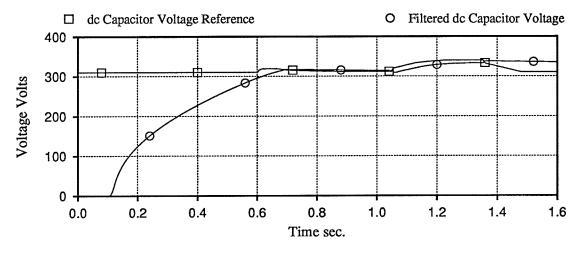

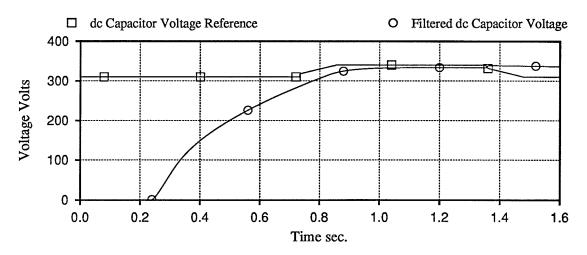

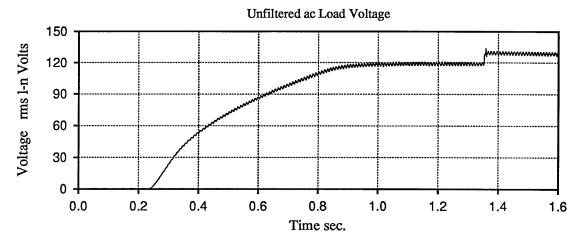

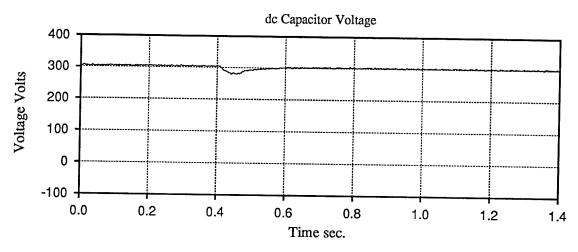

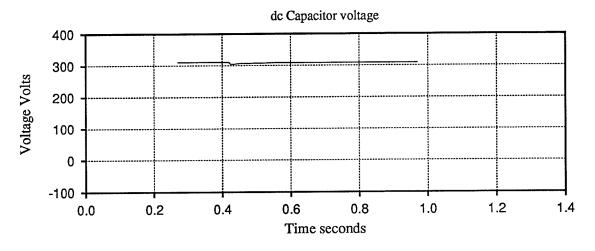

| 54         | Case 1 – dc Capacitor Voltages $V_{\rm Iref}$ and $V_{\rm I}$ | 107  |

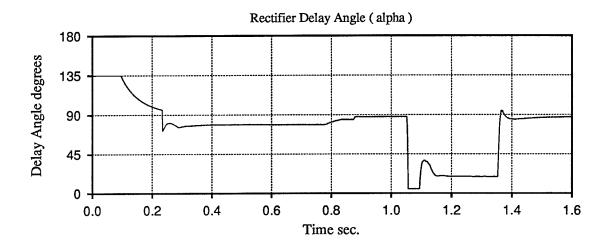

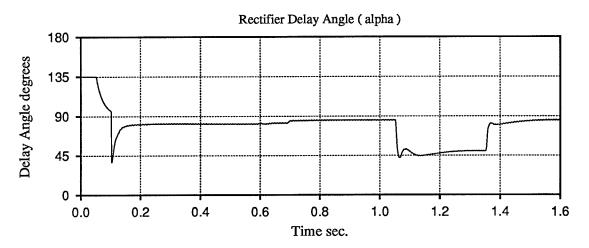

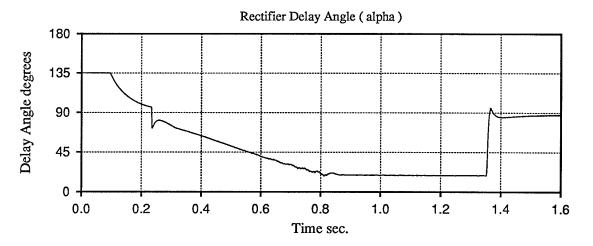

| 55         | Case 1 – Rectifier Delay Angle $\alpha$                       | 108  |

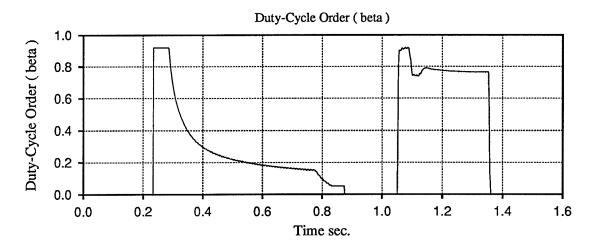

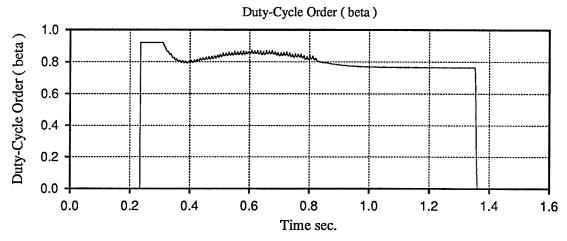

| 56         | Case 1 – The Duty–Cycle Order $\beta$ for the Boost Converter | 108  |

| 57         | Case 1 – Power Order in Per Unit                              | 109  |

| 58         | Case $1 - V_{comp}$ Voltage Signal from the                   |      |

|            | Voltage-boost Converter Controller                            | 109  |

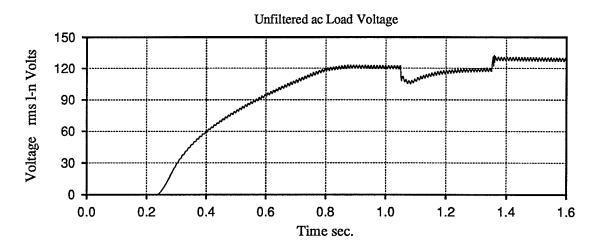

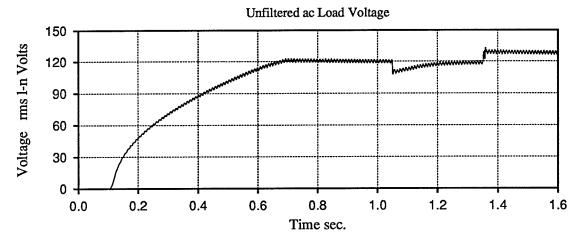

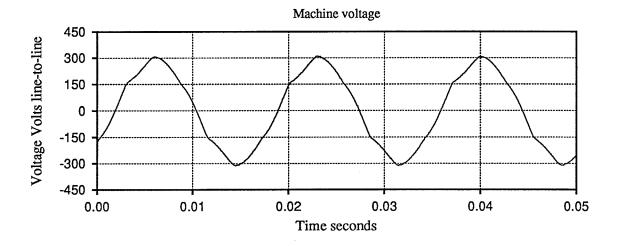

| 59         | Case 1 – Measured ac Load Voltage                             | 110  |

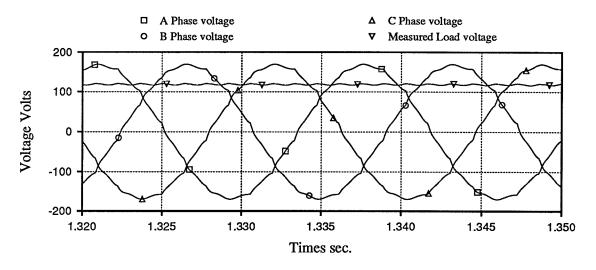

| 60         | Case 1 – Load Voltage Waveshapes                              | 110  |

| 61         | Case $2-dc$ Currents $I_d*(ord)$ and $I_d$                    | 125  |

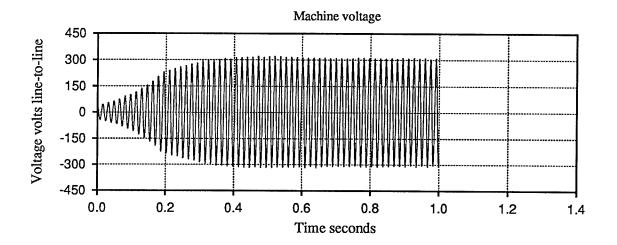

| 62         | $Case\ 2-Machine\ Voltage\ V_{m}$                             | 125  |

| 63         | Case 2 – dc Capacitor Voltages $V_{\rm Iref}$ and $V_{\rm I}$ | 125  |

| 64         | Case 2 – Measured ac Load Voltage                             | 126  |

| 65         | Case $2$ – Rectifier Delay Angle $\alpha$                     | 126  |

| 66         | Case 2 – The Duty–Cycle Order $\beta$ for the Boost Converter | 126  |

| 67         | Case $3-dc$ Currents $I_d*(ord)$ and $I_d$                    | 129  |

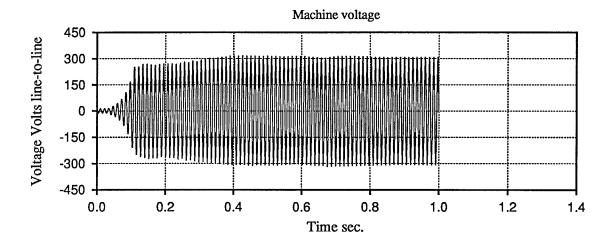

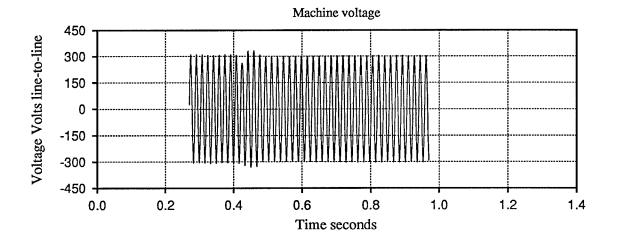

| <b>6</b> 8 | Case 3 – Machine Voltage $V_m$                                | 129  |

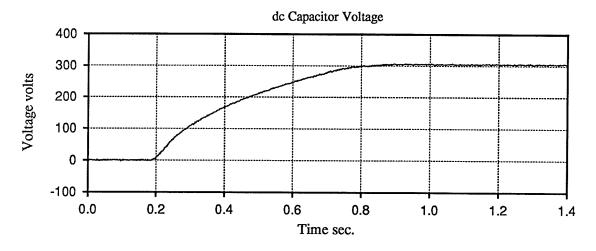

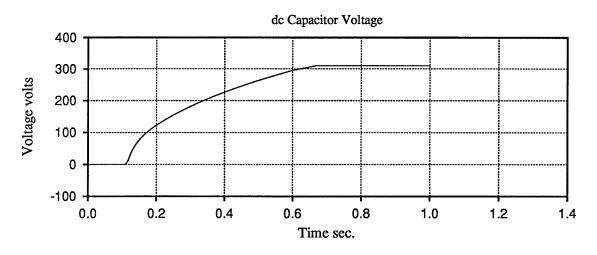

| 69         | Case 3 – dc Capacitor Voltages $V_{\rm Iref}$ and $V_{\rm I}$ | 129  |

| 70         | Case 3 – Measured ac Load Voltage                             | 130  |

| 71         | Case $3$ – Rectifier Delay Angle $\alpha$                     | 130  |

| 72         | Case 3 – The Duty–Cycle Order $\beta$ for the Boost Converter | 130  |

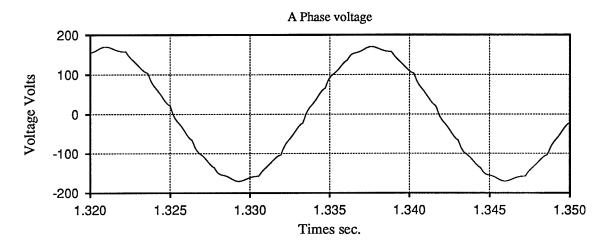

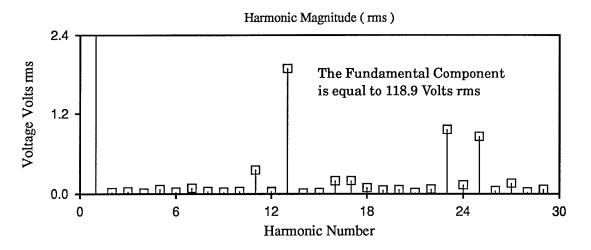

| 73         | Case 3 – Load Voltage at Full Load                            | 131  |

| Figure 1 | <u>Number</u>                                                 | <u>Page</u> |

|----------|---------------------------------------------------------------|-------------|

| 74       | Case 3 – Harmonics of Full Load Voltage                       | 131         |

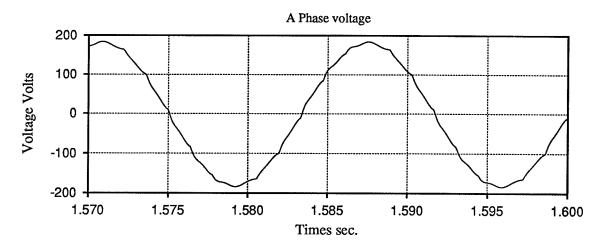

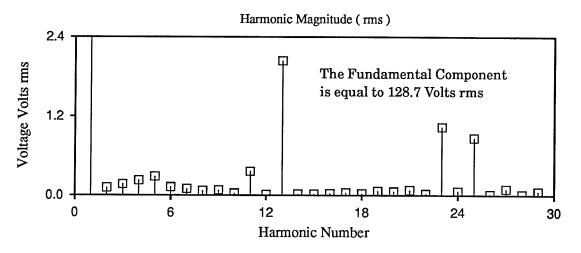

| 75       | Case 3 – Load Voltage at No Load                              | 132         |

| 76       | Case 3 – Harmonics of No Load Voltage                         |             |

|          | (during overvoltage following load rejection)                 | 132         |

| 77       | Case 3 – Transformer Contributions                            |             |

|          | to A Phase Load Voltage                                       | 133         |

| 78       | Case 3 – Composition of Load Voltage                          | 134         |

| 79       | Case 3 – Currents in a Capacitive Loop                        | 134         |

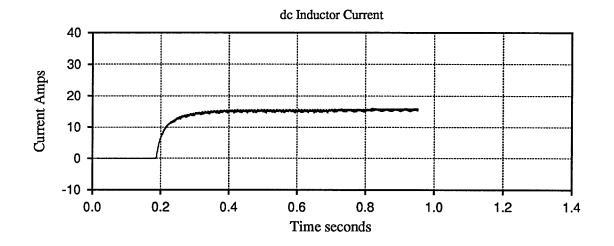

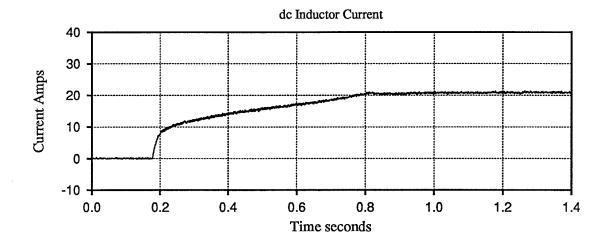

| 80       | Case 4 – dc Currents $I_d$ *(ord) and $I_d$                   | 137         |

| 81       | $Case \ 4-Machine \ Voltage \ V_m$                            | 137         |

| 82       | Case 4 – dc Capacitor Voltages $V_{\rm Iref}$ and $V_{\rm I}$ | 137         |

| 83       | Case 4 – Measured ac Load Voltage                             | 138         |

| 84       | Case 4 – Rectifier Delay Angle $\alpha$                       | 138         |

| 85       | Case 4 – The Duty–Cycle Order $\beta$ for the Boost Converter | 138         |

| CHAPT    | ER 6                                                          |             |

| Figure l | <u>Number</u>                                                 | Page        |

| 86       | Laboratory Test Apparatus                                     | 140         |

| 87       | A Photograph of the Laboratory Test Apparatus                 | 142         |

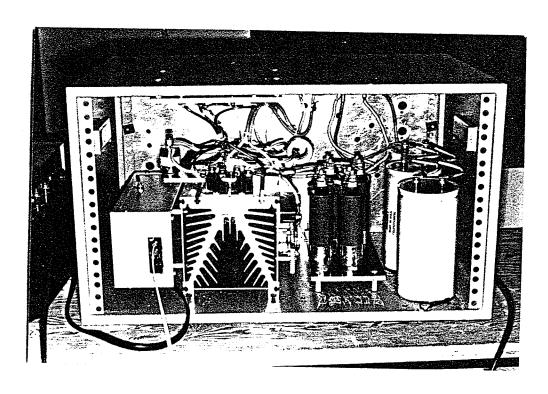

| 88       | A Photograph of the Voltage-boost Converter                   | 143         |

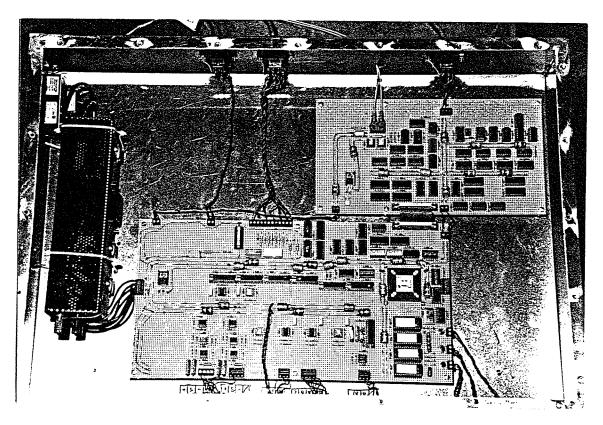

| 89       | A Photograph of the Apparatus Control System                  | 143         |

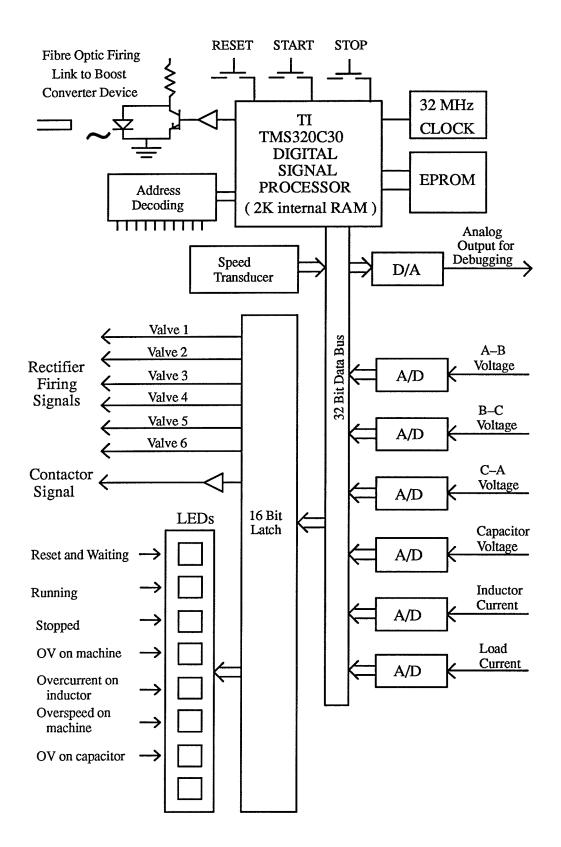

| 90       | The Basic Architecture of the Digital Control                 | 145         |

| 91       | Test 1 – Laboratory Test Results for                          |             |

|          | a No Load Start at 1.0 p.u. Speed                             | 147         |

| Figure N | <u>lumber</u>                                | Page |

|----------|----------------------------------------------|------|

| 92       | Test 1 – Simulation Results for              |      |

|          | a No Load Start at 1.0 p.u. Speed            | 148  |

| 93       | Test 2 – Laboratory Test Results for         |      |

|          | a No Load Start at 1.38 p.u. Speed           | 151  |

| 94       | Test 2 – Simulation Results for              |      |

|          | a No Load Start at 1.38 p.u. Speed           | 152  |

| 95       | Test 2 – Simulation Results for              |      |

|          | a No Load Start at 1.38 p.u. Speed           |      |

|          | with an Altered Integrator Initial Condition | 153  |

| 96       | Test 3 – Laboratory Result for Start-up      |      |

|          | Under Load at 1.0 p.u. Speed                 | 157  |

| 97       | Test 3 – Simulation Result for Start-up      |      |

|          | Under Load at 1.0 p.u. Speed                 | 157  |

| 98       | Test 4 – Laboratory Result for Start-up      |      |

|          | Under Load at 1.38 p.u. Speed                | 158  |

| 99       | Test 4 – Simulation Result for Start-up      |      |

|          | Under Load at 1.38 p.u. Speed                | 158  |

| 100      | Test 5 – Laboratory Result for Applying      |      |

|          | 0.95 p.u. Load at 1.0 p.u. Speed             | 160  |

| 101      | Test 5 – Simulation Result for Applying      |      |

|          | 0.95 p.u. Load at 1.0 p.u. Speed             | 161  |

| 102      | Test 6 – Laboratory Result for Applying      |      |

|          | 0.95 p.u. Load at 1.38 p.u. Speed            | 162  |

| 103      | Test 6 – Simulation Result for Applying      |      |

|          | 0.95 p.u. Load at 1.38 p.u. Speed            | 163  |

| Figure 1 | <u>Number</u>                                          | Page Page |

|----------|--------------------------------------------------------|-----------|

| 104      | Test 7 – Waveshapes from Laboratory Testing during     |           |

|          | Steady-running at 1.0 p.u. Speed with 0.95 p.u. Load   | 165       |

| 105      | Test 7 – Waveshapes from Simulation of                 |           |

|          | Steady-running at 1.0 p.u. Speed with 0.95 p.u. Load   | 167       |

| 106      | Test 8 – Waveshapes from Laboratory Testing during     |           |

|          | Steady-running at 1.0 p.u. Speed with No Load          | 170       |

| 107      | Test 8 – Waveshapes from Simulation of                 |           |

|          | Steady-running at 1.0 p.u. Speed with No Load          | 171       |

| 108      | Test 9 – Machine Voltage Wave from Laboratory Testing  |           |

|          | during Steady–running                                  |           |

|          | at 1.38 p.u. Speed with 0.95 p.u. Load                 | 172       |

| 109      | Test 9 – Simulated Machine Voltage Wave                |           |

|          | for Steady–running                                     |           |

|          | at 1.38 p.u. Speed with 0.95 p.u. Load                 | 172       |

| 110      | Test 10 – Machine Voltage Wave from Laboratory Testing |           |

|          | during Steady–running                                  |           |

|          | at 1.38 p.u. Speed with No Load                        | 173       |

| 111      | Test 10 – Simulated Machine Voltage Wave               |           |

|          | for Steady-running                                     |           |

|          | at 1.38 p.u. Speed with No Load                        | 173       |

| 112      | Test 11 – Laboratory Results for Load Rejection        |           |

|          | of 0.95 p.u. Load at 1.0 p.u. Machine Speed            | 175       |

| 113      | Test 11 – Simulation Results for Load Rejection        |           |

|          | of 0.95 p.u. Load at 1.0 p.u. Machine Speed            | 176       |

| Figure N | <u>Number</u>                                   | <u>Page</u> |

|----------|-------------------------------------------------|-------------|

| 114      | Test 12 – Laboratory Results for Load Rejection |             |

|          | of 0.95 p.u. Load at 1.38 p.u. Machine Speed    | 177         |

| 115      | Test 12 – Simulation Results for Load Rejection |             |

|          | of 0.95 p.u. Load at 1.38 p.u. Machine Speed    | 178         |

| 116      | Test 13 – Laboratory Results for Application of |             |

|          | Overload at 1.2 p.u. Speed                      | 180         |

| 117      | Test 13 – Simulation Results for Application of |             |

|          | Overload at 1.2 p.u. Speed                      | 181         |

| 118      | Test 14 – Laboratory Results showing Recovery   |             |

|          | from Overload at 1.2 p.u. Speed                 | 183         |

| 119      | Test 14 – Simulation Results showing Recovery   |             |

|          | from Overload at 1.2 p.u. Speed                 | 184         |

### List of Symbols

The following list contains symbols which are used frequently in the text. Other symbols which are rarely used in the text are defined where used.

the rectifier firing delay angle. α the voltage-boost converter duty-cycle order. The duty-cycle order β describes the ordered fraction of the voltage-boost converter period during which the GTO device is turned off. the signal describing the actual voltage-boost converter duty-cycle. β\* the angle of the main flux linkage vector with respect to the q-axis ρ in the description of the induction machine. the duration of an integration time-step.  $\Delta T$ the phase error signal produced by the phase comparator in the phase locked oscillator. the vector of machine flux linkages in the dq model of the induction  $[\lambda_{dq}]$ machine. the d-axis armature flux linkage in the induction machine model.  $\lambda_{\rm d}$ the d-axis amortisseur flux linkage in the induction machine model.  $\lambda_{kd}$ the q-axis armature flux linkage in the induction machine model.  $\lambda_{\mathbf{q}}$ the q-axis amortisseur flux linkage in the induction machine model.  $\lambda_{kq}$ the d-axis mutual flux linkage in the induction machine model.  $\lambda_{md}$ the q-axis mutual flux linkage in the induction machine model.  $\lambda_{mq}$ the d-axis armature leakage flux linkage in the induction machine  $\lambda_{sd}$ model.

- $\lambda_{rd}$  the d-axis rotor leakage flux linkage in the induction machine model.

- $\lambda_{\rm sq}$  the q-axis armature leakage flux linkage in the induction machine model.

- $\lambda_{rq}$  the q-axis rotor leakage flux linkage in the induction machine model.

- v machine speed expressed generally in p.u. machine speed

- the output angle from the phase locked oscillator. The phase locked oscillator tracks the positive—sequence fundamental—frequency

( sine wave ) component of the monitored three—phase voltages.

- σ a complex number of magnitude 1 and angle 120°.

- $\omega$  frequency expressed generally in radians per second.

- B<sub>t</sub> susceptance looking into the induction machine terminals.

- C<sub>s</sub> the capacitance of wye-connected self-excitation capacitors.

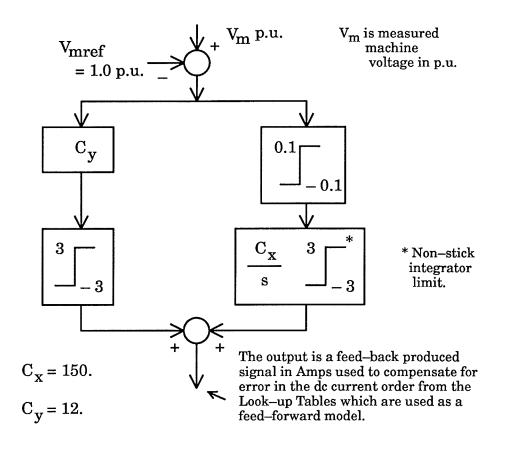

- $C_x$  the integrator gain in the Machine Voltage PI Control Loop.

- C<sub>v</sub> the proportional gain in the Machine Voltage PI Control Loop.

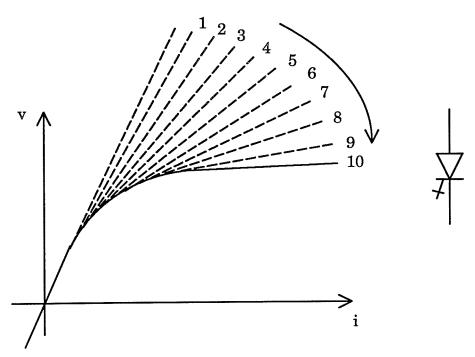

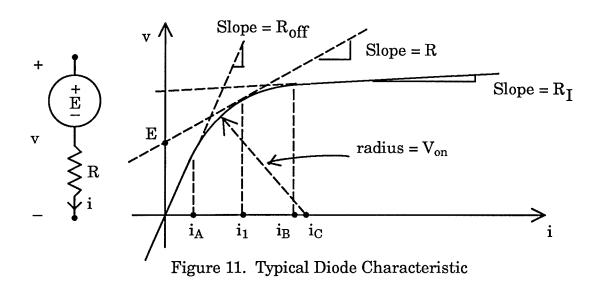

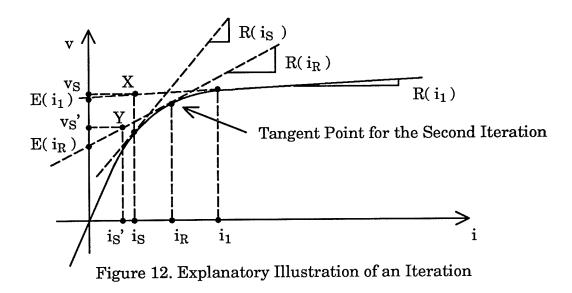

- E(i) the current-dependant voltage source used in representing a device characteristic at a given device current.

- f frequency expressed generally in p.u. frequency.

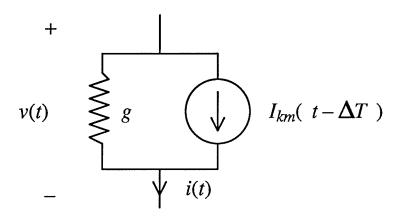

- g the conductance of a given resistor.

- [G] the conductance matrix used in the Dommel algorithm for nodal admittance circuit analysis.

- [ $G_{dq}$ ] the machine generation matrix.

- $G_{t}$  conductance looking into the induction machine terminals.

- i current

- [I] the vector of total current injection used in the Dommel algorithm for nodal admittance circuit analysis.

- I<sub>c</sub> the rms current in a wye-connected self-excitation capacitor

- I<sub>d</sub> the average dc current in the Graetz bridge rectifier.

- $I_{d'}$  the d-axis armature current in the induction machine model.

- [  $I_{dq}$  ] the vector of machine winding currents in the dq model of the induction machine.

- $I_d(ord)$  the final dc current order obtained by adding components of the order in the Rectifier Current Controller.

- $I_d^*(ord)$  the basic dc current reference provided as output from the Look-up Tables.

- $I_h(t-\Delta T)$  the history current term used as an injection in representing a particular branch in the Dommel algorithm for nodal admittance circuit analysis.

- $I_{kd}$  the d-axis amortisseur current in the induction machine model.

- $I_{km}(t\!-\!\Delta T) \ \ the \ history \ current \ term \ used \ as \ an injection \ in \ representing \ a$  branch in the Dommel algorithm for nodal admittance circuit analysis.

- I<sub>q</sub> the q-axis armature current in the induction machine model.

- $I_{kq}$  the q-axis amortisseur current in the induction machine model.

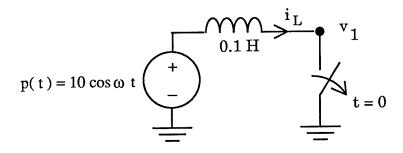

- $I_L$  the dc current provided to the inverter or dc load.

- $I_{md}$  the d-axis magnetizing current causing the d-axis mutual flux linkage in the induction machine model.

$I_{mq}$  the q-axis magnetizing current causing the q-axis mutual flux linkage in the induction machine model.

$I_{m'}$  the net vector of magnetizing current causing the main flux linkage in the induction machine model.

I<sub>m</sub> the rms magnetizing current for the induction machine.

I<sub>R</sub> the rms magnitude of the current into the Graetz bridge rectifier.

$I_{react}$  the rms magnitude of the reactive current into the Graetz bridge rectifier.

$I_{real}$  the rms magnitude of the real current into the Graetz bridge rectifier.

$I_{\rm XL}$  a constant magnitude of rms reactive current into the Graetz bridge rectifier.

K a constant.

K# gains in the control system where # equals 1 to 6.

$K_{\rm I}$  the integral gain in the phase locked oscillator.

$K_p$  the proportional gain in the phase locked oscillator.

L an inductance.

$L_c$  the inductance of the commutating inductors.

L<sub>inc</sub> the incremental inductance at the operating point on the induction machine magnetizing curve. This represents the slope of a line which is tangent to the curve.

$L_{\mathrm{inst}}$  the instantaneous inductance of the induction machine magnetizing curve at the operating point. This represents the slope of a line which passes through the origin and the operating point.

$L_{md}$  the inductance of the d-axis mutual flux linkage in the induction machine model.

$L_{mq}$  the inductance of the q-axis mutual flux linkage in the induction machine model.

$L_s$  the inductance of the armature leakage flux linkage for both the d and q axes in the induction machine model.

$L_r$  the inductance of the rotor leakage flux linkage for both the d and q axes in the induction machine model.

p(t) an independent time varying voltage source.

$P_{\text{base}}$  the base power selected for the power transfer apparatus.

P<sub>t</sub> the power out of the induction machine terminals.

p.u. per unit.

R(i) the current-dependant series resistance used in representing a device characteristic at a given device current.

R<sub>c</sub> the equivalent commutation resistance.

[  $R_{dq}$  ] the winding resistance diagonal matrix used in the dq induction machine model.

$R_{

m I}$  the resistance used to represent a device according to the linear part of a simple v-i characteristic curve for positive current.

$R_{\mathrm{iron}}$  the resistance used in the phasor equivalent circuit of the induction machine to represent the iron losses.

$R_{off}$  the off resistance of a simple characteristic curve for a device.

$R_{\rm r}$  the rotor resistance used in the phasor equivalent circuit of the induction machine.

$R_{rotor}$  the resistance used in the phasor equivalent circuit of the induction machine to represent the quantity  $R_r$ /s.

R<sub>s</sub> the stator resistance used in the phasor equivalent circuit of the induction machine.

s the slip of the induction machine.

S<sub>f</sub> the factor by which the resistance R(i) is allowed to change in one iteration of the electromagnetic transients simulation time-step.

T<sub>#</sub> time constants in the control system where # equals 1 to 6.

$T_{\rm off}$  the time that the GTO device in the voltage—boost converter is off during a period of the voltage—boost converter.

$T_{vbc}$  the period of the voltage-boost converter.

$T_{\rm w}$  the time constant of the low-pass real-pole filter in the phase locked oscillator.

$T_x$  the time constant of the low-pass real-pole filter which filters the magnitude of the ac load voltage in the ac Load Voltage PI Controller.

$T_y$  the time constant of the integrator in the ac Load Voltage PI Controller.

v a voltage.

$V_{\alpha}$  the  $\alpha$  voltage produced in the abc to  $\alpha\beta$  transform of input voltages in the phase locked oscillator.

$V_{\beta}$  the  $\beta$  voltage produced in the abc to  $\alpha\beta$  transform of input voltages in the phase locked oscillator.

[ v(t) ] the node voltage solution vector used in the Dommel algorithm for nodal admittance circuit analysis.

V<sub>a</sub> an A-phase voltage.

V<sub>a</sub>(load) the A-phase load voltage.

V<sub>ac</sub>(load) the rms magnitude of the load voltage.

V<sub>b</sub> a B-phase voltage.

V<sub>b</sub>(load) the B-phase load voltage.

V<sub>c</sub> a C-phase voltage.

V<sub>comp</sub> the compensation voltage provided by the Voltage—boost Converter Controller to the Rectifier Current Controller. The signal represents the present value of the voltage at the load end of the dc inductor. The signal improves the speed with which the Rectifier Current Controller can respond to sudden changes in voltage which would affect the dc current.

V<sub>c</sub>(load) the C-phase load voltage.

V<sub>d</sub> the average dc output voltage of the rectifier.

$V_d(adj)$  the component of the final dc voltage order in the Rectifier Current Controller which arises out of the dc current error.

$V_d(ord)$  the final dc voltage order obtained by adding components of the order in the Rectifier Current Controller.

$V_d$ \*(ord) the basic dc voltage reference provided as output from the Look-up Tables.

$V_{d0}$  the average dc output voltage of a Graetz bridge rectifier fired with zero firing delay angle and disregarding the commutation drop.

[  $V_{dq}$  ] the vector of voltages applied to the windings in the dq model of the induction machine.

$V_g$  the airgap voltage in the phasor equivalent circuit of the induction machine.

- V<sub>I</sub> the voltage on the dc capacitor at the output of the voltage—boost converter. This voltage is used to supply the inverter in the full apparatus and to supply the dc load in the laboratory apparatus.

- $V_{\mathrm{Iref}}$  the intermediate reference value produced by the ac Load Voltage PI Controller for the voltage on the dc capacitor which is located at the output of the voltage—boost converter.

- V<sub>on</sub> the radius of the arc that makes up part of the simple characteristic curve for a switching device. This voltage basically describes the forward voltage drop on the device.

- V<sub>m</sub> the rms magnitude of the machine terminal voltage.

- $V_{mref}$  the rated machine terminal voltage which is used as a reference in the apparatus.

- V<sub>t</sub> the rms magnitude of the machine terminal voltage.

- V<sub>+</sub> the positive-sequence fundamental-frequency voltage component.

- $X_r$  the rotor leakage inductance used in the phasor equivalent circuit of the induction machine expressed in units of Ohms per p.u. frequency.

- $X_s$  the stator leakage inductance used in the phasor equivalent circuit of the induction machine expressed in units of Ohms per p.u. frequency.

- $X_m$  the magnetizing inductance used in the phasor equivalent circuit of the induction machine expressed in units of Ohms per p.u. frequency.

- $X_L$  the reactance of the commutation inductors expressed in units of Ohms per p.u. frequency.

### Chapter One

#### Introduction

#### 1.1 General Introduction

This thesis describes the development of an apparatus for supplying an isolated ac load from an induction generator operable at variable speed. The ac voltage supplied to the load is well regulated in frequency and magnitude.

Induction generators have certain advantageous features which promote their use. The main feature is that an induction machine can include a robust squirrel—cage rotor rather than a wound rotor. The use of the sturdy squirrel—cage rotor obviates the need for brushes and a separate source of dc excitation current which are required for a synchronous machine. Another advantage is that an induction generator typically has lower unit cost and maintenance costs than a synchronous generator.

In isolated operation, the excitation current for an induction generator can be supplied by capacitors connected at the terminals of the machine. Such a configuration is known as a self–excited induction generator. However, the output voltage and frequency of a self–excited induction generator are highly dependent on rotor speed, terminal capacitance and load [1,2,3]. Significant variation in either load or shaft speed during operation of the self–excited induction generator thus dictates the need for additional apparatus to control and condition the output. This thesis describes power electronic apparatus which provides the required control and conditioning.

#### 1.2 Background and Scope of the Thesis

Considerable prior work has been done in researching the use of self-excited induction machines.

Several investigators have looked at supplying load directly from the three phase induction machine terminals [4,5,6,7]. In such a configuration frequency is regulated using precise machine speed control and voltage magnitude is regulated using an arrangement of switched capacitors [4,7] or a static compensator [4,5,6] for excitation control.

Alternatively several other investigators [8,9,10] have looked at supplying a dc load from the rectified output of a self–excited induction machine. These investigators relied on the reactive power absorbed by a Graetz bridge rectifier to help control machine voltage. However no mechanism remains for machine voltage control when dc load and thus the rectifier current go to zero. Furthermore these techniques can only regulate dc output voltage for narrow ranges of load resistance and machine speed.

Yet other investigators [11,12,13] have looked at asynchronously linking the output of a self—excited induction generator to an existing ac system through a dc link. These latter schemes are unable to supply isolated ac load.

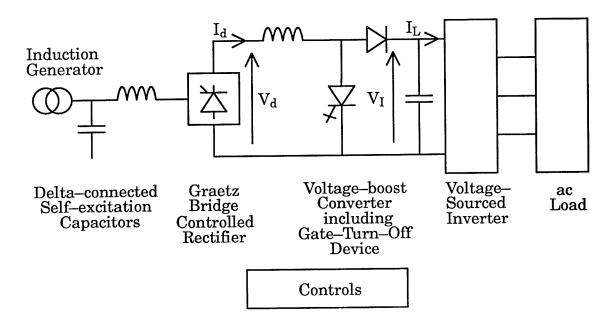

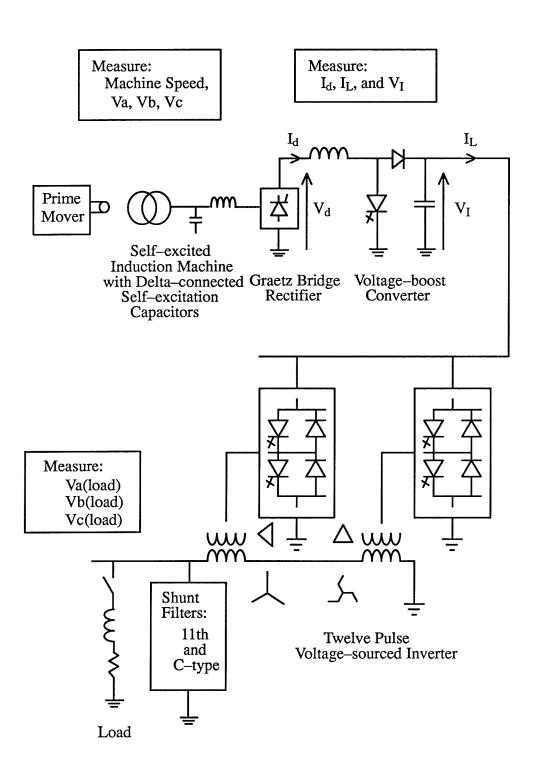

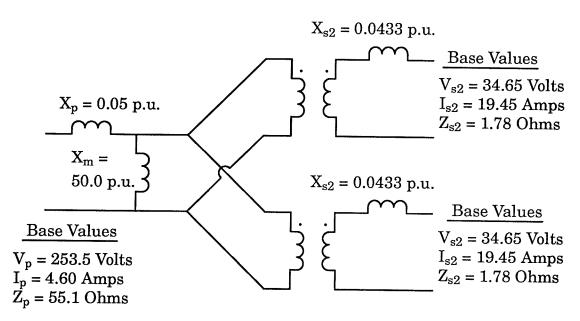

This thesis develops apparatus as illustrated in Figure 1 for supplying isolated ac load from a self-excited induction generator through a dc link. A voltage-boost converter is used in the apparatus between the Graetz bridge rectifier and the voltage-sourced inverter. This arrangement of power equipment enables the apparatus to be designed for operation in a specified range of machine speed (e.g. 1.0 to 1.4 p.u. speed) with 0.0 to 1.0 p.u. load. In these operating ranges machine voltage is regulated to 1.0 p.u. and the output voltage is well-regulated in frequency and magnitude. In the event that the load requires regulated dc voltage rather than ac voltage then the supply can be provided directly from the regulated output of the voltage-boost converter. The controls which have been developed respond quickly and accurately to transient load conditions including application and rejection of full load at any speed in the specified operating range. The controls have been experimentally tested for dc loads.

Figure 1 - Configuration of Developed Apparatus

# 1.3 The Choice of Apparatus Configuration

The apparatus is made up of four main power system components. They are, as illustrated in Figure 1, the induction generator; the Graetz bridge rectifier; the voltage—boost converter; and the voltage—sourced inverter.

Various authors [1,2] have listed the beneficial attributes of a squirrel—cage induction generator. The use of a squirrel—cage induction generator eliminates the need for slip rings and a separate source of dc excitation current which are required when a synchronous generator is used. Also unit costs and maintenance costs for induction generators are generally lower than those for synchronous generators.

In order to permit variable speed operation of the induction generator it is necessary to provide an asynchronous link between the generator and the load.

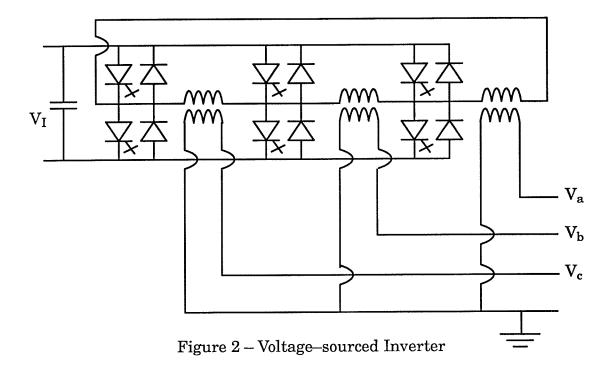

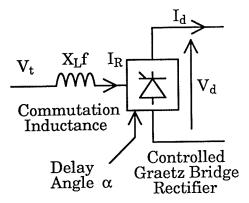

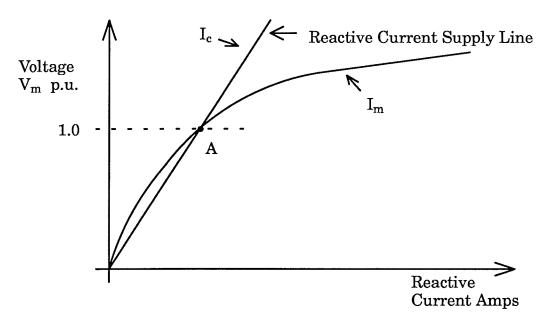

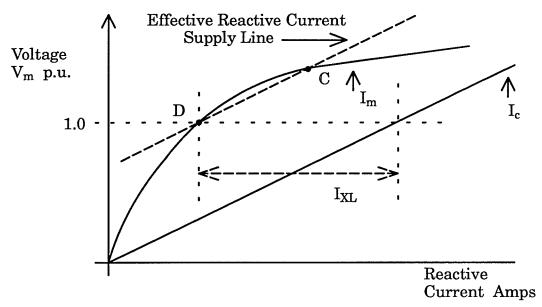

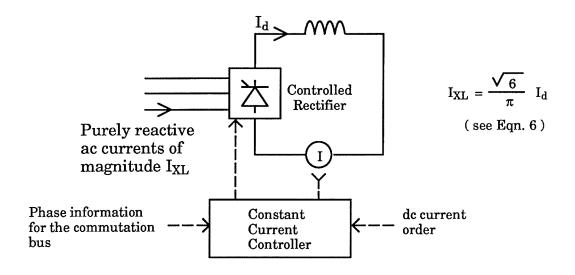

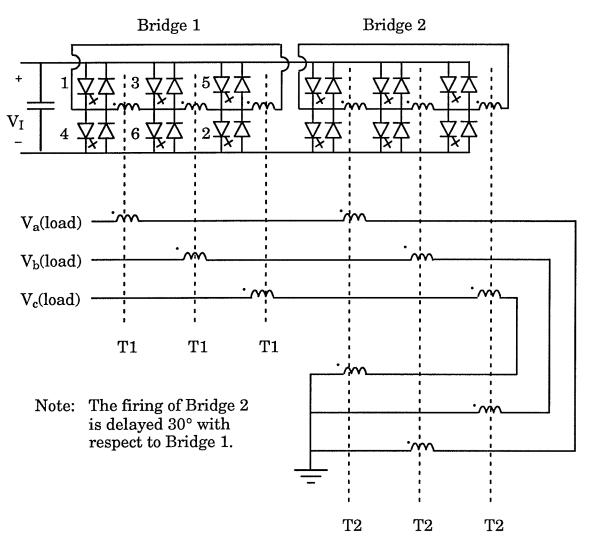

Provision of the dc link thus requires the selection of a suitable rectifier and inverter. The rectifier type is chosen to satisfy the requirements of operating the induction generator. The self-excitation capacitors on the terminals of the induction generator provide excitation current for the machine. However, at higher speeds these capacitors provide more VARS (volt-amperes reactive power) than the machine requires for operation at 1 p.u. terminal voltage. The rectifier in the apparatus is required to absorb the excess reactive power. The rectifier must also absorb sufficient real power to supply the load. The need to simultaneously absorb certain levels of real and reactive power into the rectifier dictates that a rectifier should be chosen which permits control of the input power factor. The well-known controlled Graetz bridge rectifier has been chosen because it is a very simple bridge and because power factor control can be accomplished through control of the firing delay angle. The choice of inverter is based primarily on the need for acceptable transient response during complete rejection of the ac load. The selected voltage-sourced inverter can be modelled as a voltage source behind a reasonably small (e.g. 0.1 p.u.) reactance. Therefore rejection of the ac load will result in only small changes in the load voltage. The change is related to the on-load voltage drop across the inverter transformer reactance. A schematic for a six-pulse voltage-sourced inverter is illustrated in Figure 2.

The Graetz bridge rectifier is chosen to meet the needs of the self—excited induction generator and the voltage—sourced inverter is chosen to meet the needs of the ac load. However, the variable dc output voltage of the rectifier is not compatible for directly supplying the required relatively fixed dc voltage needed at the input of the voltage—sourced inverter. This is evident from a consideration of operation at light load. At light load the rectifier must absorb almost no real power from the induction machine while continuing to absorb reactive power to control the induction machine voltage. The rectifier must therefore be operated

with a delay angle of approximately 90 ° in order to have the proper power factor for absorbing the reactive power. Operation at approximately 90 ° corresponds with almost zero average rectifier output voltage. The very low output voltage will not sustain current flowing from the output of the rectifier to the higher voltage on the capacitor at the input of the voltage—sourced inverter. Without the presence of rectifier current the rectifier cannot regulate the machine voltage and even the small acload will not be supplied. It is therefore apparent that the output of the Graetz bridge rectifier cannot be directly connected to the input of the voltage—sourced inverter.

It is shown in this thesis that a voltage—boost converter can be successfully used as an interface between the output of the controlled Graetz bridge rectifier and the input to the voltage—sourced inverter. The voltage—boost converter operates properly only when it is called upon to boost voltage. The minimum reference level for the voltage on the capacitor at the input of voltage—sourced invert-

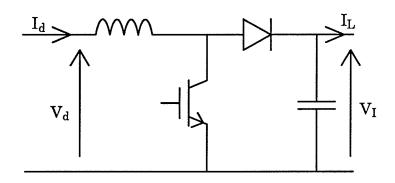

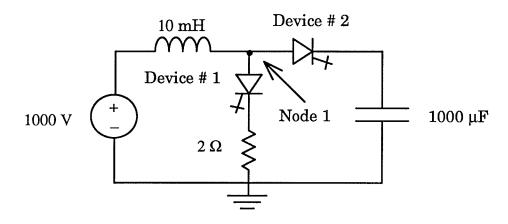

er is thus chosen to be higher than the maximum output of the rectifier for 1.0 p.u. machine voltage. A voltage—boost converter is illustrated in Figure 3.

Figure 3 – Voltage-boost Converter

It will be noted that the voltage—boost converter is a simple apparatus which includes only one GTO (gate—turn—off) device and one diode device in addition to the dc smoothing inductor and dc smoothing capacitor normally used with the Graetz bridge rectifier and the voltage—sourced inverter. The symbol for the GTO device illustrated in Figure 3 is the symbol for the insulated gate bipolar transistor (IGBT) used in the experimental apparatus. In steady running the output voltage  $V_{\rm I}$  of the voltage—boost converter is related to the average input

voltage  $V_d$  according to  $\frac{V_d}{V_I} = \beta$  where duty cycle  $\beta$  is the fraction of the period of the GTO device during which the device is "off". Controls are developed in this thesis which simultaneously control the duty—cycle order to the voltage—boost converter and the delay angle order to the rectifier so as to provide acceptable steady running and transient operation.

#### 1.4 Outline of the Thesis

The thesis contains seven chapters.

The first chapter provides a brief description of the apparatus and techniques used by earlier investigators and then proceeds to give a brief description of the apparatus which has been developed in the thesis. The choice of converters in the apparatus is explained.

The second chapter describes a non–linear search technique for producing characteristic curves descriptive of operation of the apparatus with the induction machine voltage regulated to 1.0 p.u. voltage. Curves are produced for machine speeds between 0.95 and 1.6 p.u. speed and for load power between 0.0 and 1.0 p.u. power. These curves disclose the steady operating characteristics of the apparatus. Characteristic curves for average rectifier output voltage  $V_d$  and current  $I_d$  are used as a model in a feed–forward control system described later in this thesis. The feed–forward control system is supplemented by feed–back control loops to correct for small errors between the model and the real system.

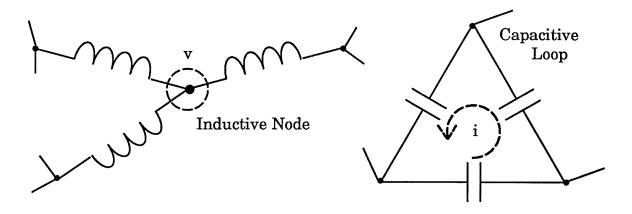

The third chapter describes simulation techniques which have been implemented in a prototype transients simulation program written as part of the thesis work. The program is particularly adapted to the simulation of GTO and other power—electronic devices at a system level. Two time—step sizes are used in the program. Individual switching devices are represented according to simple characteristic curves. The modified algorithm includes iteration of a time—step when required to provide solutions on the curves. A technique is described for suppressing numerical oscillations in solutions for currents in capacitive loops and for voltages at inductive nodes. Nodes are termed inductive nodes when the incident branches are inductive. A brief description is given of an improvement in the transients simulation modelling of saturation of the main flux path in an

induction machine. The improvement in representation of saturation has also been developed by others [14]. The effectiveness of the improvement is demonstrated by comparison of simulation results to laboratory results.

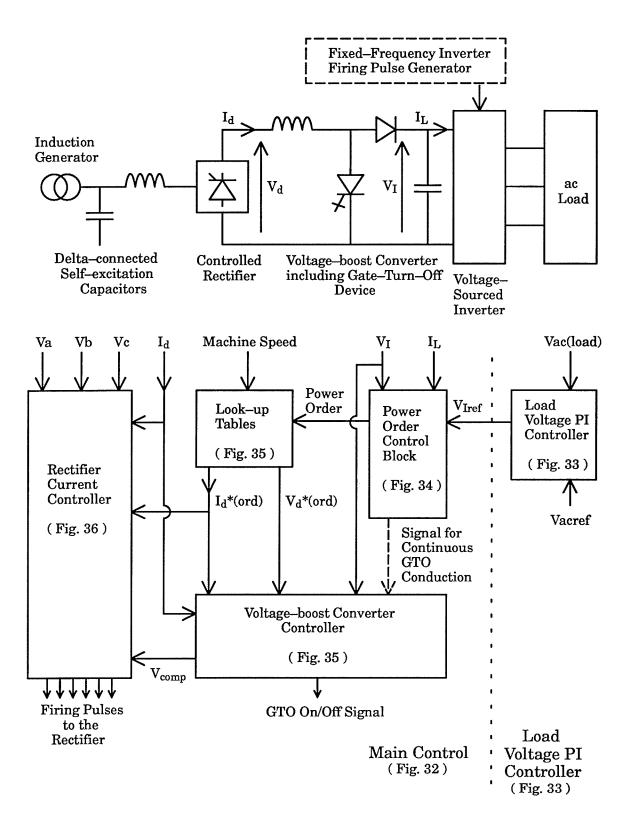

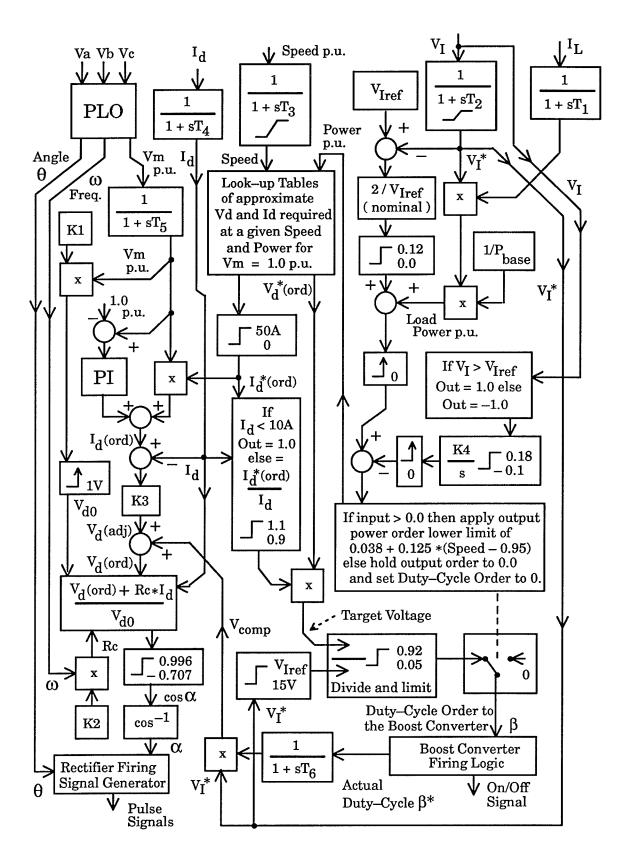

The fourth chapter describes the development of a control system for coordinated control of the voltage—boost converter duty cycle and the controlled rectifier delay angle.

The fifth chapter presents simulation results which demonstrate the good steady running performance and transient response of the apparatus which is provided by the control system. The simulated disturbances include instantaneous full—load rejection. It is demonstrated through simulation that the output ac voltage of a twelve pulse voltage—sourced inverter can be filtered using a reasonable amount of filter apparatus so as to be acceptable for most loads.

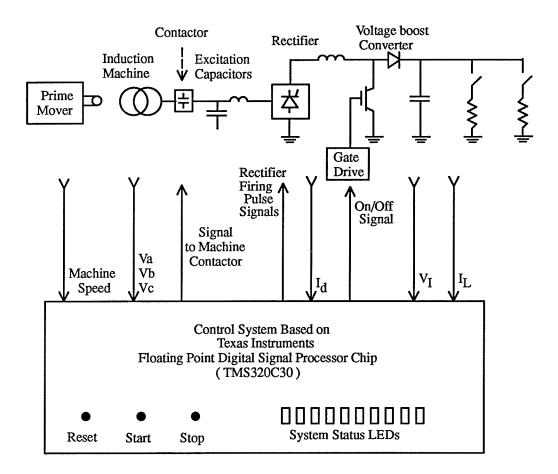

The sixth chapter describes an experimental apparatus which has been built and tested in the laboratory to confirm the simulated operation of the apparatus. The apparatus includes a self–excited induction machine; a controlled Graetz bridge rectifier; a voltage–boost converter; a dc load; and a digital control system. The induction machine is a high power factor squirrel–cage induction motor described in Appendix I. A high power factor machine is used in order to keep the required self–excitation capacitors as small as possible. The reduced capacitor size reduces the level of excess VARS produced during high speed operation. This in turn reduces the current ratings of the rectifier; the dc smoothing inductor; and the voltage–boost converter. The voltage–boost converter includes a 50 Amp 1000 Volt IGBT (insulated gate bipolar transistor). An IGBT gate firing card including fibre optic isolation was designed and built as part of the thesis work. The digital control system is based on a 33 MHz Texas Instruments TMS320C30 floating–point DSP (digital signal processor) chip. The control system

tem was also designed, built, and programmed by the author. The transient responses observed in the laboratory generally correlate well with the responses predicted by transients simulation. Minor differences between simulated and actual responses are discussed and explained.

Chapter seven presents conclusions and contributions from the work.

### **Chapter Two**

## Steady-state Characterization of the Apparatus

### 2.1 Description of the Steady State Characterization

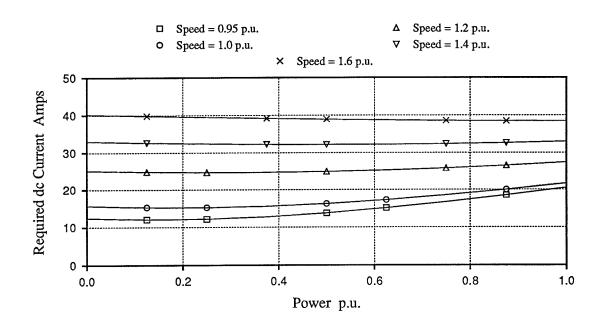

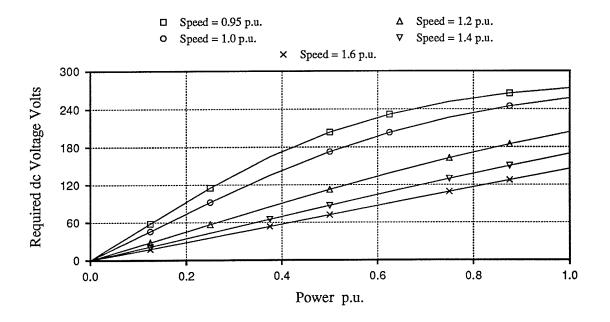

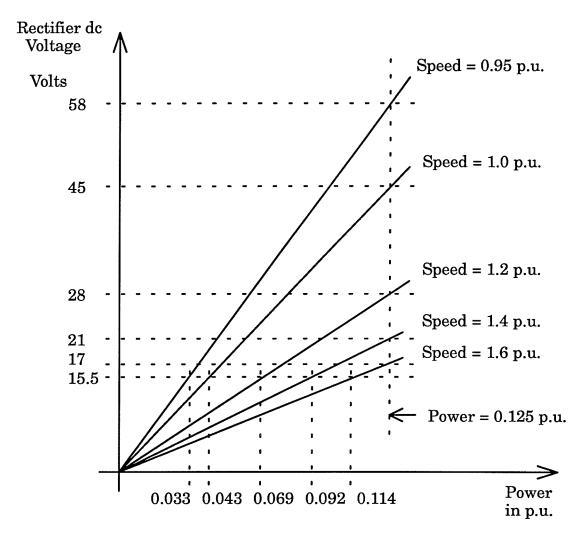

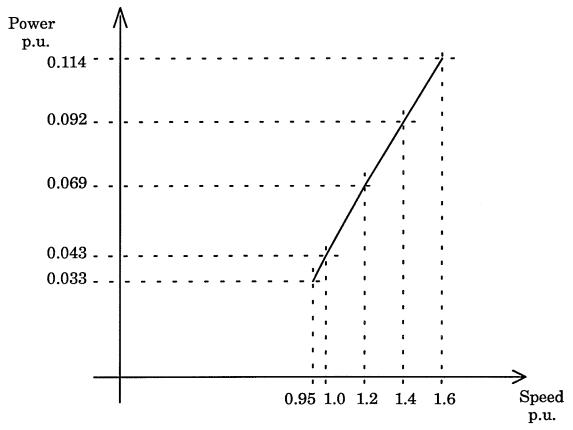

Certain data must be calculated using a steady state equivalent circuit of the induction machine prior to building the apparatus illustrated in Figure 1. Different models of induction machines have different saturation curves. Therefore, it will be necessary to calculate the capacitance of the self–excitation capacitors  $C_S$  whenever a different machine is included in the apparatus design. This chapter describes a method for the calculation of capacitance  $C_S$ . In addition, the apparatus design must enable operation of the apparatus within specific ranges of machine speed and output power. Therefore, for any permitted combination of speed and load, it is useful to know the values of average rectifier voltage  $V_d$  and current  $I_d$  which will supply the load power and properly regulate the machine voltage. This chapter describes a method for calculating curves of  $V_d$  and  $I_d$  required for specified ranges of machine speed and load power. Curves for the test apparatus are illustrated in Figures 7 and 8.

A non–linear search procedure for obtaining curves which characterize the operation of the self–excited induction machine at 1.0 p.u. voltage is described in section 2.3. The characterization of the induction machine enables the calculation of required capacitance  $C_S$  and the curves of  $V_d$  and  $I_d$  described above. The curves of  $V_d$  and  $I_d$  are ultimately used as a model in the feed–forward part of a control system described in chapter 4.

A choice has been made to operate the machine at constant 1.0 p.u. terminal voltage during variations in speed rather than operate at constant flux. This is beneficial because it eliminates continuous overvoltage on stator insulation at

high speed. It also is suitable because it was decided to generate the same maximum power at maximum speed as can be generated at minimum speed. The output power capability remains essentially constant at 1.0 p.u. machine voltage with an increase in speed because the speed increase balances the decrease in the maximum possible torque which is associated with reduced flux due to operation at constant machine voltage and increased frequency.

### 2.2 The Steady-State Equivalent Circuit for the Induction Machine

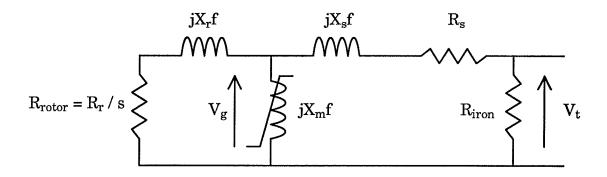

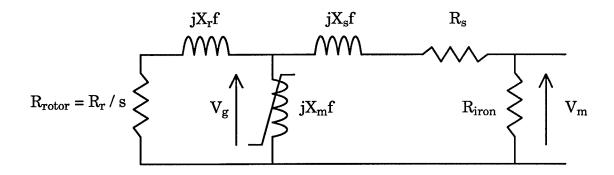

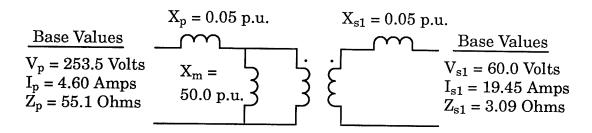

Earlier investigators [1,2] have confirmed the acceptability of a steadystate equivalent circuit representation of the induction machine. The equivalent circuit is illustrated in Figure 4.

Figure 4 - Induction Machine Equivalent Circuit

In order to slightly improve the accuracy of the model, a representation of iron losses has been added through the inclusion of the iron—loss resistor at the terminals of the equivalent circuit. The iron—loss resistor was included at the terminals of the machine rather than at the magnetizing branch because of convenience of modelling. Positioning the iron—loss resistance on the terminal side of the stator leakage impedance rather than parallel to the magnetizing branch typically will not cause significant error in simulating a self—excited induction machine because  $R_{\rm rotor}$ ,  $X_{\rm m}$ , and  $R_{\rm iron}$  are typically much larger in magnitude

than  $R_s$  and  $X_s$ . The iron loss resistance appropriate for the machine described in Appendix I is  $R_{iron} = 32.3$  p.u.

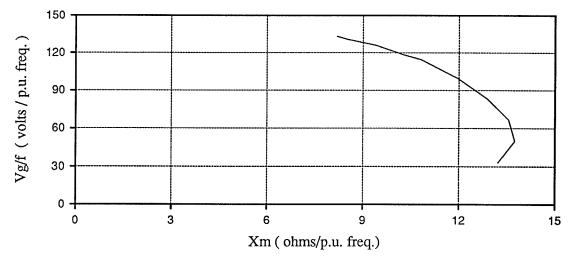

In Figure 4, the reactances  $X_m$ ,  $X_r$ , and  $X_s$  are descriptive of reactance at 1 p.u. frequency. Therefore, as illustrated in Figure 4, it is necessary to multiply these reactances by p.u. frequency "f" in order to obtain true reactances at frequencies other than 1.0 p.u. frequency. In accordance with existing practise [1,2], the relation between air—gap voltage and magnetizing reactance is expressed according to a curve  $\frac{V_g}{f}$  versus  $X_m$ . The curve for the test machine, based on the data in Appendix I, is illustrated in Figure 5. This curve is used in the non–linear search procedure to include the effect of saturation of the main flux path.

Figure 5 -  $V_g/f$  versus Xm Saturation Curve

#### 2.3 The Non-linear Search Procedure

In order to characterize the operation of the overall apparatus shown in Figure 1, it is first necessary to characterize the operation of the machine at 1.0 p.u. voltage over the speed and power ranges of interest. Characterization of the machine allows selection of the size of the self–excitation capacitors (section 2.4)

and generation of curves of  $I_d$  and  $V_d$  in Figures 7 and 8 descriptive of the operation of the overall apparatus ( section 2.5 ).

The objective of this section is to provide a method of characterizing the operation of the induction machine alone at 1.0 p.u. voltage over the desired operating ranges of machine speed and load power. A non–linear search procedure has been developed to provide a solution for slip s; frequency f; saturated magnetizing impedance  $X_m$ ; admittance looking into the machine terminals  $G_t + jB_t$ ; and current (real and reactive) into the machine for a given combination of output power  $P_t$  and speed  $\nu$ . In order to characterize the machine for the speed and power ranges of interest, the non–linear search procedure was conducted at 45 combinations of output power and machine speed to determine the steady–state operating characteristics of the machine. However, for the purposes of explaining the search procedure, it is sufficient to describe the procedure for finding a single steady–state solution at a given machine speed  $\nu$  and output power  $\nu$ .

It is necessary first of all to select the search variables for the search procedure. The terminal voltage  $V_t$  and the real power  $P_t$  out of the machine represented in Figure 4 are dependant solely upon the saturation  $X_m$  and the frequency f for a given machine speed  $\nu$ . The effective rotor resistance  $R_{rotor}$  (  $R_{rotor}$  is equal to  $R_r/s$ .) is related directly to frequency "f" at a given speed  $\nu$  because slip s is equal to  $(1-\nu/f)$ . In addition, the dependence of air—gap voltage  $V_g$  upon  $X_m$  and f according to the curve in Figure 5 can alternatively be treated as a dependence upon  $X_m$  and  $R_{rotor}$ . It is therefore possible to use  $X_m$  and  $R_{rotor}$  as the search variables rather than  $X_m$  and f.

The objective is to search over  $X_m$  and  $R_{rotor}$  until  $V_t$  = 1.0 p.u. and the desired power  $P_t$  is obtained at the given speed  $\nu$ . However, the objective  $P_t$  can be transformed into a more convenient form. At the solution point  $(X_m, R_{rotor})$  the voltage

$V_t$  will be equal to 1 p.u. and therefore the desired power  $P_t$  at the solution point can be transformed into a desired conductance  $G_t$  looking into the terminals of the machine.

The search is thus carried out over  $R_{rotor}$  and  $X_m$  and the objective is to obtain both  $V_t$  equal to 1.0 p.u. voltage and the desired conductance  $G_t$  looking into the machine terminals. However it is useful to note that terminal conductance  $G_t$  is strongly dependant on  $R_{rotor}$  and only weakly dependant on  $X_m$ . Conversely, terminal voltage  $V_t$  is strongly dependant on saturation in  $X_m$  and only weakly dependant on  $R_{rotor}$ .

The strong dependance of  $V_t$  on  $X_m$  and the strong dependance of  $G_t$  on  $R_{rotor}$  forms the basis for the selection of the search routine. The search routine begins with an initial estimate of  $R_{rotor}$  and  $X_m$ .  $R_{rotor}$  is then searched until  $G_t$  is at the desired value. A single change to  $X_m$  is then made to improve  $V_t$ . The change in  $X_m$  is followed by a search of  $R_{rotor}$  to again bring  $G_t$  to the desired value. The pattern of single changes to  $X_m$  each followed by a search of  $R_{rotor}$  is repeated until  $X_m$  has been searched and both  $V_t$  and  $G_t$  are at their desired values. In the case of  $V_t$  the desired value is always 1 p.u. voltage. The weak dependance of  $G_t$  on  $X_m$  and the weak dependance of  $V_t$  on  $R_{rotor}$  assures that convergence occurs quite rapidly.

Sufficiently accurate initial estimates for  $R_{rotor}$  and  $X_m$  can be obtained by ignoring  $R_s$ ,  $X_s$ , and  $X_r$  in Figure 4. In that case,  $R_{rotor}$  can be estimated from  $(1/R_{rotor}) = (G_t - 1/R_{iron})$ . The estimate of  $R_{rotor}$  allows an estimate of slip s to be calculated from  $R_{rotor} = R_r/s$ . An estimate for slip at a given speed v allows an estimate of frequency f to be calculated. Ignoring stator inductance  $X_s$  and resistance  $R_s$  indicates that air—gap voltage  $V_g$  should be estimated as  $V_g = V_t = 1.0$  p.u. Finally, the estimates for  $V_g$  and f allow an estimate of  $X_m$  from the

$V_g\,/\,f$  versus  $X_m$  curve in Figure 5. In this manner, adequate initial estimates for  $R_{rotor}$  and  $X_m$  can be obtained.

The non–linear search procedure was conducted at nine values of power between 0 and 1 p.u. power for each of five different values of machine speed  $\nu$  between 0.95 and 1.6 p.u. speed. For each combination of  $P_t$  and  $\nu$ , a record was made of the solution for s, f,  $X_m$ ,  $G_t$ , susceptance  $B_t$ , and current (real and reactive) into the machine. By this method a record was made of the operating characteristics of the machine at 1.0 p.u. voltage for the speed and power ranges of interest. The solution for the 45 combinations of  $\nu$  and  $P_t$  required a few minutes of computer time.

# 2.4 Calculation of the Required Self-excitation Capacitance

The self–excitation capacitors must produce reactive current sufficient to supply the needs of the induction machine and the rectifier. In determining the capacitance  $C_S$ , for operation of the machine at 1.0 p.u. voltage, it is necessary to note that the maximum reactive power is absorbed by the machine when it is operated at the minimum machine speed and the maximum load. Furthermore, operation of the machine at minimum speed and 1.0 p.u. load causes operation at the minimum frequency f . Operation at the minimum frequency f causes the minimum reactive power to be produced by the self–excitation capacitors at 1 p.u. voltage. Operation at minimum speed and maximum power therefore represents the case that determines a lower limit for the capacitance  $C_S$  of the self–excitation capacitors.

As noted above, the self–excitation capacitors must provide the reactive current for both the rectifier and the machine. The non–linear search procedure described in section 2.3 gives the reactive current absorbed by the machine at all speeds and output powers of interest at  $V_t = 1.0 \ \mathrm{p.u.}$  voltage. This section de-

scribes the calculation of the reactive current absorbed by the rectifier at minimum speed and maximum load. Determination of the reactive current absorbed by the machine and rectifier leads directly to the calculation of the required capacitance  $C_S$  of the self–excitation capacitors.

The rectifier should be forced to absorb as little reactive power as possible at minimum speed and maximum load so that the capacitance  $C_S$  can be kept to a minimum. Maximum loading dictates that the rectifier must simultaneously absorb 1.0 p.u. real power. Therefore, at minimum speed and maximum load, the rectifier should be operated at minimum delay angle  $\alpha$  (e.g.  $\alpha$  = 5  $^{\rm O}$ ) so that the power factor of the current into the rectifier can be maintained as high as possible.

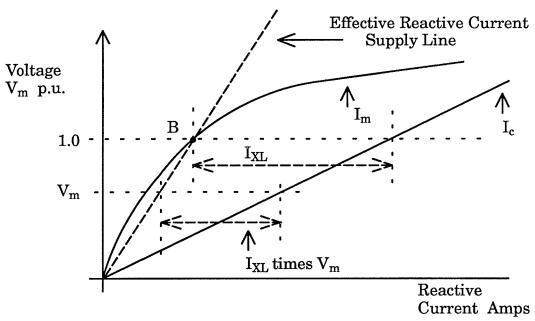

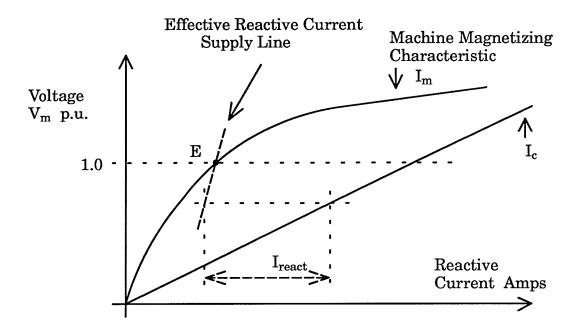

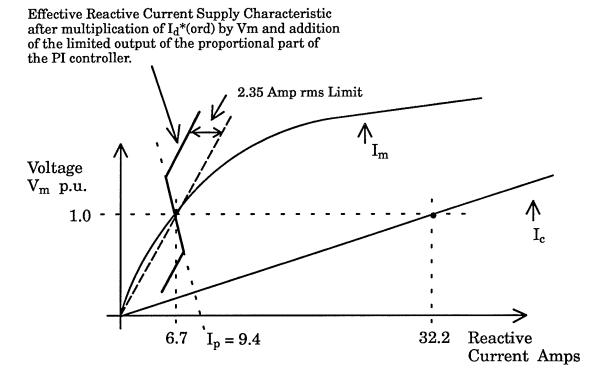

With reference to Figure 6, several quantities are known for the purpose of selecting the self–excitation capacitors. The ac machine voltage  $V_t$  is 1.0 p.u. voltage. The commutation reactance  $X_L$  (defined at 1 p.u. frequency ) is a physical parameter which is known. The frequency f for steady–state operation at minimum speed (i.e. 0.95 p.u. speed ) and maximum power (i.e. 1.0 p.u. power ) was found during the non–linear search procedure described in section 2.3. The delay angle  $\alpha$  should be minimum (e.g.  $\alpha$  = 5  $^{\rm O}$ ). In addition, the product of  $V_d$  and  $I_d$  is 1.0 p.u. power for purposes of selecting capacitance  $C_S$ .

Figure 6 - Controlled Graetz Bridge Rectifier

In the analysis of the Graetz bridge rectifier it is often assumed that the commutation reactance and the bridge are lossless. Based on that assumption, standard approximate equations [15] are available with respect to the circuit in Figure 6. They are as follows:

$$V_d = V_{d0}\cos\alpha - R_c I_d$$

Eqn. 1

$$V_{d0} = \frac{3\sqrt{6}V_t (rms)}{\pi}$$

Eqn. 2

$$R_c = \frac{3 f X_L}{\pi}$$

Eqn. 3

Multiplying both sides of Eqn. 1 by Id gives:

$$V_d I_d = V_{d0} I_d \cos \alpha - R_c I_d^2$$

Eqn. 4

A review of the list of known quantities ( $V_t$ ,  $X_L$ , f,  $\alpha$ , and  $P_d = V_d I_d$ ) described above reveals that the only unknown quantity in Eqn. 4 is  $I_d$ . Thus the dc current  $I_d$  at minimum speed and maximum power can be obtained by solving for  $I_d$  in Eqn. 4. Eqn. 4 is in quadratic form and therefore the solution is

$$I_d = \frac{K_B - \sqrt{K_B^2 - \frac{4P_d}{R_c}}}{2}$$

where  $K_B = \frac{V_{d0} \cos \alpha}{R_c}$  Eqn. 5

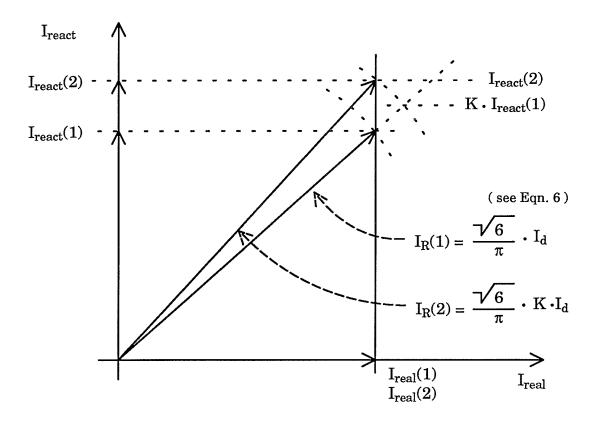

The magnitude of the ac current  $I_R$  into the rectifier for the selection of the self–excitation capacitor can subsequently be found using the following approximate [ 15 ] equation with reference to Figure 6:

$$I_R (rms) = \frac{\sqrt{6} I_d}{\pi}$$

Eqn. 6

The real component of current into the rectifier is given by the equation  $I_{\text{real}} = P_t/(3\,V_t)$ . Finally the reactive power into the rectifier for selecting the capacitors is obtained using

$$I_{react} = \sqrt{I_R^2 - I_{real}^2}$$

Eqn. 7

The reactive current into the machine at minimum speed and maximum power (from section 2.3) can be added to the reactive current into the rectifier to give the total reactive current  $I_C$  that the self–excitation capacitors must provide at minimum speed and maximum load.

The final step in determining capacitance  $C_S$  is accomplished by using  $I_C$  obtained as described above; the p.u. frequency f at minimum speed and maximum power obtained as described in section 2.3; and recalling that  $V_t$  is equal to 1.0 p.u. voltage. The appropriate equation is  $C_S = |I_C|/(2\pi\,f\,V_t)$ .

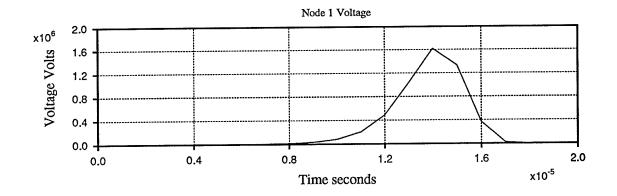

# 2.5 Obtaining Characteristic Curves for Operation of the Apparatus

The complex current into the rectifier is the sum of the complex currents out of the machine and the self–excitation capacitors. Section 2.3 describes a method for obtaining the frequency f and the induction machine current ( real and reactive ) for combinations of speed  $\nu$  and power  $P_t$  at 1.0 p.u. machine voltage. Section 2.4 describes the method for determining the required capacitance  $C_S$  for the self–excitation capacitors. Given f and  $C_S$ , the reactive current  $I_C$  produced by the self–excitation capacitors is thus also readily obtained for the al-

lowable combinations of speed and power at  $V_t$  = 1.0 p.u. voltage. Consequently, the real and reactive currents into the rectifier and the corresponding magnitudes  $I_R$  of the ac current can be obtained for the allowable combinations of speed and power.

The magnitude of ac current  $I_R$  into the rectifier approximately determines  $I_d$  according to Eqn. 6. Rectifier output voltage  $V_d$  for a given power  $P_d$  is then available from  $V_d = P_d \, / \, I_d$ . Families of curves describing required  $I_d$  and  $V_d$  as functions of speed v and power  $P_d$  are presented in Figures 7 and 8 respectively. At a given speed and power both  $I_d$  and  $V_d$  must be at approximately the values indicated in the curves in order to regulate the machine voltage to the proper level and to cause the correct power to be delivered.

The capacitance  $C_S$  and the curves in Figures 7 and 8 are sufficient for the design of the apparatus and control system as described in chapter 4.

Figure 7 - Required Rectifier Operating Current  $I_d*(ord)$

Figure 8 - Required Rectifier Operating Voltage  $V_d$ \*(ord)

## **Chapter Three**

# Transients Simulation Techniques for Power Electronic Apparatus

### 3.1 Outline of the Chapter

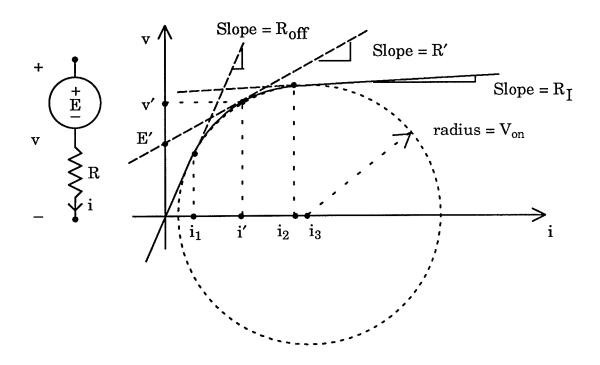

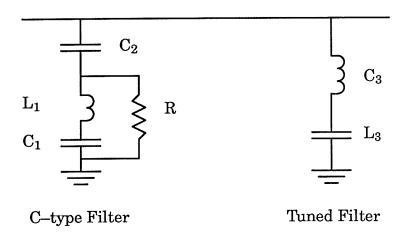

This chapter describes special modifications for adapting a transients simulation program based on the trapezoidal algorithm of Dommel [16]. The modifications facilitate the simulation of systems which include arbitrarily specified configurations of power—electronic switching devices such as diodes, thyristors, and GTO devices.

The modifications are based on three techniques. The three techniques when combined in the simulation program result in shortened preparation time for simulating new power electronic apparatus. In addition, the techniques remove certain difficulties normally encountered in simulating switching events. A technique is described for representing devices according to simple characteristic curves. This approach provides for automatic coordination in the switching of devices which are in close proximity in the simulated circuit. A technique of using two time—step sizes provides benefits which will be described. In addition, a technique is described for modifying the normal trapezoidal algorithm to remove certain numerical oscillations from solutions.

An improved method is briefly described for representing saturation of the main flux path in an induction machine in a transients simulation program. The improvement in representing saturation has also been developed by other investigators [14].

# 3.2 Motivating Factors for Modification of the Transients Simulation Algorithm

It was found necessary, as part of the thesis work, to investigate some new and unusual configurations of power—electronic devices arranged as components in power system apparatus. However, difficulties were encountered in attempting to simulate the new arrangements of power electronic devices using existing techniques. This led to the development of novel modifications to the simulation algorithm particularly suited to facilitating simulation of novel power electronic apparatus.

Traditionally, the trapezoidal algorithm of Dommel [ 16 ] has been used for the simulation of power system transients. A primary feature of the Dommel algorithm is that a computer program can readily be prepared to automatically formulate the admittance matrix used in the solution method. Also of note is the ease with which travelling—wave transmission line models [ 16 ] and machine models can be interfaced to the main network solution [ 17 ]. These features make the Dommel algorithm the method of choice when simulating large electrical power systems.

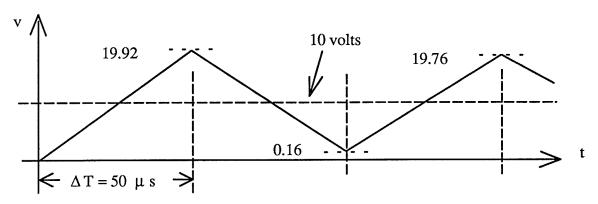

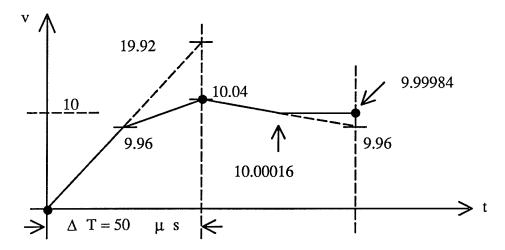

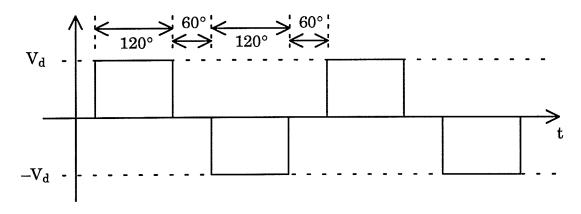

Figure 9. Inductive Nodes and Capacitive Loops

There are of course limitations to any numerical method. One limitation of this type of nodal admittance matrix analysis becomes apparent when the network to be simulated contains capacitive loops or nodes which are connected to the rest of the network only through inductive branches as illustrated in Figure 9. In the case of capacitive loops a numerical oscillation of two time—step period can arise in the solution for currents in the capacitive loop. A similar numerical error can appear in the voltage solution for inductive nodes at which only inductors are incident [18]. The oscillations often arise at discontinuities in the solutions which in turn occur because of device switchings.

One technique available to reduce these numerical oscillations is to make slight changes to the resistive nature of the network in question in order to damp out the oscillations. However, this method of adding small resistances does have an effect on the accuracy of the solution. If fast damping of the numerical oscillations is desired then the damping resistances can have a significant effect on solution accuracy.

Another technique for suppressing numerical oscillations involves making a temporary modification to the solution technique when numerical oscillations arise [ 18 ][ 19 ][ 20 ][ 21 ]. The temporary modification includes using the results of a half—size time—step based on the backward Euler method [ 18 ]. The half—size time—step is taken following a discontinuity in the solution such as can be expected when a switch operates. The time—step length for the backward Euler method is advantageously chosen to be equal to one—half that for the trapezoidal rule because then the same conductance matrix can be used [ 18 ].

A modification to the solution technique is described in this chapter which allows for the continuous use of the trapezoidal rule but which also eliminates numerical oscillations. The trapezoidal algorithm is used exclusively for the de-

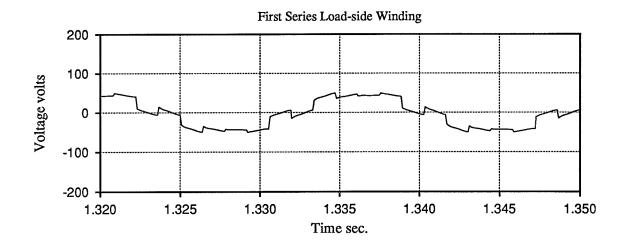

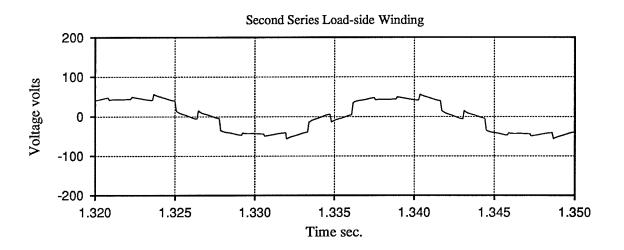

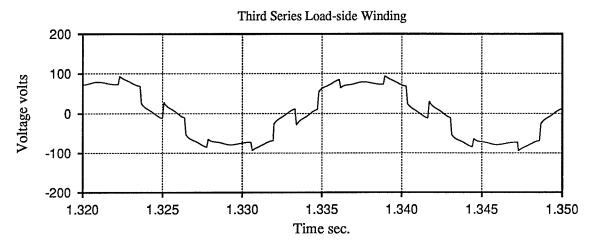

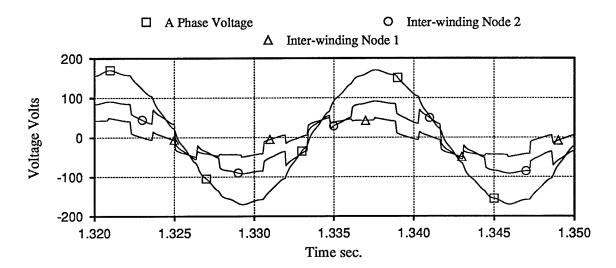

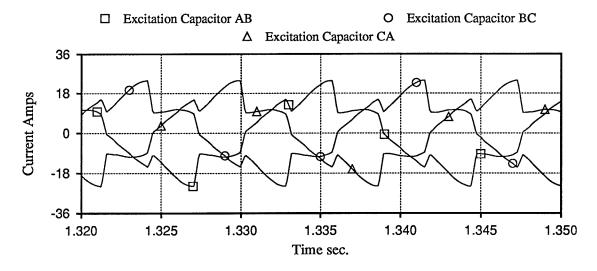

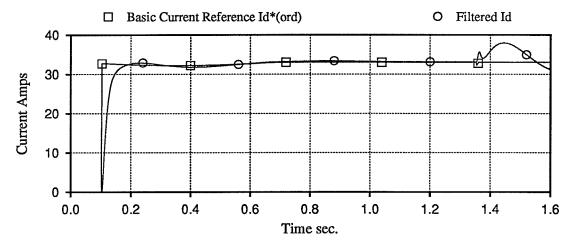

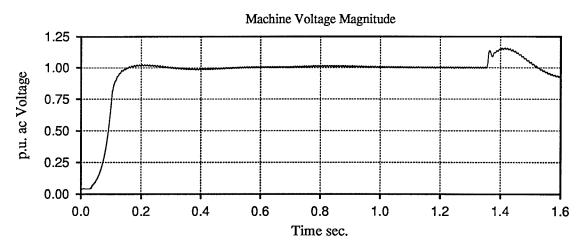

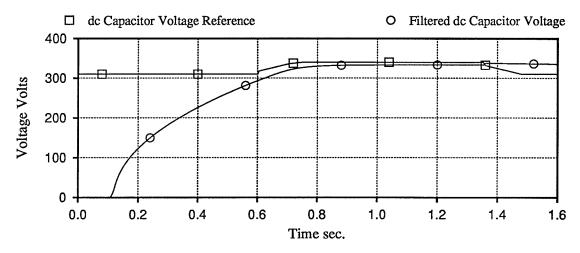

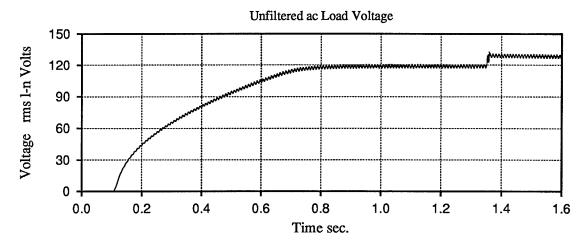

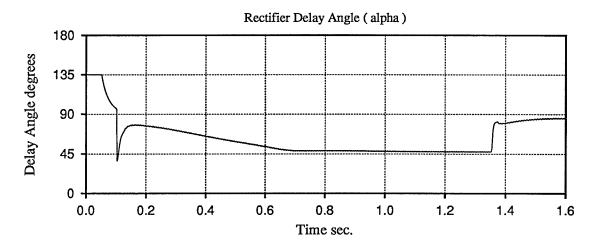

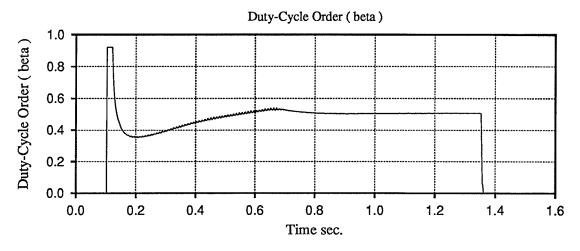

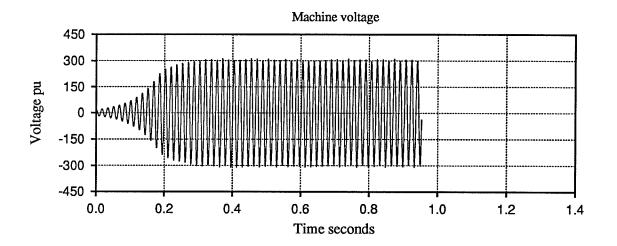

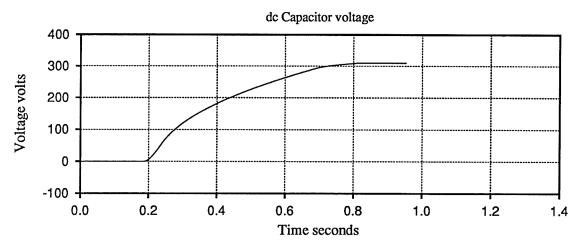

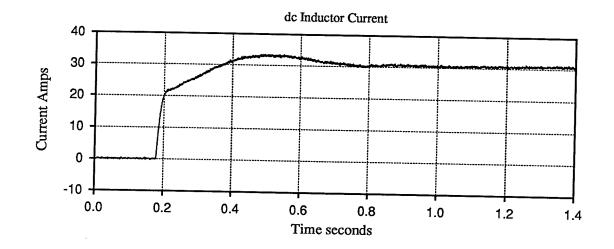

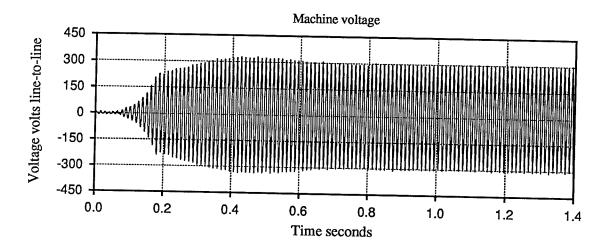

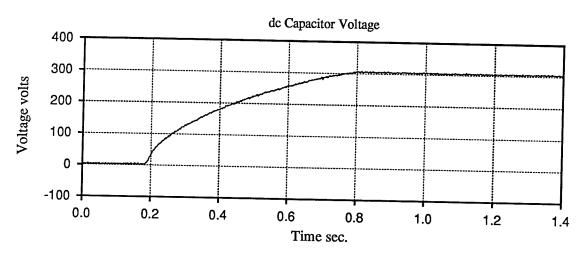

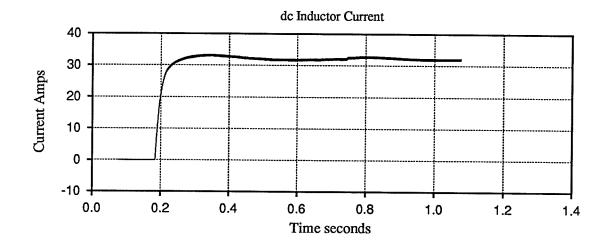

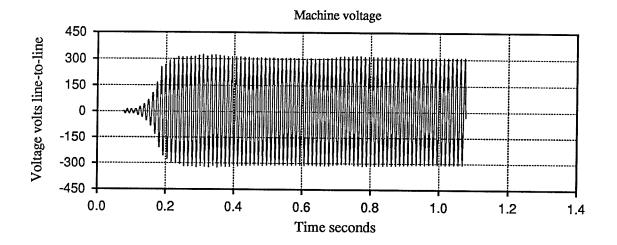

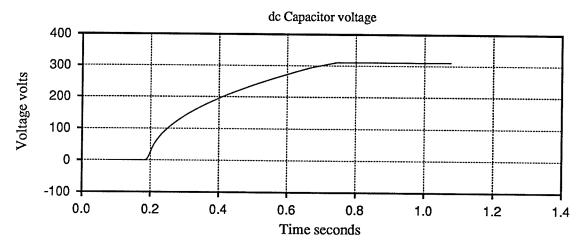

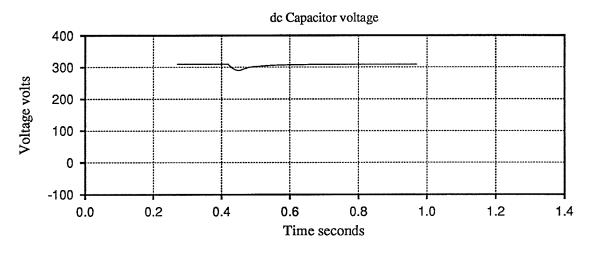

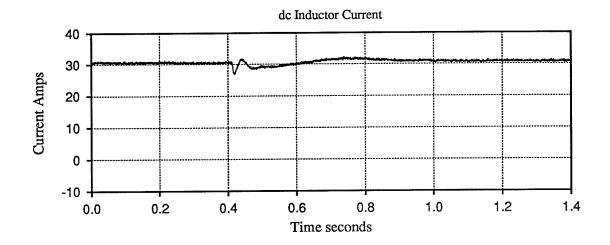

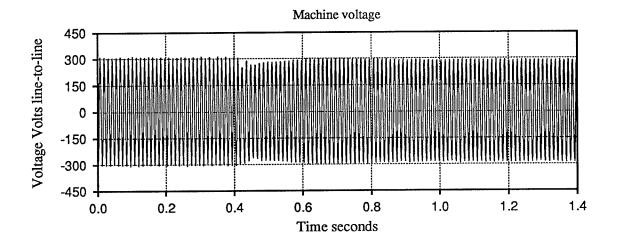

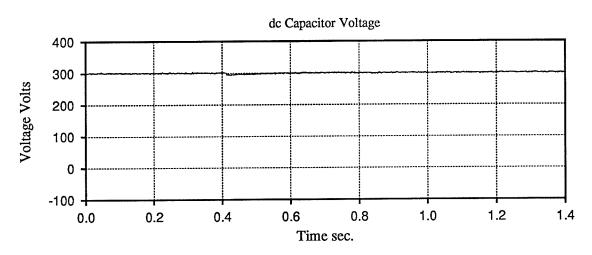

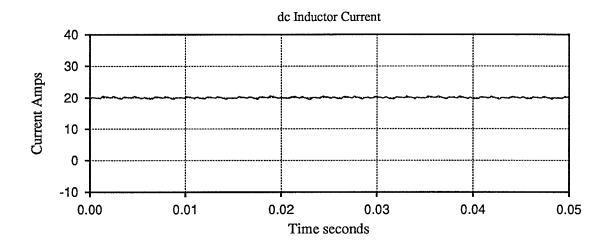

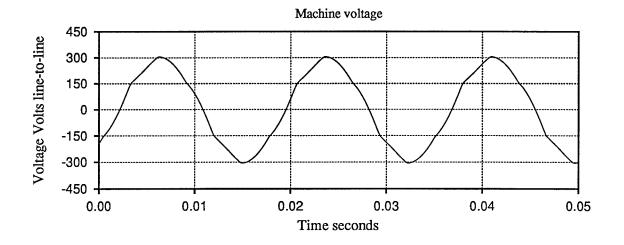

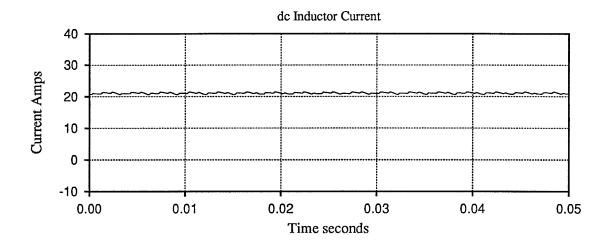

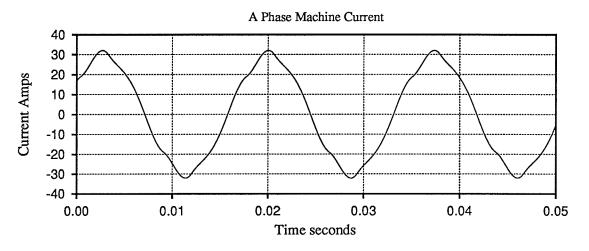

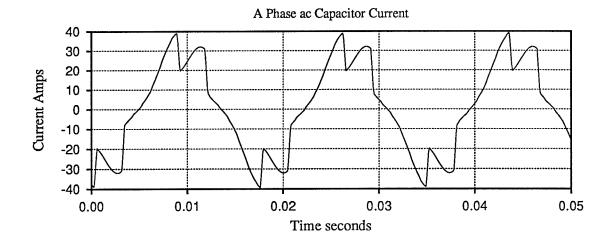

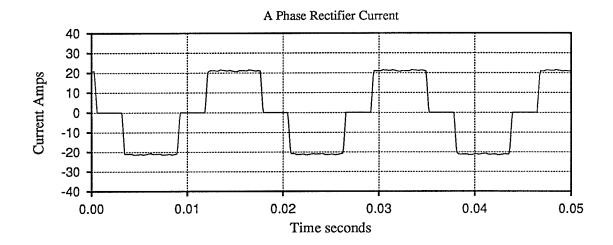

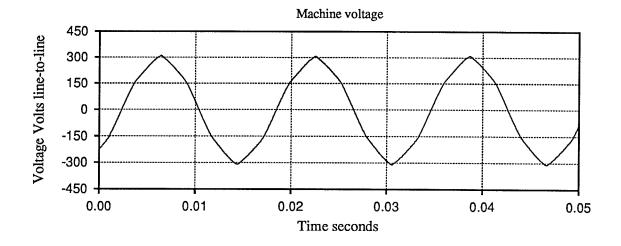

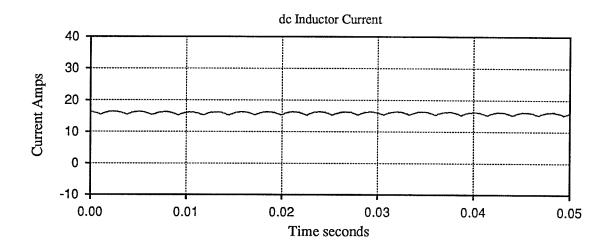

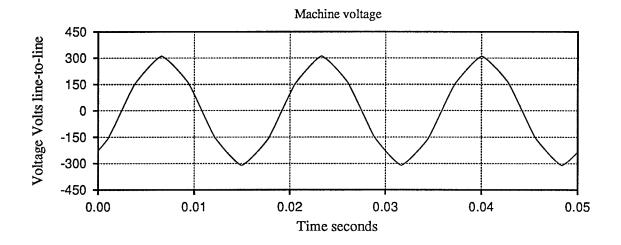

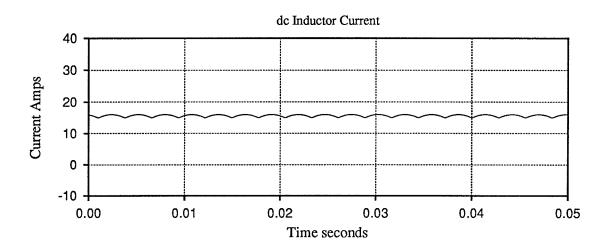

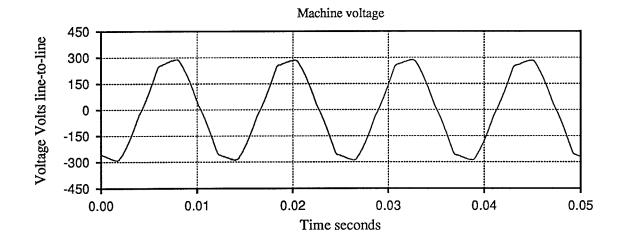

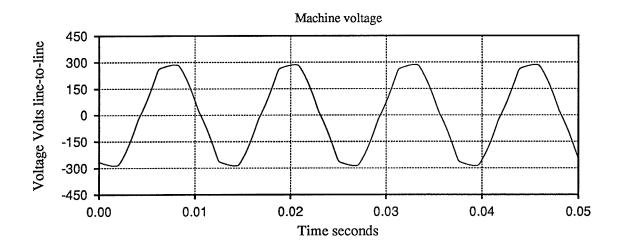

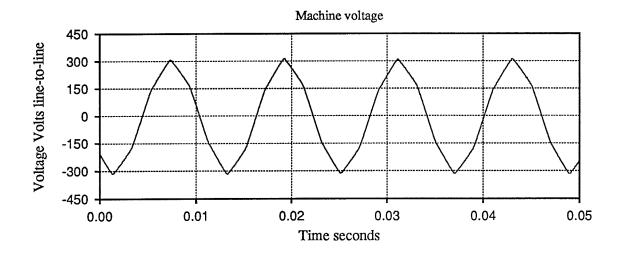

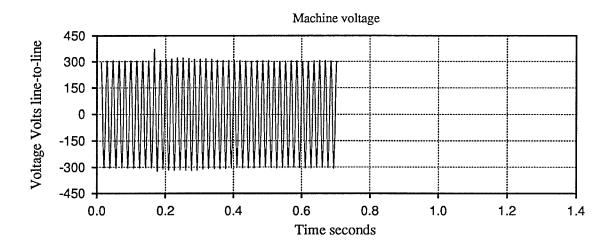

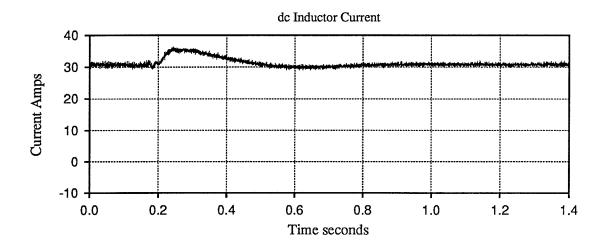

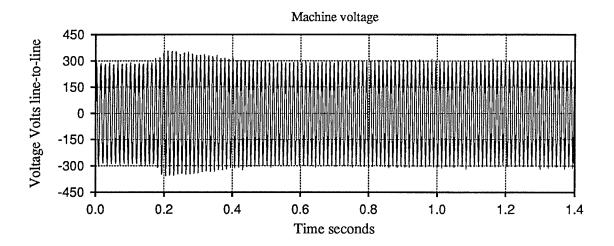

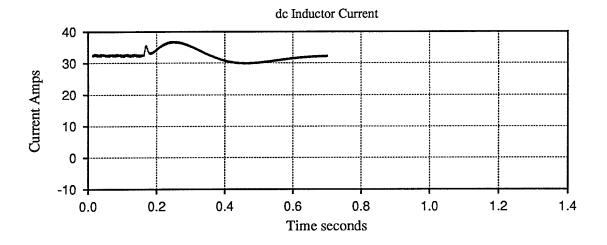

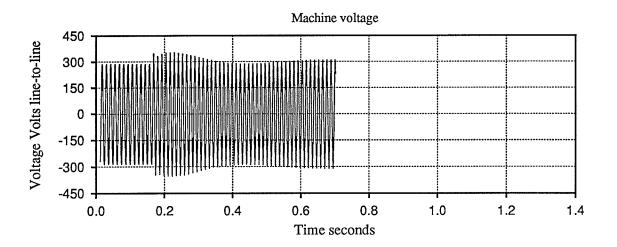

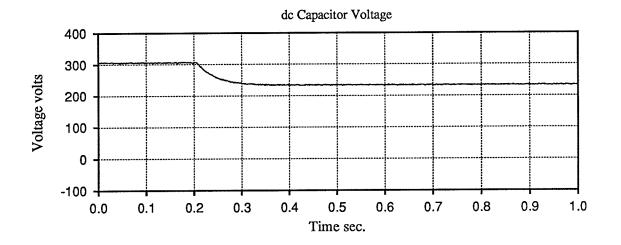

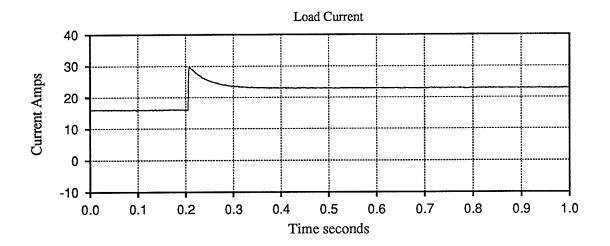

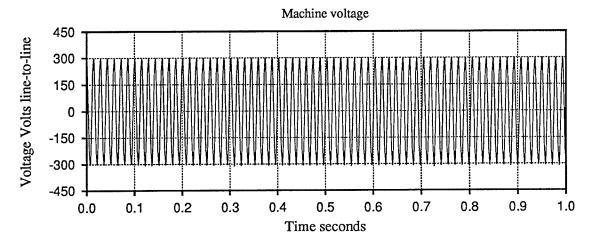

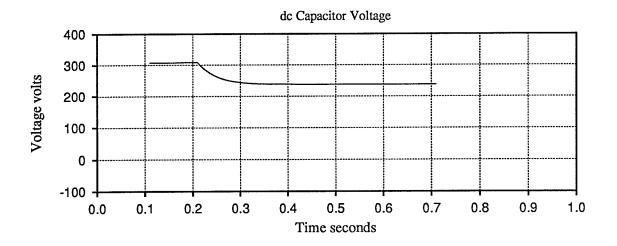

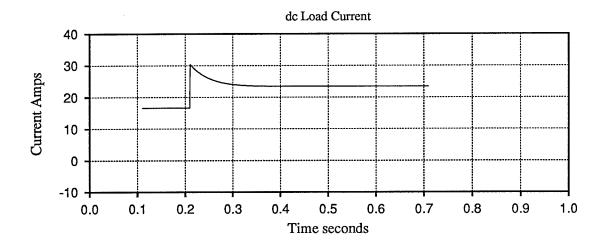

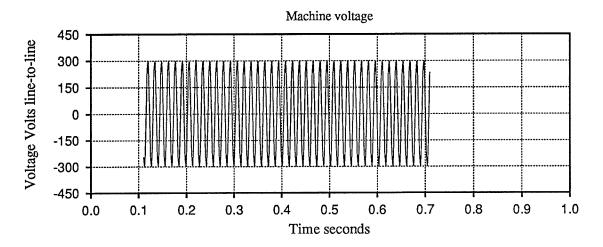

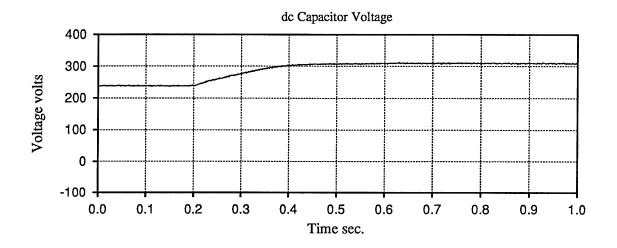

scribed solution technique because it it known to be more accurate than the backward Euler method [ 18 ]. The more accurate trapezoidal algorithm is employed in the described solution technique because the oscillation suppression technique is used in every time—step rather than only at expected discontinuities.