# A Chemical Sensor Design Using a Standard CMOS Process

by

# Kaijian (Jane) Cao

A thesis submitted to the Faculty of Graduate Studies in partial fulfillment of the requirement for the degree of

## **Master of Science**

Department of Electrical and Computer Engineering

University of Manitoba

Winnipeg, Manitoba, Canada

© Kaijian (Jane) Cao, April 2007

# **Abstract**

By integrating an electrochemical deposition process and a silicon chip manufacturing process, a chemical sensor based on a floating gate field-effect transistor was developed. The sensor was fabricated using the standard 0.35µm CMOS process with minimal post-processing. A pH-sensitive organic polymer was electrochemically deposited on the "pseudo" floating gate extension. This "pseudo" floating gate extension was an external area connected to the floating gate of the testing device. By monitoring the change of the current-voltage characteristics during exposure to the gas phase of the chemical aqueous solution, the sensor was shown to be feasible with a reasonable sensitivity.

# Acknowledgements

First of all, I would sincerely thank my advisor Dr. Douglas A. Buchanan for patiently guiding me and spending lots of time to discuss the project with me, for strongly encouraging me to prove my own ideas and for proofreading. Without his support, I would not have gone as far in my research nor would I been able to learn as much during the past three and half years.

This project was in collaboration with Dr. Michael Freund's group in the Chemistry Department of the University of Manitoba. I would sincerely thank Dr. Freund for his valuable advice, Joseph. T. English for the polymer deposition and Dr. Sergei Rudenja for the XPS measurements.

The research work was supported by the Natural Science and Engineering Research Council of Canada (NSERC), the Canadian Foundation for Innovation (CFI), and the Manitoba Innovation Fund.

My thanks should also be extended to Dr. Cyrus Shafai and Dr. Behraad Bahreyni for all of their suggestions and discussions on developing the post-processes, to Dwayne Chrusch and Daryl Hamelin for their assistance in the Nanofabrication Laboratory, and to Guy Jonatschick, Allan Mckay, Allen Symmons and Cory Smit for their technical

support.

I would like to thank all of my friends and colleagues, especially Pommy Patel,

Nishant Dhruve and Kwanyu Lai. Without these fellows, my graduate study would not be

so colorful. ©

Last but not least, I would especially thank my parents, who have strongly supported me for my whole life.

# **Table of Contents**

| ABSTRACT                                          | I        |

|---------------------------------------------------|----------|

| ACKNOWLEDGEMENTS                                  | II       |

| TABLE OF CONTENTS                                 | IV       |

| LIST OF FIGURES                                   | VII      |

| LIST OF TABLES                                    |          |

| LIST OF SYMBOLS                                   |          |

|                                                   |          |

| LIST OF ABBREVIATIONS AND ACRONYMS                |          |

| CHAPTER 1 INTRODUCTION                            | 1        |

| 1.1 MOTIVATION                                    | 1        |

| 1.2 Organization of Thesis                        | 2        |

| CHAPTER 2 INTRODUCTION OF CHEMICAL SENSORS        | 4        |

| 2.1 Chemiresistors                                | 4        |

| 2.1.1 Tin Oxide Chemiresistors                    | 5        |

| 2.1.2 Conducting Polymeric Chemiresistors         | 6        |

| 2.1.3 Non-conducting Polymeric Chemiresistors     | <i>7</i> |

| 2.2 CHEMFETS                                      | 8        |

| 2.2.1 Ion Sensitive Field-Effect Transistors      | 8        |

| 2.2.2 Enzyme Field-Effect Transistors             |          |

| 2.2.3 Work Function Field-Effect Transistors      | 14       |

| 2.2.4 Floating Gate Field-Effect Transistors      |          |

| CHAPTER 3 CHEMICAL SENSOR DESIGN                  | 22       |

| 3.1 FIRST ITERATION OF THE CHEMICAL SENSOR DESIGN | 22       |

| 3.1.1 Sensors with a Floating Gate Extension      | 22       |

| 3.1.2 Reference Transistors                       | 28       |

| 3.1.3 Bonding Pads                                | 29       |

| 3.1.4 The First Chip Layout                       | 32       |

| 3.2 RESULTS FROM THE FIRST CHIP                   | 37       |

| 3.2.1 Gate Leakage Current                        | 37       |

| 3.2.2 Undercutting                                | 39       |

| 3.2.3 Bonding Pads                                                  | 39     |

|---------------------------------------------------------------------|--------|

| 3.3 SECOND ITERATION OF THE CHEMICAL SENSOR DESIGN                  |        |

| 3.3.1 Sensor with the Improved Floating Gate Extension              | 41     |

| 3.3.2 The Second Chip Layout                                        | 44     |

| CHAPTER 4 THE MINIMUM POST-PROCESSING TO EXPO                       | SE THE |

| FLOATING GATE EXTENSION                                             | 47     |

| 4.1 METAL DEPOSITION PROCESS                                        | 50     |

| 4.2 Photolithography Process                                        | 52     |

| 4.2.1 Photoresist Coating                                           | 53     |

| 4.2.1.1 Photoresist                                                 | 53     |

| 4.2.1.2 Spin Coating Process                                        | 53     |

| 4.2.2 Hard Contact Lithography                                      | 61     |

| 4.2.3 Developing                                                    | 62     |

| 4.2.4 Hard Baking                                                   | 62     |

| 4.2.5 Photomask Design                                              | 62     |

| 4.3 WET ETCHING PROCESS                                             | 64     |

| 4.4 PLASMA ETCHING PROCESS                                          | 66     |

| 4.4.1 Why Plasma Etching?                                           | 66     |

| 4.4.2 Plasma Etching Technique                                      | 67     |

| 4.4.3 Trion ICP Plasma Etcher                                       | 68     |

| 4.4.4 Plasma Etching of Dielectrics                                 | 69     |

| 4.4.4.1 Etching the Silicon Nitride Layer                           | 70     |

| 4.4.4.2 Etching the Silicon-Oxy-Nitride Layer                       | 71     |

| 4.4.4.3 Etching the ILD Layer                                       | 71     |

| 4.4.5 Establish the Appropriate Etch Time                           | 79     |

| CHAPTER 5 DEVICE CHARACTERIZATION                                   | 85     |

| 5.1 Theory                                                          | 85     |

| 5.1.1 I-V Characteristics of a Standard MOSFET                      | 85     |

| 5.1.2 I-V Characteristics of Floating-Gate Field-Effect Transistors |        |

| 5.1.3 I-V Characteristics of Sensors                                |        |

| 5.2 I <sub>DS</sub> –V <sub>G</sub> Measurement Set-up              | 95     |

| 5.3 VOLTAGE LIMITS FOR THE I-V MEASUREMENT                          |        |

| 5.4 Typical $I_{DS} - V_G$ Characteristics of Sensors               | 98     |

| 5 4 1 I-V Characteristics of Devices on the First Chin              | 98     |

| REFEI                 | REFERENCES |                                                                                       | 130 |

|-----------------------|------------|---------------------------------------------------------------------------------------|-----|

| CHAPTER 6 CONCLUSIONS |            | 127                                                                                   |     |

| 5.5                   | I - V      | CHARACTERISTICS DURING THE CHEMICAL SENSING                                           | 121 |

|                       | 5.4.2.3    | Effect of the Extension Area                                                          | 116 |

|                       | 5.4.2.2    | Effect of the Gate Width/ Length Ratios                                               | 112 |

|                       | 5.4.2.1    | Typical I-V characteristics of Sensors                                                | 110 |

| 5.4                   | 4.2 I-V C  | Characteristics of Sensors on the Second Chip                                         | 110 |

|                       | 5.4.1.3    | I – V Characteristics of Sensors                                                      | 102 |

|                       | 5.4.1.2    | I – V Characteristics of Floating-Gate Reference Transistors                          | 101 |

|                       | 5.4.1.1    | I <sub>ds</sub> – V <sub>g</sub> Characteristics of Single-Gate Reference Transistors | 99  |

# **List of Figures**

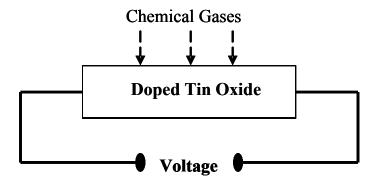

| Figure 2-1:                    | Tin oxide doped with a precious metal                                      | 5     |

|--------------------------------|----------------------------------------------------------------------------|-------|

| Figure 2-2:                    | Configuration of a conducting polymeric chemiresistor                      | 6     |

| Figure 2-3:                    | a) Particles of carbon black are embedded in the non-conducting poly       | mer;  |

| b) after t                     | he chemiresistor is exposed to the chemical gases                          | 7     |

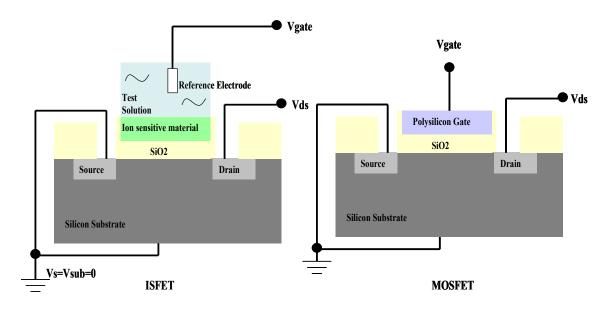

| Figure 2-4:                    | Schematic representation of a) an ISFET and b) a MOSFET                    | 9     |

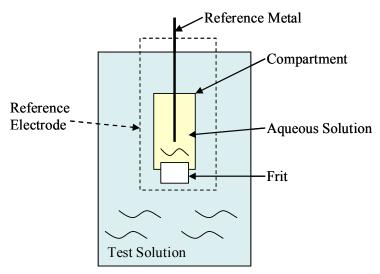

| Figure 2-5:                    | A conventional reference electrode.                                        | 11    |

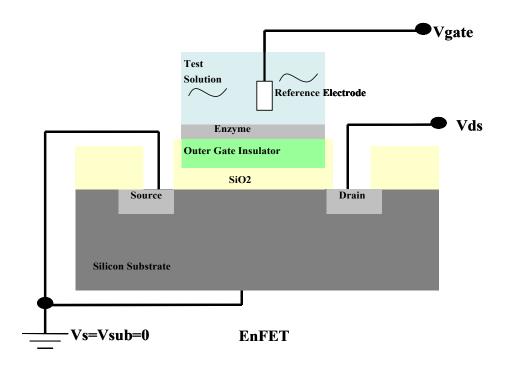

| Figure 2-6:                    | Schematic Diagram of an enzyme field-effect transistor                     | 13    |

| Figure 2-7:                    | Schematic diagram of a work function field-effect transistor (WF-FET)      | ") 15 |

| Figure 2-8:                    | Schematic diagram of a floating gate field-effect transistor               | 17    |

| <b>Figure 2-9:</b> <i>FETs</i> | Energy band diagram of a floating gate structure in the floating           |       |

| Figure 2-10:                   | The chemical sensor built on top of the floating gate field-e              |       |

| 8                              | r structure                                                                |       |

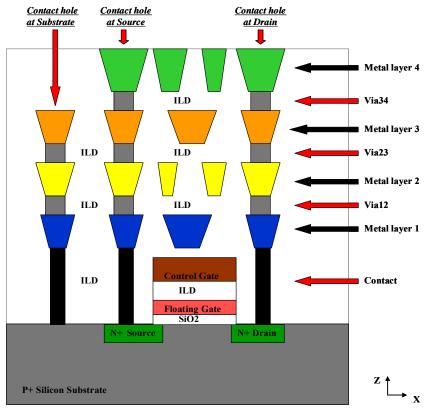

| Figure 3-1:                    | A 3D schematic diagram of an n-type sensor with a floating                 |       |

| extension                      |                                                                            |       |

| Figure 3-2:                    | The difference between the anisotropic etching and isotropic etching       |       |

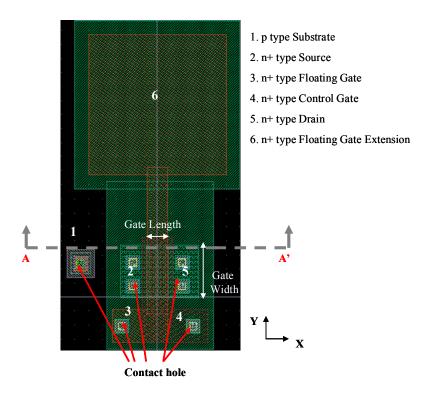

| Figure 3-3:                    | Layout of an n-type sensor with a floating gate extension                  |       |

| Figure 3-4:                    | The cross section (A-A') of the device                                     |       |

| Figure 3-5:                    | Reference Transistors - single-gate field-effect transistor                |       |

| Figure 3-6:                    | Reference Transistors – floating gate field-effect transistor              |       |

| Figure 3-7:                    | Bonding Pad $(80 \times 80  \mu\text{m}^2)$                                |       |

| Figure 3-8:                    | A conducting path generated from the test equipment to the elect           |       |

| region                         |                                                                            | 31    |

| Figure 3-9:                    | Sensor connected with the bonding pads and interconnects                   |       |

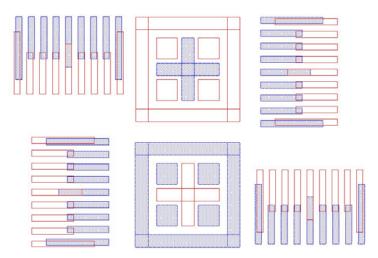

| Figure 3-10:                   | Top layout of the first iteration of sensor system design                  |       |

| Figure 3-11:                   | Alignment Marks                                                            | 34    |

| Figure 3-12:                   | a) Design rule: PO2 cannot pass over the thin oxide layer. b) De           | esign |

| in the ser                     | nsor system: Both polysilicon layers have to put on top of thin oxide laye | er.35 |

| Figure 3-13:                   | a) Design in the sensor; b) Design Rule in 0.35 µm CMOS process.           | 36    |

| Figure 3-14:                   | The clearance between the bonding pads                                     |       |

| Figure 3-15:                   | The gate dielectric and dielectrics used in the sensor                     | 38    |

| Figure 3-16:                   | Setup for electrochemical deposition of the sensitive polymer              |       |

| Figure 3-17:                   | 3-D drawing of the improved sensor structure by using an N-                | -tvne |

| floating g           | gate field-effect transistor                                              | . 41 |

|----------------------|---------------------------------------------------------------------------|------|

| <b>Figure 3-18:</b>  | The layout of an n-type sensor designed in the second iteration           | . 43 |

| Figure 3-19:         | Second iteration of the chip design                                       | . 45 |

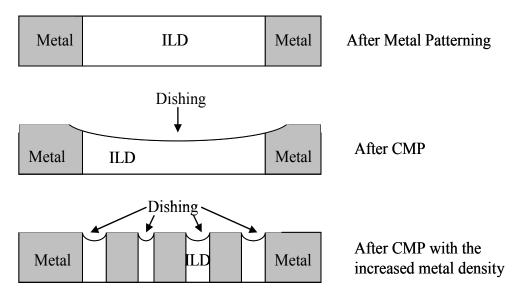

| Figure 3-20:         | The dishing could be reduced by increasing the metal density              | . 46 |

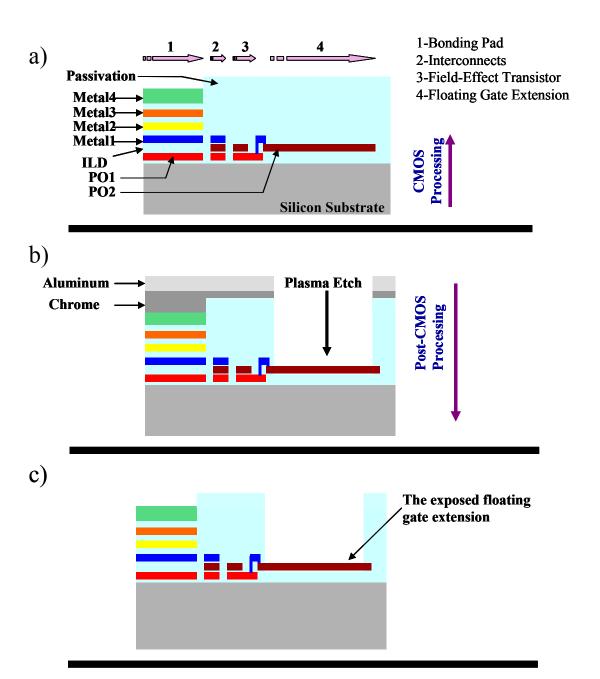

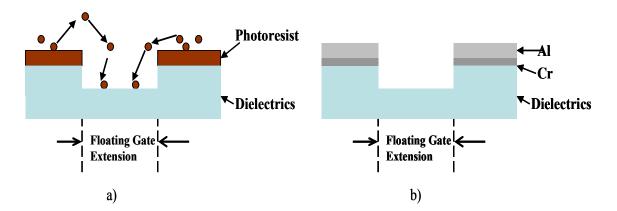

| Figure 4-1:          | Process flow. a) The structure after the CMOS processing; b) use Al m     | etal |

| "hard" i             | mask to etch the dielectrics and expose the floating gate extension,      | ; c) |

| structure            | after metal mask removal                                                  | . 48 |

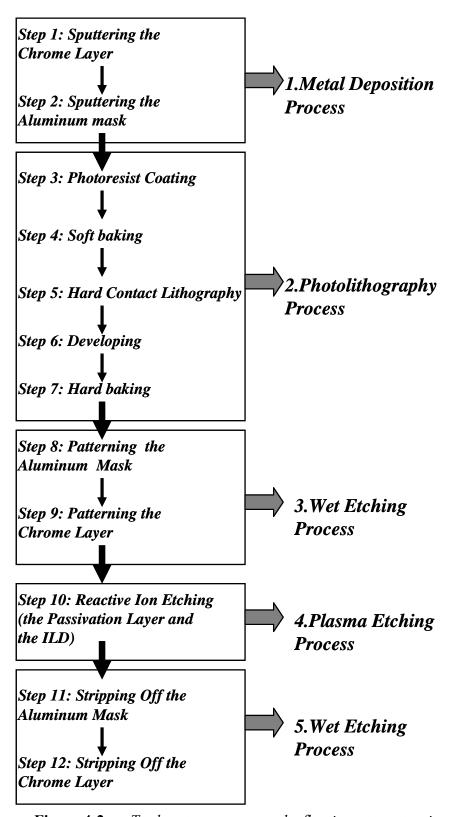

| Figure 4-2:          | Twelve steps to expose the floating gate extensions                       | . 49 |

| Figure 4-3:          | "Soft mask"-photoresist and "hard mask"-metal layers                      | . 50 |

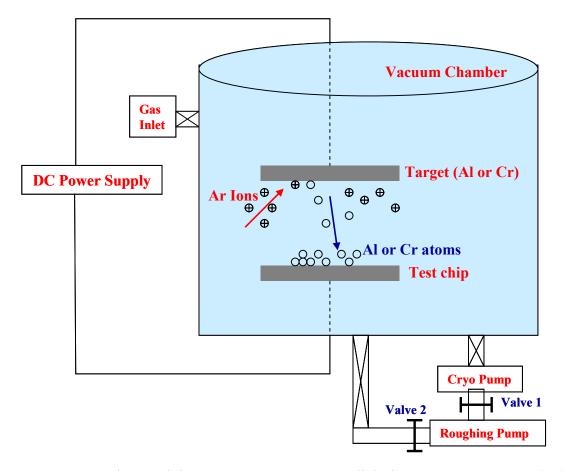

| Figure 4-4:          | The metal deposition process in a parallel-plate sputtering system        | . 51 |

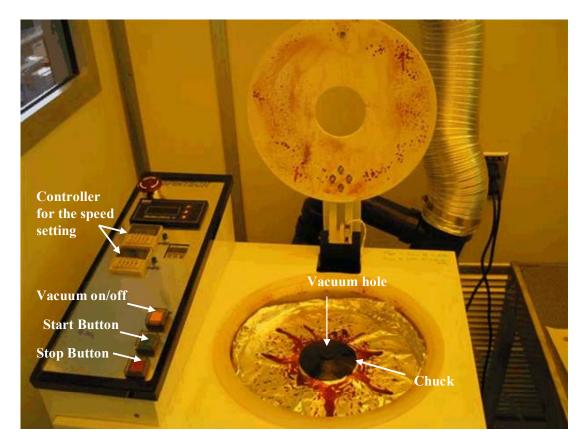

| Figure 4-5:          | Photoresist Spinner.                                                      | . 54 |

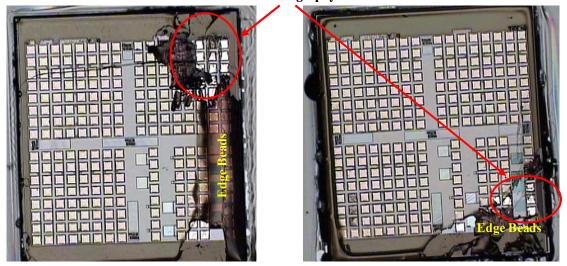

| Figure 4-6:          | Edge beads on the chip.                                                   | . 55 |

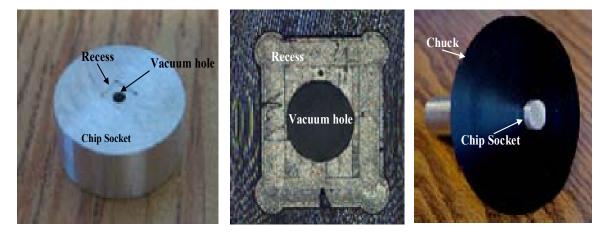

| Figure 4-7:          | a) The chip socket; b) The hole in the center of the chip socket to pass  | the  |

| vacuum;              | c) The chip socket is put on the chuck used in the spin coating process   | . 56 |

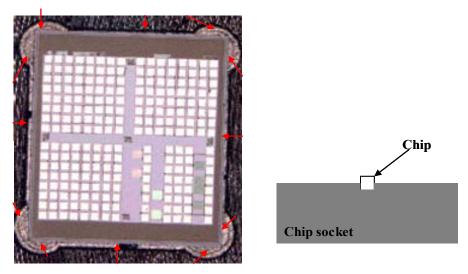

| Figure 4-8:          | Illustration of the chip and the chip socket showing a) the space between | een  |

| the chip             | and the notch edge( red arrows); b) the chip surface residing above       | the  |

| socket               |                                                                           | 57   |

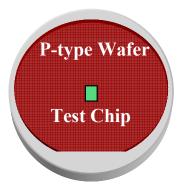

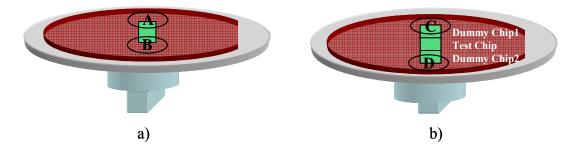

| Figure 4-9:          | Chip position relative to the silicon wafer before the spin coating       | . 58 |

| <b>Figure 4-10</b> : | Two positions that will have edge beads after the spin coating production | cess |

|                      |                                                                           | 59   |

| <b>Figure 4-11</b> : | A test chip coated with a layer of the uniform photoresists               | . 59 |

| <b>Figure 4-12</b> : | The standard procedure for the chip spin coating process (                | 2nd  |

| method)              |                                                                           | . 60 |

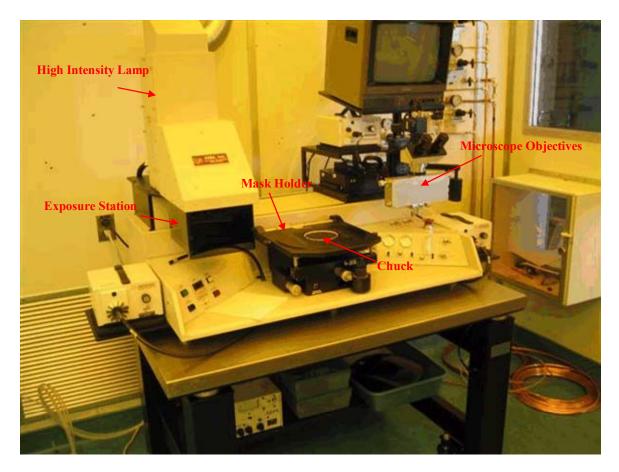

| <b>Figure 4-13</b> : | ABM 6 inch Two-Sided Mask Aligner (a contact mode printer)                | . 61 |

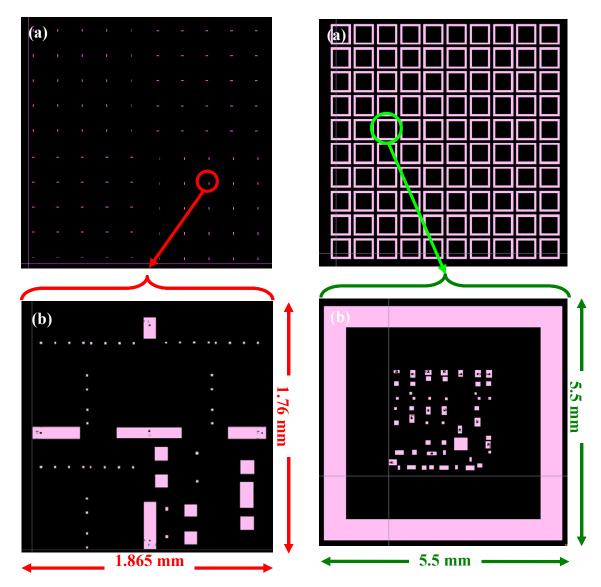

| <b>Figure 4-14</b> : | a) Photomask of the first chip; b) single mask of the first chip          | . 64 |

| <b>Figure 4-15</b> : | a) Photomask of the second chip; b) single mask of the second chip        | . 64 |

| <b>Figure 4-16</b> : | A schematic of a plasma etching system.                                   | . 68 |

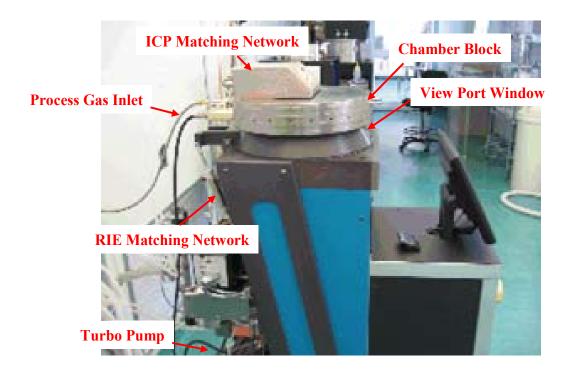

| <b>Figure 4-17</b> : | A photo of the Trion ICP Plasma Etcher.                                   | . 69 |

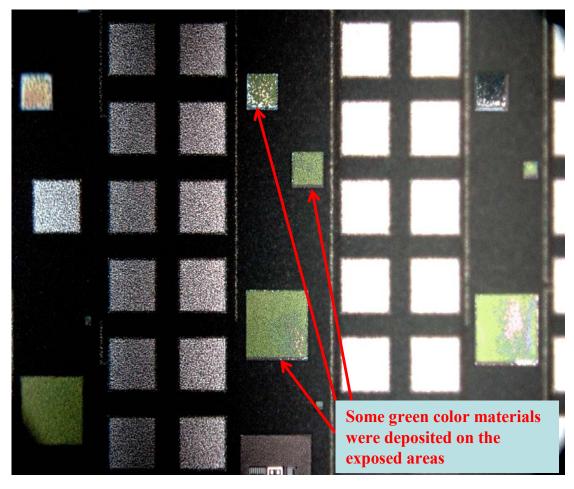

| <b>Figure 4-18</b> : | The green color materials were deposited on the exposed chip areas        | and  |

| blocked t            | the further etching.                                                      | . 76 |

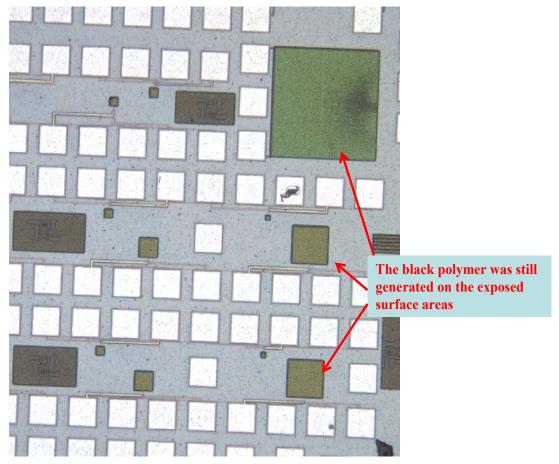

| <b>Figure 4-19</b> : | After RIE, the black polymer was observed on the exposed areas.           | The  |

| floating g           | gate extension was green color due to the thick ILD remained on top of    | the  |

| polysilico           | on                                                                        | . 78 |

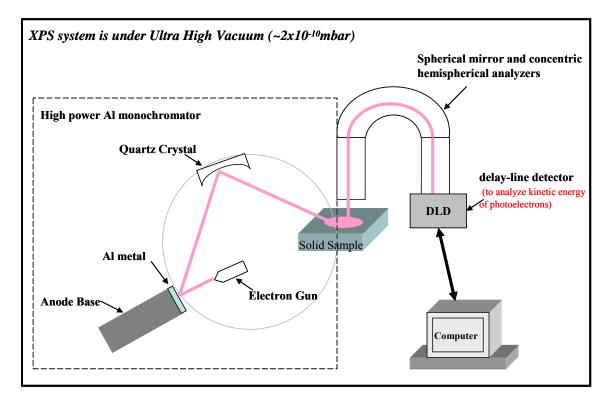

| <b>Figure 4-20</b> : | The operation principle of an x-ray photoelectron spectrosc               | opy  |

| (XPS)                |                                                                           | 80   |

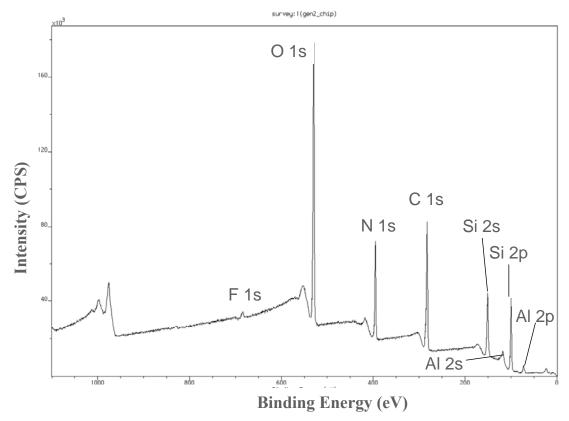

| Figure 4-21          | A spectrum with a series of photoelectron peaks. The spectrum             | was  |

| obtained             | after running a survey scan on the designed chip surface                                                                    |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------|

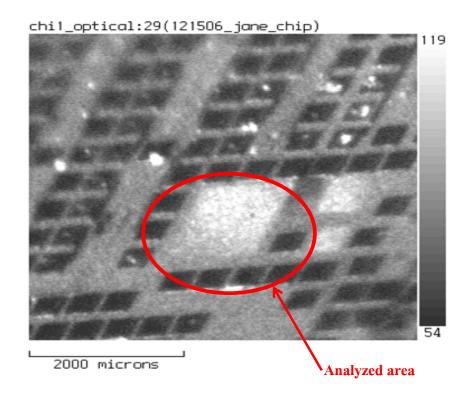

| <b>Figure 4-22</b> : | a) The image of the area to be analyzed by XPS; b) Spectra of silicon                                                       |

| binding e            | nergy before and after the post-processing83                                                                                |

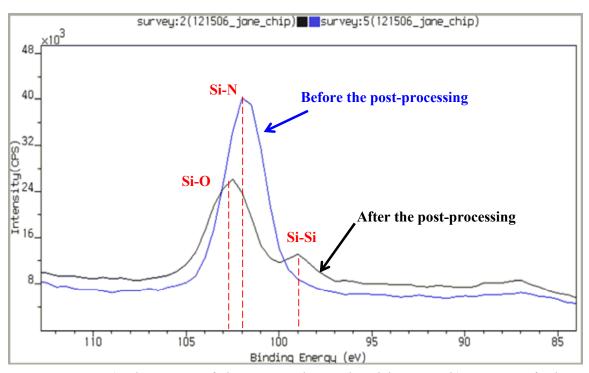

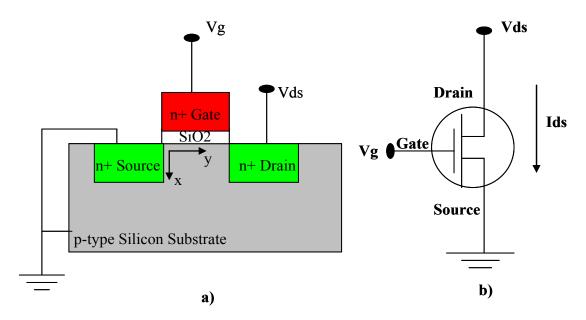

| Figure 5-1:          | The operation mode of an n-type MOSFET                                                                                      |

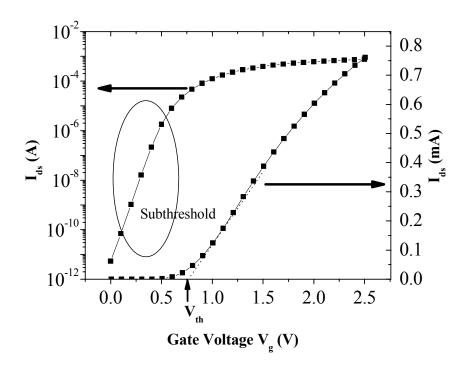

| Figure 5-2:          | The $I_{ds}$ - $V_g$ characteristic of an n-type MOSFET (W=5 $\mu$ m and L=0.8 $\mu$ m)                                     |

| with a sn            | nall drain voltage ( $V_{ds}\!=\!0.5V$ ). The drain/source current is plotted on both                                       |

| LINEAR               | and LOGARITHMIC scales87                                                                                                    |

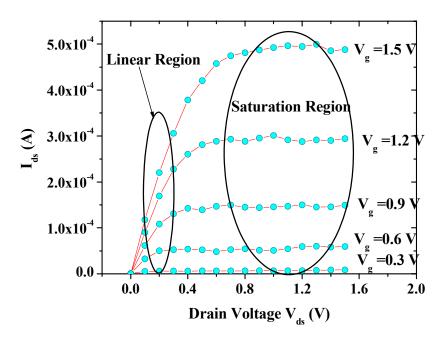

| Figure 5-3:          | The $I_{ds}$ - $V_{ds}$ characteristic of an n-type MOSFET with a variable gate                                             |

| voltage              |                                                                                                                             |

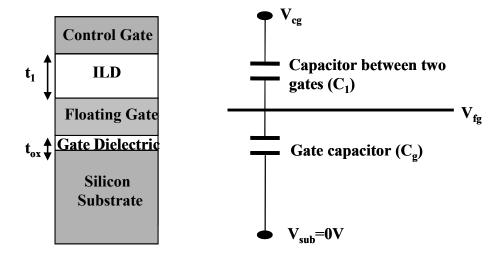

| Figure 5-4:          | Schematic Diagram of the gate stack in a floating-gate field-effect                                                         |

| transisto            | r and the relative capacitor equivalent circuit90                                                                           |

| Figure 5-5:          | Capacitance equivalent circuits of the sensor. 92                                                                           |

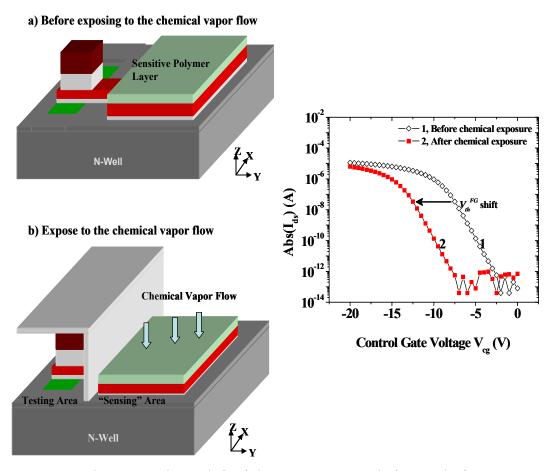

| Figure 5-6:          | The expected I-V shift of the p-type sensors before and after exposure to                                                   |

| the chem             | ical vapor flow94                                                                                                           |

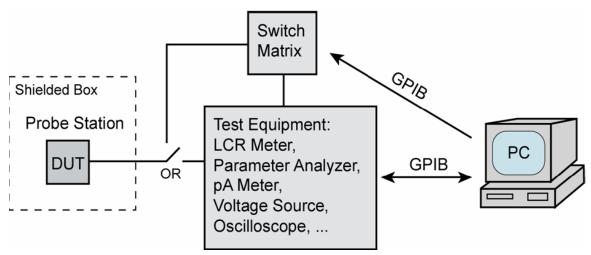

| Figure 5-7:          | Measurement set-up for the device characterization96                                                                        |

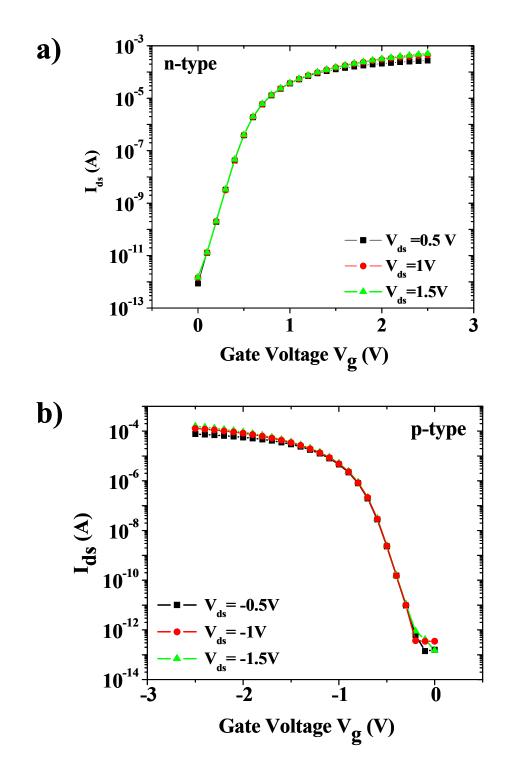

| Figure 5-8:          | Typical $I_{ds}$ - $V_g$ characteristics of single-gate reference transistors with a                                        |

| gate widi            | th to length ratio of $W/L=3$                                                                                               |

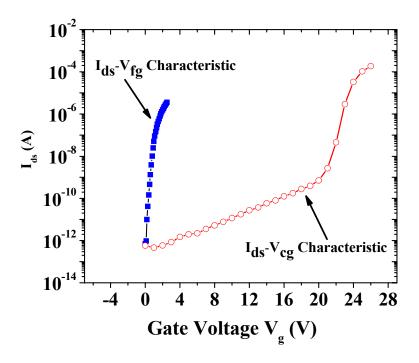

| Figure 5-9:          | I-V Characteristics of an n-type floating-gate reference transistor with a                                                  |

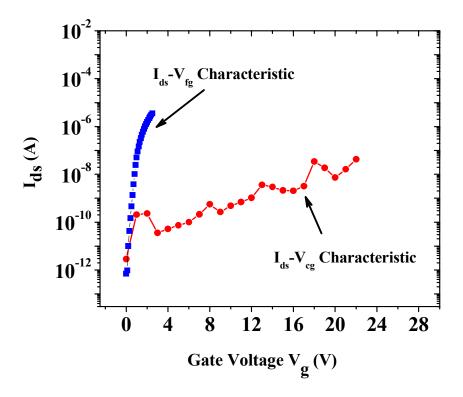

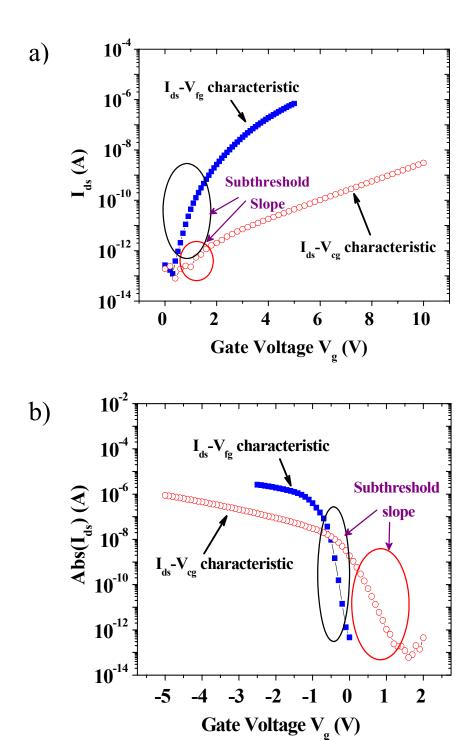

| W/L of 3,            | including the $I_{ds}$ - $V_{fg}$ and $I_{ds}$ - $V_{cg}$ characteristics. $V_s$ = $V_{sub}$ =0; $V_{ds}$ =0.5 $V_{cs}$ 102 |

| <b>Figure 5-10</b> : | Two I-V characteristics of an n-type sensor with a W/L of 3 and a 10um                                                      |

| x 10um e             | xtension area. During the characterization, $V_s = V_{sub} = 0$ ; $V_{ds} = 0.5V$                                           |

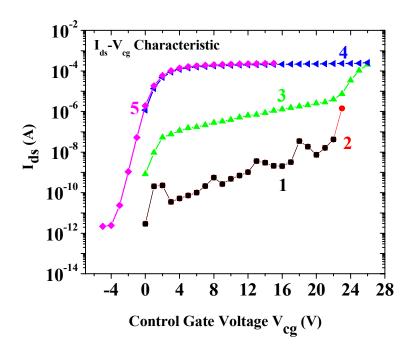

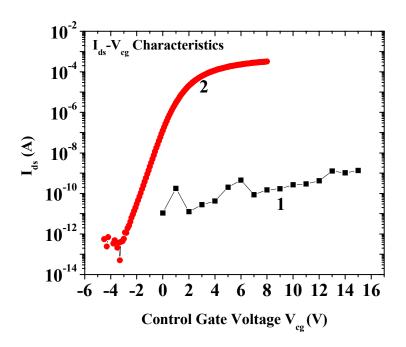

| Figure 5-11:         | The $I_{ds}$ - $V_{cg}$ characteristics of an n-type sensor with a W/L of 3 and a                                           |

| 10×10un              | n extension area                                                                                                            |

| <b>Figure 5-12</b> : | The $I_{ds}$ - $V_{cg}$ characteristics of an n-type sensor with a W/L of 3 and a                                           |

| 10×10un              | n extension area                                                                                                            |

| <b>Figure 5-13</b> : | The $I_{ds}$ - $V_{cg}$ characteristics of an n-type sensor with a W/L of 3 and a                                           |

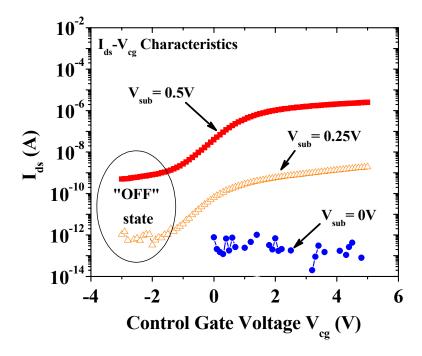

| 10× 10u              | m extension area. The different I-V characteristics were obtained at the                                                    |

| different            | substrate biases. During the measurement, $V_s$ is $0V$ and $V_{ds}$ is $0.5V$ 109                                          |

| <b>Figure 5-14</b> : | Typical I-V characteristics of sensors designed on the second chip.                                                         |

| The cha              | racterized sensor (W=16um, L=0.8um, and the extension area is                                                               |

| 100×100              | um. a) n-type device: $V_s = V_{sub} = 0V$ , $V_{ds} = 1V$ ; b) p-type device: $V_s = V_{n-well}$                           |

| $=0V$ , $V_{ds}$     | = - <i>IV</i>                                                                                                               |

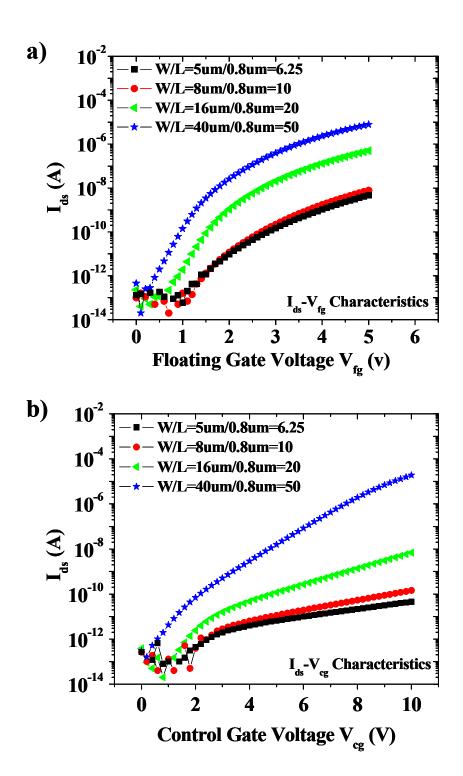

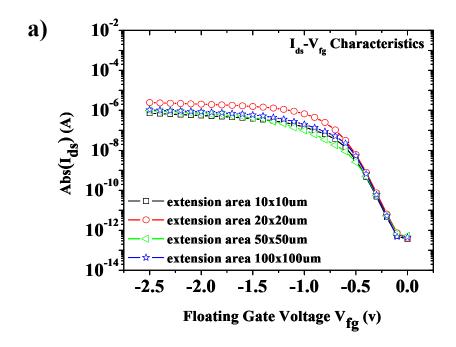

| Figure 5-15:         | The I-V characteristics of four <b>n-type</b> sensors with the same $20 \times 20 \mu m$                                    |

| extension            | area but with a different W/L ratio; a) $I_{ds}$ - $V_{fg}$ characteristics; b) $I_{ds}$ - $V_{cg}$                         |

| characte             | ristics. During the measurement, $V_s = V_{sub} = 0V$ , $V_{ds} = 1V$                                                       |

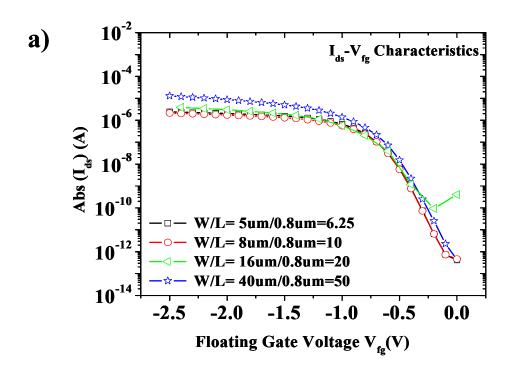

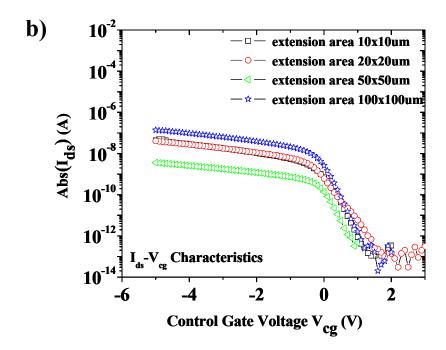

| Figure 5-16:         | The I-V characteristics of four <b>p-type</b> sensors with the same 20 x 20µm                                               |

| extension area but with a different W/L ratio; a) $I_{ds}$ -      | $V_{fg}$ characteristics; b) $I_{ds}$ - $V_{cg}$ |

|-------------------------------------------------------------------|--------------------------------------------------|

| characteristics. During the measurement, $V_s = V_{n-well} = V_s$ | 0V, V <sub>ds</sub> =-1V115                      |

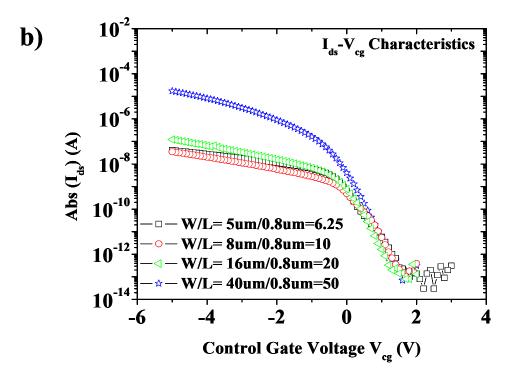

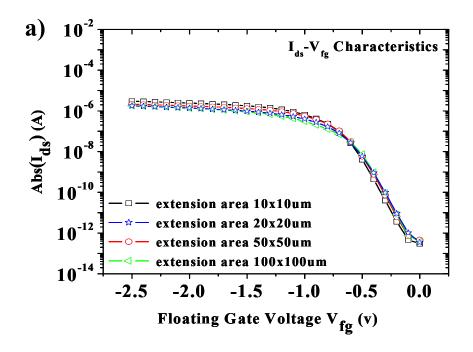

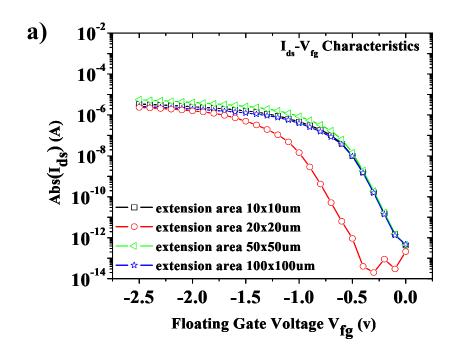

| Figure 5-17: The I-V characteristics of p-type sensor             | rs with the same W/L ratio                       |

| $(W/L=5\mu m/0.8\mu m=6.25)$ , but a different extension area     | <i>t</i> 117                                     |

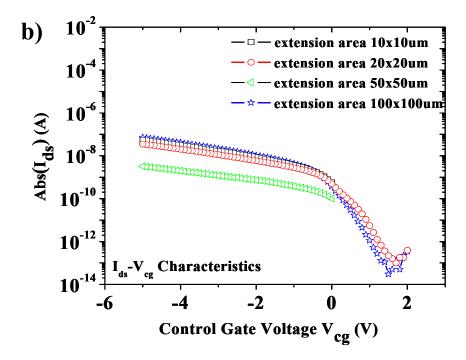

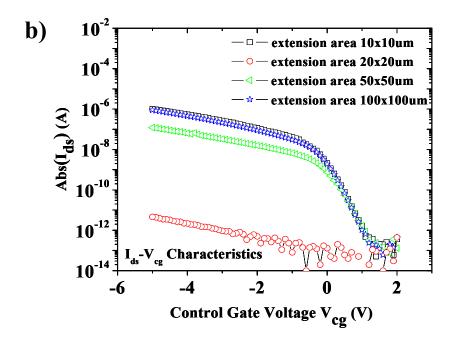

| Figure 5-18: The I-V characteristics of p-type sensor             | rs with the same W/L ratio                       |

| $(W/L=8\mu m/0.8\mu m=10)$ , but a different extension area       | 118                                              |

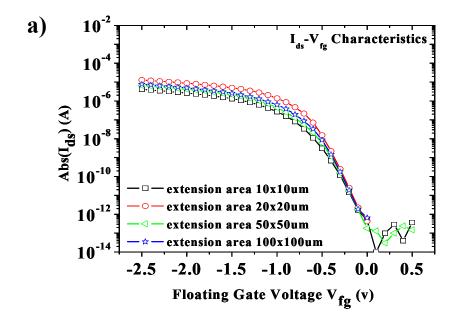

| Figure 5-19: The I-V characteristics of p-type sensor             | rs with the same W/L ratio                       |

| $(W/L=16\mu m/0.8\mu m=20)$ , but a different extension area.     | 119                                              |

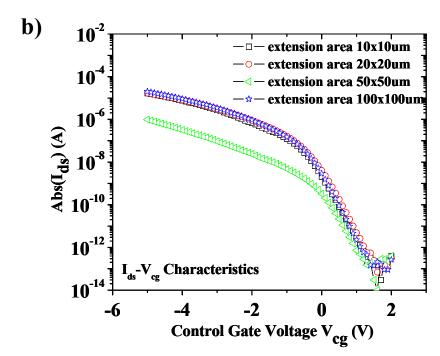

| Figure 5-20: The I-V characteristics of p-type sensor             | rs with the same W/L ratio                       |

| $(W/L=40\mu m/0.8\mu m=50)$ , but a different extension area.     |                                                  |

| Figure 5-21: The set-up of the pseudo floating gate               | extension that was used in                       |

| chemical sensing                                                  |                                                  |

| Figure 5-22: Sites within the polymer chain of po                 | lyaniline that have become                       |

| positively charged upon exposure to some acid ana                 | lyte in the test environment.                    |

| Illustrated are a) sites before the chemical exposure a           | and b) sites after the chemical                  |

| exposure                                                          | 123                                              |

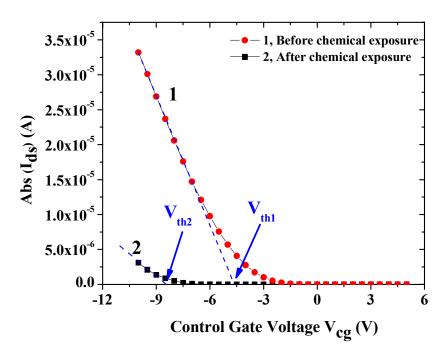

| Figure 5-23: The current-voltage (I-V) characteristics            | of a p-type sensor ( $W=5\mu m$ ,                |

| $L$ =0.8 $\mu$ m) before and after the chemical exposure.         | The obtained drain/source                        |

| current was plotted on the LINEAR scale                           |                                                  |

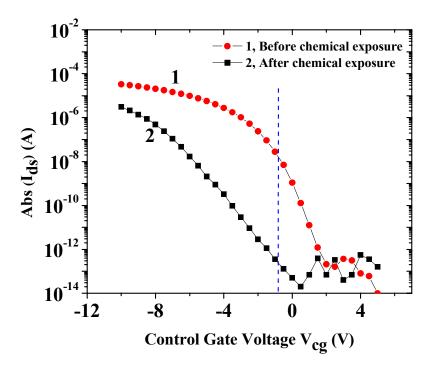

| Figure 5-24: The current-voltage (I-V) characteristics            | of a p-type sensor ( $W=5\mu m$ ,                |

| $L{=}0.8\mu$ m) before and after the chemical exposure.           | . The obtained drain/source                      |

| current was plotted on the LOGARITHMIC scale                      |                                                  |

| Figure 6-1: The potential sensor with the floating gate           | e extension exposed after the                    |

| standard CMOS process. No post-processing is require              | d 129                                            |

# **List of Tables**

| <b>Table 3-1:</b> | Sensor gate lengths and widths                                                  | 24    |

|-------------------|---------------------------------------------------------------------------------|-------|

| <b>Table 3-2:</b> | List of N/P type sensors designed in the second iteration with a float          | ıting |

| Gate ext          | ension                                                                          | 44    |

| <b>Table 4-1:</b> | RIE Recipe for the silicon nitride layer                                        | 70    |

| <b>Table 4-2:</b> | RIE Recipe for the silicon-oxy-nitride layer                                    | 71    |

| <b>Table 4-3:</b> | Recipes with the variable RIE power                                             | 73    |

| <b>Table 4-4:</b> | Recipes with the variable ICP power                                             | 73    |

| <b>Table 4-5:</b> | Recipes with the variable pressure                                              | 74    |

| <b>Table 4-6:</b> | Recipes with the variable $O_2$ concentration in the gas mixture                | 75    |

| <b>Table 4-7:</b> | The first RIE Recipe for ILD that has been tested on the designed chip          | 75    |

| <b>Table 4-8:</b> | Four different RIE recipes for ILD                                              | 77    |

| <b>Table 4-9:</b> | Binding energy of silicon in the different materials                            | 81    |

| <b>Table 5-1:</b> | Data used to calculate the capacitance coupling factor of the sensors           | 98    |

| <b>Table 5-2:</b> | The measurement sequence and test conditions of an n-type sensor                | 104   |

| <b>Table 5-3:</b> | Voltages applied to the terminals in the second method                          | 107   |

| <b>Table 5-4:</b> | List of sensors (L=0.8 $\mu$ m) used to test the effect of the gate width to le | ngth  |

| ratio             |                                                                                 | .113  |

| <b>Table 5-5:</b> | List of p-type sensors used in this experiments                                 | .116  |

| <b>Table 5-6:</b> | The predicted sensitivity of the p-type sensor                                  | 125   |

# **List of Symbols**

| Symbol                   | Description                                             | Unit                             |

|--------------------------|---------------------------------------------------------|----------------------------------|

| α                        | Capacitance coupling factor                             | None                             |

| $\epsilon_{\mathrm{si}}$ | Permittivity of silicon                                 | CV <sup>-1</sup> m <sup>-1</sup> |

| $\epsilon_1$             | Permittivity of ILD                                     | CV <sup>-1</sup> m <sup>-1</sup> |

| $\epsilon_{\rm ox}$      | Permittivity of the gate dielectric (SiO <sub>2</sub> ) | CV <sup>-1</sup> m <sup>-1</sup> |

| ν                        | Optical frequency                                       | Hz                               |

| $\phi_{\mathrm{B}}$      | Difference between Fermi level and intrinsic level      | V                                |

| $\phi_s$                 | Work function of the solid                              | V                                |

| μ                        | Mobility of charge carriers                             | cm <sup>2</sup> /V-s             |

| BE                       | Binding energy                                          | eV                               |

| $C_0$                    | Capacitance per unit area                               | F/cm <sup>2</sup>                |

| $C_1$                    | Capacitance between the two gates                       | F                                |

| $C_{\text{dm}}$          | Maximum depletion-layer capacitance (per unit area)     | F (F/cm <sup>2</sup> )           |

| $C_{g}$                  | Gate capacitance                                        | F                                |

| $C_2$                    | Capacitance between the floating gate and the substrate | F                                |

| $C_p$                    | Capacitance associated with the polymer                 | F/cm <sup>2</sup>                |

| $d_1$                 | Thickness of the I <sub>1</sub> layer          | μm                |

|-----------------------|------------------------------------------------|-------------------|

| $d_2$                 | Thickness of the I <sub>2</sub> layer          | μm                |

| $\Delta{V_{th}}^{FG}$ | Difference of the threshold voltage            | V                 |

| $\Delta Q_{FG}$       | Difference of the net charge                   | C                 |

| E                     | Electric field                                 | V/cm              |

| $E_0$                 | Constants dependent on the electron effect     | None              |

| g                     | Resist thickness                               | nm                |

| h                     | Plank's constant (=6.626×10 <sup>-34</sup> Js) | Js                |

| $I_{ds}$              | Drain/source current                           | A                 |

| $I_{\text{max}}$      | Maximum drain/source current                   | A                 |

| $I_{min}$             | Minimum drain/source current                   | A                 |

| j                     | Current density                                | A/cm <sup>2</sup> |

| KE                    | Kinetic energy                                 | eV                |

| k                     | Constant related to the photoresist process    | None              |

| $N_a$                 | Acceptor impurity density                      | cm <sup>-3</sup>  |

| L                     | Gate length                                    | μm                |

| Q(t)                  | Charge density on the floating gate            | C/cm <sup>2</sup> |

| $Q_{FG}$              | Net charge on the floating gate                | C                 |

| $t_1$                         | ILD thickness between floating gate and control gate | μm |

|-------------------------------|------------------------------------------------------|----|

| $t_{ox}$                      | Thickness of the gate dioxide                        | μm |

| V                             | Voltage                                              | V  |

| $V_{cg}$                      | Potential applied to the control gate                | V  |

| $V_{d}$                       | Potential applied to the drain electrode             | V  |

| $ m V_{fb}$                   | Flat-band voltage                                    | V  |

| $ m V_{fg}$                   | Potential applied to the floating gate               | V  |

| $V_{g}$                       | Potential applied to the gate electrode              | V  |

| $V_{s}$                       | Potential applied to the source                      | V  |

| $V_{\text{sub}}$              | Potential applied to the substrate                   | V  |

| $V_{\text{th}}$               | Threshold voltage                                    | V  |

| ${V_{\text{th}}}^{FG}$        | Threshold voltage of a floating-gate FET             | V  |

| $V_{\text{th}}{}^{\text{SG}}$ | Threshold voltage of a single-gate FET               | V  |

| $W_{min}$                     | Minimum feature size                                 | nm |

| W                             | Gate width                                           | μm |

# **List of Abbreviations and Acronyms**

CHEMFET Chemical field effect transistor

CMP Chemical mechanical polishing

DC Direct current

DLD Delay-line detector

DUT Device under test

FET Field-effect transistor

MOSFET Metal-oxide field-effect transistor

EnFET Enzyme field-effect transistor

ICP Inductively coupled plasma

ILD Inter-layer dielectric

ISFET Ion sensitive field-effect transistor

I-V Current-voltage

GPIB General purpose interface bus (the IEEE 488 standard)

RIE Reactive ion etching

SAW Surface acoustic wave

UV Ultraviolet

WF-FET Work function field-effect transistor

XPS X-ray photoelectron spectroscopy

# **Chapter 1 Introduction**

#### 1.1 Motivation

In traditional food, beverage, cosmetic, and tobacco industries, trained people are used to detect individual smells and/or flavors of various products. Although the human nose is a very good "sensing system", the special training process required is expensive and greatly increases production cost.[1] In the past several decades, researchers have tried to develop less expensive and more accurate chemical sensing systems which can mimic the function of the human nose. These chemical sensing systems are called "electronics noses". In "electronic noses", chemical sensors are used to react with the detected environment and give off electric signals. The electric signals are further analyzed with the application of pattern recognition techniques.

Among the variety of concepts and the different types of chemical sensors proposed in literature, one of the most attractive approaches is to combine the chemical recognition processes with the silicon chip manufacturing.[2] As such, chemical sensors were developed based on field-effect transistors. This type of chemical sensor is attractive because it has many potential advantages, such as the small size, high sensitivity, inexpensive fabrication, and the possible integration into large sensor arrays. Especially,

with the rapid development of semiconductor micro- and nano-technologies, these micro-sensors and "system on a chip" devices have become realizable.[2]

In this thesis, the development of a FET based micro-sensor is described. The sensor was composed of a floating gate field-effect transistor with a large extension area connected to the floating gate. The basic sensor structure was fabricated using a standard CMOS process, while the "sensing" polymer was deposited in post-processing. Using the field-effect transistor's non-linear nature of the sub-threshold current, the sensor was found to be highly sensitive to the chemical reactions processed on the "pseudo" floating gate extension. In the future, this designed sensor will be used to create a sensor array system that will emulate the capabilities of mammalian olfaction.

## 1.2 Organization of Thesis

In Chapter 2, several types of chemical sensors are introduced. In particular, the advantages and disadvantages of the floating-gate field-effect transistor structure are discussed to show why it was used in the new chemical sensors.

Two iterations of the chemical sensors, reference transistors and other structures were developed and their designs are introduced in Chapter 3. Issues found in the post-processing or the device characterizations are discussed. An improved sensor design

in the second iteration is then presented.

In Chapter 4, the post-processing procedures developed to expose the "sensing" area of the device are introduced. Difficulties met in etching and the XPS techniques used to differentiate between two dielectrics are discussed.

The current-voltage characteristics of the different devices are presented in Chapter 5. From the I-V curves before and after the exposure to the gas phase of the chemical aqueous solution, the feasibility of the sensor was demonstrated.

In Chapter 6, the project work is summarized and conclusions are presented.

Improvements to the sensors are described while discussing the future work that can be undertaken.

## **Chapter 2 Introduction of Chemical Sensors**

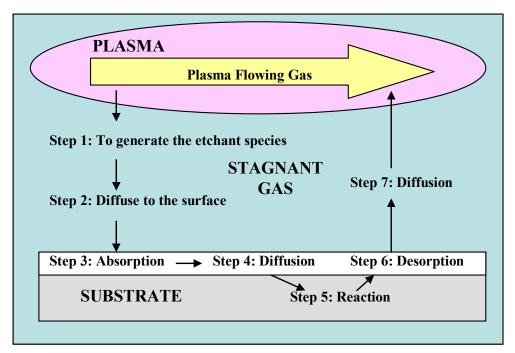

Chemical sensors can detect certain molecules in both chemical solutions and gases. However, the operation mechanism used in various chemical sensors is quite different. For example, with resistive sensors, the chemical gas changes the conductivity of the sensing material while with the chemical transistors (or CHEMFETs), the chemical reaction changes the charge stored on the gate and shifts the threshold voltage of the transistor. With the surface acoustic wave (SAW) chemical sensors, the gas adsorption changes the wave impedance of the device.[3] In quartz-resonator arrays, the mass of molecules adsorbed is utilized in changing the resonance frequency.[3] Although many different types of chemical sensors exist, the discussion in this chapter will be restricted to resistive sensors and CHEMFETs since these devices work in a similar manner by assessing the change of the current in the respective devices.

#### 2.1 Chemiresistors

As its operation depends on the resistance change, resistive sensors that are used for chemical sensing are referred to as chemiresistors.[1] Various materials have been used as the sensing films including metal oxides, conducting and non-conducting polymers.

Specific material application as well as the general operation of chemiresistors will be discussed in this section.

#### 2.1.1 Tin Oxide Chemiresistors

The tin oxide detector (see Figure 2-1) is a type of sensor developed by Figaro Inc. (Japan).[3] It can be used in olfactory sensing system. Its sensing part consists of a thin tin oxide (SnO) film doped with a metal behaving as an n-type semiconductor. When molecules react with the chemisorbed lattice oxygen in the SnO film, electrons are injected from the valence band of the semiconductor to the conduction band, and the electron mobility, through a lowering of intergranular barriers, is increased, which results in the change of the conductivity in semiconductor.[3]

**Figure 2-1:** *Tin oxide doped with a precious metal. [3]*

Tin oxide detectors are a commercial product and are sensitive to several combustible gases with the sensitivities in the range of ~1 part per million (ppm).

Typically, prior to the actual operation, detectors are warmed up to approximately 300~400°C to reduce its response time. However, the sensitivity of the Figaro SnO gas sensors varies with the temperature as well as the doping concentration and the exposure environment.[3] The ultimate sensitivity is also very dependent upon the detailed manufacturing process.

#### 2.1.2 Conducting Polymeric Chemiresistors

Compared to the metal oxide used in the aforementioned chemiresistor, conducting polymers used in conducting polymeric chemiresistors can be more easily deposited electrochemically.[3] The device can operate at the room temperature. A general view of a sensing device of this type is shown in Figure 2-2. The sensor is built on a substrate which is typically a ceramic tile. Two electrodes are formed which are separated by an insulator. The conducting polymer is deposited in the space between these two electrodes.

This item has been removed due to copyright issues. To view it, refer to its source.

**Figure 2-2:** Configuration of a conducting polymeric chemiresistor. [3]

When a small voltage is applied across the electrodes, a current is generated which passes through the conducting polymer. The current varies when the sensor is exposed to different gases due to the change of the polymer resistance. Therefore, this type of sensors can distinguish various chemical gases.

### 2.1.3 Non-conducting Polymeric Chemiresistors

Non-conductive, chemically sensitive polymers can also be used to make chemiresistors. For example, conductive particles of carbon black [4, 5] are embedded into a non-conductive polymer to create a conducting path. When the sensor is exposed to the particular chemical environment, chemicals diffuse into the polymer and cause it to swell. Due to the swelled polymer, the length of conducting paths and therefore the resistance of the sensor increases. This phenomenon is illustrated in Figure 2-3. Since the base value of the resistance can still be recovered by removing the adsorbed chemicals through healing and out-gassing, this type of sensors is reusable.

This item has been removed due to copyright issues. To view it, refer to its source.

**Figure 2-3:** *a)* Particles of carbon black are embedded in the non-conducting polymer; *b)* after the chemicalistor is exposed to the chemical gases. [4]

#### 2.2 CHEMFETS

Chemresistors typically have a sensitivity that is linear: i.e. a change in resistance that is to some degree linearly proportional to a change in chemical concentration. However, the drain/source current of a field-effect transistor (FET) can have a logarithmic relationship with the applied gate voltage in the sub-threshold regime. Therefore, a linear change in the gate bias can produce an exponential change in the drain/source current, which makes this type of device extremely sensitive. If transistors are used for chemical sensing, they are often referred to as CHEMFETs. In this section, three types of CHEMFETs will be introduced: ion sensitive field-effect transistors, enzymatically selective field-effect transistors and work function field-effect transistors.

#### 2.2.1 Ion Sensitive Field-Effect Transistors

An ion sensitive field-effect transistor (ISFET) is an electronic device very similar to a standard metal-oxide-semiconductor field-effect transistor (MOSFET). Schematic diagrams of these two devices are shown in Figure 2-4. Unlike a standard MOSFET, the gate of the ISFET is separated from the device and is formed by a reference electrode inserted in the test solution that is in contact with the gate oxides. By depositing an ion sensitive material on top of the traditional gate oxide (e.g. SiO<sub>2</sub>), an ISFET is formed.

**Figure 2-4:** *Schematic representation of a) an ISFET and b) a MOSFET.*

This material can react with chemicals and change the ion concentration in the test solution. The change in the charge state of the ion sensitive material, due to different ion concentrations, then generates the charge at the oxide/solution interface in the form of protonized (OH<sub>2</sub><sup>+</sup>) or deprotonized (O OH groups [6]. Subsequently a change in the surface potential of the ISFET is observed, leading to a change in the threshold voltage of the ISFET. The threshold voltage, V<sub>th</sub>, is the gate voltage required to turn on an FET. In the linear regime, its relationship with the drain/source current of an ISFET can be expressed using

$$I_{ds} = C_{ox} \mu \frac{W}{L} \left[ \left( V_g - V_{th} \right) V_{ds} - \frac{1}{2} V_{ds}^{2} \right]$$

(2.1)

where  $C_{ox}$  is the gate capacitance per unit area,  $\mu$  is the mobility of charge carriers in the

channel, W and L are the width and length of the gate, respectively,  $V_g$  is the gate voltage, and  $V_{ds}$  is the applied drain voltage. The drain/source current is measurable, and the shift of the threshold voltage can then be calculated using this equation. Since its threshold voltage can be chemically modified via the potential generated at the electrolyte/oxide interface, ISFETs are often used in sensors to measure the ion concentration (or pH) of the test solution. Typically,  $Si_3N_4$ ,  $Al_2O_3$ ,  $SiO_2$  and  $Ta_2O_5$  are used as the gate oxides in ISFETs.

The operation of the ISFET is highly dependent upon the use of a reference electrode as the gate. A conventional reference electrode is made by placing a reference metal (e.g., Ag) in a compartment filled with the aqueous solution (e.g., the saturated KCl) as shown in Figure 2-5. The bottom of the compartment is sealed by a thick frit, which is a porous glass that allows for ions to pass though, but larger molecules and solvent flow more slowly through the frit. When there is no bias applied on the reference metal, a liquid junction exists between the test solution and the aqueous solution. Since no ions can be easily transferred, the content of the aqueous solution remains the constant and a stable reference potential is formed. However, over time, the KCl in the aqueous solution has a tendency to diffuse out of the compartment into the test solution, likewise, ions in the test solution may diffuse into the compartment. If the diffusion in either direction occurs,

ion current will exist and as such can make the reference potential not entirely stable. Therefore, the period over which the reference potential remains constant is defined as the stable lifetime of the reference electrode. The operation range of an ISFET is limited by the stable lifetime.

**Figure 2-5:** A conventional reference electrode.

Since the measurement apparatus for an ISFET is comprised of an ISFET and a reference electrode submersed in the test solution, the application of ISFETs as a sensor can be limited by the size of the reference electrode. Several methods have been tried to solve this issue. One of them is to make the micro-reference electrodes by reducing the size of the compartment. However, due to the lesser amount of aqueous solution that can be filled in the compartment, the contents of the aqueous solution are more quickly changed by diffusion. In other words, the stable lifetime of micro-reference electrodes will

be shortened. The fabrication of a stable micro-reference electrode for ISFETs used in the micro biosensor is still one of the challenges.

Depending on the type of ion sensitive oxides used in an ISFET, some post-processing might be required. For example, Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub> may need to be thermal evaporated or sputtered on the device, [7] while organic polymers may have to be deposited electro-chemically.

#### 2.2.2 Enzyme Field-Effect Transistors

A second type of CHEMFET is the enzyme field-effect transistor (EnFET) whose structure is very similar to an ISFET. However, EnFETs are capable of sensing electrically neutral species due to a layer of enzyme adsorbed on the surface of the ion sensitive oxide (see Figure 2-6). Enzyme molecules catalytically hydrolyze the test solution and change its ion concentration. The ion sensitive oxides (i.e., outer gate insulator and SiO<sub>2</sub>) detect the change and induce a surface charge at the interface. The surface potential and thus the threshold voltage of the device is changed, which in turn changes the drain/source current of the FET.[8] As a consequence, Enzyme FETs translate the change in the ion concentrations of a test solution into the change in the drain/source current of an FET.

**Figure 2-6:** *Schematic Diagram of an enzyme field-effect transistor.*

Two methods can be used to operate an EnFET. Firstly, the EnFET can be set up similarly to a standard ISFET with the same type of reference electrodes. However, as stated previously, due to the difficulties in making micro-reference electrodes, the measurement apparatus of EnFETs is usually large. Therefore, a differential measurement system is often employed. In this method, the operation of the EnFET is controlled by measuring the potential difference between the EnFET and a reference FET, which is identical to the EnFET but insensitive to the ion concentration of the test solution. These EnFETs with a differential measurement system are more applicable for the construction of sensor arrays.

#### 2.2.3 Work Function Field-Effect Transistors

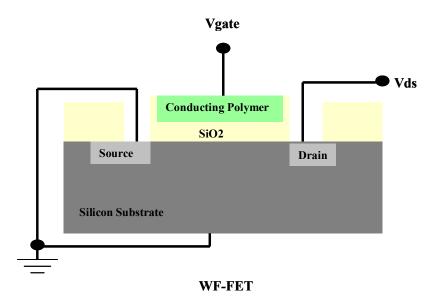

Work function field-effect transistor (WF-FET) is another type of CHEMFET. It can be used to detect electrically neutral species in non-conducting environments such as gases and dielectric liquids.[9] An example of such a WF-FET is shown in Figure 2-7 where a conducting polymer is deposited as the gate electrode. The conducting polymer is stable in air and water. Its conductivity can vary over a certain range depending on its oxidation state and doping level.[8] When this WF-FET is exposed to the particular gaseous analyte, a chemical or electrochemical modification of the conducting polymer occurs.[8, 10, 11] Gas molecules penetrate the polymer up to the interface between the conducting polymer and the gate dielectric, where they are adsorbed and form an electrical dipole with an associated electric field. The work function of the conducting polymer and therefore, the threshold voltage of the WF-FET, are shifted.

The conducting polymer used in a WF-FET is usually deposited by a spinning process. For example, when the conducting polymer polyaniline is used as the gate, it can be dissolved in aqueous formic acid first and then spun onto the gate dielectric. The device is heated to approximately 60°C for 30 minutes to evaporate the formic acid. [8] The remaining polyaniline is then patterned with a photolithography process which will be discussed more in Chapter 4. This operation procedure could be repeatedly used in the

deposition of the different conducting polymers. However, the baking temperatures and time should be adjusted.

**Figure 2-7:** *Schematic diagram of a work function field-effect transistor (WF-FET).*

The biggest advantage of using the WF-FET chemical sensors is that no reference electrodes or reference FETs are required to operate the device. The gate bias can be directly applied to the conducting polymer. The silicon substrate, which is covered by a gate dielectric consisting of silicon dioxide or silicon nitride, can work as a stable internal reference electrode. The chemical reaction induced change in a WF-FET can thus be easily obtained by comparing the gate voltage before and after exposing the device to the chemical analyte. Since the measurement system is very simple, WF-FETs are more suitable for the miniaturization and construction of sensor arrays. [9]

Even though WF-FETs are much simpler to operate than ISFETs and ENFETs, they still have several limitations. Firstly, polymers that have been deposited on the gate and used as the electrode need to be conductive. Secondly, the fabricated WF-FETs can only be scaled down to several microns since the gates are not self-aligned.[13] The gate-to-source and gate-to-drain overlap capacitance can be a serious issue if the gate dimension is very small. Thirdly, only a single conducting polymer can be deposited and patterned on a chip as all of devices on the same chip are heated up at the same time with the same temperature.

#### 2.2.4 Floating Gate Field-Effect Transistors

So far, the introduced chemresistors have been shown to be easy to fabricate but limited in sensitivity. Chemtransistors do have the high sensitivity, however, they cannot be easily fabricated using standard CMOS processes due to the conducting polymers or ion sensitive polymers which are used as the gate making the integration difficult. Due to the desire to be able to integrate the sensors with a standard CMOS process, another form of sensor was thus investigated: the floating-gate field-effect transistor.

The floating-gate field-effect transistor structure was firstly introduced by D. Kahng and S.M. Sze in 1967.[12] As shown in Figure 2-8, two metal layers (M2 and M3)

This item has been removed due to copyright issues. To view it, refer to its source.

**Figure 2-8:** Schematic diagram of a floating gate field-effect transistor.[12]

were used as separate gates and were isolated by a thick insulating layer (I2). The M2 layer was separated from the substrate by a thin insulating layer (I1). During the device operation, a high voltage was applied to the M3 gate with respect to the substrate and a negative voltage was applied on the drain with respect to the source. Since the potential M2 layer was not tied (i.e., floating), it was named as the floating gate. Hence, FETs with this structure were named as floating gate field-effect transistors.

In this floating gate field-effect transistor, charge can be held on the floating gate for a long period of time even after the bias was removed. This phenomenon can be explained using the energy band diagram shown in Figure 2-9.

# This item has been removed due to copyright issues. To view it, refer to its source.

**Figure 2-9:** Energy band diagram of a floating gate structure in the floating gate FETs. a) when a positive bias was applied on the M3 layer; b) when this bias was removed, the stored charge Q causes an inversion of the silicon substrate. [12]

When a positive bias is applied to the M3 layer, electrons can tunnel through the thin I1 layer and accumulate on the floating gate (M2). Since the I2 layer is designed to be much thicker, most of electrons cannot be transported across the I2 layer, but remain on the floating gate surrounded by insulators. This charge storage nature thus enables floating gate FETs to work as a bistable memory with a nondestructive read-out capability.[12]

Currently, floating gate field-effect transistors are one of components that have been widely used in the electronically erasable programmable read only memory (EEPROM) or flash memory industry.

For a given current density j, the charge density stored on the floating gate, Q, is given by [12]

$$Q(t) = \int_0^t jdt \qquad \text{C/cm}^2$$

(2.2)

To the thin I1 layer made of  $SiO_2$ , the charge was transported by the Fowler-Nordheim tunneling.[13] Therefore, the current density j, can be given by

$$j = C_0 E^2 \exp(-E_0 / E)$$

(2.3)

where  $C_0$  and  $E_0$  are constants dependent upon the electron effective mass and interfacial barrier height, and E is the electrical field across the I1 layer.[12] The electrical field (E) is a function of the applied voltage V and Q(t), and is expressed as

$$E = \frac{V}{d_1 + d_2(\varepsilon_1/\varepsilon_2)} - \frac{Q}{\varepsilon_1 + \varepsilon_2(d_1/d_2)}$$

(2.4)

where  $d_1$  and  $d_2$  are the thickness, and  $\varepsilon_1$  and  $\varepsilon_2$  are the permittivity of I1 and I2, respectively.[12] For a given applied gate voltage, the charge stored on the floating gate can be estimated using equations 2.2, 2.3 and 2.4. However, parasitic capacitances were neglected in these equations.

As shown in equation 2.4, if a chemical reaction can change the charge density of

the floating gate, the surface potential of silicon and therefore the threshold voltage will be changed. By comparing the threshold voltages before and after the sensor is exposed to the chemical analytes, the floating gate field-effect transistor can transform chemical reactions into easier measurable electronic signals.

However, a sensitive polymer has to be deposited onto the floating gate to be able to affect the charge storage on the floating gate. With a standard CMOS process, this is not easily possible. Therefore, a "revised" CMOS process was required to fabricate the sensor. As well, the floating gate structure in a device was "revised" to make the integration of sensors easier. As such, the floating gate in the field-effect transistor (FET) was attached with a large extension area as shown in Figure 2-10. The extension area could only be exposed in the post-processing and followed by the deposition of a sensitive polymer. However, with the application of the floating gate extensions, the size of the field-effect transistor in a sensor was greatly scaled down. A smaller sensor should be more sensitive as a larger percentage of the sensor area could be affected by the chemical molecules.

**Figure 2-10:** The chemical sensor built on top of the floating gate field-effect transistor structure.

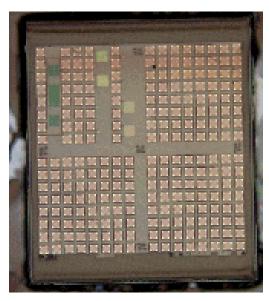

In this project, a commercialized tool (Cadence) was used for the design of the sensor chips. The Cadence system was supplied by Canadian Microelectronics Corporation (CMC) Microsystems. Among various CMOS processes, the 0.35 μm CMOS process supplied by Taiwan Semiconductor Microelectronic Company (TSMC) was selected to fabricate the sensor chips since this is a process providing two polysilicon layers which could be used to form the floating gate and the control gate of the sensor. The sensor chip was designed following a set of material and dimensional restrictions known as "design rules", which are the basic layout guide as defined by TSMC for this 0.35 μm process.

## **Chapter 3 Chemical Sensor Design**

For the first iteration of the chemical sensor development, twenty four different sensors were designed and then grouped on the final chip into devices. However, only one group of sensors exhibited the reasonable operating characteristics. This working sensor structure will be presented and discussed in section 3.1. Due to the design issues found after the initial device characterization, improvements were made to the sensor structure for the second iteration of the chemical sensor development. Forty eight different types of sensors were designed based on the improved structure and integrated into the second chip which will be presented in section 3.3.2.

## 3.1 First Iteration of the Chemical sensor Design

#### 3.1.1 Sensors with a Floating Gate Extension

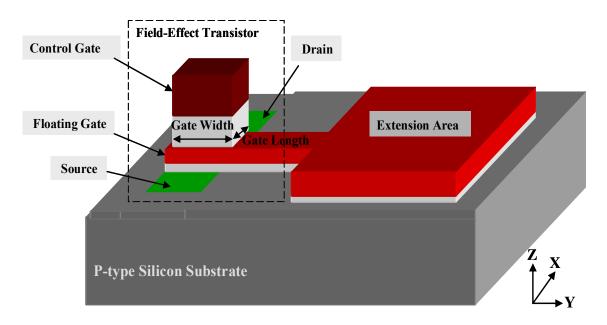

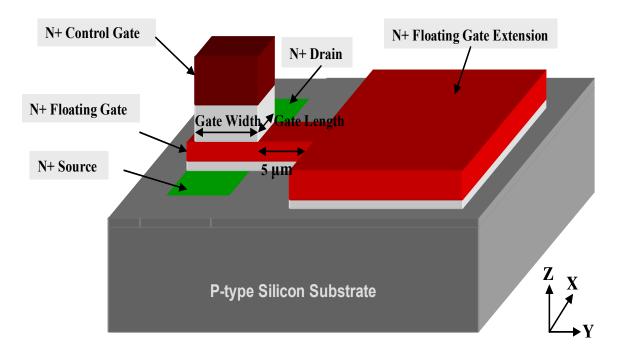

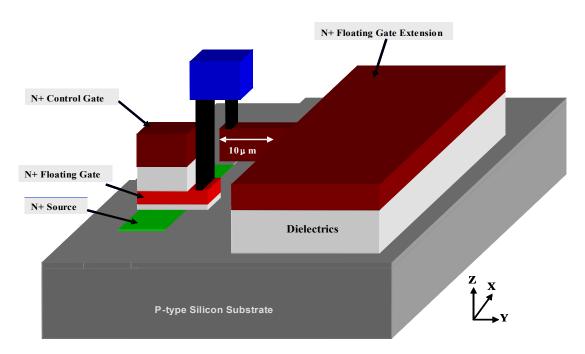

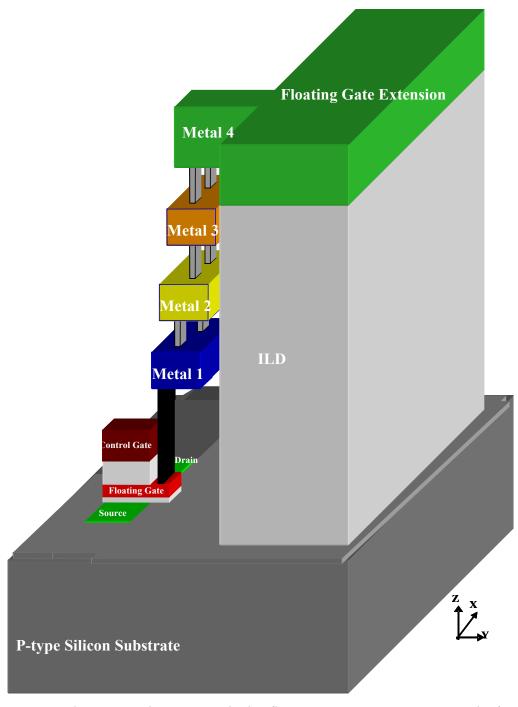

In Figure 3-1, a schematic diagram of a sensor structure is presented. This structure was used for all the sensors of the first iteration. As shown in the figure, the sensor has five different terminals: source, drain, floating gate, control gate and substrate. The floating gate field-effect transistor portion of the sensor is shown on the left side of Figure 3-1. The "sensing" part of the device was achieved by attaching a large extension

area to the floating gate as shown on the right hand side of Figure 3-1. It is on this floating gate extension that a chemically sensitive polymer layer was deposited. This was performed using a selective electrochemical deposition technique, with a bias applied on the floating gate.

**Figure 3-1:** A 3D schematic diagram of an n-type sensor with a floating gate extension.

In this sensor, the floating gate extension was  $10 \times 10$  µm and was placed 5 µm away from the floating gate of the field-effect transistor. It was formed using the same polysilicon layer as the floating gate. However, the gate width and length of the field-effect transistor were varied in the different sensors and are listed below in Table 3-1.

**Table 3-1:** *Sensor gate lengths and widths*

| Gate Width-to-Length | Gate Length | Gate Width |  |  |

|----------------------|-------------|------------|--|--|

| (W/L) Ratio          | (µm)        | (µm)       |  |  |

| 6.25                 | 0.8         | 5          |  |  |

| 3                    | 1.2         | 3.6        |  |  |

| 2.50                 | 1.5         | 3.75       |  |  |

Different gate widths and lengths were used to improve the sensitivity of devices. The sensitivity depends on the operating characteristics of the floating gate field-effect transistor, particularly the drain/source current where a larger current range leads to a more sensitive device. As shown in equation 3.1, the drain/source current ( $I_{ds}$ ) of this transistor can be affected by the mobility of charge carriers, the gate width-to-length ratio (W/L), the applied drain voltage, the oxide capacitance and the potential difference between the gate voltage and the threshold voltage. However, with a standard CMOS process, only the gate width-to-length ratio (W/L) is adjustable in the sensor design. Therefore, the drain/source current was changed by the factor of 1.2 or 2.5 when the W/L ratios were varied from 2.5 to 3 or 6.25.

$$I_{ds} \sim \mu C_{ox} \frac{W}{L} (V_g - V_{th}) V_{ds}$$

(3.1)

The large  $10 \times 10$  µm floating gate extension was also designed to increase the sensitivity of devices. A polymer deposited on the floating gate extension reacts chemically with the gas analyte and induces the change in the charge density on the

floating gate, which in turn shifts the threshold voltage of the field-effect transistor. A larger floating gate extension produces a larger area of reactive polymers, which induces a larger shift of the threshold voltage. Therefore, the extension area was designed to be significantly larger than the gate area of the field-effect transistor.

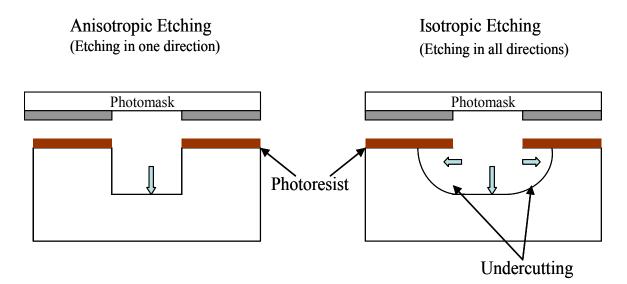

The floating gate extension was separated from the floating gate to allow for post-processing (see Figure 3.1). Since the entire sensor area, including the floating gate extension, was covered by a series of dielectrics, a number of post-processing steps were required to expose the extension area using either wet etching or reactive ion etching techniques. Initially it was assumed that wet etching would be used.

Wet etching is an isotropic etching process and generates an "undercutting" around the exposed floating gate extension as illustrated in Figure 3-2. The undercutting could damage the field-effect transistor if the extension was not at least 5  $\mu$ m away as this was approximately the depth of dielectrics that was to be etched and the etch rates in the vertical and lateral directions were assumed to be the same. This 5  $\mu$ m separation should protect the field-effect transistor structure from being attacked during wet etching.

**Figure 3-2:** *The difference between the anisotropic etching and isotropic etching.*

Although the schematic diagram shown in Figure 3-1 includes all the important sections of the sensor structure, it is not an exact representation of the final design that was manufactured. A plan view of the actual sensor layout that was designed is presented in Figure 3-3. In this design, the contact holes were placed over each electrode region to generate a conducting path from the isolated layer to the top chip surface. The cross-section (A-A') shown in Figure 3-4 reveals the layers that must be etched to access the floating gate extension.

**Figure 3-3:** *Layout of an n-type sensor with a floating gate extension.*

**Figure 3-4:** The cross section (A-A') of the device.

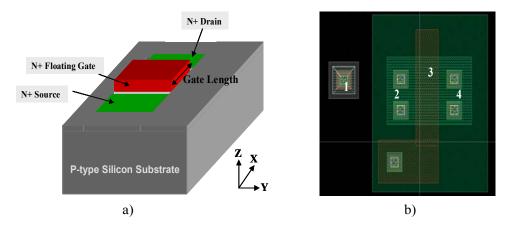

#### 3.1.2 Reference Transistors

Reference transistors are simply standard transistors without the floating gate extension. To extract the basic device parameters, two types of reference transistors were introduced: the single-gate field-effect transistor and the floating-gate field-effect transistor.

Figure 3-5 shows a schematic diagram of a single-gate field-effect transistor and a plan view of the actual layout. The single-gate field-effect transistor was only composed of four terminals: gate, source, drain and substrate. The bottom polysilicon, used for the gate, was on the same layer used for the floating gate extension. Since the design of these terminals or electrode regions was identical for both the single-gate field-effect transistors and the actual sensors, the single-gate field-effect transistors were able to extract the basic device parameters in the FET of each sensor.

**Figure 3-5:** Reference Transistors - single-gate field-effect transistor. a) 3-D schematic diagram and b) layout of an n-type single gate field-effect transistor: 1-Substrate;  $2-N^+$ Source;  $3-N^+$ Gate;  $4-N^+$ Drain.

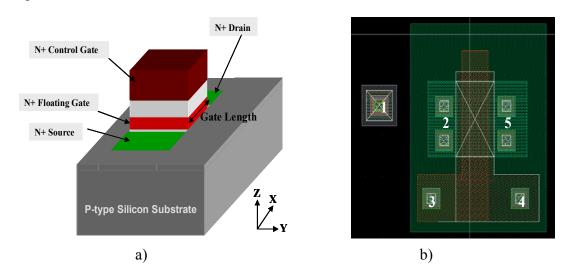

Figure 3-6 a) shows a floating gate field-effect transistor design. This reference transistor was a five terminal device, the same as the designed sensor. However, this device did not have the floating gate extension structure. The operating characteristics of the floating gate field-effect transistor could be compared to the operating characteristics of the sensor. The difference in the current-voltage characteristics would be a result of the floating gate extension. The characterization results of these FETs will be presented in Chapter 5.

**Figure 3-6:** Reference Transistors - floating-gate field-effect transistor. a) 3-D schematic diagram and b) layout of an n-type floating-gate field-effect transistor: 1-Substrate;  $2-N^+$  Source;  $3-N^+$  Floating Gate;  $4-N^+$  Control Gate;  $5-N^+$  Drain.

#### 3.1.3 Bonding Pads

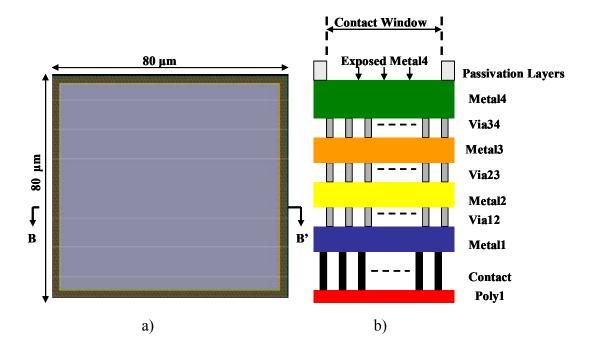

The plan view of the bonding pad layout for the external chip access and its cross-section schematic is shown in Figure 3-7 a) and b), respectively. The  $80 \times 80 \ \mu m$

bonding pads consist of a heavily-doped bottom polysilicon layer and four metal layers.

These five conducting layers are connected by contacts or vias through the different ILDs.

A contact window was defined to open the top metal (Metal4) contacts at the end of the CMOS process.

**Figure 3-7:** Bonding Pad  $(80 \times 80 \ \mu\text{m}^2)$ ; a) The plan view of the bonding pad layout; b) The cross-section(B-B') of the bonding pad.

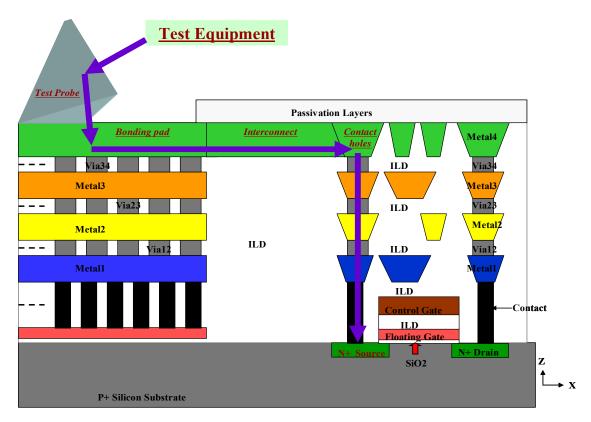

As shown in Figure 3-8, every sensor and reference transistor was covered by a series of passivation layers after the CMOS process. Bonding pads were required when generating the conducting paths from the test equipment supplying the electrical signals to the electrode regions in the sensor.

**Figure 3-8:** A conducting path generated from the test equipment to the electrode region.

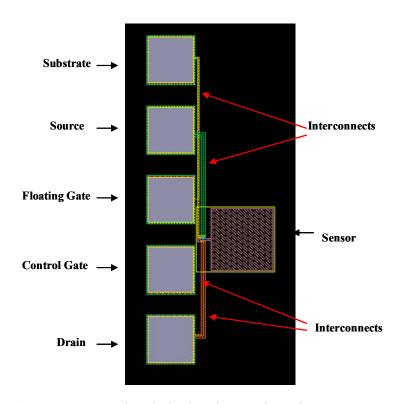

Initially, each bonding pad was connected to one terminal of the device (ie, source, drain or gate etc.). Therefore, five individual bonding pads were required for each sensor (see Figure 3-9). However, due to the limited chip space, the total number of bonding pads that could be placed on the chip was limited to a maximum of 232. Even though the separation between the bonding pads was decreased from 65  $\mu$ m to 25  $\mu$ m, the total number of bonding pads required for all of the devices was still much higher than was possible. Therefore, certain bonding pads were shared between several different devices.

For example, the substrate or n-well of certain devices with the same gate width and length were connected to the same bonding pad. However, when a bonding pad is connected to more than one electrode region, the parasitic capacitance among the different electrode regions can interact and hence affect the threshold voltage of the devices. These parasitic effects were not found to be significant.

**Figure 3-9:** Sensor connected with the bonding pads and interconnects

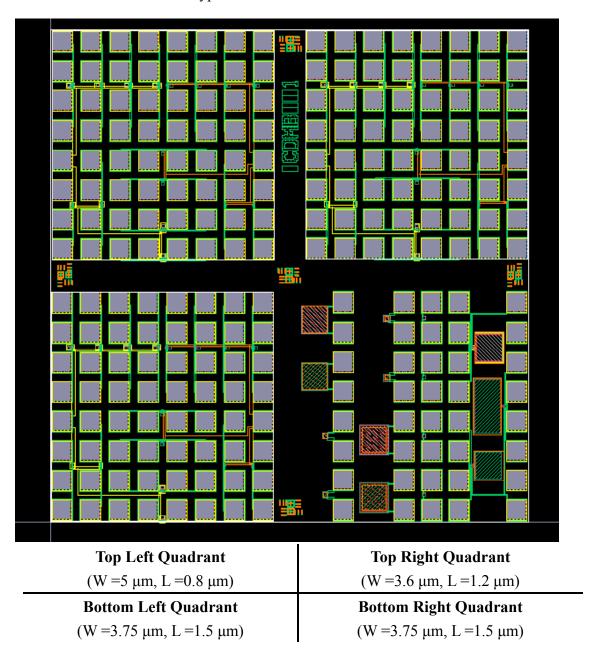

### 3.1.4 The First Chip Layout

The dimension of the first chip was  $1.865 \times 1.76$  mm. A plan view of this chip layout is shown in Figure 3-10. The capacitors and the three multi-finger sensors were

placed on the right bottom quadrant. Other sensors and reference transistors were placed on the remaining three quadrants and were grouped by the gate widths and lengths. Even though the devices introduced in the previous sections were all n-type, some p-type devices were also included for each type of sensor and reference transistor.

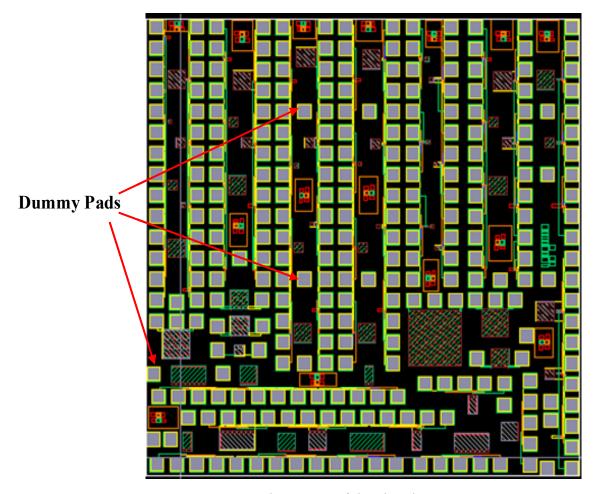

Figure 3-10: Top layout of the first iteration of sensor system design.

The chip design also included the design of alignment marks that were used in post-processing. As mentioned previously, it was required to post-process the chip in order to expose the floating gate extensions. Photolithography, which was one of the post-processes and will be discussed in detail in Chapter 4, was used to transfer the image pattern printed on the photomask to the chip surface. To be able to align the chip with the photomask, alignment marks were required. These marks were a series of crosses and bands and are shown in Figure 3.11. Blue marks were formed by the top metal layer (Metal4) and were placed on the chip. Pink marks were made of chrome and were printed on the photomask. When two sets of alignment marks line up as shown, it represents that the chip is perfectly aligned with the photomask.

Figure 3-11: Alignment Marks.

The floating gate field-effect transistor is a device not generally fabricated with the 0.35 µm standard CMOS process. Therefore, several design rules had to be broken in

order to produce the floating gate structure. These are discussed in some detail below.

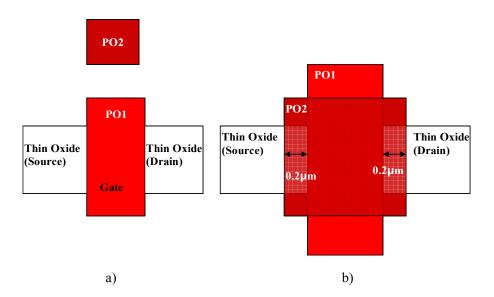

In the 0.35 µm CMOS process, the bottom polysilicon layer (PO1) is usually used to form the gates of MOSFETs, while the top polysilicon layer (PO2) is used to build up resistors or capacitors. Therefore, the PO2 layer is not allowed to pass over the gate dielectric as shown in Figure 3-12 a).[14] However, a floating gate field-effect transistor is a two-gate device. Both polysilicon layers (PO1 and PO2) should be used to form the two gates: the floating gate and the control gate. Since the control gate was directly built up on top of the floating gate, these two polysilicon layers would have to be stacked vertically passing over the gate dielectric. The aforementioned design rule was thus broken. Figure 3-12 b) shows how this was implemented in the current work.

**Figure 3-12:** *a)* Design rule: PO2 cannot pass over the thin oxide layer. *b)* Design in the sensor system: Both polysilicon layers have to put on top of thin oxide layer.

In the sensor design (see Figure 3-13 a)), the length of the control gate was designed to be 0.4  $\mu$ m wider than the length of the floating gate in order to prevent the control gate to be over-etched during the formation of the floating gate. This broke the design rule schematically shown in Figure 3-13 b) which dictates that the minimum extension of the PO1 layer beyond the PO2 layer should be at least 1  $\mu$ m.[14]

**Figure 3-13:** *a) Design in the sensor; b) Design Rule in 0.35 µm CMOS process.*

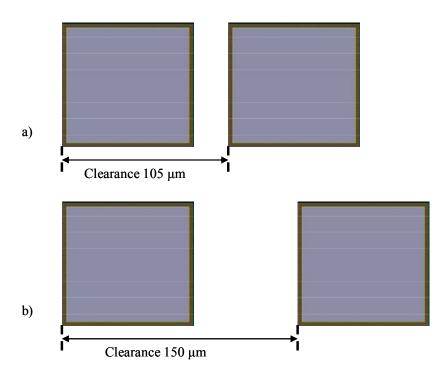

Another design rule that had to be broken related to the spacing of bonding pads. During the chip layout design, the clearance between the bonding pads was set as 105  $\mu$ m to save "real estate" on the chip, which was less than the minimum clearance (150  $\mu$ m) defined by the design rules (Figure 3-14) [14]. However, this clearance was still tolerable to the 0.35  $\mu$ m CMOS process.

**Figure 3-14:** The clearance between the bonding pads. a) The clearance used on the first chip; b) The clearance defined by the design rules.

## 3.2 Results from the First Chip

Sensors designed in the first iteration were characterized and post-processed. In this section, the effects of the gate leakage current, undercutting, and bonding pad dimensions on the performance of the manufactured devices will be addressed.

## 3.2.1 Gate Leakage Current

When characterizing the designed sensors, it was found that devices could only be turned on after some charge was tunneled onto the floating gate. This charge only remained for a short period of time, indicating that there was a leakage current channel in

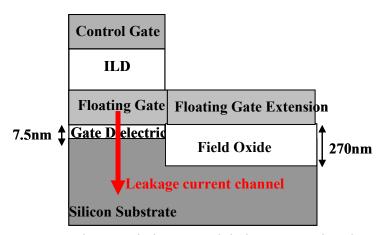

structure was analyzed (see Figure 3-15). In the sensor, the floating gate and the substrate was isolated by a 7.5 nm gate dielectric, while the floating gate extension and the substrate were isolated by a 270 nm field oxide.[14] Due to the large difference in dielectric thickness, the leakage current channel was more possibly formed in the gate dielectric, especially if the gate dielectric was partly damaged by the charge that could have accumulated during some of the plasma based CMOS processes. This plasma processes induced gate dielectric damage will be illustrated more in Section 3.3.1.

**Figure 3-15:** *The gate dielectric and dielectrics used in the sensor.*

This large gate leakage current highlighted two issues. First, the leakage current degraded the gate dielectric leading to a poor performance of the field-effect transistor.

This will be discussed more in Chapter 5. Second, the gate leakage current would affect the charge stored on the floating gate. It thus would be difficult to determine the effect

induced by the chemical reaction on the floating gate extension.

For these two reasons, the gate leakage current had to be reduced. One simple method is to temporarily isolate the floating gate extension from the field-effect transistor structure by using a metal jumper as was introduced in the second design.

#### 3.2.2 Undercutting

Even though the floating gate extension was placed 5  $\mu$ m away from the field-effect transistor to prevent the transistor from being damaged by the undercutting generated during wet etching, this distance was found to be inadequate. After a series of post-processing experiments, the transistor structures were found to be attacked or sometimes completely destroyed by the undercutting. In the second iteration (Section 3.3), the minimum separation between the floating gate extension and the FET was increased to at least 10  $\mu$ m.

#### 3.2.3 Bonding Pads

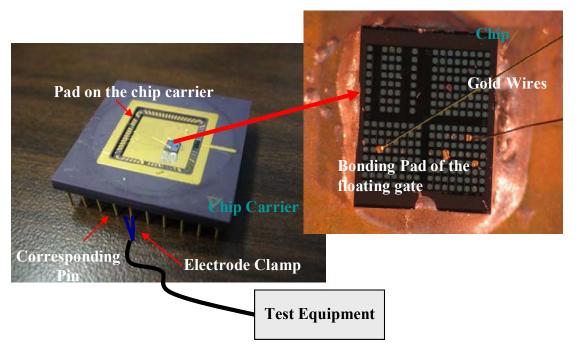

Bonding pads were used both for device characterization and for electrochemical deposition of the polymer. During the electrochemical deposition, a chip carrier (Figure 3-16) was used onto which the chip was bonded with the conducting silver epoxy. The bonding pads of the floating gates were wire bonded to the selected pads on the chip carrier and the test equipment was connected to the corresponding pin at the backside of the chip

carrier. The gold wires used in the wire bonding process were 25.4 µm in diameter. The bonds formed using these wires were found to be bigger than the designed bonding pads. In some cases, they were able to short the neighboring bonding pads on the chip. This issue was solved by increasing the space between adjacent bonding pads as well as by increasing the dimension of the bonding pads in the second design.

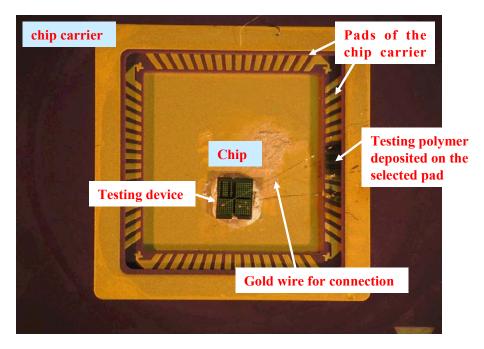

**Figure 3-16:** *Setup for electrochemical deposition of the sensitive polymer.*

## 3.3 Second Iteration of the Chemical Sensor Design

A second iteration of the sensor design was implemented to resolve the aforementioned issues that arose from the first chip (Section 3.2). Once again, sensors were fabricated using the same  $0.35~\mu m$  CMOS process.

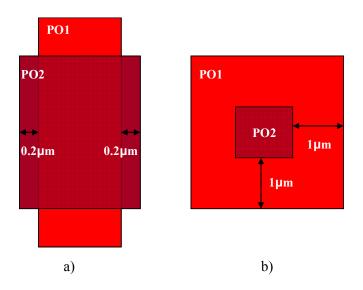

#### 3.3.1 Sensor with the Improved Floating Gate Extension

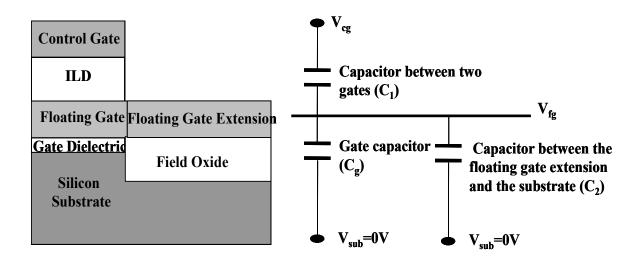

The schematic diagram of the improved sensor structure is shown in Figure 3-17. The floating gate extension was formed by the same polysilicon used for the control gate. From the design rules of the  $0.35~\mu m$  CMOS process, the dielectric thickness between the floating gate extension and the substrate was increased to  $\sim\!3070~\text{Å}[14]$  and the parasitic capacitance between the floating gate extension and the substrate was reduced. The devices could therefore have a lower threshold voltage and a better I-V characteristic. This will be discussed in detail in Chapter 5.

**Figure 3-17:** 3-D drawing of the improved sensor structure by using an N-type floating gate field-effect transistor.

Since the doped polysilicon can behave as an n-type conductor or a p-type conductor, the floating gate extension formed by the polysilicon layer could be put either in

an n-type sensor or in a p-type sensor. As a result, the top polysilicon layer was selected as the substitute of the bottom polysilicon layer.

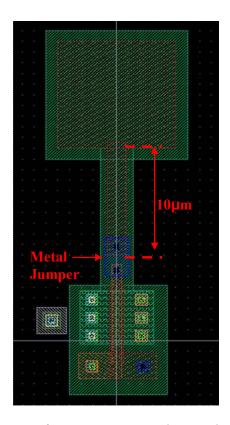

The floating gate extension was placed 10  $\mu m$  away from the field-effect transistor to keep the undercutting from affecting the transistor structure. Since the dimension of the gate extension was large, a metal jumper formed of the Metal1 layer was used to connect the floating gate extension and the floating gate of the field-effect transistor. During the sensor fabrication, the floating gate extension was not connected to the field-effect transistor until the metal jumper was formed. This temporary isolation kept the gate dielectric from being damaged by the charge that could have accumulated during some of the plasma based CMOS processes.

This plasma processes induced gate dielectric damage is referred to as the antenna effect [15, 16, 17, 18]. It is produced in the aluminum or polysilicon processing when the plasma etching is used. These metal layers are always covered by a non-conducting photoresist and built on top of an ILD layer, like a floating "island". During the plasma etching process, the charge can be stored on the sidewalls of these layers and induce a potential which may discharge through the oxide. This creates the defects in the dielectrics and reduces the insulating nature of the gate dielectric or ILDs. For MOSFETs, the gate damage during etching is an issue. The discharging channel through

the gate dielectric must be temporarily broken in order to protect the transistor.