## THE UNIVERSITY OF MANITOBA

## THE DESIGN OF A SOFTWARE ENVIRONMENT FOR THE DEVELOPMENT OF MODULAR PROGRAMS

by:

D. J. F. Hughes

#### A THESIS

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF COMPUTER SCIENCE

UNIVERSITY OF MANITOBA

WINNIPEG, MANITOBA

October, 1979

# THE DESIGN OF A SOFTWARE ENVIRONMENT FOR THE DEVELOPMENT OF MODULAR PROGRAMS

BY

## DAVID JOHN HUGHES

A dissertation submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements of the degree of

## DOCTOR OF PHILOSOPHY © 1979

Permission has been granted to the LIBRARY OF THE UNIVER-SITY OF MANITOBA to lend or sell copies of this dissertation, to the NATIONAL LIBRARY OF CANADA to microfilm this dissertation and to lend or sell copies of the film, and UNIVERSITY MICROFILMS to publish an abstract of this dissertation.

The author reserves other publication rights, and neither the dissertation nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

## **ACKNOWLEDGEMENTS**

I would like to acknowledge Dr. C. R. Zarnke, my supervisor, for his advice, suggestions and corrections and Dr. D. D. Cowan for providing me with computing resources at the University of Waterloo.

## DEDICATION

I would like to dedicate this thesis to my wife, Christine, without whose prodding this thesis would never have been completed.

#### ABSTRACT

Modular program development is the state-of-the-art methodology for computer project development. As yet, how-ever, there is no programming environment in which this methodology can be used conveniently and safely for the development of computer software projects.

This thesis examines the current typical program development environment from the point of view of the modular

program development methodology and points out the weaknesses in the present environment. It then focuses on the

interaction of the user with the system and outlines the

goals of a software system suited to this methodology.

These goals are then used in the design of such a soft-ware system, called DEMOS. DEMOS is an interactive system for the development of programs. It maintains complete control over the inter module interfaces not only at the user level but also at the operating system level. Consequently, it guarantees complete consistency checking during separate compilation of modules and thus encourages modular development. In this environment a module is always developed as a fragment of a larger program. This program, in turn, is con-

sidered as a module in an even larger program which may be a module of the operating system.

It should be noted that this thesis is concerned with the design of the software environment and does not describe a specific implementation of such a system.

## TABLE OF CONTENTS

| mah | le o | e co   | n +0 | n+ ~ |      |     |     |     |       |      |      |     |     |     |          |     |     |       |     |    | •   |   | -44   | . 4          |

|-----|------|--------|------|------|------|-----|-----|-----|-------|------|------|-----|-----|-----|----------|-----|-----|-------|-----|----|-----|---|-------|--------------|

| Tab | re o | יו ני  | и се | nus  | •    | 4 % | •   | • • | •     | •    | •    | •   | • . | •   | •        | •   | •   | •     | ٠   | •  | •   | , | 1.1.1 | <b>- 1</b> . |

| Tab | le o | f Fi   | gur  | es   | • •  | •   | •   | • • | •     | •    | •    | •   | • , | •   | •        | •   | • , | •     | ٠   | •  | . • | • | X     | i            |

| 1   | Intr | oduc   | tio  | n    |      | •   | •   |     | •     | •    | •    | •   | •   | •   | •        | •   | •   | •     | •   | •  | •   | • | • .   | 1            |

|     | 1.1  | Pro    | gra  | m D  | eve  | Lop | me  | nt  | in    | Pr   | es   | en  | t   | Da  | у        | Er  | ıVi | r     | onm | er | ıt  |   | •     | 3            |

|     | 1    | . 1. 1 | l T  | hе   | Env  | iro | nm  | ent |       | •    | •    |     | • . | •   | •        | • . | •   | •     | • , |    | •   | • | •     | 3            |

|     | -1   | .1.2   | . P  | rog  | ram  | De  | ve  | lop | mer   | ıt   | Pr   | oc  | es  | s   | •        | •   | •   |       |     | •  | •   | • | •     | 4            |

|     | 1.2  | Pro    | ble  | ms   | Enc  | oun | te  | red | ir    | 1 (  | ur   | re  | nt  | . E | n v      | rir | on  | ı m e | ∍nt | :  | •   | • | • ,   | 7            |

| 2   | A Mo | dern   | ı Pr | ogr  | am   | Dev | el  | opm | ent   | : E  | en v | ir  | on  | m e | en t     | :   | •   | •     | •   | •  | •   | • | 1     | 1            |

|     | 2.1  | Abs    | stra | ct   | Тур  | es  | •   |     | . • . |      | •    | • , | •   | •   | <b>.</b> | •   | •   | • 1   | ٠   |    | • , | • | 1     | 1            |

|     | 2.2  | Con    | sis  | ten  | су   | Che | ck  | ing | •     |      |      | •   | •   | •   | •        | •   | •   | •     | •   | •  | • , | • | 1     | 3            |

|     | 2.3  | sep    | para | te   | Com  | pil | at  | ion |       |      |      | •   | •   |     |          | •   | • , | •     | •   | •  | •   | • | 1     | 5            |

|     | 2.4  | Aut    | oma  | tic  | . Co | nsi | .st | enc | ус    | : he | ec k | in  | g   | • , |          | •   | •   | •     |     | •  | • , | • | 1     | 16           |

| -   | 2.5  | Des    | sign | Go   | als  | of  | D   | EMO | s     |      | •    | •   |     |     |          | •   | •   | •     | •   | •  |     | • | 1     | 9            |

|     | 2.6  | Reg    | [uir | eme  | nts  | fo  | Γ   | the | DI    | SMC  | s    | So  | lu  | tj  | on       | 1   | •   | • .   | . • | •  | •   | • | 2     | 0 9          |

| 3   | Logi | cal    | Org  | ani  | .zat | ion | . 0 | f D | EMC   | s    | •    | •   | •   | •   |          | •   | •   |       | •   | •  | •   |   | 2     | 22           |

|     | 3.1  | Mod    | lule | s i  | n D  | EMO | S   |     | •     | •    | •    |     | •   | • , | • ,      | •   | •   |       | • . | •  | • . | • | 2     | 22           |

|     | 3.2  | Mod    | lule | Re   | pre  | sen | ta  | tio | n     | •    | •    | •   | •   | •   | •        | • , | . • |       | •   | •  | •   |   | 2     | 24           |

|     | .3   | . 2. 1 | l C  | omp  | on e | nts | ;   |     | *     |      |      |     |     |     |          |     |     |       |     |    | •   |   | 2     | 26           |

| 3.2.1.1 Abstraction Components             |            |

|--------------------------------------------|------------|

| 3.2.1.2 Realization Components             |            |

| 3.2.1.3 Separate Procedures                |            |

| 3.2.1.4 Module Instances                   |            |

| 3.2.2 Component Dependencies               | 47         |

| 3.3 Consistency of Module Components       | 5(         |

| 3.3.1 Consistency and Compilation          | 50         |

| 3.3.2 Consistency and Modification         | 51         |

| 3.3.3 Compilation for Consistency Checking | 5 8        |

| 3.3.3.1 Categories of Dependence           |            |

| 3.3.3.2 Deferred Consistency Checks        |            |

| 3.4 Abstract Machines                      | 67         |

| 3.4.1 Machine Representation               | 70         |

| 3.4.2 The Development Environment          | 72         |

| 3.4.2.1 Machine Development                |            |

| 3.4.2.2 Machine Use                        |            |

| 3.4.3 Machines and Address Spaces          | 75         |

| Physical Organization of DEMOS             | <b>7</b> 9 |

| 4.1 Data Management                        | <b>7</b> 9 |

| 4.1.1 Data Areas                           | <b>7</b> 9 |

| 4.2 Address Management                     | 83         |

| 4.2.1 Address Spaces                       | 83         |

| 4.2.2 Address Allocation                   | 86         |

| 4.2.3 Address Resolution                   | 88         |

| 4.2.4 Addressing Scheme                    | <b>9</b> 0 |

|     | 4.2    | .5 U  | ser D | efine   | d A  | ddre | SS  | SĮ    | ac: | es | •   | • • |      | •   | •   | ٠     | •   | 98  |

|-----|--------|-------|-------|---------|------|------|-----|-------|-----|----|-----|-----|------|-----|-----|-------|-----|-----|

|     | 4.3 M  | emory | Mana  | gemen   | t .  |      | •   |       |     | •  | • , | •   |      | •   | •   | •     | •   | 104 |

|     | 4.3    | .1 M  | emory | Spac    | es . |      | • , |       | •   | ٠  | •   | •   |      | •   | •   |       | •   | 104 |

|     | 4.3    | . 2 A | ddres | s Dec   | odiı | ng   | •   |       | •   | ٠  | •   | • . | •    | •   | •   |       | • , | 107 |

|     | 4.4 н  | ardwa | re Su | pport   | • (  | • •  | •   |       | •   | •  | •   |     | •    | •   | •   | •     | •   | 114 |

| 5   | DEMOS  | in Re | view  | • . • • |      |      | •   | • , • |     | •  | •   | • 4 |      | . • | •   | . • , |     | 119 |

|     | 5.1 s  | atisf | actio | n of    | the  | Goa  | ls  | •     | •   | ٠  | •   | • • |      | •   | • , |       | • , | 119 |

|     | 5.2 A  | dditi | onal  | Benef   | its  | and  | F   | utu   | ıre | De | eve | 10] | om e | nt  | •   | •     | •   | 125 |

| App | endix  | A Ad  | dress | Space   | e Mo | odu1 | е   | Exa   | mp: | le | •   | • • | •    | •   |     | •     | •   | 128 |

| Ref | erence | s     |       |         |      |      |     |       |     |    |     |     |      |     |     |       |     | 136 |

## TABLE OF FIGURES

| 3.2.a Mo  | dule Dep  | endenc | е      |         |      | • 1     | • •   | • , | • •   | • •   | • •             | 25           |

|-----------|-----------|--------|--------|---------|------|---------|-------|-----|-------|-------|-----------------|--------------|

| 3.2.1.a   | Component | t Grou | ps .   | . • • • |      | • (     |       | • , | • 1   |       |                 | 27           |

| 3,2,1,1.a | Abstrac   | ction  | Compo  | nents   |      | , •     |       | •   | •     |       | • , •           | 30           |

| 3.2.1.1.b | Abstrac   | ction  | Repre  | sentat  | ion  |         | • , • | •   | • 4   |       | • . •           | 34           |

| 3.2.1.2.a | Realiza   | ation  | Compo  | nents   |      | •       |       | . • | •     |       |                 | 36           |

| 3.2.1.2.b | Realiza   | ation  | Repre  | sentat  | ion  | • (     |       | •   |       |       | , <b>•</b> 70 ( | , 41         |

| 3.2.1.3.a | Separat   | ce Pro | cedur  | e Comp  | onen | ts      |       | • . | • 1   | • , • | • , •           | 43           |

| 3.2.1.3.þ | Separa    | e Pro  | cedur  | e Repr  | esen | tat:    | ion   | •   | •     | •     | • . •           | 45           |

| 3.2.1.4.a | Data Ar   | cea Re | prese  | ntatio  | n .  | • (     | • , • | •   |       | • , • | • , •           | . 4 <b>7</b> |

| 3.2.2.a   | Module Co | mpone  | nt Su  | nmary   |      |         | • , • | ٠   | •     |       | • . •           | 48           |

| 3.2.2.b   | Component | t Depe | ndenc  | ies Ma  | inta | ined    | l b   | y D | EMO   | os    | • , •           | 51           |

| 3.3.3.2.a | Deferre   | ed Con | siste  | ncy Ch  | ecks | • •     | • •   | . • | •     |       |                 | 64           |

| 3.4.3.a   | Containe  | d and  | Separa | ate In  | stan | ces     | •     | •   |       |       |                 | 76           |

| 4.1.1.a   | Data Area | а Туре | s      |         |      | . • . • | • , • | . • |       | •     | • , •           | 82           |

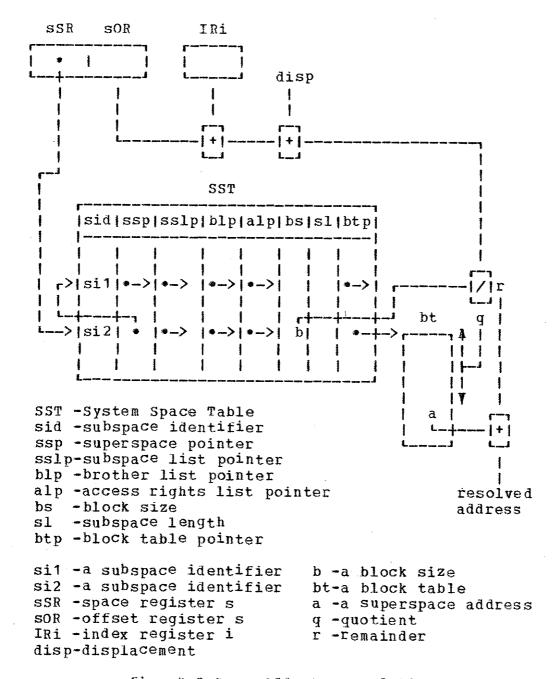

| 4.2.4.a   | Address H | Resolu | tion   | • • •   | • •  | • •     |       | •   | • . • | •     | • 2 •           | 93           |

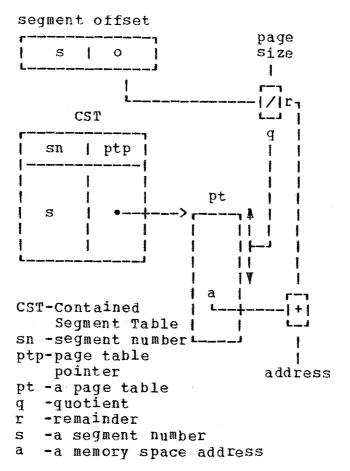

| 4.3.2.a   | Address I | ecodi  | ng .   | • . • • |      | • •     |       |     | • . 4 |       | • •             | 111          |

#### 1 INTRODUCTION

Modular program development is the state-of-the-art program development methodology. It incorporates the concepts of stepwise refinement [23], structured programming [9], and top down design [17]. The breakdown of a task into subtasks done by chief programmer teams [1] reflects this methodology. Languages have also been developed with this methodology in mind [24]. However, up to now, few attempts have been made to provide a programming environment in which this methodology can be used conveniently and safely for the development of computer software projects [19], [22], [6], [4].

modular programming implies the decomposition of a system into a number of interacting components called modules. The decomposition is done according to a set of guidelines. A number of sets of guidelines have been used including functional decomposition [23] and decomposition by abstract data types [14]. Other decomposition criteria have also been proposed [21]. Throughout this thesis the term modular

INTRODUCTION 2

programming will be used to imply decomposition by abstract data types.

terminals) and software (e.g. interactive systems) used in program development. The Current environment is inadequate mainly in the area of software. The software provided in current program development environments is outdated by the modern program development methodology. It is the interaction between the user and the software system which requires updating to make the program development environment suitable for modular program development.

This thesis, therefore, concentrates on the design of a suitable software system. The designed system, DEMOS (Development Environment for MOdular Systems), integrates the tools of program development into a single system which is oriented towards modular programming. Included in the system are facilities for module abstraction and realization, control of module interaction and resource needs, and testing and modifying of modules. The system is interactive since program development requires constant feedback. The system automates consistency checking and therefore frees the programmer from the error prone task of verifying consistency of interfaces between modules. Module development

INTRODUCTION

is done within the environ of an abstract machine which itself contains modules which are in the environ of still other abstract machines which ultimately are machines of the operating system.

The designed system will realize these goals and, at little extra cost, will yield added advantages. Some of these advantages include the easy integration of: a high-level debugging aid which can yield meaningful information, a simulator for modules which have been designed and not yet implemented, and an automated program prover (when this becomes possible).

#### 1.1 PROGRAM DEVELOPMENT IN PRESENT DAY ENVIRONMENT

#### 1.1.1 THE ENVIRONMENT

Tools in the software system of the typical program development environment include a procedure oriented language and a compiler for it (eg. PL/I, FORTRAN, COBOL), an online editing and job submission (usually to batch) system (eg. TSO), a linkage editor or loader, a job control language processor and system level routines which are used as primitives in program development.

THE ENVIRONMENT 4

The language and compiler allow compilation of a procedure and perform type Checking within the scope of the compilation. The information passing between separately compiled procedures is limited to parameters and some set of common external names.

The online system allows program editing and submission. Sometimes it includes foreground or online execution and debugging.

The linkage editor (or loader) is used to connect separately compiled procedures together prior to execution time. It also connects library procedures into the resulting object deck.

The job control language processor is used to control the order of execution of the tools (eg. compiler and linkage editor) and specify the source and destination of all "files" (eg. procedure text, object deck, data etc.).

The system level routines are either linkedited into the object deck or are dynamically invoked at execution time by supervior calls (SVC's).

## 1.1.2 PROGRAM DEVELOPMENT PROCESS

Within the previously outlined system (section 1.1.1) a certain program development process emerges. This process is an approximation to the modular programming methodology which is restricted by the tools available.

The first step in the process is that of developing a complete problem statement. This is really a process which precedes the actual software development process and is the same in all environments.

The next step is the stepwise refinement process. This is carried out by the chief programmers [1]. It includes specification and documentation of procedure interfaces and behaviour, description of global and local data areas, and definition of access rights to procedures and levels of the program. The result of this step is a document (or documents) indicating the expected behaviour of the entire project. It may be stored online so that it may be accessed as needed by programmers during the development phase of the project.

Once the design phase is completed the programmer teams develop their portions of the project more or less independently. Within each team, development usually progresses

from bottom to top, that is, the procedures which depend only on system routines, library procedures, and/or programming language features, are coded first and once they have been coded, tested, and debugged, procedures at the next level may be developed. An alternative is a top down approach where program stubs are used.

Each procedure is developed independently with reference to the design document for specification of interfaces and use of global data areas, etc. The procedure is compiled and tested independently of others and when it is thought to be correct, it is linkedited into the object deck for the entire project. Once this is done it provides part of a basis for the next level of development.

sometimes, during the development phase, a design decision is found to be incorrect or incomplete. When this occurs, it is necessary to re-evaluate parts of the design phase and then modify the design document. After this has been done it is then the responsibility of each team to ensure that the procedures they have previously developed and are currently developing, conform to the new, modified design document. This is probably the most confusing and error prone part of the development process.

Once the development process reaches the top level of the design, an overall system test may be carried out and then the integration of the project into common use can begin.

## 1.2 PROBLEMS ENCOUNTERED IN CURRENT ENVIRONMENT

There are numerous problems in trying to use modular program development methodology in the current environment. These stem from the fact that the current environment was developed to support the development of a program as a single entity. Only when the need for independent development of separate portions of the same project was realised were some attempts made to adapt the environment to this purpose.

The major problem in the current environment is the lack of any control or verification of the interfaces between separately compiled parts of a program. The only method for controlling these interfaces is the design document which states what these interfaces should be. There is no automatic method of verifying that these proposed interfaces are the ones actually used. Thus it is quite possible, and often the cause of many problems, for one

procedure to view an interface one way and another procedure to view it in some other way, causing incorrect intercommunication between these procedures. This error is not detected except after a painstaking search when some unexplainable bug is encountered after these two prodedures are used together.

Another area where lack of interface verification is a problem is that between the program and the operating system. The operating system has no a priori knowledge that a program is going to communicate with it correctly. It must, therefore, test at execution time whether the program's usage of the interface is correct if it is to make any test at all. Unfortunately, the number of ways in which the interface could be used incorrectly is large and the operating system cannot check for all of them. Also since this verification is done at execution time it is performed every time the interface is used and is thus very expensive.

When the design document is being developed there is no automatic method of discerning whether or not its specification of interfaces is consistent. It must, therfore, be thoroughly checked for consistency by its authors. This is a time consuming process and is definitely error prone.

When a design decision is reevaluated, and this leads to a modification of the specification of an interface or interfaces, there exists no mechanism which can ensure that the new interface specification is reflected throughout the project, both in existing, already tested procedures and ones under development. Sometimes the change in interface does not affect a procedure other than to change some data typing information; othertimes it may have far reaching effects and may demand redevelopment of a procedure.

A large portion of development time is spent in verifying the interfaces between procedures. It is not sufficient to test a procedure by itself but it must also be tested in conjunction with every other procedure with which it could interact. If there was a guarantee that a procedure used its interface correctly, that its only method of accessing external information was via that interface, and that any intercommunication with that procedure was via that interface, then a large portion of the testing could be eliminated since the definition of a procedure would be guaranteed consistent with its uses.

There is a requirement for users of the current environment to have a familiarity with many languages. In addition to the language in which the program is being written, the user is required to know the online system command language, the editor commands, the linkage editor commands and the debugging facility commands. This proliferation of languages causes time loss and confusion to the users.

Procedure testing and debugging is usually carried out at a lower level than that of the programming language. That is, most debugging packages allow only machine level interaction with the procedure to be debugged. This means that a user must understand the way in which the compiler he is using operates and represents the data structures of his program. If a debugging package is not used then either core dumps or traces must be used. Both of these produce a large amount of output which must then be searched for what is really desired. Again, the core dump and some traces are at the machine level and thus suffer from the same problems as the machine level debugging package.

A final problem in the current environment is the unit which can be developed independently. In most languages and compilers this unit is the procedure. This limits definition of interfaces to specification of procedure parameters and declaration and use of global variables. There exists no way of grouping together, into a single development unit, the data and the procedures which work on that data (i.e. an

abstract type [14]) and specifying inter type rather than inter procedure interfaces.

#### 2 A MODERN PROGRAM DEVELOPMENT ENVIRONMENT

#### 2.1 ABSTRACT TYPES

The design of a system using stepwise refinement involves the definition of the behaviour of the system and the resources it provides to a user. The abstractions necessary to implement the system can then be specified by defining their behaviour and indicating what resources each provides. The 'aggregate of these abstractions defines an abstract machine which provides the resources desired In the next level of refinement user of the system [14]. the abstractions necesary to implement the abstractions of the previous level can be specified. Again, these can be aggregated into subsystems required to implement abstract types of the previous abstract machine, and each of these subsystems is in fact an abstract machine at the lower level. Eventually the abstractions required to implement all of the remaining abstract machines will be available on the target machine, and the design will be complete.

ABSTRACT TYPES 13

The abstractions at each level are definitions of new abstract types with the operations defined upon the abstract type as part of the definition. These abstract types make up the modules of the modular programming methodology.

The abstraction is the design unit in which an abstract type is defined. It includes a definition of the abstract type's behaviour, a specification of the resources provided, and a specification of the abstract types required for this abstract type's implementation [8]. The specification of the resources provided and the abstract types required constitute the abstract type's interface with other abstract types in the design.

In the implementation of a program in a top down manner, an abstract type at one level is implemented in code

for an abstract machine of the next lower level. The

abstractions of the abstract machines at the lowest level

are implemented in the code of the target machine.

The realization is the programming unit in which one abstract type of an abstract machine is realized. It consists of code, written for the underlying abstract machine, which realizes the resources specified in the abstraction according to the behaviour there defined and using the abstract types there specified.

An abstract type is thus two parts [12]: an abstraction which includes the module's interface with the external environ, and a definition of the abstract type's behaviour; and a realization.

when design and implementation are complete we have a collection of abstract types, each providing resources for some abstract types and each depending on resources provided by other abstract types.

## 2.2 CONSISTENCY CHECKING

As a program is being designed using the method indicated in section 2.1, a number of abstractions evolve. To verify that the design is correct it is necessary to prove these abstractions to be both complete and consistent.

completeness means that all abstractions which have been referenced by any abstraction are defined in the system. Consistency means that the abstractions interact in a consistent manner, that is, reference only the resources provided by other abstractions and use these resources in a manner consistent with their definitions.

Proof of completeness is easily done by comparing references with the abstractions defined. The proof of consistency involves proving each abstract type's interface to be consistent with that of every other abstract type with which the first intercommunicates. This implies, for example, verifying that the type, number of actual parameters and types of the actual parameters in the reference match the type, number of formal parameters and types of the formal parameters in the resource definition. In addition the object referenced in the operation must be verified to be an instance of the abstract type for which the operation is defined.

During implementation, a realization is developed for each abstraction. It is necessary to prove this realization valid. To do this, it must be verified that the realization behaves as defined in the abstraction and that it uses the interface specified in the abstraction correctly.

Whenever a modification is made, be it to the abstraction or the realization of the abstract type, some reverification must be done. Depending on the change, the reverification may be localized or very general. If the change is to a realization, the reverification is localized and involves verification that the new realization is con-

sistent with the abstraction for this abstract type. If the change is to an abstraction then it is necessary to verify that the realization for this module is still consistent with the new abstraction and that the interfaces of this abstract type and all abstract types with which it intercommunicates are still consistent.

### 2.3 SEPARATE COMPILATION

As was indicated in section 2.1, the implementation of an abstract type is perceived as a single problem during the implementation phase. This implies that the only concern during the implementation of an abstract type should be how it is implemented and not how it is to fit into the scheme of things for the entire project. The implementation proceeds with reference only to the abstraction defined during the design phase of project development. Thus implementation of an abstract type proceeds without knowledge of the abstract type from which it was abstracted [20]. This, in essence, is what modular programming is all about and what makes it a reasonable program development methodology.

Since the implementation of an abstract type proceeds independently of the implementation of other abstract types, so the verification of the implementation should proceed independently. The verification process includes a proof of the implementation's consistency with the behaviour and interface given in the abstraction.

The proof that the realization is consistent with the definition of the abstract type's behaviour is actually a program proof as defined in the literature [16]. Automatic program proving or a formal or informal manual proof may be used to verify this consistency. The compiler used to compile the realization may verify that the realization uses the interface specified in the abstraction correctly if the abstraction is compiled along with the module.

## 2.4 AUTOMATIC CONSISTENCY CHECKING

Separate compilation as described above (section 2.3) can provide automatic consistency checking on only two of the four areas described in section 2.2 (i.e. that abstractions are complete and consistent and that realizations behave as defined and use the interfaces correctly). The

checks on completeness of abstractions and the checks of consistency of interfaces cannot be automatically done at compile time using separate compilation in current systems. The check of completeness can be done at link-edit time but the check of consistency of interfaces is done at execution time, if at all. This would require that code be produced at each point of access to every module to verify that the module has been accessed correctly.

This solution is expensive in three ways. First, it does not provide the check until the abstraction is tested with all other abstractions with which it interacts, at which time, if there are any errors, development must return to a point which was passed possibly months before. Secondly, of course, the interfaces are checked whenever the program is run causing extra execution time. Thirdly, the solution is incomplete, since only the interfaces actually used in the test are verified instead of testing all interfaces which may be used in production. If the operating system is developed in this same way, this solution could provide consistency checking of the interface between the modules in the project and the modules in the operating system.

A second solution providing automatic consistency checking is to eliminate separate compilation and force all abstract types in a project to be compiled simultaneously. In this way, complete consistency checking could be done since all information required by the compiler is available.

This solution is cost prohibitive. In a large project the number of abstract types to be compiled would be exceedingly large and compilation times would be long. Whenever a modification, however minor, were made to a abstract type, complete recompilation of the entire project would have to be done. In addition, to maintain complete consistency checking of the project to operating system interface at compile time would require a complete recompilation of the operating system and the project together which is essentially impossible.

what is desired is a system in which complete consistency checking can be done automatically at compile time, thus eliminating the errors and oversights common in manual checking, and providing all the information about consistency errors at the time that it is required. In addition, of course, the solution must allow separate compilation.

#### 2.5 DESIGN GOALS OF DEMOS

The intent of the design of DEMOS is to provide a suitable software environment for the modular development of programs. The system will support the complete development process (section 2.1) from design through implementation and testing as well as the project's life in production. Complete consistency between all abstract types (section 2.2) will be enforced by the system, including those in the operating system, while allowing separate compilation of abstract types to be performed (section 2.3).

Inconsistencies will be detected and reported at compile time. The design phase will be conducted on-line so that any design inconsistencies can be detected at that time. Abstract types will be checked for consistency when they are entered during development. Whenever abstractions or realizations are modified, any resulting inconsistencies will be noted. At no time will an inconsistent abstract type be allowed to be utilized.

Data security will be provided by the enforcement of consistency in access to data by the compiler and be supplimented by access rights checking, by the execution environment, of access to instances of abstract types.

The system will be on-line to provide immediate feedback and will be integrated rather than a collection of tools.

## 2.6 REQUIREMENTS FOR THE DEMOS SOLUTION

The provision of the facility of automatic consistency checking at compile time while still allowing separate compilation, places certain requirements on the system. These requirements include: use of high-level language(s) only, retention of abstractions after compilation, provision of a mechanism to detect possible inconsistencies after a modification is made, and provision for the development of the operating system utilizing this system.

A high level language is necessary since only a compiler can do the required consistency checking. To allow a translator (for a language at any level) which does not or can not do the consistency checking to be used in this system would defeat the entire purpose of the system. The language(s) must not allow low level operations which could be used to defeat the consistency checking (e.g. unrestricted use of pointers etc.) for the same reason.

The abstraction provides valuable information to be used for consistency checking. It is created during the design phase and should not be included in the code for the realization but should be automatically used when the realization is compiled. After compilation the abstraction should not be discarded but retained so that other compilations may refer to it. When an abstract type is designed to interact with another abstract type, the abstractions are used to ensure consistency. After a modification is made, the abstractions may be used to reverify the consistency of the interfaces.

There must be a supervisory system which enforces consistency upon abstract types. It is this system which provides the correct abstractions to the compiler when compilation of a realization is being done. It also verifies completeness of the abstractions. A further requirement is that it be able to detect when inconsistencies are caused by modification of an abstract type and which abstract types are affected, and ensure that these inconsistencies are corrected before any execution is begun.

Finally, the operating system must have been developed within this system since project abstract types interact with operating system abstract types and the consistency of this interface must also be under control of the system.

## 3 LOGICAL ORGANIZATION OF DEMOS

### 3.1 HODULES IN DEMOS

The module concept in DEMOS is a language independent concept similar to that of the class concept in SIMULA [3], the cluster concept in CLU [14], [15], the form concept in Alphard [25], and similar constructs in other languages [18], [10], [24]. It embodies the data type abstraction discussed in [14] and section 2.1. The difference between the module in DEMOS and the class in SIMULA is in the ability to reference the individual parts which make up the entity. In SIMULA all names in the class may be referenced by any process which has access to any member of that class. In DEMOS, the module explicitly states which parts are visible (referable) outside the module and which are not.

The class definition in SIMULA and the module definition in DEMOS both are declarative in nature and provide the

MODULES IN DEMOS 24

definition of a class of entities which could be created by anyone having access to the definition. In SIMULA, when a new member of the class is created (using the new operator), it appears to have all the facilities declared in the class definition but is distinct from any other member of that class. The same is true in DEMOS. When a module instance is created, it appears to have all the facilities defined in the module definition but is an entity different from any other instance of that module.

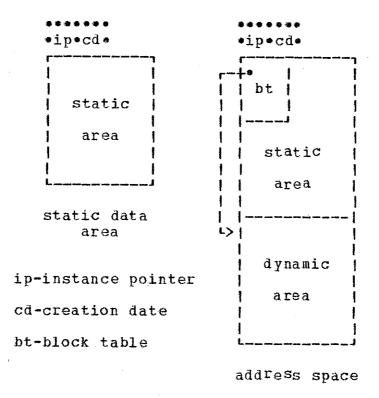

In DEMOS there are two things then, the module definition (hereafter called the module) and the instances of the module (hereafter called the module instances). The module serves as a definition of the behaviour and form of the module instances. The module consists of the two parts mentioned earlier (section 2.1), namely the abstraction and the realization. The module instance appears to include within itself the complete abstraction and realization and behaves accordingly, but is in fact only a data area (section 4.1.1) upon which operations specified in the module operate.

## 3.2 MODULE REPRESENTATION

A module is the development unit in the DEMOS system. The system provides for separate compilation of modules while retaining complete consistency checking. Modules in the system have interdependencies which force a new consistency check of a previously checked module to be performed whenever a module with which it interacts is modified, in order to maintain assurance of consistency. Since, in general, one module may interact with many other modules each of which may interact with others, and so on, the number of new consistency checks of other modules due to a change in one module may be large and an effort must be made to limit the number and complexity of these consistency checks.

To do this, DEMOS does not maintain a module as a single unit, but as a collection of pieces called components. The choice of what makes up a component is made with the need for limiting the complexity of the consistency checks in mind.

In addition to the components which make up a module, the system maintains a set of dependency relationships between module components, both within and among modules. A component A is said to be dependent upon a component B if:

- a) A is another representation for the information in B (direct dependence)

- b) there is an implicit mapping of entries in component B to entries in component A (form dependence)

- c) there is an explicit mapping (i.e. a pointer, offset or index) from A to component B (Pointer dependence)

- d) component A contains information taken from component B (information dependence)

Dependencies are used to determine when components must be subjected to new consistency checks. The rule used is: if component A is dependent upon component B and component B is modified, then component A must undergo a new consistency check.

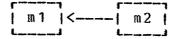

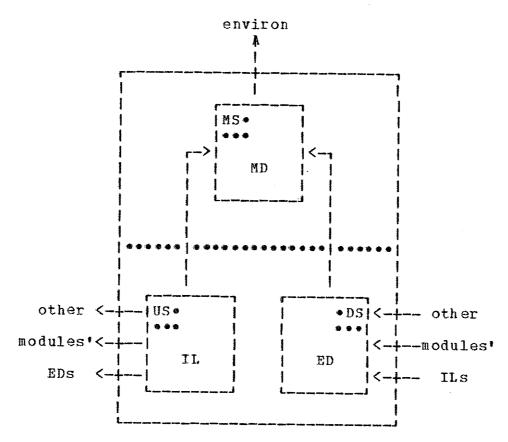

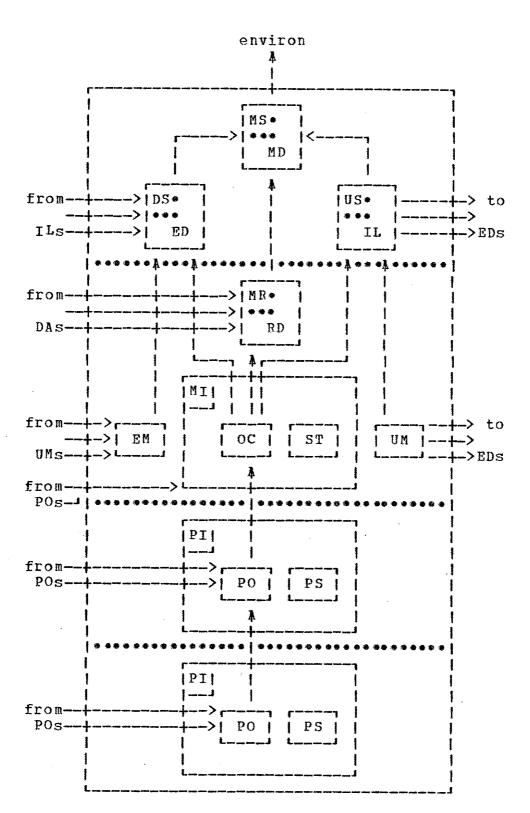

fig. 3.2.a Module Dependence

Logically, when a module m2 uses resources provided by a module m1, we have a dependence relationship such that m2 is dependent upon m1. This relationship can be viewed as

shown in figure 3.2.a. Here a module m2 is dependent upon a module m1 (as shown by the arrow) since a change to module m1 must force a consistency check of module m2 to ensure consistency. In DEMOS, the logical dependence of m2 upon m1 is reflected by the actual dependence of some components of module m2 upon some components of module m1.

## 3.2.1 COMPONENTS

As was indicated in section 2.1, to a user a module is composed of two parts: an abstraction and a realization. These are two distinct entities developed at different times in the development process, the abstraction being developed during the design phase and the realization during the implementation phase.

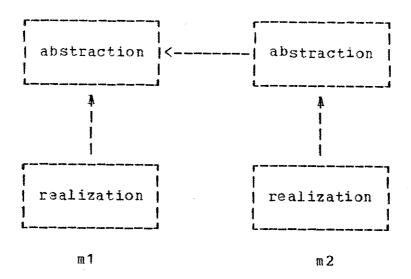

In DEMOS the logical division of a module into two parts is reflected by a division of the module representation into two groups of components. The first group consists of components reflecting the definition of the module, i.e. the abstraction. This group also defines the interface of the module with other modules within the system. The second group reflects the particular realization of the defining abstaction. (see figure 3.2.1.a)

fig. 3.2.1.a Component Groups

Here the dependence of module m2 upon m1 is reflected by a dependence of the abstraction of m2 upon the abstraction of m1 and indicates that m2 uses resources provided by m1. The realization is dependent upon the abstraction since it is a realization of the module as defined by the abstraction.

The realization is separated from the abstraction since the realization has no effect upon the interface between this module and others. Any realization which realizes the module defined by the abstraction would suffice and a change to the realization does not require any new consistency checks of the interface between this module and others.

## 3.2.1.1 ABSTRACTION COMPONENTS

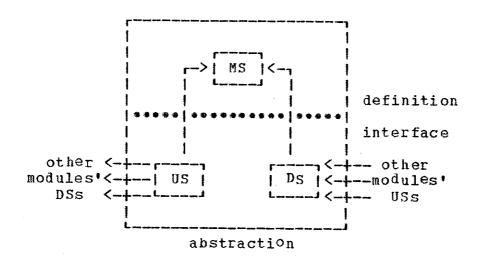

The abstraction can be viewed as a definition part and an interface part. The definition part indicates the parameterization of the module and the machine upon which this module is to be implemented. The interface part indicates the interface that this module has with other modules.

The definition part is represented by a single component called the module specification (MS) which contains the parameterization and the name of the implementation machine for the module. A module may be parameterized so that different instances of the module may vary structurally but remain organizationally the same [25]. This parameterization includes parameters of the standard types within the system language and parameters of the type type (i.e. module may be parameterized by a data type). This allows a module to be somewhat representation independent, at least in these parameters. For example: a single module "stack" could be defined, parameterized by an integer (the maximum stack depth) and a type (the type of elements in the stack). This one module could be used to define stacks of any depth and type including even a stack of stacks. The values of module parameters are not available until module instance creation time and thus the use of parameters cannot be consistency checked until that time.

The interface part is represented by two components, the uses specification (US) and the defines specification (DS).

The uses specification indicates the resources required by this module and the names of the module(s) which are expected to provide them. This component is dependent upon the module specification since the modules available to provide the resources needed belong to the machine listed in the module specification or are parameters of the module (as indicated by the module specification). The existence of the resources is known only to the module from which the resources are drawn. Thus the uses specification is dependent upon the defines specification of all modules from which this one draws resources.

The defines specification indicates the resources provided by the module to other modules within the system. For each resource it also gives complete typing information. Since the types may be modules which provide resources to this module, or types in the parameter list, this component is dependent upon the module specification of this module.

The components that make up the abstraction of a module are shown in 3.2.1.1.a. It can be seen that the dependence of one module's abstraction upon that of another is repre-

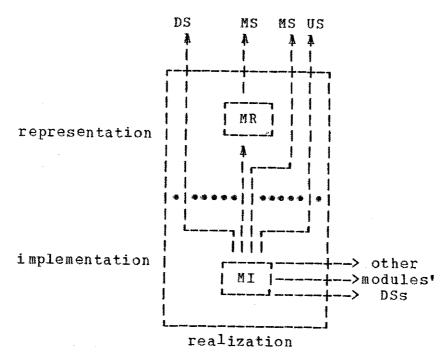

fig. 3.2.1.1.a Abstraction Components

sented by the dependence of that module's US upon the DS of the other.

The resources defined and used by a module are all operations upon the abstract type which is defined by the module. These are represented by procedures and operators. Data objects within the module are not provided as resources since this would cause a dependency of modules upon the representation (see section 3.2.1.2) of the module which is not part of the abstraction. If, in fact, access is desired to a data object from within another module, this access may be made via procedures defined for this purpose in the defining module. These procedures themselves are dependent upon the representation but the use of the procedure is not and thus the unwanted dependency between a module and the representation of another is avoided.

The three components of the abstraction are created by the designer of the module and thus originate in a human comprehendable (external) form. To facilitate consistency checking, an internal form would be preferred. DEMOS maintains an internal form of each of the three components of the abstraction.

The internal form of the module specification is called the module definition (MD). It consists of a pointer to a machine and a table containing one entry for each parameter in the parameter list. In addition the table contains one entry for each module available for use in implementation of this module. Each entry contains: the module or formal parameter name; a flag indicating whether the entry is for a module or a formal parameter; the type of the object described by the entry (modules have type type) in a coded form; and an address field which is either the offset within the parameter space to the parameter (if the entry is a parameter) or the module address within the system (if the entry is for a module which is not a parameter).

The internal form of the uses specification is called the import list (IL). A resource is said to be imported if it is provided by another module and used by this one. The import list contains one entry for each resource used by the module. Each entry contains: the resource name; the offset in the MD of the entry for the module providing the resource; and the index, into the export definition (ED see next paragraph) of the module providing the resource, of the entry for the resource used. This provides a link from the IL to the ED of the module providing the resource since the location of the ED can be found from the module address which is contained in the MD. Note however, that if the module providing the resource is a parameter, the ED index is not available until module instance creation time and differs with different module instances. Thus, for a module parameter, the ED index field is not used in the IL but resides in the parameter space.

The internal form of the defines specification is called the export definition (ED). It contains one entry for each resource defined by this module. Each entry contains: the resource name and the type of the resource in a coded form. The coded form includes an offset within the MD whenever a type defined by a module is used in the parameterization of the resource.

The module definition contains all the information contained in the module specification except for the machine name. Due to this fact, if the machine name is retained in

the MD, the external form of the module specification can be regenerated from the internal form except for the layout (i.e. spacing etc.). If a standard layout is adopted, it is not necessary to maintain the external form at all, since, whenever the external form is desired, it can be regenerated from the internal one. Changes can be made by the user, directly to the internal form as well, (even though the user may think he is modifying the external form). Thus DEMOS maintains only the MD and an imaginary MS.

A similar argument can be used for the uses specification and the defines specification except for one thing. When the IL (or ED) is consistent with the MD, the pointer into the MD can be used to regenerate the module names referred to by the entry. However, if the MD is modified, the pointer is no longer valid, and there is no longer any way to regenerate the module name for this entry. come this problem, another field is added to each of the IL The field added to the IL contains the name of the module providing the resource. The field added to the ED contains an internal text form of the typing information of the resource. Now all the information required for regeneration of the US from the IL and the DS from the ED is avaILable for listing, modification or consistency checking purposes, and so DEMOS maintains only the IL and ED and an immaginary US and DS.

fig. 3.2.1.1.b Abstraction Representation

The final form of the abstraction part of the module representation is shown in figure 3.2.1.1.b. Here the IL and the ED are dependent upon the MD by pointer dependence since they contain offsets into the MD. The IL is dependent upon the EDs of other modules which supply resources to this module by pointer dependence since it contains indices into these EDs. The MD has a dependence as well since it is dependent upon the source of the module names and addresses by information dependence. This source is termed the environ of the module and is discussed in section 3.4.

### 3.2.1.2 REALIZATION COMPONENTS

The realization of a module can be viewed as two parts, a representation part and an implementation part [12], [5]. The representation part indicates the concrete representation of the abstract data type defined by the module and the implementation part indicates the implementation of the operations defined upon that type.

The representation part is represented by a single component called the module representation (MR). The module representation contains declarations of all variables (fields) which make up the concrete static representation of the abstract type. This representation defines the instantiation of the module (i.e. the module instance or data area). The typing information includes references to modules listed in the module definition component of the abstraction part of the module.

The implementation part is represented by a single component called the module implementation (MI). The module implementation contains the source code for operations defined by or local to the module, and the code for creation and disposal of the module instances. The source code makes reference to the resource declarations given in the DS of this and other modules, uses only resources listed in the US

and references modules of the environ indicated by the MS and the variables declared in the MR.

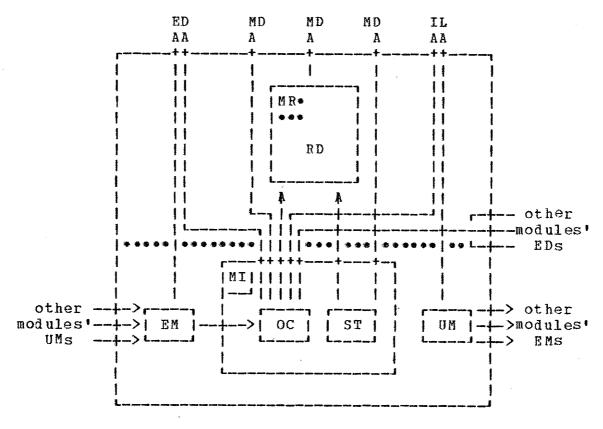

The realization part is thus represented as shown in figure 3.2.1.2.a.

fig. 3.2.1.2.a Realization Components

The two components of the realization were created by the implementor in a human comprehendable (external) form. Execution speed can be improved if internal forms of the components are maintained, since this would obviate the necessity of scanning the MR and interpreting the MI during execution. To facilitate this improvement, DEMOS maintains

some internal components for the realization part of the module definition.

The internal form of the module representation is called the representation dictionary (RD). The representation dictionary contains one entry for each field (variable) in the representation of the abstract data type. Each entry contains the field name, the type of the field (encoded in an internal form) and the address of the field within the data area. The internal form of the type includes an offset into the MD or standard type table to entries for the names of the modules which define the types of the fields.

The RD contains all of the information from the MR as long as it is consistent with the MD. However, this consistency may be violated if the MD is modified and, in this event, it is impossible to determine the types of the fields directly from the coded type in the RD (since this contains offsets into the MD which are now invalid). To enable the maintenance of only the RD and not the MR, a new field must be added to the RD which contains the type of the field in an internal text form. This now allows the regeneration of the MR from the RD and thus eliminates the need to maintain both the MR and the RD.

The internal form of the MI is more involved. Clearly the most important component is the object code (OC) created from the MI. This object code requires the addresses of all resources which it utilizes including those provided by other modules. If these addresses were coded directly into the OC, they would force the OC to be dependent upon the OCs of other modules by pointer dependence. This is undesirable since this would make the implementation of one module dependent upon the implementation of another which violates the desire that modules be implementation independent.

To overcome this, a new component is added to the implementation part of the realization. This component, called the entry map (EM), contains the offsets of the resources defined by this module within the object code component. This enables a reference to this table by the system at execution time when a call is made to a resource in this module, in order to get the address of the resource.

This, however, has two drawbacks. Firstly, this reference must be done at each use of the resource even if its address has not changed since the last use and, secondly, requires system intervention at execution time to resolve the reference.

To remove these drawbacks, another component is maintained as part of the implementation. This component, called the use map (UM), contains one entry for each external name referenced. This entry contains the offset within the OC of the providing module of the resource referenced. These offsets are loaded from the EMs of the providing modules. All references to external resources from the OC are made indirectly via the UM. As long as the UM is consistent with the EM of a providing module, the reference to the resource can be made without system intervention. If the UM is not consistent with the EM, the new offsets in the EM must be loaded into the UM before execution may proceed.

Since there is one entry for each resource referenced by the module implementation in the UM and there is one entry for each resource referable in the IL, there is an entry in the IL for each entry in the UM. In fact, in a fully implemented module, there should be a one-to-one correspondence of entries in these two components. The UM could even be considered as part of the IL except that it is dependent upon implementational not abstraction considerations. Due to this correspondence, the UM is maintained only as a table of offsets organized so that there is a correspondence between the entries in it and the entries in the IL such that the first entry in the UM is the offset of the resource described by the first entry in the IL, etc.

A similar argument can be used for the structure of the EM resulting in the EM being simply a table of offsets which has a one-to-one correspondence to ED entries such that the first entry in the EM is the offset for the resource described in the first entry of the ED, etc.

It is now possible to do an efficient job of loading the UM when necessary. If the IL is consistent with all EDs upon which it depends, it contains indices into the EDs (and hence EMs) of the providing modules and its entries correspond one-to-one with the entries in the UM to be loaded. Thus a series of simple index and copy operations can be used to load the UM from the required EMs.

A final component is added to the implementation part of the realization of a module. This component, called the symbol table (ST), is added for consistency checking of separately compiled procedures (section 3.2.1.3). The symbol table contains one entry for each name declared in the MI. Each entry contains the name, the encoded form of the type, the scope of the name and its offset or value. This component is another internal form of the MI.

The OC and the ST together do not give all the information contained in the MI since the translation of source language statements into machine language instructions does

OF MANITOBA

LIBRARIE

not have a well defined reciprocal operation. Thus, the MI must be maintained in order to have a human readable form, unlike the cases for the MS, DS, US, and MR.

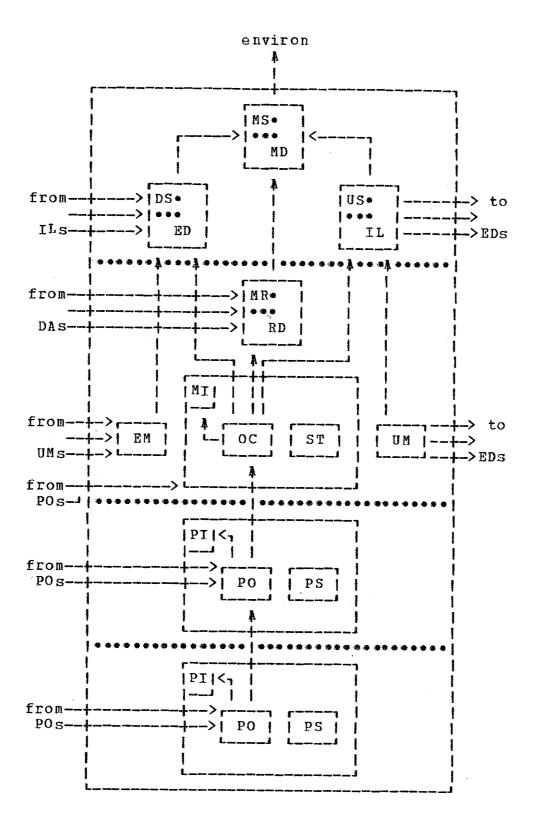

fig. 3.2.1.2.b Realization Representation

The final representation of the module realization is shown in figure 3.2.1.2.b. Here the RD is dependent upon the MD by pointer dependence since it contains indices into the MD (i.e. to module names defining the types of the fields). The MR does not actually exist but is an imaginary component.

The OC and ST are directly dependent upon the MI since they are internal forms of the MI. The EM is dependent upon the OC by pointer dependence, since it contains offsets into the OC, and upon the ED by form dependence since its form is defined by the form of the ED. The UM is dependent upon the IL by form dependence and upon the EMs of other modules by information dependence. The OC is dependent upon the ED, RD, MD, IL and EDs of other modules by information dependence since information from these components is implicitly encoded in the OC. The ST is dependent upon the MD by pointer dependence since it contains indices into the MD.

## 3.2.1.3 SEPARATE PROCEDURES

The module concept provides data type abstraction; however, this is probably not sufficient for program

development [14]. Additionally a functional abstraction is

needed. Functional abstraction is represented in DEMOS by

procedures within a module. In order that development of a

functional abstraction may proceed separately from that of

the rest of the module, DEMOS provides for, a special type of

procedure, termed a separate procedure.

A separate procedure is no different functionally from any other procedure. Its difference lies in the manner in

which consistency checking is done. A separate procedure is consistency checked at a time potentially different from that of the rest of the procedures in the module.

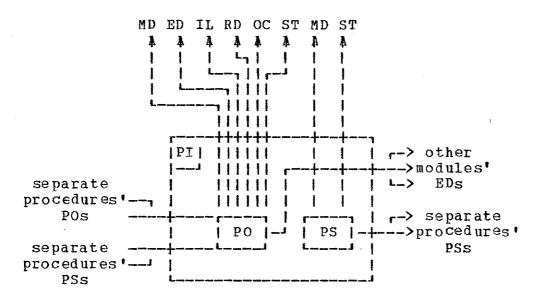

maintained as a separate entity within the module representation. Since its environ is like that of any other procedure within the same module, it is essentially another part of the implementation part of the module. The separate procedure is represented by a component called the procedure implementation (PI). The procedure implementation is the source code of the procedure body. It makes reference to the MS, DS and US of the abstraction part of this module, the MR and MI of the realization of the module and the DSs of modules supplying resources used by this procedure. A separate procedure is represented as shown in figure 3.2.1.3.a.

fig. 3.2.1.3.a Separate Procedure Components

It should be noted that the procedure header (declaration) resides in the MI and not in the PI, that is, the procedure is declared in the MI and implemented in the PI. This is to enable references to the separate procedure by the MI to be consistency checked without being forced to compile the PI.

As expected, an internal form of the PI is maintained by DEMOS. This is similar to that of the MI and consists of two components, the procedure object code (PO) and the procedure symbol table (PS), which are organized in the same manner as their corresponding components in the implementation.

A functional abstraction may be made at any level, and, in fact, may be made from a separate procedure. In this case one separate procedure may be dependent upon another, higher level separate procedure in which its procedure header resides. Of course it is also dependent upon all separate procedures upon which its encompassing separate procedure depends as well as upon the MI.

The entry point of a defined resource must reside in the OC of the module and thus a separate prodecure may not implement a defined resource directly. This is due to the fact that the entries in the UM of a module using the

resource are assumed to point into the OC of the defining module and this would not be true for a separate procedure. This does not pose any restriction since a defined resource could be implemented by a dummy procedure in the MI which simply invokes the separate procedure.

fig. 3.2.1.3.b Separate Procedure Representation

The final form of a separate procedure is shown in figure 3.2.1.3.b. Here the PO and PS are directly dependent upon the PI. The PO is dependent upon the MD, ED, IL, RD, OC and ST of the module, POs and PIs of other separate procedures in which it is imbedded within the module, and EDs of modules which supply resources utilized by this separate procedure, since the PO contains information from these

sources encoded within it. Since the PS contains indices into the MD and ST of the module and PSs of separate procedures in which this one is imbedded, the PS is pointer dependent upon these components.

## 3.2.1.4 MODULE INSTANCES

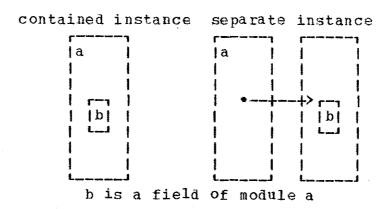

A module instance is one instantiation of the abstract type defined by a module. It thus incorporates the definition of the module as well as a data area in which the values of the fields of this instance are retained. Thus a module instance could be represented by a copy of the components that represent the module with the addition of a data area unique to this instance.

This representation would be inefficient, however, since it implies duplication of the components common to all instances of the same module. In addition, whenever a change is made to the module, all instances would have to be updated to reflect this change. A far more efficient representation is realized if only one copy of the module is maintained and each module instance is represented by only a data area which contains values unique to this instance.

Within DEMOS a module instance is represented by a data area (section 4.1.1). This data area (DA) is defined by the

MODULE INSTANCES 48

representation of the module (i.e. the MR) and is thus dependent upon the RD by form dependence (i.e. the RD defines the form of the DA). A data area is solely dependent upon the RD (see figure 3.2.1.4.a) which means that only a change to the MR will make a data area inconsistent.

fig. 3.2.1.4.a Data Area Representation

### 3.2.2 COMPONENT DEPENDENCIES

The components (figure 3.2.2.a) which make up the module representation discussed in section 3.2.1 have dependencies between them which arise from the inherent dependence of the abstract types upon other abstract types in terms of which the first are defined; the dependence of the realization of the abstract type upon the abstraction which defines the abstract type; and finally the desire to improve efficiency by maintaining internal forms of some module components. These dependencies indicate the components whose modification would require the reverification of consistency of a component.

| _ |         |                           |           |      |

|---|---------|---------------------------|-----------|------|

| 1 | ACRONYM | COMPONENT                 | SECTION   | TYPE |

|   | MS      | Module Specification      | 3.2.1.1   | ()   |

| 1 | DS      | Defines Specification     | 3.2.1.1   |      |

| 1 | បទ      | Uses Specification        | 3.2.1.1   |      |

| 1 | MD      | Module Definition         | 3.2.1.1   | -    |

| l | ED      | Export Definition         | 3.2.1.1   |      |

| 1 | IL      | Import List               | 3.2.1.1   |      |

| 1 | MR      | Module Representation     | 3.2.1.2   |      |

| 1 | MI      | Module Implementation     | 3.2.1.2   | -    |

| 1 | RD      | Representation Dictionary | 3.2.1.2   |      |

| 1 | EM      | Entry Map                 | 3.2.1.2   |      |

|   | OC      | Object Code               | 3.2.1.2   |      |

| 1 | ST      | Symbol Table              | 3.2.1.2   |      |

| 1 | UM      | Use Map                   | 3.2.1.2   |      |

| 1 | PΙ      | Procedure Implementation  | 3.2.1.3 j |      |

| ı | PO      | Procedure Object          | 3.2.1.3   |      |

| 1 | PS      | Procedure Source          | 3.2.1.3   |      |

| 1 | DA      | Data Area                 | 3.2.1.4   | S    |

TYPE: U - User component S - System component

fig. 3.2.2.a Module Component Summary

In any system under development, the number of modifications to components would be large and thus DEMOS will spend a large portion of its time performing consistency checks. It is important to minimize the number of components that must be interrogated to determine if a component need be consistency checked. To this end, the number of dependence relationships maintained in DEMOS is reduced to the minimum number needed to maintain complete consistency.

The first method used to reduce the number of dependencies that need to be maintained is due to noting that if there is a sequence of dependencies A->B->C and an additional dependence A->C, the dependence of A on C is not required since the discovery of C's modification will cause B to be consistency checked (modifying B) and this modification will lead to the consistency checking of A. This removes the need for the maintenance of the dependencies of: the EM upon the ED; the OC upon the MD and the EDs of other modules; the PO on the MD, ED, EDs of other modules, IL, RD and, if the separate procedure is local to another separate procedure, the OC, ST and POs and PSs of separate procedures other than that in which it is imbedded.

A second set of dependencies can be removed by noting that whenever the OC is regenerated (by recompiling the MI), the ST is recreated and vice versa. This implies that any dependencies that the ST has in common with the OC are not needed since the consistency checking of the ST will occur at the same time as that of the OC anyway. This removes the dependence of the ST upon the MD. The same argument works for the PS and the PO of separate procedures, removing the need for the dependence of the PS on the MD, ST and PSs of other separate procedures.

The dependence of the POs of separate procedures local to the module upon the ST can be removed by noting that,

since the OC and ST are modified at the same time, if the ST is modified, the consistency check indicated by the PO->ST dependence will be forced by the PO->OC dependence. The same is true for the dependence of the PO of a separate procedure local to another separate procedure upon the PS of that procedure.

Lastly, the dependence of the EM upon the OC can be removed since, by necessity, the EM must be recreated at the same time as the OC since that is the only time that the information necessary to create the EM is available.

This leaves the dependency relationships shown in figure 3.2.2.b to be maintained by the system. The direct dependencies are not shown by arrows but by the inclusion of a component in the same box as the component it is directly dependent upon.

# 3.3 CONSISTENCY OF MODULE COMPONENTS

## 3.3.1 CONSISTENCY AND COMPILATION

The three areas of consistency mentioned in section 2.2 must be verified for all modules within the system to be

fig. 3.2.2.b Component Dependencies Maintained by DEMOS

certain that the system will function correctly. of these areas is completeness of the abstractions; that is, when an abstraction states that the module uses a resource provided by a second module, that second module exists provides the named resource, and secondly, that all external resources used by a realization are stated in the abstrac-The second area is consistency of utilization and provision of resources by the realizations; that is, that all resources declared as provided by the abstraction are realized in the realization consistent with their definition in the abstraction, and secondly, that the usage of external the realization is consistent resources by with resources' definitions in the abstractions of the modules which provide the resources. The last area is consistency of the behaviour of the resources provided by the module with the definition of that behaviour in the abstraction.

A compiler is capable of verifying the consistency of the first two areas listed above if it has access to the MS, US, DS, MR, MI and PIs of all modules concerned. At the current time, compilers are not able to perform the consistency check upon the third area, which amounts to automatic program proving, but progress is being made in that area [11].

With the introduction of system maintained components into the module representation, a new type of consistency must be maintained. This is consistency of the information encoded in these components (the MD, ED, IL, RD, EM, OC, ST, UM, PO and PS) with the sources of that information. This differs from consistency in the user created components (i.e. the MS, US, DS, MR, MI and PI) in that inconsistency of system components implies that they were created from obsolete versions of user components while inconsistency of user components indicates a flaw in the design or implementation of one or more modules.

The system components can all be generated by a suitable compiler using the user components as sources. This compilation and generation process does consistency checking of the source (user) components as well as creating new, consistent system components. Since the system maintains internal forms of user entered components, the compiler need not use the user components as sources at all times but may use the internal forms of them as long as they are consistent with their external forms. This reduces the time required to generate new, consistent system components when old ones are inconsistent.

Since it is desirable to reduce the number (and duration) of the compilations needed to maintain and verify consistency, the compiler is broken into parts capable of compiling single user components using system components as additional sources. This allows regeneration of an inconsistent system component without recompiling all other module components.

There is effectively a "compiler" for each type of user component, that is, an MS compiler, a US compiler, a DS compiler, an MR compiler and an MI compiler. Since the PI is similar to the MI the same compiler can be used for the PI as the MI. Since the MS, US, DS and MR are not maintained concretely within the system, their compilers are really just table lookup and update routines invoked directly when the user wishes to modify one of these components. The MI compiler is the only real compiler within the system.

### 3.3.2 CONSISTENCY AND MODIFICATION

Whenever a component is modified, a check must be made to see if this component and all components dependent upon it are still consistent within the system. If there is an inconsistency, some action must be taken to reconcile it. The dependencies recognized by DEMOS are those discussed in Section 3.2.2. The maintenance of consistency of components related by these dependencies is sufficient to ensure consistency of all modules within the system. All the dependencies maintained are of system components upon either the user component of which they are an internal form or upon other system components. A system component is inconsistent whenever any component upon which it depends is modified. To restore the consistency, the system component is regenerated by "compilation" of the user component of which it is the internal form.

This compilation can result in a new, consistent version of the system component or will fail indicating that there is an inconsistency between two or more user components one of which is the one being recompiled, and the others being some of the indirect sources for the compilation.

Whenever a system component is discovered to be inconsistent, an attempt is made to regenerate the component. This attempt may either successfully complete yielding a consistent component, or fail indicating an inconsistency between user components. This second case requires intervention by a user to reconcile the inconsistency before a consistent system component can be generated.

Some components do not fit this scheme. The EM, ST and PS have no dependencies but are regenerated in consistent form as a byproduct of the regeneration of the OC and PO. The UM has no user component upon which it is dependent. When the UM is found inconsistent, it is regenerated by a special routine which accesses the IL and EMs of other modules. Regeneration of the UM cannot fail if the IL and the EMs are consistent and thus cannot indicate any inherent inconsistency betweem user components.

The inconsistency of the DA with the MR is an unreconcilable inconsistency since it implies that the DA no longer has the form defined by the MR and thus the data within it is incomprehensible. Recreation of a consistent DA would have to be done by a user by reinvoking the operations which created the DA using the new module representation and the old data.

When the MD is discovered inconsistent within the system, its regeneration will either be successful, indicating the MS is consistent, or will fail, indicating an incompleteness of the abstractions since the MS references a module which does not exist within its environ.

When the ED is discovered inconsistent with the MD, its regeneration is either successful, indicating the DS is con-

sistent with the MS, or will fail, indicating the DS refers to some module not listed in the MS.

When the IL is discovered inconsistent with the MD or EDs of other modules, its regeneration is either successful or fails, indicating either an inconsistency between the US and MS (i.e. the US refers to a module not listed in the MS) or an inconsistency between the IL and the DS of some other module (i.e. an incompleteness of abstraction since the IL refers to a resource not provided by the module named).

When the RD is discovered inconsistent with the MD, its regeneration is either successful or fails, indicating an inconsistency between the MR and the MS (i.e. that the MR refers to a module not listed in the MS).

When the OC is discovered inconsistent with either the ED, RD, or IL, its regeneration is either successful, in which case new, consistent versions of the EM and ST will also be produced; or will fail, indicating an inconsistency between the MI and the MS, DS, MR, US and/or the DSs of other modules. These inconsistencies are inconsistencies of the realization of a module with the abstractions defining the module or those defining modules utilized by this one.

When the UM is discovered inconsistent with the IL or the EMs of other modules, its regeneration is always successful since its regeneration simply involves copying of information from the EMs in the order defined by the IL.

When the PO is found inconsistent with the OC or the PO of another separate procedure, its regeneration will either be successful, in which case a new, consistent version of the PS will also be generated, or will fail, indicating an inconsistency between the PI and the MS, DS, US, MR, MI, PO of another separate procedure and/or the DSs of other modules.

The regeneration of system components found inconsistent due to modification of a component upon which DEMOS knows the component is dependent, results in consistency checking of the user components in the two areas discussed in section 3.3.1 and thus verification of consistency of the modules in the system.

### 3.3.3 COMPILATION FOR CONSISTENCY CHECKING

The timing of the compilations to perform consistency checking is important. Along with the desire to report a user component's inconsistency as soon as possible, there is the requirement of informing the correct user, that is, the

user with the knowledge and responsibility to reconcile the inconsistency. Also, since compilation requires time and will cause a real-time delay to the user who must wait for it to be done, it is important to cause the appropriate user this delay. The solution derives from dividing the dependencies into two categories and performing the requisite consistency checks for these two categories at different times.

## 3.3.3.1 CATEGORIES OF DEPENDENCE

The scheme used is based upon the assumption that different groups of people develop different modules and that within one group, two subgroups exist, one developing the abstraction and one the realization. Under this assumption, a change to an abstraction should cause reporting to the changer of any inconsistencies the change causes within the abstraction or between it and the abstractions of modules upon which this one depends. Likewise a change to the realization should cause reporting to the changer of any inconsistencies within the realization or between the realization and the abstraction it implements.

Two sets of inconsistencies are not covered by this.

These are the inconsistency of the realization with the

abstraction defining it after a change to the abstraction, and the inconsistency of an abstraction with the abstraction of a module it is dependent upon when the providing module's abstraction is modified. In both of these cases, the person making the change has neither the responsibility nor the expertise to understand messages concerning the inconsistency nor make the modifications required to reconcile them.