# High Level Design and Test Methodologies with VHDL

by

Ruomei Wang

A Thesis

Submitted to the Faculty of Graduate Studies

in Partial Fulfilment of the Requirements

for the Degree of

Master of Science

Department of Electrical and Computer Engineering University of Manitoba Winnipeg, Manitoba

© 1996 Ruomei Wang

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence exclusive irrévocable et non Bibliothèque permettant à la nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette disposition la personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-16366-0

# THE UNIVERSITY OF MANITOBA FACULTY OF GRADUATE STUDIES COPYRIGHT PERMISSION

HIGH LEVEL DESIGN AND TEST METHODOLOGIES WITH VHDL

BY

#### RUOMEI WANG

A Thesis/Practicum submitted to the Faculty of Graduate Studies of the University of Manitoba in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

Ruomei Wang

© 1996

Permission has been granted to the LIBRARY OF THE UNIVERSITY OF MANITOBA to lend or sell copies of this thesis/practicum, to the NATIONAL LIBRARY OF CANADA to microfilm this thesis/practicum and to lend or sell copies of the film, and to UNIVERSITY MICROFILMS INC. to publish an abstract of this thesis/practicum..

This reproduction or copy of this thesis has been made available by authority of the copyright owner solely for the purpose of private study and research, and may only be reproduced and copied as permitted by copyright laws or with express written authorization from the copyright owner.

I hereby declare that I am the sole author of this thesis.

I authorize the University of Manitoba to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the University of Manitoba to reproduce this thesis by photocopying or other means, in whole or in part, at the request of other institutions or individuals for the purpose of scholarly research.

# **ABSTRACT**

The growing complexity and density of integrated circuits requires that good design and test methodologies be utilized throughout the design process. This thesis presents high level design methodologies typically involved in the design process, from behavioral to gate-level structural descriptions. Test and design for testability techniques are reviewed, and experience with the Synopsys test synthesis tools is presented. The diverse styles and advantages of testbenches are also discussed. A novel approach for doing testbench simulation on RTL level and gate-level circuits and comparison of the outputs from both versions of the design is demonstrated. As a real design, an elevator controller is developed utilizing these methodologies, and the simulation results are presented. The Synopsys CAD tools are involved in each design and test stage, which greatly relieves the designer from tedious and error prone tasks.

# **ACKNOWLEDGEMENTS**

I would like to express my sincere thanks and appreciation to my supervisor, Dr. Robert McLeod for his intellectual advice throughout my study at the University of Manitoba. Even though he is very busy at the University and TRLabs, he still made time to support and guide my study. I would also like to thank some other students in the VLSI group, Guy Jonatschick and Budi Rahardjo for their helpful discussions and suggestions. Special thanks go to Ken Ferens for his invaluable assistance. Also, Kevin Zong's encouragement is gratefully acknowledged.

Heartfelt appreciation goes to my parents. Even though they are very far away from me, their understanding and love made me overcome all the difficulties.

CMC and Micronet who provided financial support are highly appreciated.

# TABLE OF CONTENTS

| Chapter 1 Introduction                                 | 1  |

|--------------------------------------------------------|----|

| Motivation                                             |    |

| Levels of Abstraction                                  |    |

| Introduction to High Level Design Flow                 |    |

| Introduction to HDL Testbenches and Their Applications |    |

| Organization of the Thesis                             |    |

| Organization of the friends                            | .0 |

| Chapter 2 Test and Design-for-Testability Overview     | 7  |

| Introduction                                           | .7 |

| Testing Overview                                       |    |

| Design-for-Testability (DFT)                           |    |

| Scan Design Methodology                                |    |

| Internal Scan (Scan Design)                            |    |

| Full Scan and Partial Scan                             |    |

| Boundary Scan                                          |    |

| Design Flow Using Synopsys Test Synthesis Tools        |    |

| Test Synthesis                                         |    |

| Design Flow Using Synopsys Test Compiler Tool          |    |

| Experience With Synopsys Test Synthesis tools          |    |

| Utilizing ATPG Test Vectors                            |    |

| IC Testing Using VXI and IC Test Head                  |    |

| Summary                                                |    |

| Summary                                                | •  |

| Chapter 3 High Level Design Methodologies              | 9  |

| Introduction                                           |    |

| High Level Design Process                              |    |

| The VHDL Hardware Description Language                 |    |

| Functional Partitioning                                |    |

| Design Entry Schematic and VHDL                        |    |

|                                                        | •  |

| From Behavioral Description to RTL Code                           | 35    |

|-------------------------------------------------------------------|-------|

| From RTL Level to Gate Level                                      |       |

| Summary                                                           |       |

|                                                                   |       |

| Chapter 4 Testbench Generation and Application Methodologies      | 43    |

| Introduction                                                      |       |

| VHDL Testbench                                                    |       |

| Testbench Styles and Coding Strategies                            | 46    |

| Ad-Hoc                                                            | 46    |

| Algorithmic                                                       | 47    |

| Vector Files                                                      | 48    |

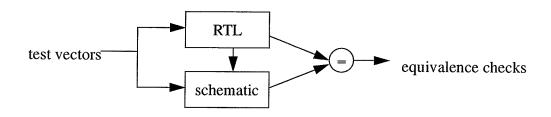

| Testbench For RTL and Schematic Model Equivalence Checking        | 51    |

| Testbench For Mixed Level Simulation                              |       |

| Simulation With Back-annotation                                   |       |

| Behavioral Test Pattern Generation Algorithms Survey              |       |

| Simulation Results and Discussions                                |       |

| Summary                                                           | 65    |

|                                                                   |       |

| Chapter 5 Conclusions and Future Work                             | 67    |

| Summary and Conclusions                                           | 67    |

| Future Work                                                       | 69    |

|                                                                   |       |

| APPENDIX A Design Example 1: Elevator Controller                  | 70    |

| Functional Specifications and Assumptions                         | 70    |

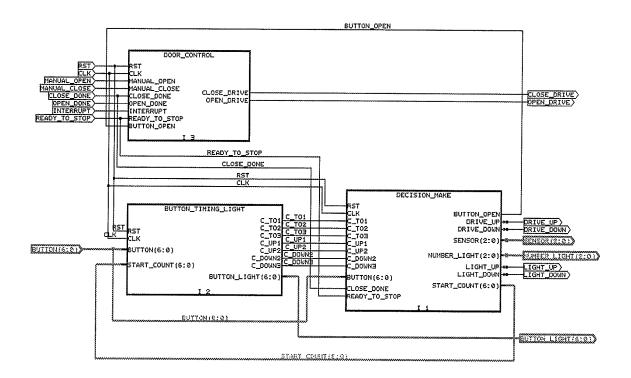

| Schematic Diagram                                                 |       |

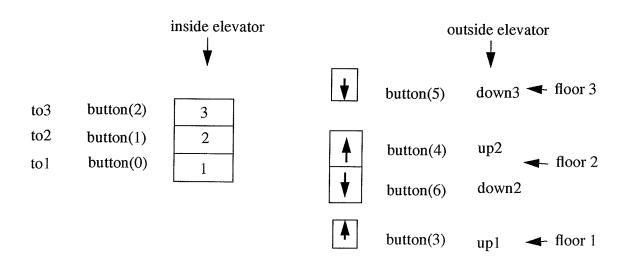

| Signal Names and Assignments                                      | 71    |

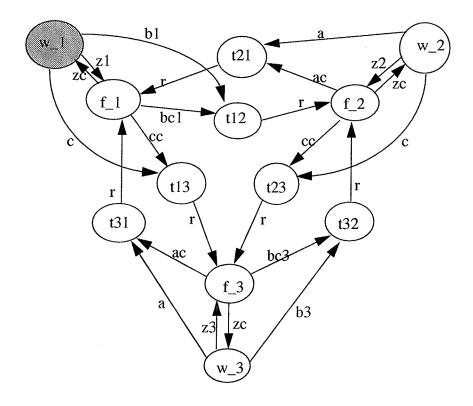

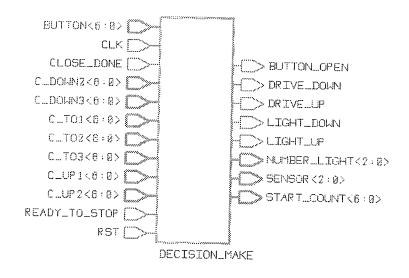

| Finite State Machine for Module decision_make                     | 73    |

| VHDL Template Generated by SGE                                    | 76    |

| Behavioral VHDL Source Code for Subdesigns                        |       |

| Synthesized Schematic of Module decision_make                     | 93    |

| ADDEADLY D. D. C. C. C. ALLIE                                     | 24 04 |

| <b>APPENDIX B</b> Design Example 2: ALU Function generator DM7418 |       |

| Behavioral Description                                            | 94    |

| Source Code for ALU                                               |       |

| Functional Testbench for ALU                                      |       |

| Simulation Results                                                | 100   |

| ATPG Results by Test Compiler                                     | 100   |

| BIBILIOGRAPHY                                                     | 103   |

# LIST OF FIGURES

| Fig. 1.1:The Y-chart                                                                       |

|--------------------------------------------------------------------------------------------|

| Fig. 1.2: High Level Design Flow                                                           |

| Fig. 1.3: HDL testbench and its applications                                               |

| Fig. 2.1: Design Before and After Adding Scan Circuitry                                    |

| Fig. 2.2: Full Scan and Partial Scan Symbolic Representation                               |

| Fig. 2.3: Full, Partial, and Non-Scan Trade-offs                                           |

| Fig. 2.4: Boundary Scan                                                                    |

| Fig. 2.5: Module and Chip Level Testability Analysis and Design                            |

| Fig. 2.6: Board Level Testability Design                                                   |

| Fig. 2.7: Fault Simulation Strategies                                                      |

| Fig. 2.8: Multi-style, Multi-pass Capability                                               |

| Fig. 2.9: ATPG Vectors Simulation in RTL Level                                             |

| Fig. 2.10: Two-inputs And Gate with Registered Output (circuit ANDGATE)23                  |

| Fig. 2.11: VHDL Code for the Register (1) Before and (2) After Test Structure Insertion 24 |

| Fig. 2.12: ATPG Vectors Simulation Results                                                 |

| Fig. 2.13: Signal Routing and Distribution                                                 |

| Fig. 3.1: High Level Design Flow                                                           |

| Fig. 3.2: Elevator Controller and its Submodules                                           |

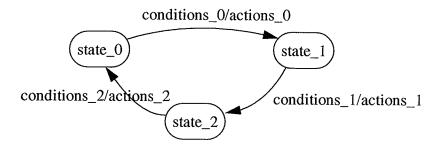

| Fig. 3.3: Mealy State Transition Diagram                                                   |

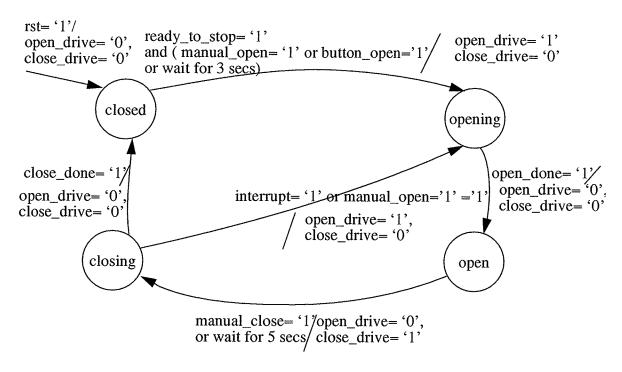

| Fig. 3.4: State Machine for <i>door_control</i> Module                                     |

| Fig. 3.5: Typical VHDL Coding for State Machine                                            |

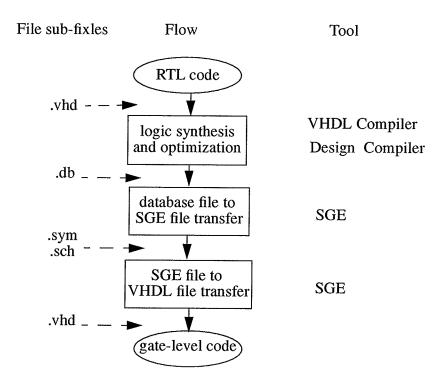

| Fig. 3.6: From RTL Level to Gate-Level                                     |

|----------------------------------------------------------------------------|

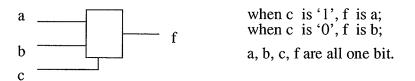

| Fig. 3.7: Multiplexer                                                      |

| Fig. 3.8: RTL Level VHDL Description for Multiplexer                       |

| Fig. 3.9: Gate-level VHDL Description for Multiplexer                      |

| Fig. 4.1: Structure of a testbench                                         |

| Fig. 4.2: Testbench Structural Contents                                    |

| Fig. 4.3: Ad-hoc Style and Simulation Results                              |

| Fig. 4.4: Algorithmic Style for ALU Testbench                              |

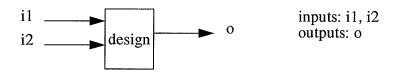

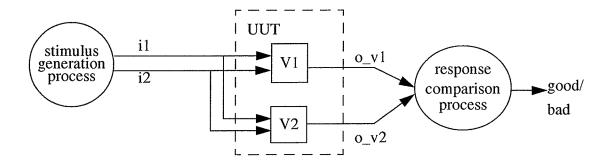

| Fig. 4.5: Example: <i>and</i> _2                                           |

| Fig. 4.6: Testbench Fetch Test Vectors From Data File and Data File50      |

| Fig. 4.7: Simulation Result for Circuit and 2                              |

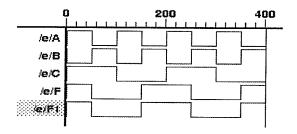

| Fig. 4.8: Clock Generation Process                                         |

| Fig. 4.9: Equivalence Checking for RTL and Schematic Model                 |

| Fig. 4.10: Design Example                                                  |

| Fig. 4.11: RTL Version (V1) for the Design                                 |

| Fig. 4.12: Schematic Version (V2) for the Design                           |

| Fig. 4.13: Design in two versions V1 and V254                              |

| Fig. 4.14: VHDL Model for UUT54                                            |

| Fig. 4.15: Testbench Simulation on UUT55                                   |

| Fig. 4.16: Testbench Simulation on RTL and Gate-level Equivalence Checking |

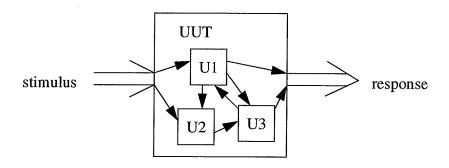

| Fig. 4.17: UUT (TOP) and its Components                                    |

| Fig. 4.18: Configuration Statement for TOP Design                          |

| Fig. 4.19: Configuration Statement for Testbench                           |

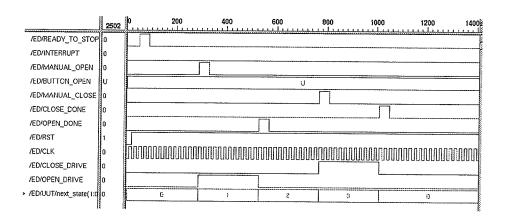

| Fig. 4.20: Simulation Results for <i>door_control</i> Module               |

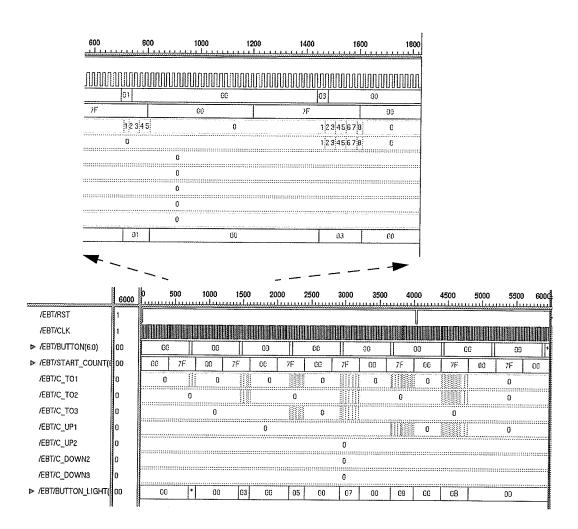

| Fig. 4.21: Simulation Results for button_timing_light Module               |

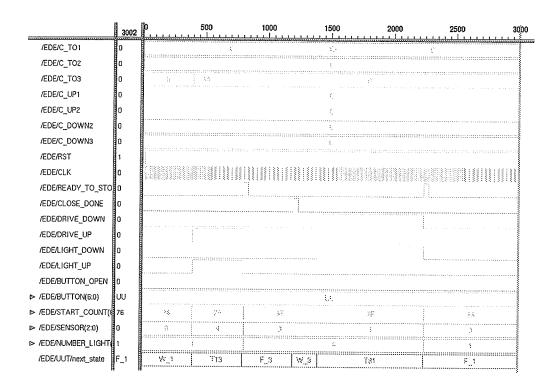

| Fig. 4.22: Simulation Results for <i>decision_make</i> Module              |

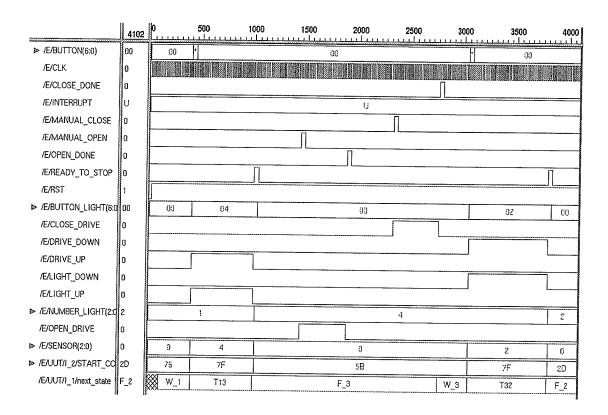

| Fig. 4.23 : Simulation Results for <i>Elevator Contoller Top</i> Module    |

| Fig. A.1 Button Signal Name Assignment71                                   |

| Fig. A.2 Schematic Entry Block Diagram for elevator_controller             |

| Fig. B.1 Simulation Results 100                                            |

# CHAPTER 1 INTRODUCTION

#### 1.1 Motivation

Conventional electronic design begins by manually entering the logic diagram, followed by timing verification at the gate-level. Only after this is done can comprehensive functional verification be performed. As a result, any functional specification errors or deficiencies will not be detected and corrected until a later stage in the design process. This means that any modification in the logic diagram requires long iteration loops. This iterative design process takes too long and results in low productivity. Because of the fast growth of VLSI designs, there is a need to improve designer's productivity and shorten time-to-market.

High level top-down design can significantly increase the designer's productivity. High level design flow methodologies are currently an active area of research. CAD and CASE tools play important roles in the design flow: synthesizing behavioral code to gate-level implementations, high-level simulation, gate-level simulation, insertion of scan chains, generation of test patterns, and board-level simulation. Automation of these tasks saves designer's time and energy. CAD and CASE tools continuously need to be improved to meet the increasing demands of IC designers.

According to many designers' experience, the majority of time in designing a system is spent on capturing and verifying the functional design. CAD tools can carry out most of the remaining tasks. Thus the design methodology focuses on capturing and verifying the design. Time is spent on writing behavioral code and a good testbench, modifying the behavioral code, until the behavior is satisfactory. As a result, verification at a high level has significant meaning. Functional testbench generation and application methodologies need to be developed for high level verification.

#### 1.2 Levels of Abstraction

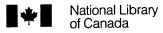

Any complex system may be broken down into gates and memory elements by successively subdividing the system in a hierarchical manner. This subdivision may be done manually or by automated techniques. To do this, integrated circuits may be described at different abstraction levels. There are three design domains that represent a system: behavioral, structural, and physical domains. Behavioral representation specifies what a system does, the structural domain specifies how entities are connected together, and the physical domain binds the system in space or to silicon. Each design domain may be specified at a variety of abstraction levels. From highest to lowest, these include: system, RTL (Register-Transfer-Level), logic and circuit level. The Y-chart [20] of Figure 1.1 illustrates the tripartite representation of design.

#### **Design Strategies**

A good VLSI design system should be capable of providing consistent descriptions in all three domains and at all abstraction levels. The design parameters may be described in terms of performance, size of die, time to design, ease of test generation and testability. The design process involves trade-offs to achieve good results for all of the parameters. There are some

classical approaches to reducing the complexity of IC design including: hierarchy, regularity, modularity, and locality.

Fig. 1.1: The Y-chart

### 1.3 Introduction to High Level Design Flow

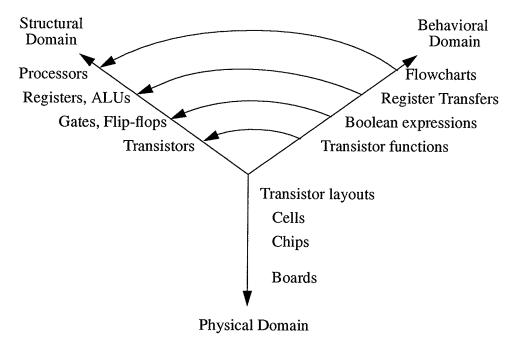

Figure 1.2 shows a high level design methodology [28]. In the Design Entry stage, design description consists of schematic diagrams and Register-Transfer-Level HDL code (such as Verilog or VHDL) which define the behavior of the designs. The validation phase is used for simulating the source code and making sure the RTL code behaves in the way it is intended to. This phase involves interactive simulation and source code debugging. The next phase is implementation where logic and test synthesis tools are used to translate RTL code to a gate-level schematic (or netlist). Test synthesis performs scan insertion in addition to logic synthesis. In the verification phase, the HDL testbench is designed for testing against the RTL description, and also against the gate-level implementation. The HDL testbench and test vectors are used to automatically exercise the circuit during simulation. In this phase, a wide

Fig. 1.2: High Level Design Flow

tural and behavioral alternatives can be explored, and the best trade-offs among speed, size, and testability are chosen. If there are malfunctions or errors detected in the verification phase, the design is returned to the design entry phase, with subsequent modification of the code or gate-level structure. The Synopsys tools help in each phase and are indicated in the design flow of Figure 1.2. *VSS* is the VHDL System Simulator, *DC* is the Design Compiler, *SGE* is the Synopsys Graphical Environment, and *TC* is the Test Compiler.

## 1.4 Introduction to HDL Testbenches and Their Applications

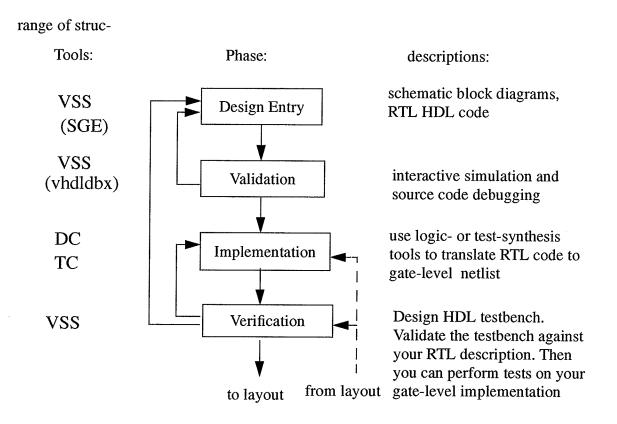

This thesis proposed a complete scheme for HDL testbench methodologies. The scheme is shown in Figure 1.3.

HDL testbenches basically divide into two types: structural and behavioral testbenches.

A structural testbench is generated by an ATPG (Automatic Test Pattern Generator) using DFT (Design-for-Testability) techniques developed from the structural model (gate-level schematic or netlist). This is simulated on the gate-level design, detecting gate-level faults, and generating a fault coverage report. This work can be done using CAD tools such as the Synopsys Test Compiler and TestSim. A complete set of test vectors is generated by the Synopsys Test Compiler. This set of test vectors can be simulated at the module, chip and system level.

Fig. 1.3: HDL Testbenches and Their Applications

A behavioral testbench is manually generated. It is developed from the behavioral model (RTL code, State Machine, BDD, Petri-Nets, etc.), and is used to verify the design's compliance to its functionality, i.e. to check its behavior. A behavioral testbench is also called a functional testbench. If there are Hard-To-Detect (HTD) faults in the gate-level design,

behavioral testbenches can help detect them. Both ATPG and functional test vectors are used for gate-level simulation (this is called a multi-pass, multi-style test process, which is a feature of the Synopsys test synthesis tools). In this way, higher fault coverage is achieved. Before doing test synthesis, a functional testbench (without scan) is written for the RTL HDL code to verify its functionality. It can also be used at the gate-level, which is one of the HDL testbench's advantages, mixed level simulation. Synopsys SGE can generate the functional HDL testbench template, while the user writes the behavioral part by hand.

#### 1.5 Organization of the Thesis

In Chapter 2, test and design for testability techniques are reviewed. Experiences using the Synopsys test synthesis tools are then presented.

Chapter 3 discusses all the methodologies involved in the entire high level design process, such as functional partitioning, schematic generation, VHDL design entry, synthesis and optimization.

In Chapter 4, functional testbench styles and generation methodologies are presented, and how such a testbench works on the RTL and gate level descriptions is demonstrated. A couple of behavioral test pattern generation algorithms are also given. Testbench simulation results for the elevator controller design are also demonstrated in this chapter.

Chapter 5 presents a summary and general conclusions, as well as future work.

Design schematics, behavioral descriptions, source code and experimental results using test synthesis tools are shown in APPENDIX A and APPENDIX B.

# **CHAPTER 2**

# TEST AND DESIGN FOR TESTABILITY OVERVIEW

#### 2.1 Introduction

The purpose of testing is to detect faults and locate the faults in the design. As such, testing is an important issue in VLSI design. In this chapter, some fundamental concepts in testing, such as ATPG, testability, DFT, and scan-based design will be presented. Testing techniques have been developed to greatly improve test efficiency and flexibility. These techniques will be discussed. The test synthesis approach is presented. The results for several examples using these test methodologies and CAD tools will be given. Experience with physical testing of a chip (DM74181) using the VXI bus test system and IC test head is also presented.

## 2.2 Testing Overview

#### **Tests**

Design quality implies three aspects: usability, reliability and efficiency [20]. Usability refers to the functionality of design and what it can do. Reliability means how long the design functionality can last and efficiency asks the question "Is it worthwhile using it?". There are always some faults that occur in a design, due to the VLSI processing, packaging and assembly, and/or specification ambiguity. Testing helps detect malfunctions and errors

in the system thus ensuring that it is fault free. Therefore, testing ensures a high quality design.

Tests may be divided into two categories: functional tests and manufacturing tests [20]. A functionality test verifies that the system performs as intended. It is used in the early design stages. In a high level design cycle, this is called validation. It proves that the design performs according to some specifications. The specification might be a verbal description, a plain-language textual specification, or a high-level computer language such as C, FORTRAN, VHDL, SDL, tables of inputs and required outputs, or high level languages such as statecharts. Functional test pattern generation methodologies are discussed in Chapter 4. In this chapter, test refers to manufacturing test.

A manufacturing test verifies internal gates, detects manufacturing defects which might come from fabrication or ware out. Normally, three kinds of fault models are defined: the stuck-at fault, stuck-open fault and line-delay fault. The stuck-at fault is the most common in industry and is the only gate-level fault model examined in this thesis.

#### **Testability**

The quality of testing is evaluated by testability. According to R.G. Bennetts [27], "Testability is the ability to generate, evaluate, and apply tests to satisfy a number of predefined test objectives (e.g. fault coverage, fault isolation, runtime, time-to-profit) subject to the two fundamental constraints of time and money".

There are two attributes used to evaluate testability. They are controllability and observability. Controllability is the ability to drive an internal node to a specified logic value by setting primary inputs to specific values. Observability is the ability to predict the response of an

internal node and propagate the response to primary outputs [28]. A design is testable when it can be put into a known initial state, and the internal nodes are controllable and observable.

#### 2.3 Design-for-Testability (DFT)

Traditionally, design and test were separate processes. In today's design flow, test and design are merged early in the design cycle. This approach improves controllability and observability. The incorporation of test hardware into a circuit design is called Design-for-Testability.

Generally speaking, there are two approaches to DFT: Ad-Hoc and Structured. Ad-Hoc DFT does not make big changes to the design. It includes: minimizing redundant logic, minimizing asynchronous logic, isolating clocks from the logic, and adding internal control and observation points. Structured DFT is a more systematic and automated approach to enhance design testability and thus is a more popular one. The purpose of structured DFT is to increase the controllability and observability of a circuit. There are various methods to reach this goal. Scan design is the most common method. It changes the internal sequential circuitry of the design. Another method is boundary scan which modifies the chip circuitry and increases board level testability. DFT techniques lower test cost, improve product quality, and reduce time-to-market.

# 2.4 Scan Design Methodology

There are two main types of scan circuitry: internal scan and boundary scan. Internal scan (also referred as scan design) can be full scan or partial scan. Internal scan modifies circuitry

within the original design itself and increases chip level testability. Boundary scan adds circuitry around the periphery of the design and increases board level testability.

#### 2.4.1 Internal Scan (Scan Design)

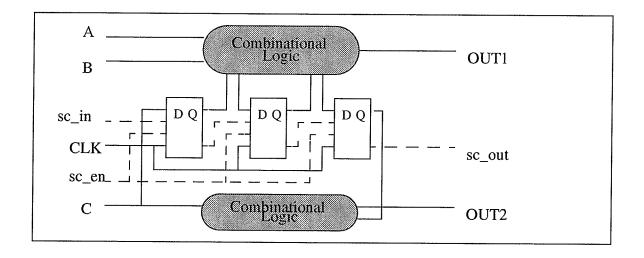

A sequential circuit is much more difficult to test, compared with a combinational circuit. Scan design makes a sequential circuit behave like a combinational circuit when the design is in test mode. To achieve this goal, sequential elements are replaced by scannable sequential cell (scan cells), then scan cells are stitches together into scan chains. These serially-connected scan cells can shift data in and out during the test process [28].

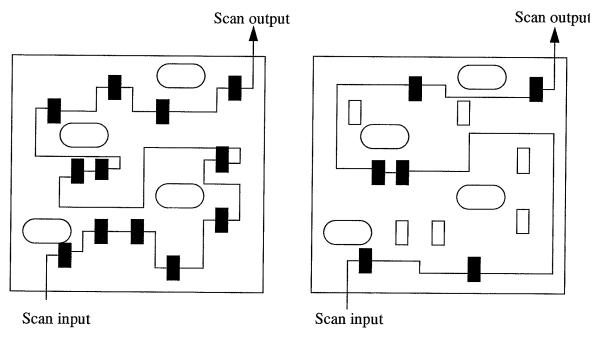

Scan design methodology is depicted in Figure 2.1. The original design contains combinational and sequential portions. Before scan circuitry is added, the design has three inputs: A, B, and C, and two outputs, OUT1, OUT2. This "before scan" circuit is difficult to test because it is hard to initialize the design to a known state. Thus it is difficult to control and observe its behavior by using the primary inputs and outputs. After adding scan circuitry (shown by -----lines), there are two additional inputs, sc\_in (scan input) and sc\_en (scan enable), and one additional output, sc\_out (scan output). The original sequential elements are replaced by scan elements, to allow data to be read in from sc\_in and shifted out to sc\_out when sc\_en line is enabled. The se\_out line from each flip-flop feeds into the next flip-flop's se\_in, and sc\_en is connected in parallel to each sequential element. This permits serial I/O to the scan elements which requires minimal pin out overhead.

#### 2.4.2 Full Scan and Partial Scan

In full scan design, all storage elements are replaced by their scannable equivalents and stitched into scan chains. Whereas in partial scan design, only the storage elements of interest are replaced by their scannable equivalents and stitched into scan chains [28].

Fig. 2.1: Design Before and After Adding Scan Circuitry

Figure 2.2 gives a symbolic representation of a full scan and partial scan design. The rounded boxes represent combinational portions. Rectangular boxes represent sequential elements and black rectangles are sequential cells that have been converted to scan cells. The line connecting them is the scan chain.

Fig. 2.2: Full Scan and Partial Scan Symbolic Representation

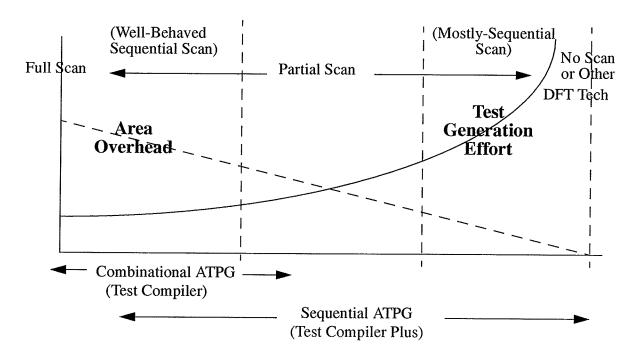

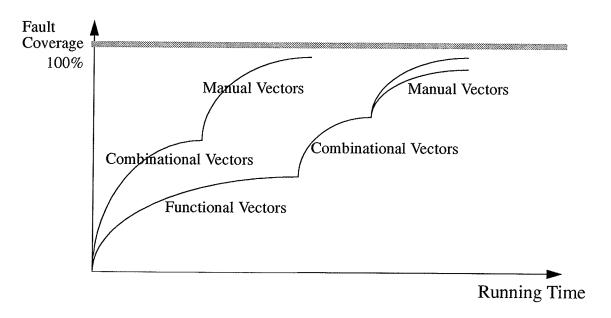

There are trade-offs among full scan, partial scan and non-scan designs as shown in Figure 2.3. Full scan requires a significant amount of area overhead because all the sequential cells are replaced by scannable cells. However it requires less test generation effort and since the scan insertion process is automated, it ensures high efficiency, high fault coverage and high quality. Partial scan is more flexible with respect to area overhead and fault coverage. Partial and non-scan designs require much less area overhead but far more test generation effort.

Full scan employs a combinational ATPG algorithm, while partial scan utilizes sequential ATPG. The Synopsys Test Compiler only has combinational ATPG algorithm, while Test Compiler Plus has both combinational and sequential ATPG algorithms [28].

Fig. 2.3: Full, Partial, and Non-Scan Trade-offs

There are some limitations to the scan design technique. For example, scan design techniques do not work well with certain circuit structures, including:

- Large, nonscan macro functions (e.g., microprocessor cores).

- Compiled cells (e.g., RAMs and ALUs).

- Analog circuitry.

#### 2.4.3 Boundary Scan

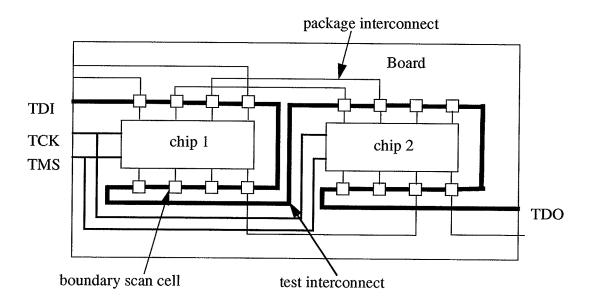

Boundary scan improves board level testing by providing an interface through which data can shift between circuits on the board, thereby, making each net on a board accessible. Boundary scan is also referred to as JTAG (Joint Test Action Group) and IEEE standard 1149.1 testing. Figure 2.4 shows how boundary scan works.

Fig. 2.4: Boundary Scan

The input and output ports of each chip are stitched together into a scan path [13]. The scan path begins at TDI (test data in) and ends at TDO (test data out). The TDO line of one chip is connected to TDI of the next chip. TCK (test clock) and TMS (test mode select) are inputs connected to every boundary scan device. The scan path connects all the boundary scan devices on the board. This configuration allows board interconnection test, snapshots of nor-

mal system data, and testing of individual chips.

The IEEE standard 1149.1 Boundary Scan interface consists of:

- TAP (Test Access Port): At least four signals TMS, TCK, TDI, TDO compose the test bus, TRST (asynchronous test reset signal) is optional.

- TAP Controller: Controls the operation of the instruction and test data registers.

- Instruction Register: At least two bits long, it decodes at least three instructions which

are BYPASS (allows testing a specific chip in the scan chain without shifting through

the SR stages in all chips), EXTEST (allows testing of off-chip circuitry), SAMPLE/

PRELOAD (places the boundary-scan register in the DR chain, and samples or preloads

the chip I/Os).

- Boundary Scan Register: A shift register consisting of the connection of boundary scan

cells that can parallel/serially load and unload the input and output data of the circuit.

- Bypass register: shortens the serial path between TDI and TDO when there is no requirement to test the current device. In this manner data bypasses the current chip and are shifted to other chips more directly.

- Test Data Register: includes the optional device identification register and data-specific registers.

# 2.5 Design Flow Using the Synopsys Test Synthesis Tools

#### 2.5.1 Test Synthesis

Test Synthesis is a technique which incorporates test and synthesis into one [14]. Traditionally, DFT circuitry is added manually after logic synthesis, however this is very time-consuming. Test synthesis approaches shorten design time and are therefore an increasingly

important part of circuit design.

There are two classes of test synthesis tools available: gate-level and RTL test synthesis. In gate-level test synthesis, the gate-level model is used to drive the test synthesis process. First, logic synthesis of RTL code is performed, then test circuitry is added and test vectors are generated for the synthesized model. In RTL synthesis, designers add the test circuitry in the RTL code, then conduct logic synthesis for this RTL code with the test circuitry. Gate-level test synthesis is more mature and more suitable for full scan design. The Synopsys Test Compiler family and Mentor Graphics FastScan use gate-level test synthesis techniques. RTL test synthesis is newer and more suitable for a boundary scan methodology.

#### 2.5.2 Design Flow Using the Synopsys Test Compiler Tool

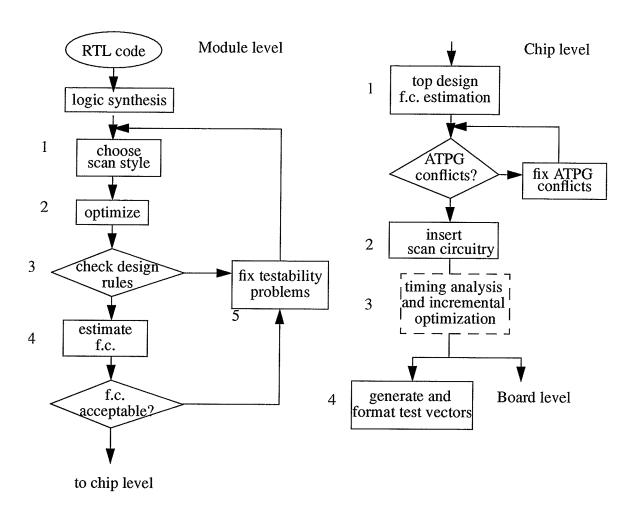

A typical DFT design flow using the Synopsys test compiler is described below. The features of the Test Compiler tools are also illustrated within the flow. The Test Compiler is used in three hierarchical stages: module level, chip level, and board level. A complex design is partitioned into subdesigns which are less complex, subdesigns are at the module level. At this level, scan compliance is analyzed, fault coverage is estimated and testability problems are identified and solved. These activities are called testability analysis. By doing testability analysis at the module level, problems are corrected early in the design cycle and time-to-market is shortened. At the chip level, testability analysis on the top level design is done as was done for the module level, this ensures all the test violations are solved, then the scan structure is inserted into the design. If boundary scan is not to be added to the design, final test vector sets are generated and formatted. However, if boundary scan is to be added, the process moves to the board level test process, in which JTAG is added, and the final test vectors are generated and formatted for a specific technology.

Referring to Figure 2.5, the methodology for using the Test Compiler on subdesigns is [29]:

- 1. Choose scan styles. If the design is purely combinational, define combinational as the scan style. If the design is sequential, select one of the styles the Test Compiler supports, which are Multi flip-flop, Clock Scan, LSSD and Auxiliary Clock LSSD. The Test Compiler requires that the same scan style be used on the entire chip.

- 2. Optimize the subdesign by using the Design Compiler.

- 3. Check design rules. For combinational designs, the Test Compiler checks combinational feedback loops. For sequential designs, it analyzes the design for compliance with the scan design rules associated with the selected scan style, and reports any violations.

- 4. Estimate fault coverage. Design rule violations cause significantly lower fault coverage. Statistical ATPG can quickly estimate the fault coverage.

- 5. Fix testability problems. If the fault coverage estimated is not acceptable, the designer needs to fix the testability problems which were detected in step 2. The best method is selected to fix the problem. The target for modification might be the RTL description or gate-level netlist. After the design modification, the cycle from step 1 to step 5 is repeated until an acceptable fault coverage result is achieved.

After module level testability analysis is done for all the subdesigns, the next step should be chip level testability design. The methodology using the Test Compiler at this level is:

- 1. The same testability analysis is done on the top design as it is done on module level, this ensures that all the violations have been identified and resolved. 100% fault coverage estimated on each module does not ensure 100% fault coverage at the chip level.

- 2. Insert scan circuitry. Although the scan logic is inserted at the top level, the Test Compiler can automatically insert the scan test structure through the whole hierarchy. Single or multiple scan chains, full or partial scan style can be chosen. The Test Compiler supports full scan design. The Test Compiler Plus supports partial scan design, by selecting a percentage of

sequential cells to scan according to performance, area, and testability constraints.

Fig. 2.5: Module and Chip Level Testability Analysis and Design

- 3. If necessary, perform timing analysis and incremental optimization.

- 4. Generate and format manufacturing test patterns. An ATPG is used to generate the final set of manufacturing test patterns which is targeted to a specific semiconductor vendor (for example, FPGA, BiCMOS, i.e.). After the generation, you can format the patterns to one of the following styles: Synopsys generic format, TDS ASCII format, WGL format, Verilog format, or VHDL format. If you want to do board level testability design, test patterns can be generated and formatted later.

Fig. 2.6: Board Level Testability Design

The fault coverage used by the Test Compiler is defined as follows. It is used to calculate both incremental and cumulative fault coverage [28].

A tied fault cannot be tested because it is connected to logic 1 (tied high) or logic 0 (tied low). A redundant fault cannot be tested because the overall static behavior of the circuit is independent of the values at this node. Test compiler and Test Compiler Plus use a combinational ATPG algorithm for full-Scan designs; Test Compiler Plus uses a Sequential ATPG algorithm for partial-scan designs. Combinational ATPG uses random and deterministic techniques to generate test patterns for stuck-at faults. Sequential ATPG uses deterministic techniques to generate patterns for stuck-at faults.

After the chip level testability design is completed, a core design is ready for board level boundary scan insertion. This is shown in Figure 2.6. The Test Compiler does not support boundary scan synthesis on designs without an I/O pad ring. It synthesizes the 1149.1 JTAG

logic around the core logic design. After the insertion, a boundary scan report is generated and testability is analyzed. Finally, test patterns are generated for the entire design with JTAG circuitry included. The Test Compiler does not generate test patterns to test boundary scan logic, so the fault coverage of this test set is low. When the fault coverage is checked, the fault coverage for the core design will be close to the fault coverage obtained for the chip level testability design before the JTAG was inserted.

After the DFT and ATPG is done for the design using the Test Compiler, fault simulation using TestSim may be performed. Preparation for the fault simulation includes generating a TestSim library, generating a TestSim model for the design, and starting the fault simulation. TestSim can simulate both the patterns generated by Test Compiler ATPG and functional vectors generated manually. TestSim fault simulates ATPG vectors either in serial mode (for multi flip-flop designs only), or in parallel mode. TestSim does not support fault simulation for LSSD designs. The fault coverage results reported by TestSim are greater than or equal to those reported by Test Compiler. This is because Test Compiler treats some cells as black boxes due to design rule violations, but these cells are not black boxes for TestSim. The functional vectors which TestSim can use must meet two requirements. One is that the vector file must be one of the formats accepted by TestSim which are TSSI TDS, ASCII, TSSI WGL, or WIF, the other is that the vectors must be cycle-based. A set of vectors is cycle-based when this sequence of events is of the same period (or cycle) throughout the vector set.

TestSim automatically disables the scan functionality at the start of the fault simulation, so the verification result of the pre-scan logic simulation can be used on the scannable design.

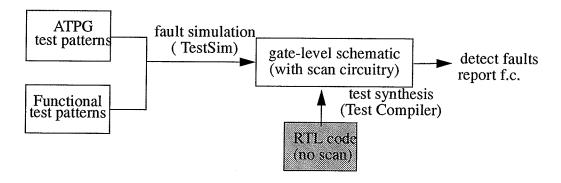

The Multi-Style, Multi-Pass capability of the Test Manager enhances fault coverage [28]. This is shown in Figure 2.8.

Fig. 2.7: Fault Simulation Strategies

Fig. 2.8: Multi-style, Multi-pass Capability

# 2.6 Experience With the Synopsys Test Synthesis Tools

## Testability Analysis and Design Results

Testability analysis and design results for five examples are reported here. A brief description and test results are given below. Time reported is on a SUN/SPARC5 with 64 MB of

memory. The designs are denoted *rom* (Read-Only-Memory), *tlc* (traffic light controller), *wfg* (waveform generator), *vend* (vending machine), and *counts* (count zeros circuit). Test synthesis was used both for combinational and sequential circuits, with a scannable cell number up to 49. Fault coverage of 100% is achieved for all of the circuits, with run time being very short. The number of scannable cells is the same as the number of clocks per pattern. The Synopsys test synthesis system has proven to be quite successful.

Table 1: Experiment results using the Synopsys Test Compiler

|        | # of faults<br>(non-collapsed) | # of faults<br>(collapsed) | cpu time<br>( sec) | f.c<br>(%) | # of test<br>patterns | # of compacted patterns | # of scannable squential cells |    |

|--------|--------------------------------|----------------------------|--------------------|------------|-----------------------|-------------------------|--------------------------------|----|

| rom    | 47                             | 27                         | 0.12               | 100        | 4                     | 4                       | 0                              |    |

| counts | 444                            | 267                        | 0.29               | 100        | 34                    | 29                      | 11                             | 11 |

| wfg    | 641                            | 375                        | 0.85               | 100        | 43                    | 35                      | 11                             | 12 |

| vend   | 388                            | 261                        | 0.29               | 100        | 26                    | 25                      | 3                              | 3  |

| tlc    | 2143                           | 2093                       | 3.12               | 100        | 90                    | 67                      | 49                             | 49 |

## 2.7 Utilizing ATPG Test Vectors

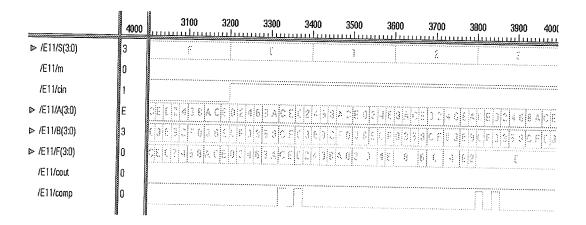

ATPG test patterns generated by the Synopsys Test Compiler are developed from the gate-level model. These are used for detecting stuck-at faults and reporting fault coverage results. In addition to this original purpose, the author developed two new methods to use this ATPG in which ATPG works as the normal functional VHDL testbench, simulating at the RTL and gate-level of the design. The simulation results are shown as waveforms for all the input and output signals, thus giving us a quick idea about how the signals look. If it is a sequential circuit, the signals also include the clock, test\_sc, test\_se and test\_so signals. All the incorrect responses can be detected and the error message will be shown on the screen. ATPG test

patterns used for this purpose must be formatted in VHDL.

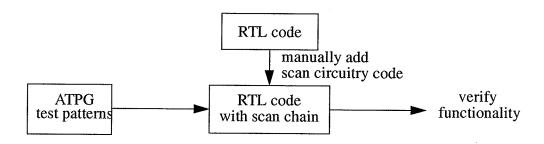

#### ATPG Test Vectors Simulated at the RTL Level

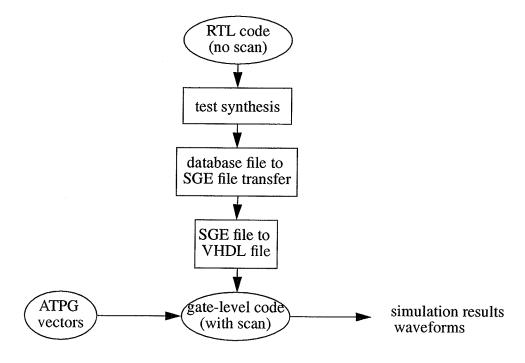

The first method developed for ATPG simulation at the RTL level is illustrated in Figure 2.9.

Fig. 2.9: ATPG Vectors Simulated at the RTL Level

Originally, in the ATPG testbench, the target model is the gate-level netlist synthesized and optimized from the RTL code, with scan circuitry inserted if it is a sequential circuit. But if add scan circuitry code into the original RTL code by hand, then replace the target model with this RTL code, and conduct simulation with the ATPG test patterns, the ATPG test patterns can be used as a functional testbench. Waveforms for the simulation results can be obtained and the functionality of the circuit can be verified. In this waveform representation, each input and output signal is clearly shown.

The VHDL configuration file feature enables the user to change the target model. For the original ATPG test patterns in VHDL format, its configuration file is as follows.

```

CONFIGURATION TOP_ctl OF TOP_tb IS

FOR testbench

FOR U0: TOP USE ENTITY WORK.TOP (SYN_SCHEMATIC);

END FOR:

END FOR;

END TOP_ctl;;

```

It can be changed into the one as follows:

```

CONFIGURATION TOP_ctl OF TOP_tb IS

FOR testbench

FOR U0: TOP USE ENTITY WORK.TOP ( SCHEMATIC );

END FOR:

END FOR;

END TOP_ctl;

```

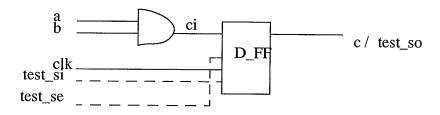

A simple example is used to present this methodology. The circuit ANDGATE is shown in Figure 2.10. After scan insertion, the circuit has three additional signals  $test\_si$ ,  $test\_se$ , and  $test\_so$ . As before,  $test\_si$  is the scan input signal,  $test\_se$  is the scan enable signal, and  $test\_so$  is the scan output signal.

Fig. 2.10: Two-input And Gate with Registered Output (circuit ANDGATE)

The code for the register part before and after scan structure insertion is as follows. When test\_se is active, the circuit is in test mode, it shifts test\_in to test\_out. When test\_se is inactive, the circuit works in normal mode.

```

entity REG is

entity REG is

port (CI: in std logic;

port (CI: in std_logic;

CLK: in std logic;

CLK: in std_logic;

C: out std_logic);

test_si: in std logic;

end REG;

test_se: in std logic;

test_so: out std_logic;

C: out std logic);

architecture BEHAVIORAL of REG is

end REG;

begin

process(clk)

architecture BEHAVIORAL of REG is

begin

begin

if (clk'event and clk='1') then

process(clk)

c \le ci;

begin

end if:

end process;

if (clk'event and clk='1') then

if (test_se='1') then

end BEHAVIORAL;

test_so<=test_si;

else

c \le ci;

end if;

end if:

end process;

(1)

end BEHAVIORAL;

(2)

```

Fig. 2.11: VHDL Code for the Register. (1) Before, and (2) After Test Structure Insertion

Similarly, for the top level code, signals test\_si and test\_se are added as inputs, and test\_so is added as an output in the entity port statement, and the same is done to the REG component port statement and the REG instantiation statement.

This technique is suitable for combinational circuits and simple sequential circuits. For combinational circuits, the designer only needs to modify the configuration file, and no scan insertion is needed. Manual scan structure insertion at the RTL level for complex sequential circuits may be complicated.

#### ATPG Test Vectors Simulated at the Gate-level

ATPG test vectors can also be used to stimulate the gate-level version of the design, For the sequential circuit, this gate-level version has scan circuitry added. Figure 2.12 shows how to get a gate-level VHDL description for the design. Test Synthesis transfers the RTL code to a Synopsys Database file, which is a gate-level netlist with scan circuitry inserted. The Synopsys SGE tool translates the database file into SGE graphics symbolic and schematic files. The Synopsys SGE tool then translates these graphics files into VHDL. Details about these processes will be discussed in Chapter 3. The gate-level VHDL description is the UUT (Unit Under Test) which will be instantiated in the ATPG testbench.

Modification of the configuration file should be done to make sure the UUT is a gate-level description. FOR U0: TOP USE ENTITY WORK. TOP (SYN\_SCHEMATIC) should be replaced by FOR U0: TOP USE ENTITY WORK. TOP (SCHEMATIC).

Fig. 2.12: ATPG Vectors Simulated at the Gate-Level

#### 2.8 IC Testing Using VXI and the IC Test Head

#### **VXIbus Test System**

VXI stands for VMEbus eXtensions for Instrumentation. VMEbus is a standard protocol (IEEE STD 1014) for interconnecting digital subsystems. The VXIbus has additional connections for a variety of trigger and clock signals. By using the VXIbus, an open hardware interface between the test instruments of a testing system is defined. Greater flexibility and higher speed communication between instruments becomes possible.

The VXI test system consists of one hardware platform, the HP 75000 Model D20 [26], and a number of software platforms that can be used with this hardware. These software platforms include: HP E1496, SCPI, SICL and HP VEE.

The HP E1496 software was used in the experiment. It consists of a vector spreadsheet and a timing cycle spreadsheet. The user can define test patterns, pin groups and timing cycles in the spreadsheets. Test patterns can be stored in a PCF (Pattern Capture Format) file and imported to the spreadsheet or put into the spreadsheet manually. After all the definitions, test data can be sent to the DUT (Design Under Test), through the I/O pattern pod or timing control pod. The PCF file can be generated in an automated way.

ATPG test sets are generated by the Test Compiler and formatted into WGL (Waveform Generation Language) style, then modified into PCF format. This is the automated way the author developed to get the PCF file.

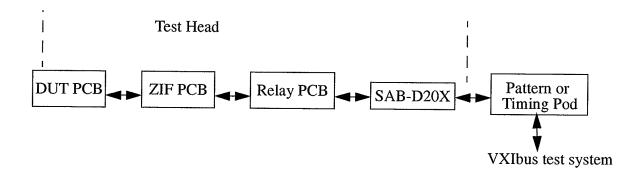

The VXI system has the following features: it is standard, flexible, and upgradable. Figure 2.13 illustrates the IC Test Head and its interface to the VXI test system.

### **IC Test Head**

Fig. 2.13: Signal Routing and Distribution

The Test Head and DUT board are the hub of any IC test system. The CMC TH1000 mixed signal IC Test Head [25] is a low cost test fixture designed to test mixed signal integrated circuits. External signals are introduced through SABs (signal adaptor boards), which can carry digital and/or analog signals for testing.

This section is included to illustrate a physical test environment that could be used for manufacturing test within the test framework developed in thesis.

Because of the faults in relay boards and lacking of SABs, the author did not finish the testing of the ALU.

# 2.9 Summary

This Chapter reviewed test and Design-for-Testability techniques including full scan, partial scan and boundary scan approaches. As a more and more important technique for testability design, test synthesis was also discussed. Design flows using the Synopsys test synthesis tools on module, chip and board level were presented, experimental results were also

shown. The author developed two novel approaches for utilizing the test vectors generated by the Synopsys ATPG, one for RTL simulation, the other for gate-level simulation. Finally, Component overview for physical testing of a chip using VXIbus test system and CMC IC test head was presented.

# **CHAPTER 3**

# HIGH LEVEL DESIGN METHODOLOGIES

### 3.1 Introduction

This chapter will describe how a design can be developed, from a behavioral description down to a gate-level structural description. High level design methodologies and the Synopsys tools are involved in each stage, including functional partitioning, state machine to RTL code transfer, schematic and VHDL design entry, logic synthesis and optimization, database file to SGE file transfer and SGE file to VHDL model transfer. The features of Synopsys SGE, VHDL Compiler and Design Compiler tool will be presented. VHDL plays an important role in the high level design process.

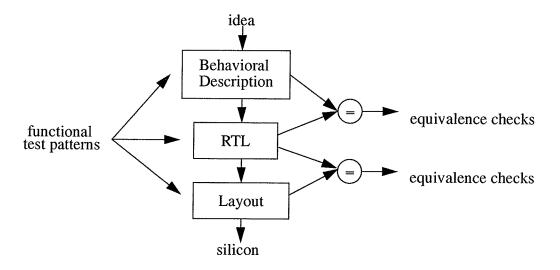

# 3.2 The High Level Design Process

Figure 3.1 is a traditional flow producing a chip from a behavioral description. The behavioral description could be natural language (e.g. English), an executable programming language (e.g. C) or some other behavioral model (e.g. Finite State Machine, Petri Net, etc.). Simulation at this stage is for identifying malfunctions, weakness or ambiguities in the behavioral description. The behavioral description can be translated into RTL code, manually or mechanically (by automation tools). The RTL model is verified with a testbench. The

Fig. 3.1: High Level Design Flow

behavioral and RTL models can be fed with the same functional test patterns and the responses must be the same. The RTL code may be then synthesized into a gate-level form and finally transformed to layout. This could also be done by hand or automatically. The functionality of different descriptions must be proved isomorphic. This is done by applying a stimulus to different abstraction levels and comparing their results.

With this design method, specification errors are identified in the early stages of the design process, and corrections are performed in shorter iteration cycles. The functional blocks are re-usable for other projects.

Methodologies for applying stimuli to RTL and layout simulation and for comparison of their results will be discussed in Chapter 4. Designers spend most of their time in the design cycle on high-level design and validation, including checking compliance to expected behavior and modifying the design as needed. As such, this is one of the most important aspects of the design process.

# 3.3 The VHDL Hardware Description Language

Because of the rapid growth of IC design complexity, hierarchical top-down design methods are utilized. An efficient approach is to incorporate a hierarchical hardware description language. VHDL (Very High Speed Integrated Circuit Hardware Description Language) is such a language and helps top-down design in two ways. First, as a specification tool, simulation of complex systems can begin before implementation details are realized. Second, VHDL facilitates the top-down design process where the higher level specification is developed, debugged and finally used to judge the correctness of the next lower level specification and implementation.

VHDL plays a significant role in high-level VLSI design. VHDL has been standardized as IEEE Standard 1076 and is accepted world-wide. It is a comprehensive language that makes dealing with design complexity easier. With VHDL, data and the design process are managed effectively. VHDL itself is not overly complex, but it is rich and powerful. The scope of VHDL includes descriptions from behavioral and architectural levels to the gate level. The language is hierarchical and mixed-level simulation is supported. VHDL covers a wide range of what other languages can not. Moreover, design automation, CAD tool development, logic synthesis, simulation and test pattern generation are made much easier using VHDL [30].

VHDL has the following features: a simulation modeling language, a design entry language, a test language, a netlist language and a standard language. In the design process, there are many points at which VHDL can be helpful: design specification, design capture and design simulation, design documentation, as an alternative to schematics, and as an alternative to a proprietary language.

By using VHDL, the designer's productivity can be dramatically improved, and he/she can take advantage of powerful tools for simulation and design verification. The reasons are:

- 1) High reuse of VHDL by building and using libraries of commonly-used VHDL modules,

- 2) With the rapid pace of development in electronic design automation (EDA) tools and target technologies, using VHDL can help you move into more advanced tools without having to re-enter your circuit descriptions. Unlike other programming languages, VHDL can describe concurrent (parallel) processes and their timing.

As a summary, the primary benefits of using VHDL are as follows:

- Makes the design specification more technology-independent:

- Allows the use of multiple vendors

- Avoids part obsolescence

- Documents in a standard way

- Automates low-level design details:

- Reduces design time

- Gets the design to market quicker

- Reduces design cost

- Eliminates low-level errors

- Improves design quality:

- Allows exploration of alternatives

- Verifies the design function at a higher level

- Verifies that the implementation matches the expected functionality

- Promotes design component re-use and sharing

VHDL has three types of descriptions: behavioral, dataflow, and structural. In the behavioral description, the sequential VHDL process is used to express the algorithm or behavior of a design. The structural description describes the interconnection of the components of a

design, by instantiating components. The dataflow description is in between, and is an operation defined in terms of a collection of data transformations.

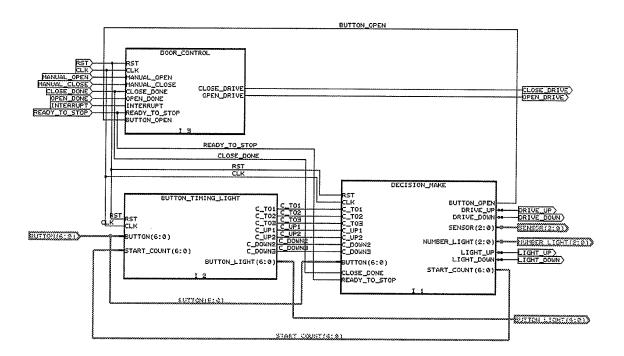

# 3.4 Functional Partitioning

In the example elevator controller system, the system is partitioned into three modules. Each module performs a specific and relatively independent function. The modules have signals interconnecting them, so they can communicate with each other. The three modules work together to carry out the functions of the whole system. The three modules are:

- door\_control

- button\_timing\_light

- decision\_make

The door\_control module controls the movement of the elevator door when the elevator stops at a certain floor. The button\_timing\_light module performs whenever the user presses the button making a request to go to a certain floor, times each request, and controls the button light turning on and off. If a request is made, the button light is turned on. Once the request is met, the button light is turned off. The final module is decision\_make. It makes the decision whether the elevator should go up or down. After the decision is made, the motor and arrow lights are given proper signals. If the elevator goes up, the motor drives the elevator up and the up arrow light is turned on. If it goes down, the motor drives the elevator down and the down arrow light is turned on. The decision is made based on comparing which request timing is the longest and which floor the elevator is currently on.

Fig. 3.2: Elevator Controller and its Submodules

# 3.5 Design Entry --- Schematic and VHDL

After the functional partitioning, the user can start entering a design either through schematic or VHDL code. Synopsys SGE (Synopsys Graphical Environment) is used for design entry and simulation of the design interactively. It consists of a schematic editor, a symbolic editor, a hierarchy navigator and a VHDL netlister. In the first two windows, the block diagram can be drawn and the signal names and types can be defined as shown in Figure 3.2. The VHDL netlister can generate the top level design structural VHDL, the top level design VHDL testbench template, and the bottom level module behavioral VHDL template. The user can use the text editor to manually enter behavioral code into the testbench and RTL level behavioral VHDL.

# 3.6 From Behavioral Description to RTL Code

The finite state machine is a very popular tool for defining the behavior of a system. It is a 5-tuple,  $F = (X, Q, Z, \delta, \omega)$ , Where X is a finite set of inputs, Q is a finite set of states, Z is a finite set of outputs,  $\delta$  is an output function,  $\omega$  is the next state function. There are two kinds of finite state machines, one is the Mealy machine, another is the Moore machine. Mealy outputs are a function of state and input  $(Q \times X-->Z)$ , while Moore outputs are a function of state (Q-->Z) alone.

Fig. 3.3: Mealy State Transition Diagram

State Transition Diagrams and State Transition Matricies are two styles for representing state machines. The general structure of a Mealy State Transition Diagram is shown above. The diagram consists of states (circles) and transitions (arrows). Transitions are made up of input conditions that cause the transition and output actions that happen along with the state transitions.

The door-control module in the elevator\_controller design is used to illustrate a realistic Mealy State Transition Diagram (see figure 3.4). Door-control controls the movement of the elevator door when the elevator stops at a certain floor. For the signal names, refer to Figure 3.2. There are four states for the door: closed, opening, open, closing. At any time, when rst is effective, regardless of what state the door is in, the door goes to the closed state. When the current state is closed, there is one possible next state: opening. When ready to go is

'1', manual\_open is effective, someone presses the open door button, or a delay for 3 seconds occurs, the door will open. The door goes to opening state, and the output action is: open\_drive is '1', close\_drive is '0', which allows the motor to drive the door open. Other transitions are easy to understand in the same way. In Figure 3.4, all '1' values mean signal effective, '0' values mean ineffective.

Fig. 3.4: State Machine for Door Control Module

A state machine may be coded using one or two case statements, but one case statement is preferable, because it is more concise and clear. Figure 3.5 shows a typical VHDL coding strategy for a state machine.

Mentor Graphics SDS tools have State Transition Diagram (STD) and State Transition Matrix (STM) editors. The tools can generate VHDL code from STD or STM automatically and do animation in STM to simulate the behavior of the system. These tools were not used for the elevator controller design. They are mentioned here and have been previously used

by the author merely to illustrate that commercial high level graphical STD tools are available.

```

architecture State_Machine of module A is

type state_type is ( state_1, state_2, state_3);

signal current_state, next_state: state_type;

begin

process ( input-list, current_state)

begin

----synchronous reset

if (rst='0') then

outputs and next state initialization

else

-----state transitions and output logic

case current_state is

when state_1 => if ( input condition is true)then

next_state <= state 2;

assign output;

end if:

end process;

process(clk)

begin

if (clk'event and clk='1') then

current_state<=next state;

end if:

end process;

end State_Machine;

```

Fig. 3.5: Typical VHDL Coding for a State Machine

## 3.7 From RTL Level to Gate Level

The process which transfers RTL level code to gate-level code is shown in Figure 3.6. The process includes three stages: logic synthesis and optimization, database file to SGE file transfer, and SGE file to VHDL file transfer. Each stage will be discussed below.

### Logic synthesis and optimization:

Synthesis is a process that transforms a circuit defined at one level of abstraction into a lower level definition subject to contain constraints. Optimization modifies the structure of the

logic according to timing and area constraints which are defined by the user, and maps the netlist to a certain technology.

Fig. 3.6: From RTL Level to Gate-Level

The Synopsys VHDL Compiler and Design Compiler are synthesis tools that work together to carry out the logic synthesis and optimization tasks. The Synopsys VHDL Compiler tools optimize the VHDL design at the architecture level. The Design Compiler tools optimize the design at the gate-level. The VHDL Compiler accomplishes two things: converting VHDL to an internal format, and optimizing block level representation through different optimization methods. The Design Compiler reads the design in internal format from the VHDL

Compiler, then optimizes and maps the design's structure for a specific technology. The VHDL Compiler synthesizes VHDL according to a certain synthesis policy. A synthesis policy consists of three parts: design methodology, design style, and language constructs. The Design Compiler takes the internal database format generated by the VHDL Compiler, performs logic optimization for area and timing, reconstructs part or all of the design, and maps it to a target technology.

Accurate and achievable constraints must be set before a design is optimized. These constraints include: clock constraints (clock period and edge), time delay constraints (for rising edge and falling edge, the maximum rise and fall, the minimum rise and fall times), and area constraints. After constraints are set for a design and before a design is compiled, the *check\_design* command is run to identify and help correct any problems in the design.

### Database file to SGE file transfer:

After synthesis and optimization using the VHDL Compiler and the Design Compiler, the technology-dependent gate-level netlist of the design will be a Synopsys database file (.db). To transfer this file to SGE graphics, the technology library must be translated to VHDL. The symbols for the CLASS library should be added to the Symbol Library search path in the .synopsys\_sge.setup file. Using the "db2sge" command or the SGE Hierarchy Navigator window menu "setup>DA to SGE transfer", the database file is transferred to SGE files, a schematic file (.sch) and a symbolic file (.sym).

### SGE file to VHDL file transfer:

Finally, a new VHDL design description can be created, by using the Synopsys SGE window menu command "code VHDL models". This a structural VHDL design. The architec-

ture consists of instantiation statements for gate-level components (refer to Figure 3.8 which presents architecture level VHDL for the multiplexer of Figure 3.7). Library CLASS is the ASIC vendor technology for this design. Port maps in the component instantiation statements express network connectivity. The configuration statement (see Figure 3.9) refers to primitives from the library CLASS with architecture FTSM. At this stage, a gate-level VHDL file (.vhd) is created for the design. In Chapter 4, this gate-level VHDL file will be shown to be very useful when doing after-synthesis simulation or mixed level simulation for a design.

Fig. 3.7: Multiplexer

```

The RTL version for multiplexer is:

```

entity MUL is

```

end MUL;

architecture BEHAVIORAL of MUL is

begin

process(a,b,c)

begin

if c='1' then

f<=a;

else

f<=b;

end if;

end process;

end BEHAVIORAL;

```

port(a,b,c: in std\_logic; f: out std\_logic);

Fig. 3.8: RTL Level VHDL Description for Multiplexer

```

--- VHDL Model Created from SGE Schematic mul.sch -- Apr 26 14:13:36 1996

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.std_logic_arith.all;

library CLASS;

use CLASS.components.all;

entity MUL is

Port (

A: IN STD_LOGIC;

B: IN STD_LOGIC;

C: IN STD_LOGIC;

F: OUT STD_LOGIC);

end MUL;

architecture SCHEMATIC of MUL is

n17: std_logic;

signal

signal

f_DUMMY: std_logic;

begin

f \leq f_DUMMY;

U8: IVA

Port Map (A=>b, Z=>n17);

U7: EON1

Port Map (A = > n17, B = > c, C = > a, D = > c, Z = > f DUMMY);

end SCHEMATIC;

configuration CFG_MUL_SCHEMATIC of MUL is

for SCHEMATIC

for U8: IVA

use entity CLASS.IVA(FTGS);

end for;

for U7: EON1

use entity CLASS.EON1(FTGS);

end for;

end for;

end CFG_MUL_SCHEMATIC;

```

Fig. 3.9: Gate-level VHDL Description for Multiplexer

Some statements are non-synthesizable, such as: wait for, assert, read, readline, while(), loop.

# 3.8 Summary

This chapter considers the issues of high level design methodologies, discusses how to develop a design from the initial specification down to gate-level implementation. The state machine is presented as a very useful behavior description tool. RTL VHDL code can be derived from the state machine model. Logic synthesis and optimization can be done automatically using CAD tools. A gate-level version of a VHDL file can be transferred from the RTL version of the VHDL file using the CAD tool Synopsys SGE. The VHDL feature demonstrated is that it works as both behavioural and implementation language. This is illustrated using an elevator controller design example.

# **CHAPTER 4**

# TESTBENCH GENERATION AND APPLICATION METHODOLOGIES

### 4.1 Introduction

In Chapter 3, it was mentioned that one of VHDL's benefits is that it is a test language. How VHDL works as a test language will be discussed in this chapter. This feature of VHDL is referred to as the VHDL testbench. Testbenches work for both manufacturing and functional verification purposes. The testbench that works for manufacturing verification purposes can be generated automatically by CAD tools, as was discussed in Chapter 2. This chapter focuses on functional testbench generation and application methodologies. In this chapter, testbench concepts, styles, generation methodologies, and how a testbench simulates at different levels of abstraction will be discussed. The testbench simulation results for the elevator controller design will also be presented.

### 4.2 VHDL Testbench

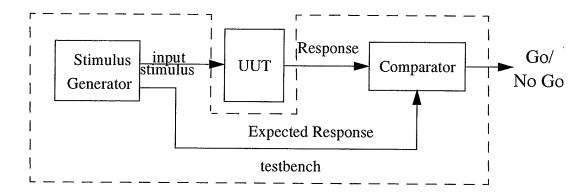

A testbench is a functional block, where the UUT (Unit Under Test) and reference models are embedded (it is also called a test bed). Responses from the reference model and from the UUT will be compared at certain clock periods. From this idea, a practical testbench scheme has been developed as illustrated in Figure 4.1 which shows the high level structure of the

testbench.

Fig. 4.1: Structure of A Testbench

The testbench consists of a Stimulus Generator block and a Comparator block. The design to be tested, is instantiated in the testbench as the unit under test (UUT). The Stimulus Generator block is responsible for stimulating the UUT and is the heart of the testbench. The Comparator block monitors device outputs and compares the expected outputs with the real outputs. If the real response does not match the expected response, an error message will be shown, and modification of the testbench, UUT, or test vectors is needed. The goal of a testbench is to thoroughly exercise the UUT by creating stimulus generators and comparators that exercise the UUT to verify its compliance to specification.

The testbench can be used to verify behavioral descriptions at the RTL level and to verify structural descriptions at the gate-level. The higher the abstraction level the testbench is generated in, the more convenient it is to control. The trend is to use a high level to generate test programs.

VHDL based testbenches have the following characteristics:

- Development efficiency

- Reusability

- Inherent documentation

- Tool vendor independence

- Mixed level simulation VHDL based testbenches allow simulation at all levels. From the behavioral level down to the gate level

A testbench consists of four major sections: library inclusions, entity declaration, test architecture and configuration statements. Libraries contain packages of shared subprograms. The testbench is the uppermost level of the hierarchy. All operations are performed inside the testbench, so it has no input and output signals in its entity. In the architecture declaration, there are component declarations (indicating which design is used as the UUT), signal declarations, and input stimulus generation and response checking processes. The components are instantiated in the configuration statement.

| library IEEE;<br>use IEEE.std_logic_1164.all;  | Section 1 Library Inclusion   |

|------------------------------------------------|-------------------------------|

| entity testbench is end testbench;             | Section 2 Top Level Entity    |

| architecture A of testbench is end A;          | Section 3 Test Architecture   |

| Configuration cfg_A of testbench is end cfg_A; | Section 4 Test Configurations |

Fig. 4.2: Testbench Structural Contents

Functional behavior is more easily described, analyzed and debugged when working with high level descriptions of the design. The same applies to a testbench. Tests are more easily described, analyzed, and debugged when working with high level descriptions of the testbench. In this thesis, high level descriptions have the same meaning as functional and behavioral descriptions.

Developing HDL (Hardware Description Language) testbenches at high levels of abstraction is the current trend. It is desirable to raise the level of abstraction, allowing testbench reuse and achieving higher quality results. Post synthesis (gate-level) simulation represents a minimal percentage of overall simulation activity in an HLD-based methodology. RTL level simulation occupies the greater percentage of the simulation activities.

The values used for input stimulus and output comparison are called test vectors. Test vectors can be created and made available during simulation in many different ways. They may be used in various combinations. For example, you can generate stimulus with a VHDL process, and use some other method to check the circuit response.

# 4.3 Testbench Styles and Coding Strategies

There are different ways to do stimulus generation, application, and response checking. As a result, testbench design has numerous styles. Although it is not necessary to do comparisons of real responses with expected responses, it is recommended to do so. Generally speaking, testbenches have three major styles: Ad-Hoc, algorithmic, and vector files [30]. These styles are discussed below.

#### 4.3.1 Ad-Hoc

An ad-hoc collection of stimulus cases are used to exercise the basic functions of the UUT. The ad-hoc style is used in the *door-control* testbench as shown is Figure 4.3. This example intends to check if the *manual\_open* signal can drive the *open\_drive* signal, and that *manual\_close* can drive the *close\_drive* signal. The simulation result is shown in section 4.8. Ad-Hoc was the major testbench style used for the *elevator\_controller* design.

```

signal_stimulus: process

begin

ready_to_stop<='0';

manual_open<='0';

manual_close<='0';

close_done<='0';

open_done<='0';

interrupt<='0';

wait for 50 ns;

ready_to_stop<='1';

wait for 40 ns;

ready_to_stop<='0';

wait for 200 ns;

manual_open<='1';

wait for 40 ns;

manual_open<='0';

wait for 200 ns;

open_done<='1';

wait for 40 ns;

open_done<='0';

wait for 200 ns;

manual_close<='1';

wait for 40 ns;

manual close<='0';

wait for 200 ns;

close done<='1';

wait for 40 ns;

close done<='0';

wait for 1500 ns;

end process;

```

Fig. 4.3: Ad-Hoc Test Vector Coding for door\_control Module

# 4.3.2 Algorithmic

Another way to generate stimuli is to write an algorithm. For example, in Figure 4.4, a loop statement is used to generate an incremental signal value. This code was used in the functional verification of a 74181 ALU. The simulation results are shown in Appendix B.

```

A_stimulus: process

variable i: integer;

variable seed: std_logic_vector(3 downto 0);

begin

A<="0000";

seed:="0000";

wait for 20 ns;

for i in 1 to 7 loop

seed:=seed+"0010";

A<=seed;

wait for 20 ns;

end loop;

end process;

```

Fig. 4.4: Algorithmic Test Vector Coding for the ALU Testbench

### 4.3.3 Vector Files

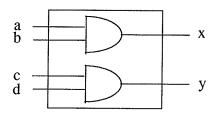

A testbench process fetches test vectors (including input stimuli and expected responses) from a data file. Thus it reads the vectors as stimulus and also monitors whether the behavior of the UUT matches the expected response in the test vector file. These test vectors might be captured during an interactive simulation session or generated using an algorithmic approach.

Figure 4.6 shows one style of a testbench which obtains test vectors from an external data file. The design is a double and gate (and\_2) as shown in Figure 4.5. In this case, two packages textio and std\_logic\_textio must be included in the library inclusion statement. The process begins with a set of variable declarations. The declaration of F tells the simulator the name of the test vector file, and2.vec. The readline statement allows one line read from the file F to be placed to the variable L. The read operations allow values from the line L to be "read" into a variable. The code for fetching and reading the values into variables is in the section labelled get a vector. Any difference between expected and real outputs are reported

by the assert statements.

Fig. 4.5: Example: and 2

```

test: process

file F: text is in "and2.vec";

variable L: line;

variable a_in,b_in,c_in,d_in,x_out,y_out:std_logic;

begin

readline (F,L);

read (L,a_in);

read (L,b_in);

read (L,c_in);

get a vector

read (L,d_in);

read (L,x_out);

read (L,y_out);

if endfile(F) then

wait;

end if;

wait for 400 ns;

a \le a_in;

b<=b_in;

assign input values

c<=c_in;

d \le d_in;

wait for 100 ns;

assert x=x_out

report "Unexpected response on x";

assert y=y_out

check output values

report "Unexpected response on y";

wait for 400 ns;

end process;

```

### Data file and2.vec:

000000 010100 111111

Fig. 4.6: Testbench Fetch Test Vectors From Data File and Data File

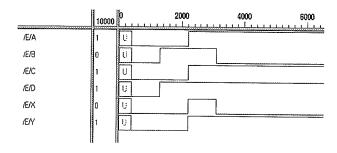

In the vector file, the storage order is a, b, c, d, x, y, i.e. a is the left most bit, and y is the right most bit. The simulation waveforms produced are illustrated in Figure 4.7.

Fig. 4.7: Simulation Result for Circuit and 2