### Parallel Algorithm Design and Implementation of Regular/Irregular Problems: An In-depth Performance Study on Graphics Processing Units

by

Steven Solomon

A thesis submitted to The Faculty of Graduate Studies of The University of Manitoba in partial fulfillment of the requirements of the degree of

Master of Science

Department of Computer Science The University of Manitoba Winnipeg, Manitoba, Canada

Copyright © 2012 by Steven Solomon

#### Parimala Thulasiraman

### Parallel Algorithm Design and Implementation of Regular/Irregular Problems: An In-depth Performance Study on Graphics Processing Units

### Abstract

Recently, interest in the Graphics Processing Unit (GPU) for general purpose parallel applications development and research has grown. Much of the current research on the GPU focuses on the acceleration of regular problems, as irregular problems typically do not provide the same level of performance on the hardware. We explore the potential of the GPU by investigating four problems on the GPU with regular and/or irregular properties: lookback option pricing (regular), single-source shortest path (irregular), maximum flow (irregular), and the task matching problem using multi-swarm particle swarm optimization (regular with elements of irregularity). We investigate the design, implementation, optimization, and performance of these algorithms on the GPU, and compare the results. Our results show that the regular problem achieves greater performance and requires less development effort than the irregular problems. However, we find the GPU to still be capable of providing high levels of acceleration for irregular problems.

### Acknowledgments

I would like to thank my advisor, Dr. Parimala Thulasiraman, for all the guidance and support she has provided throughout my research. I extend these thanks to Dr. Ruppa K. Thulasiram as well, for his added support and encouragement. I am also grateful to my examining committee, Dr. Michael Domaratzki and Dr. Shawn Liu, for providing useful feedback on my thesis and helping me to improve it further. I extend my gratitude to the National Science and Engineering Research Council of Canada (NSERC) for their financial support of my research in the form of an Alexander Graham Bell Canadian Graduate Scholarship award.

Finally, I would like to thank my family for supporting me throughout my pursuit of a Masters degree.

# Contents

|          | Abs  | tract                                                     | ii   |

|----------|------|-----------------------------------------------------------|------|

|          | Ack  | nowledgments                                              | iii  |

|          | Tab  | le of Contents                                            | vi   |

|          | List | of Tables                                                 | vii  |

|          | List | of Figures                                                | viii |

| 1        | Intr | roduction                                                 | 1    |

| <b>2</b> | Par  | allel Computing and the GPU                               | 9    |

|          | 2.1  | Parallel Systems                                          | 9    |

|          | 2.2  | CUDA Framework                                            | 11   |

|          | 2.3  | GPU Architecture                                          | 14   |

|          | 2.4  | Parallel Techniques and Performance Metrics               | 19   |

|          |      | 2.4.1 Parallel Reduction                                  | 20   |

|          |      | 2.4.2 Scan                                                | 22   |

|          |      | 2.4.3 Speedup                                             | 23   |

| 3        | Bin  | omial Lattice for Pricing Lookback Options                | 25   |

|          | 3.1  | Introduction to Option Pricing                            | 26   |

|          |      | 3.1.1 Binomial Lattice Method for Option Pricing          | 27   |

|          |      | 3.1.2 Pricing Lookback Options using the Binomial Lattice | 30   |

|          | 3.2  | Related Work                                              | 33   |

|          | 3.3  | Option Pricing on the GPU                                 | 34   |

|          |      | 3.3.1 Hybrid Computations                                 | 39   |

|          | 3.4  | Results                                                   | 40   |

|          | 3.5  | Summary                                                   | 46   |

| 4        | Bre  | adth First Search                                         | 48   |

|          | 4.1  | Introduction to BFS                                       | 48   |

|          | 4.2  | Related Work                                              | 50   |

|          | 4.3  | BFS on the GPU                                            | 53   |

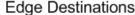

|          |              | 4.3.1          | Active Vertices Modification         | 57       |

|----------|--------------|----------------|--------------------------------------|----------|

|          | 4.4          | Result         | s                                    | 61       |

|          | 4.5          | Summ           | ary $\ldots$                         | 65       |

| <b>5</b> | The          | λίσν           | Maximum Flow Algorithm 6             | 6        |

| J        | 5.1          |                |                                      | 56       |

|          | $5.1 \\ 5.2$ |                |                                      | 58       |

|          | 0.2          | 5.2.1          | 8                                    | 59       |

|          |              | 5.2.1<br>5.2.2 | J                                    | 70       |

|          |              | 5.2.2<br>5.2.3 | 0                                    | 70       |

|          |              | 5.2.3<br>5.2.4 |                                      | 70<br>71 |

|          |              | -              |                                      |          |

|          |              | 5.2.5          |                                      | 71       |

|          |              | 5.2.6          | 1 1                                  | 22<br>72 |

|          | 50           | 5.2.7          | 1 0                                  | 2        |

|          | 5.3          |                |                                      | 74       |

|          | 5.4          | MPM            |                                      | 78       |

|          |              |                |                                      | 80       |

|          |              |                |                                      | 31       |

|          |              |                | 1                                    | 33       |

|          |              |                | 1 0                                  | 35       |

|          |              | 5.4.1          |                                      | 86       |

|          |              |                | 5                                    | 87       |

|          |              |                | 0                                    | 88       |

|          |              |                | 1                                    | 88       |

|          | 5.5          |                |                                      | 39       |

|          |              | 5.5.1          | 1 0                                  | )5       |

|          | 5.6          | Summ           | ary                                  | 97       |

| 6        | Mul          | ti-Swa         | rm Particle Swarm Optimization 10    | <b>1</b> |

|          | 6.1          | Introd         | uction to PSO and Multi-Swarm PSO    | )2       |

|          |              | 6.1.1          | Initialization                       | )4       |

|          |              | 6.1.2          | Velocity and Position Update 10      | )5       |

|          |              | 6.1.3          | Fitness Update                       | )6       |

|          |              | 6.1.4          | Local and Swarm Best Position Update | )6       |

|          |              | 6.1.5          | The Complete PSO Algorithm           |          |

|          |              | 6.1.6          | Multi-Swarm PSO                      | )8       |

|          | 6.2          | Introd         | uction to the Task Matching Problem  | )9       |

|          | 6.3          |                | d Work                               |          |

|          |              | 6.3.1          | Multi-Swarm PSO                      |          |

|          |              | 6.3.2          | PSO on the GPU                       |          |

|          |              | 6.3.3          | PSO for Task Matching                |          |

|          | 6.4          |                | Swarm PSO on the GPU                 |          |

|          |              |                |                                      |          |

|          |                                   | 6.4.1                                             | Organization of Data on the GPU                    |            |      |     | . 119                               |

|----------|-----------------------------------|---------------------------------------------------|----------------------------------------------------|------------|------|-----|-------------------------------------|

|          |                                   | 6.4.2                                             | GPU Algorithm                                      |            |      |     | . 121                               |

|          |                                   |                                                   | Particle Initialization                            |            |      |     |                                     |

|          |                                   |                                                   | Update Position and Velocity                       |            |      |     | . 122                               |

|          |                                   |                                                   | Update Fitness                                     |            |      |     | . 123                               |

|          |                                   |                                                   | Update Best Values                                 |            |      |     | . 126                               |

|          |                                   |                                                   | Swap Particles                                     |            |      |     | . 127                               |

|          | 6.5                               | Results                                           |                                                    |            |      |     | . 128                               |

|          |                                   | 6.5.1                                             | A Short Discussion on Solution Quality             |            |      |     | . 137                               |

|          | 6.6                               | Summa                                             | ry                                                 |            |      | •   | . 139                               |

|          |                                   |                                                   |                                                    |            |      |     |                                     |

| <b>7</b> | $\mathbf{Dis}$                    | cussion                                           | and Comparison                                     |            |      |     | 141                                 |

| 7        | <b>Dis</b><br>7.1                 |                                                   | and Comparison<br>tructures and Memory Performance |            |      |     |                                     |

| 7        |                                   | Data St                                           | -                                                  |            |      |     | . 142                               |

| 7        | 7.1                               | Data St<br>Load B                                 | tructures and Memory Performance                   |            |      | •   | . 142<br>. 145                      |

| 7        | $7.1 \\ 7.2$                      | Data St<br>Load B<br>Hybrid                       | tructures and Memory Performance                   | · ·<br>· · | <br> | •   | 142<br>145<br>146                   |

| 7        | $7.1 \\ 7.2 \\ 7.3$               | Data St<br>Load B<br>Hybrid<br>Speedur            | tructures and Memory Performance                   | <br><br>   | · ·  | • • | 142     145     145     146     148 |

| 7        | $7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5$ | Data St<br>Load B<br>Hybrid<br>Speeduy<br>A Brief | tructures and Memory Performance                   | <br><br>   | · ·  | • • | 142     145     145     146     148 |

# List of Tables

| 3.1 | Correctness tests for GPU and Hybrid implementations on a GTX 260.                     |     |

|-----|----------------------------------------------------------------------------------------|-----|

|     | S is the price of the underlying asset, T is the time (in years) until the             |     |

|     | maturity date of the option, $\sigma$ is the volatility, $r$ is the risk-free interest |     |

|     | rate and N is the number of time-steps                                                 | 41  |

| 3.2 | Correctness tests for GPU and Hybrid implementations on a GTX 570.                     |     |

|     | S is the price of the underlying asset, T is the time (in years) until the             |     |

|     | maturity date of the option, $\sigma$ is the volatility, r is the risk-free interest   |     |

|     | rate and N is the number of time-steps.                                                | 42  |

|     |                                                                                        |     |

| 4.1 | Profiling data for GPU BFS kernels                                                     | 64  |

| 5.1 | Average Performance Improvement Between Normal GPU and Active                          |     |

|     | Vertices Implementations                                                               | 92  |

| 5.2 | Average division in execution time between all three phases                            | 95  |

| 5.3 | Average speedup of best implementation versus sequential CPU imple-                    |     |

|     | mentation                                                                              | 95  |

|     |                                                                                        |     |

| 6.1 | Percentage of execution time taken by most significant kernels                         | 137 |

| 6.2 | Solution quality of MSPSO and PSO normalized to FCFS solution ( $< 1$                  |     |

|     | is desired)                                                                            | 138 |

# List of Figures

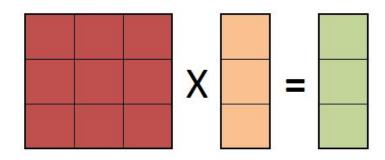

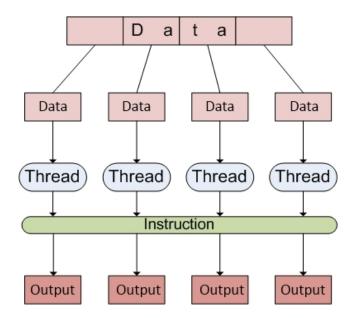

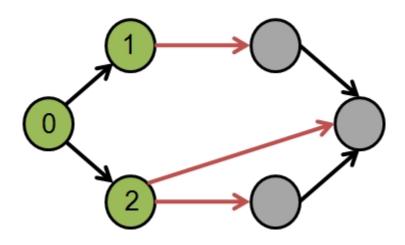

| $1.1 \\ 1.2 \\ 1.3$                     | An example of a regular problem: matrix-vector multiplication<br>An example of data-parallel computations                                                                                                        | ${3 \\ 4 \\ 5 }$     |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

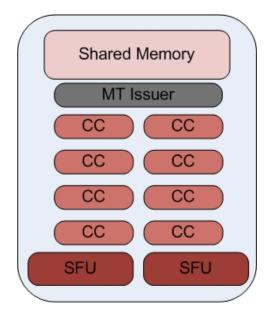

| 2.1<br>2.2<br>2.3<br>2.4                | 2D Organization of thread grid and thread blocks. [33]                                                                                                                                                           | 12<br>15<br>21<br>22 |

| $3.1 \\ 3.2$                            | Structure of a three-layer binomial lattice                                                                                                                                                                      | 28                   |

| $3.3 \\ 3.4$                            | tion and the associated $Y(t)$ , $G(t)$ , and $S(t)$ values for each node<br>Thread-level data access patterns in the lookback GPU kernel<br>Performance of the Hybrid lookback algorithm with varying threshold | 31<br>37             |

| 3.5                                     | values                                                                                                                                                                                                           | 44                   |

| 3.6                                     | mentations                                                                                                                                                                                                       | 45<br>46             |

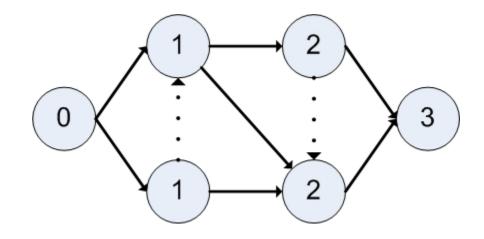

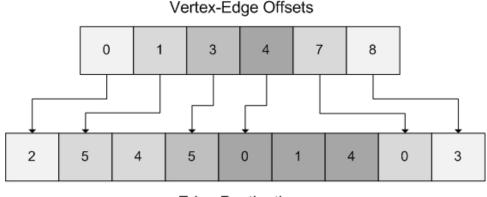

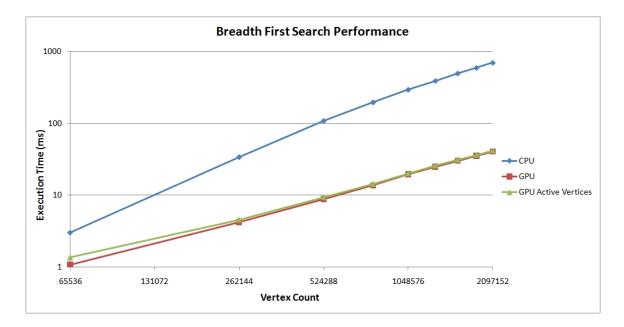

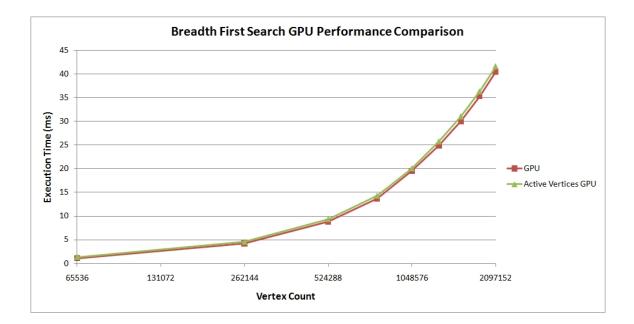

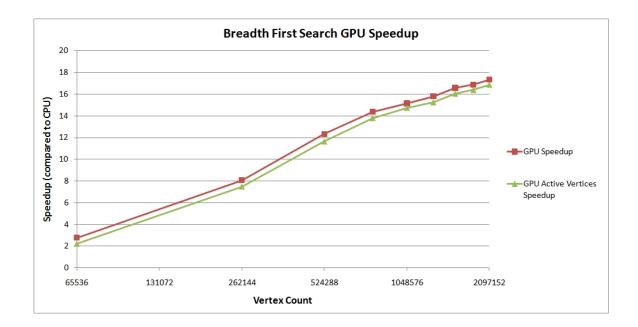

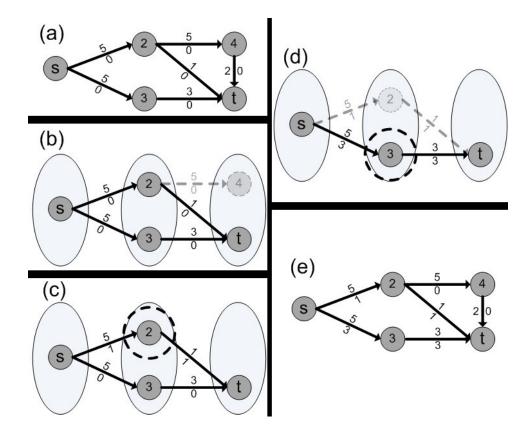

| 4.1<br>4.2<br>4.3<br>4.4                | Layered network of a graph                                                                                                                                                                                       | 49<br>54<br>60       |

| $\begin{array}{c} 4.5\\ 4.6\end{array}$ | tions                                                                                                                                                                                                            | 62<br>63<br>64       |

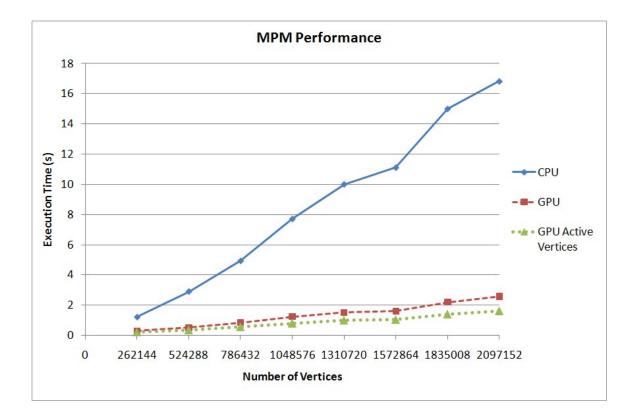

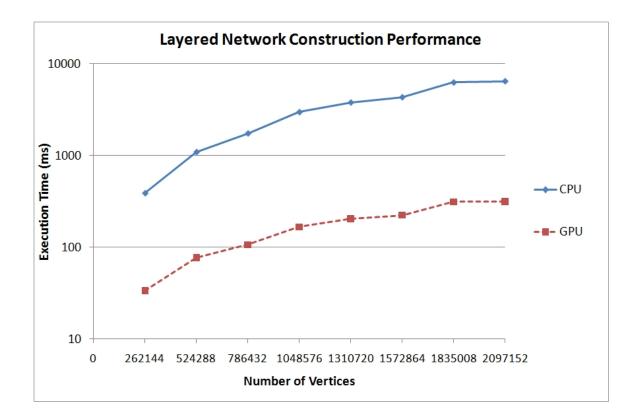

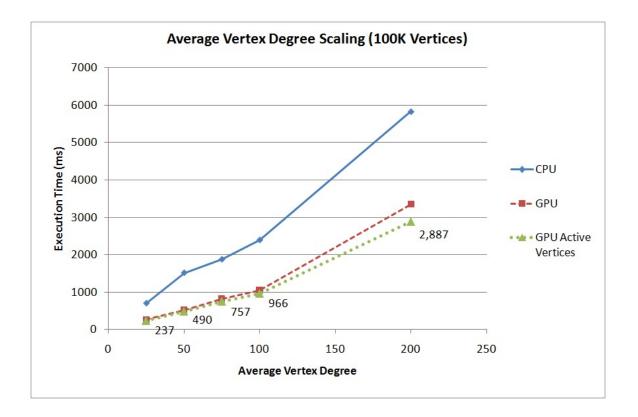

| $5.1 \\ 5.2 \\ 5.3$                     | An example iteration of the MPM algorithm                                                                                                                                                                        | 73<br>90<br>92       |

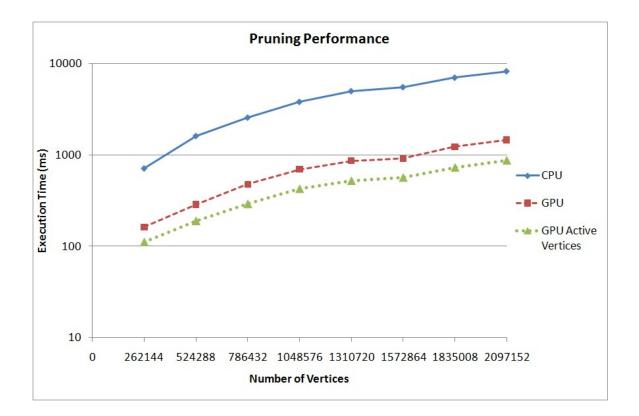

| 5.4  | Total execution time taken by pruning phase.                            | 93   |

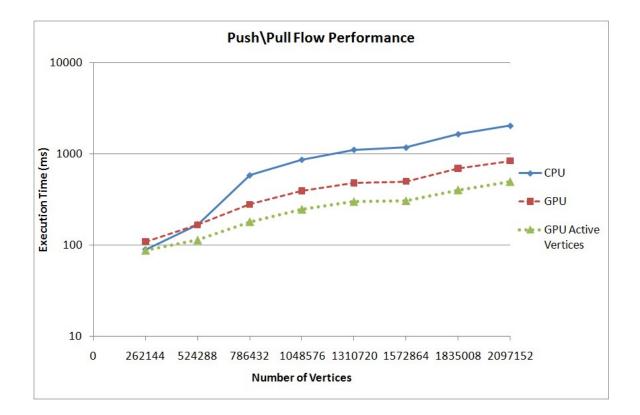

|------|-------------------------------------------------------------------------|------|

| 5.5  | Total execution time taken by push/pull flow phase                      | 94   |

| 5.6  | Performance scaling by average vertex degree                            | 96   |

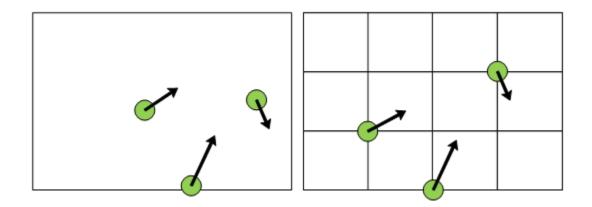

| 6.1  | Continuous (left) and Discrete (right) solution spaces                  | 103  |

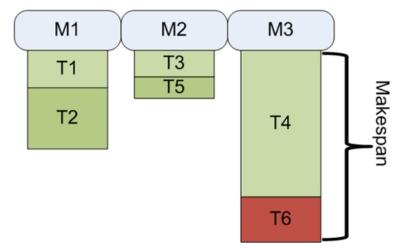

| 6.2  | Example of task matching and makespan determination                     | 110  |

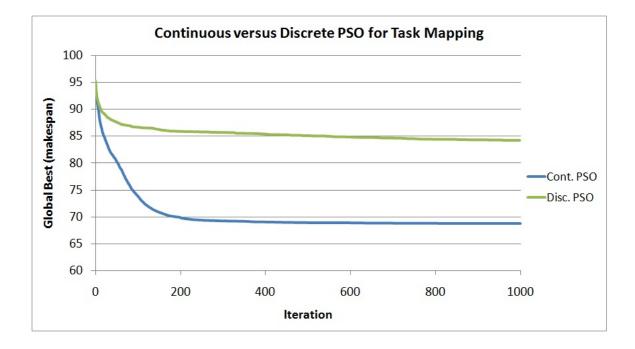

| 6.3  | Global best results for continuous and discrete PSO by iteration        | 119  |

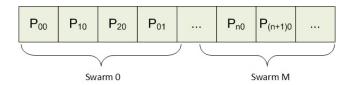

| 6.4  | Global memory layout of position, velocity, and particle best positions |      |

|      | $(P_{xy} \text{ refers to particle } x$ 's value along dimension $y$ )  | 120  |

| 6.5  | Global memory layout of fitness and particle best values                | 120  |

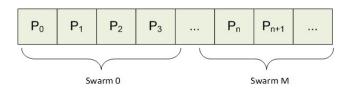

| 6.6  | Comparison between sequential CPU and GPU algorithm as swarm            |      |

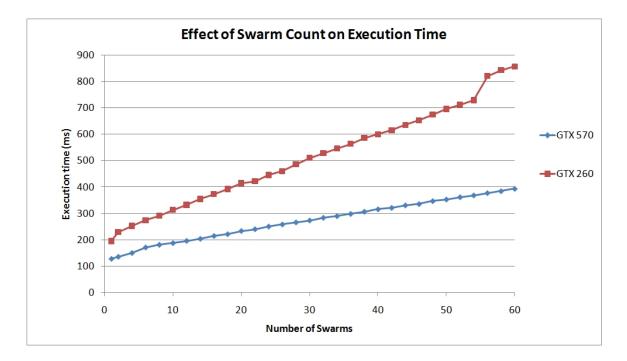

|      | count increases.                                                        | 130  |

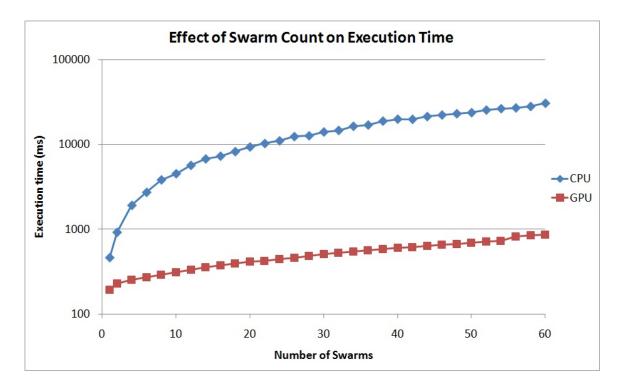

| 6.7  | Total execution time for the various GPU kernels as the swarm count     |      |

|      | increases.                                                              | 131  |

| 6.8  | Comparison between GTX 260 and 570 GPUs as swarm count increases        | .132 |

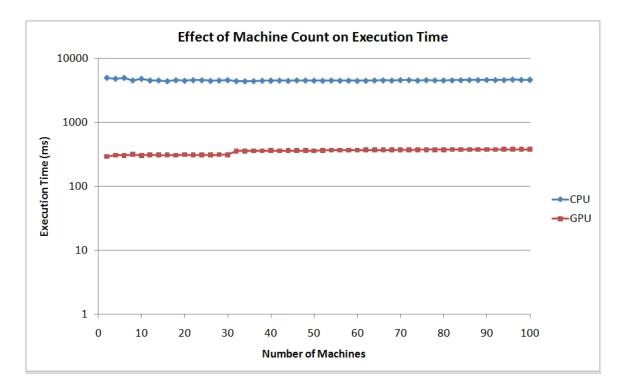

| 6.9  | Comparison between sequential CPU and GPU algorithm as machine          |      |

|      | count increases.                                                        | 133  |

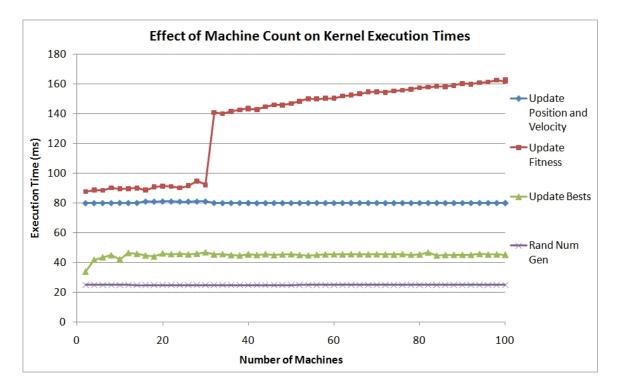

| 6.10 | Total execution time for the various GPU kernels as the machine count   |      |

|      | increases.                                                              | 134  |

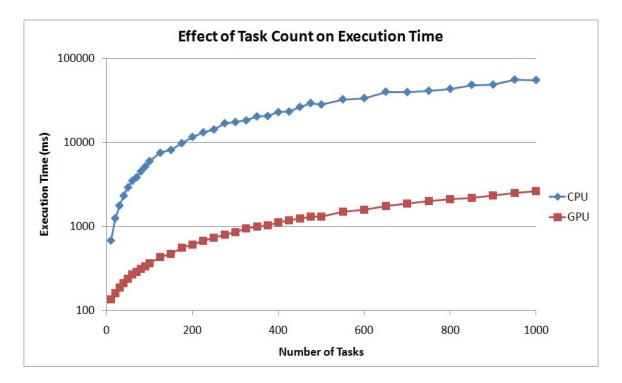

| 6.11 | Comparison between sequential CPU and GPU algorithm as task count       |      |

|      | increases.                                                              | 136  |

|      |                                                                         |      |

## Chapter 1

### Introduction

For decades, the gaming and graphics industries have driven the evolution of the Graphics Processing Unit (GPU). Essentially the only users of GPUs, these industries pushed the performance and parallelism of the GPU to greater heights, year by year. With the introduction of the programmable shader, however, the GPU became open to General Purpose GPU (GPGPU) applications. Now it was possible to execute algorithms that did not belong to the gaming or graphics world on a GPU. With the more recent addition of frameworks such as CUDA and OpenCL, from Nvidia [36] and Khronos Group [14] respectively, developing GPGPU applications became even easier. The result was a surge of interest in GPGPU applications, and an explosion of research into the capabilities and potential of the GPU for general purpose applications.

We originally considered the GPU not only because it was a new architecture for parallel computing, but also because it provides us with a tremendous level of exploitable parallelism and computational performance. Nvidia [33], for example, measures the peak performance of a modern, high-end GPU (GTX 580) at slightly over 1.5 TFLOPS (Trillions of FLoating Point Operations per Second), whereas a modern high-end multi-core CPU from Intel ranks in at under 250 GFLOPS (Millions of FLOPS). To lend further credence to this performance gap, Suda et al. [50] compared a high-end (at the time) GPU to a single node of the T2K Todai supercomputer (containing four quad-core processors). They concluded that the GPU offers power savings, improved single-precision floating point performance, and ten times lower cost compared to the supercomputer node.

Unfortunately, not all types of algorithms are guaranteed to fully exploit the GPU and harness this tremendous power. We note here two classifications of problems: regular and irregular. Regular problems feature a very structured, predictable nature in terms of both program flow and memory accesses. Consider our matrix-vector multiplication example in Figure 1.1. We know beforehand exactly what computations are required in order to generate the output vector. We know the computational steps of the basic tasks (computing an element in the output vector), and we know exactly how many of these tasks we will require. As a result, we can generally optimize an algorithm for solving this problem for a given architecture easily. In a multi-processor environment, for example, we may simply have each processor compute the resulting elements for a given number of unique rows in the matrix.

In our regular problem example, we note that the operations and data access patterns required to compute any given element in the result vector are exactly the same. We compute each task, or computation of an element in the result vector, in the exact same way, only changing the data we access. As a result, we develop an algorithm with *data-parallel* properties. Data-parallel implies that we can execute the

Figure 1.1: An example of a regular problem: matrix-vector multiplication

same instruction across multiple pieces of data in parallel. We provide an example of data-parallel processing in Figure 1.2. Note how each threads "feeds" a unique piece of data through the same instruction in parallel.

In the literature, a large amount of research has been dedicated to studying dataparallel algorithms. These types of algorithms are well suited for the GPU, due to the very data-parallel nature of the architecture which we will discuss further in Chapter 2. Regular, data-parallel algorithms allow one to exploit the thread-level parallelism of the GPU very easily and observe significant performance improvements.

Irregular problems, on the other hand, feature very unpredictable and unstructured properties for their program flow and data access patterns. They feature dynamic changes at run-time. Such problems typically (but not always) use pointerbased data structures such as graphs. With irregular problems, we do not know the interactions between tasks, or even the number of total tasks, ahead of time. Along with these unpredictable computations, these problems further features very unpredictable and unstructured memory accesses.

We use the breadth first search, shown in Figure 1.3, to illustrate the features of an algorithm with irregular properties. Until we reach a vertex and prepare to

Figure 1.2: An example of data-parallel computations

traverse its edges, we do not know what data we will need next. We do not know how many edges we will traverse until we have completed a full breadth first traversal of the graph, and we do not know the general structure of the vertices and edges at compile time (given an unstructured graph). Furthermore, the path(s) we traverse through the graph may differ depending on which vertex we choose to start with. The data itself defines the structure of the computations and, as a result, we cannot easily optimize this algorithm for the particular nuances of an architecture, especially when it comes to memory accesses and load balancing. This holds true for the GPU, where we see reduced performance with irregular problems due to their unstructured and unpredictable nature.

Irregular problems have been studied extensively for CPU-based architectures. The burden of parallelism, however, has generally been left to smart, automatic compilers rather than the developer. The Galois system from Kulkarni et al. [26], for

Figure 1.3: An example of an irregular problem: breadth first search

example, investigated the potential of automatic, dynamic (or optimistic, as they refer to it) parallelization of irregular problems. The system uses a set of parallel primitives which encapsulate parallel operations in order to invoke parallelism. The authors test their method against two irregular problems and show promising results. They further mention that the traditional static methods of automatic parallelization are ideal for regular problems, but are entirely unsuitable for irregular problems.

Kulkarni et al. [25] later investigated a number of irregular parallel algorithms using a tool they developed called "ParaMeter", which searches a given algorithm for parallelism and generates parallelism profiles of the algorithm. They then use these profiles to determine where the available parallelism lies in an algorithm, or, perhaps, to investigate if an algorithm contains a reasonable level of exploitable parallelism to begin with. These examples show that as of two years ago, there has been much ongoing investigation into the parallelization of irregular algorithms.

The study of irregular problems on the GPU, however, remains in its infancy. Due to the optimal mapping between regular problems and the GPU, the majority of existing GPU research focuses on these types of problems. In general, the GPU provides significant performance gains on regular problems when compared to traditional CPU implementations. For example, Preis et al. [39] investigate a few financial algorithms on the GPU that contain regular properties. The authors measure an approximate 80 times performance improvement on the GPU when compared to a sequential CPU implementation for the highest performing algorithm. An earlier paper by Fujimoto [11] investigated dense matrix-vector computations on the GPU and saw up to 32 times better performance on the GPU compared to a sequential CPU implementation.

In this work, we investigate the design, implementation, and performance of algorithms for both regular and irregular problems on the GPU. In order to accomplish this we closely investigated four different problems: lookback option pricing, layerednetwork construction, the maximum flow problem, and the task matching problem. Within this set of problems we have a regular problem (lookback option pricing), a simple irregular problem (single-source shortest path), a complex irregular problem (the maximum flow problem), and a problem that is computationally difficult and requires heuristics to solve (task matching). The algorithms we choose to solve these problems maintain the same regular or irregular properties of their respective problem. In this respect, we choose the binomial lattice method for pricing lookback options, a breadth-first search to solve the single-source shortest path problem, the MPM maximum flow algorithm for solving the maximum flow problem, and a multiswarm particle-swarm optimization algorithm for solving the task-matching problem. We believe this diverse choice of problems and algorithms will help to show the differences in strategy and effort required to optimize regular versus irregular problems for the GPU, as well as the general performance possible on the architecture.

This, then, is where we make our major contribution with this work. By describing the design and extensively investigating the performance of a variety of problems on the GPU, we build a solid foundation of knowledge regarding what works well on the GPU, and the general capabilities of the architecture. We present the issues associated with regular and irregular problems, discover methods for improving the performance, and provide an in-depth examination of the performance each implemented algorithm achieves on the GPU. By experimenting with a number of algorithms we build a comparison of the major differences between algorithms with regular and irregular properties, such as the effort required for optimization, the performance achieved, and even the general structure of the GPU algorithms. We chose to investigate the GPU not only for its power, but also because we believe that the results from our work will provide greater insight and understanding for the relatively young GPGPU area, an area of parallel computing that continues to grow.

We organize this thesis as follows: Chapter 2 starts with a brief introduction into parallel systems, describes the GPU architecture and CUDA framework, and concludes with a discussion on some parallel computing primitives and speedup. Chapter 3 describes the first problem we investigate, the lookback option pricing problem, using the binomial lattice algorithm. Chapter 4 contains our investigation of the breadth first search algorithm for solving the single-source shortest path problem, and Chapter 5 discusses the MPM algorithm. We complete the chapters dedicated to the problems we investigated with Chapter 6, which provides our work on a multiswarm particle swarm optimization algorithm for solving the task matching problem. In Chapter 7 we compare the algorithms we looked at, and discuss what similarities and differences we observed in terms of design, implementation, and performance. Finally, we discuss our conclusions and routes for future work in Chapter 8.

### Chapter 2

# Parallel Computing and the GPU

In this chapter, we discuss the relevant details of the GPU architecture, the CUDA framework, and two basic parallel algorithms that we use in our work. As we implemented and tested all of our work on an Nvidia GTX 260 GPU (based on the GT200 architecture), all information (and hard numbers) in this chapter pertains to this particular model. Because the GPU is a relatively new architecture in the general purpose parallel algorithms arena, we start with a brief discussion on the two general categories of parallel systems and where the GPU fits in.

### 2.1 Parallel Systems

We divide the parallel systems used in parallel computing into two major camps, homogeneous and heterogeneous, based on the processing elements contained within the system. Homogeneous systems are the most common systems, and are used very widely to this day. These include hardware like the traditional multicore processor which contains a number of equivalent, or symmetrical, cores. The system is *homogeneous*, it does not contain any processing elements that differ. Heterogeneous systems, on the other hand, contain processing elements that differ from others within the same system. They are not composed of the same hardware throughout, but contain other processing elements that may be more suited to specialized tasks.

The GPU falls under the heterogeneous systems category. While the GPU itself is composed of a number of identical processing elements, it, alone, does not compose the entirety of the system. The GPU requires a traditional CPU to drive the computational processes we want to execute on it. In effect, the GPU is an accelerator: when present in a system, we design algorithms that the main CPU will schedule for execution on the GPU in order to accelerate tasks. We need both a CPU and a GPU within a system in order to execute algorithms/code on the GPU, creating our heterogeneous system.

Outside of definitions based on processing element composition, Flynn [8], with his taxonomy, splits up parallel computing systems into three categories <sup>1</sup> based on their execution capabilities. The two we are concerned about here are Multiple Instruction Multiple Data (MIMD) and Single Instruction Multiple Data (SIMD). With MIMD, each processing element executes independently of one another. In essence, MIMD allows for each processing element to execute different instructions on different data from one another.

SIMD, on the other hand, involves each processing element executing in lock-step with one another. That is, every processing element executes the same instruction at

<sup>&</sup>lt;sup>1</sup>Flynn describes four total categories of computing systems, however the Single Instruction Single Data category is a uniprocessing system, rather than a parallel system

the same time as one-another, but executes this instruction on different data. MIMD exploits task-level parallelism (achieving parallelism by executing multiple tasks at one time), while SIMD exploits data-level parallelism (achieving parallelism by taking advantage of repetitive tasks applied to different pieces of data). As we discuss in the next two sections, the MIMD style of system is very different from that of the GPU, which follows the SIMD paradigm.

#### 2.2 CUDA Framework

Prior to discussing the GPU architecture itself, we will cover some details of the CUDA framework. Nvidia developed CUDA [36], or the Compute Unified Device Architecture, in order to provide a more developer-friendly environment for GPU application development. CUDA acts as an extension to the C language, providing access to all of the threading, memory, and helper functions that a developer requires when working with the GPU.

The GPU hardware provides us with a tremendous level of exploitable parallelism on a single chip. Not only does a standard mid-to-high end GPU contain hundreds of processing cores, but the hardware is designed to support thousands, hundreds of thousands, even *millions* of threads being scheduled for execution. CUDA provides a number of levels of thread organization in order to make the management of all these threads simpler. At the top level of the thread organization we have the thread grid. The *thread grid* encompasses all threads that will execute our GPU kernel (the application we run on the GPU). To get to the next level down, the *thread block*, we split up the threads in the thread grid into multiple, equal-sized blocks. The user

| Thread Grid              |                 |                           |                 |                           |                 |  |  |  |  |

|--------------------------|-----------------|---------------------------|-----------------|---------------------------|-----------------|--|--|--|--|

| Thread<br>Block<br>(0,0) |                 | Thread<br>Block<br>(1, 0) |                 | Thread<br>Block<br>(2, 0) |                 |  |  |  |  |

|                          |                 |                           |                 |                           |                 |  |  |  |  |

| <br>Thread Block (1,0)   |                 |                           |                 |                           |                 |  |  |  |  |

| Thread<br>(0,0)          | Tł              | nread<br>1,0)             | Thread<br>(2,0) |                           | Thread<br>(3,0) |  |  |  |  |

| Thread<br>(0,1)          | Thread<br>(1,1) |                           | Thread<br>(2,1) |                           | Thread<br>(3,1) |  |  |  |  |

| Thread<br>(0,2)          | Thread<br>(1,2) |                           | Thread<br>(2,2) |                           | Thread<br>(3,2) |  |  |  |  |

Figure 2.1: 2D Organization of thread grid and thread blocks. [33]

specifies the organization of threads within a thread block and thread blocks within a grid. What this means for a thread block is that we may organize and address threads in a one, two, or three-dimensional fashion. The same holds true for thread blocks within a grid, the user specifies one, two, or three-dimensional organization of the blocks composing the thread grid. Figure 2.1 provides an example of twodimensional organization of a thread grid and thread blocks.

At the lowest level of thread organization we have the *thread warp*. Equal sized chunks of threads from a thread block form the thread warps for that block. Unlike the size or dimensions of a block/grid, the hardware specifications predetermine the size of a warp, and the threads are ordered in a one-dimensional fashion. For the GT200 (and earlier) architecture, 32 threads form a warp. The hardware issues each

thread within a warp the same instruction to execute, regardless of whether or not all 32 threads have to execute it (we discuss this concept further in Section 2.3). When branching occurs, threads which have diverged are marked as inactive and do not execute until instructions from their path of the branch are issued to the warp. Algorithms for GPUs should therefore reduce branching, or ensure that all threads in a warp will take the same path in a branch in order to maximize performance a difficult task when working with the unpredictability of irregular algorithms.

Typically, a parallel application will involve some degree of synchronization. Synchronization is the act of setting a barrier in place until some (or perhaps all) threads reach the barrier. In essence, this ensures that the threads in question will all be at the same step in the algorithm immediately after the synchronization point. CUDA provides a few mechanisms for synchronization based around the thread warp, block, and grid. First, each thread in a warp is always synchronized with all the other threads in that same warp as they all receive the same instruction to execute. Secondly, CUDA provides block-level synchronization in the form of an instruction. By using the \_\_\_syncthreads() instruction, threads reaching the instruction will wait until all threads in the thread block have also hit that point.

Unfortunately, CUDA does not provide any mechanisms within a kernel to synchronize all threads in a grid. As a result, we must complete execution of the kernel and rely on the CPU to perform the synchronization. CUDA provides two methods for accomplishing this:

1. Launching another kernel — After invoking one kernel, attempting to launch another will result in the CPU application halting until the previous kernel has completed execution (effectively "synchronizing" all threads in the thread grid, as they must all have completed execution of the first kernel).

2. Using the cudaThreadSynchronize() instruction in the CPU application — Essentially the same as the above, but explicitly controlled by the user. Again, the CPU application will halt here until the previous kernel has completed execution.

To conclude this section we make note of a few memory instructions that CUDA provides, as we use them in our work in order to avoid read-after-write and write-after-write memory hazards. These hazards occurs when multiple threads attempt to perform some computations and store the result into the same location in memory. A second thread may read outdated data while the first thread has not completed writing the *updated* data to the memory location. This second thread then uses the outdated data for its computations, rather than the updated data it should have read (from the first thread). In order to remove these potential errors, we use CUDA's **AtomicX** operations, where **X** represents the actual operation we wish to perform on the data (such as OR or AND). This atomic memory operation forces each thread executing it to perform their accesses/transactions in a serial fashion, ensuring that each subsequent thread works with the most recent value in that memory location.

### 2.3 GPU Architecture

In this section we move on to a description of the GPU architecture itself. Further, we connect the architectural details of the GPU with the CUDA framework informa-

Figure 2.2: General Layout of a Streaming Multiprocessor

tion we discussed in the previous section. We begin with the GPU as a whole, which is composed of two separate units: the core and the off-chip memory, connected by a proprietary and undisclosed interconnection network. At this moment in time we are most interested in the units that compose the core of the GPU, the Streaming Multiprocessors or SMs. As pictured in Figure 2.2, each SM contains eight CUDA Cores, or CCs. These CCs are the computational cores of the GPU, and handle the execution of instructions for the threads executing within the SM. SMs also contain a multi-threaded instruction dispatcher, and two Special Function Units (SFUs) that provide extra transcedental mathematic capabilities.

Execution of instructions on each SM follows a model similar to SIMD, which Nvidia [33] refers to as SIMT, or Single Instruction Multiple Threads. In SIMT, the hardware scheduler first schedules a warp for execution on the CCs of an SM. The hardware then assigns the same instruction for execution across all threads in the chosen warp — only the data each instruction acts on is changed. This threading model implies that all threads in a warp are issued the same instruction, regardless of whether or not every thread needs to execute that instruction. Consider the case where the threads encounter a branch: half of the threads in a warp take path A in the branch, the other take path B. With SIMT, the hardware will issue instructions for path A to all threads in the warp, even those that took path B. This represents an important concept as threads in a warp *diverging* across different paths in a branch results in a loss of parallelism — each branch is essentially executed serially, rather than in parallel. That is to say, rather than having 32 threads performing useful work, only a subset of the threads do work for path i, while the remaining threads idle, waiting for instructions from their own path.

The importance of the thread block becomes apparent when we discuss them in context of the SM. All of the threads within a thread block must execute entirely within a single SM. This means that we (or the hardware) cannot split up the threads in a thread block between multiple SMs. Multiple thread blocks, however, may execute on a single SM if that SM has enough resources to support the requirements of more than one thread block.

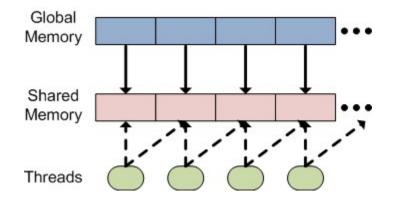

Each of the SMs further contains 16 kilobytes of shared memory. This shared memory essentially acts as a developer-controlled cache for data required during kernel execution. As a result, the responsibility is on the developer to place data into this memory space — there does not exist any automatic hardware caching of data (Nvidia changed this in their Fermi [33] architecture, which introduced a hardware-controlled cache at each SM). Nvidia [35] claims that accesses to shared memory are up to 100 times faster than global memory, given no bank conflicts. As shared memory is split into 16 32-bit wide banks, multiple requests for data from the same bank arriving at the same time cause bank conflicts and, as a result, are serialized. In effect, bank conflicts reduce the overall throughput of shared memory, as some threads must wait for their requested data until the shared memory has serviced the requests from previous threads. Shared memory is exclusive to each thread block executing on a given SM. That is to say, a thread block cannot access the shared memory data from another thread block, even if it is executing on the same SM.

Moving on to the other memory systems present within the GPU we have the global memory. Global memory is the largest memory space available on the GPU and is read/write accessible to all threads. Unfortunately, a significant latency, measured by Nvidia [33] at approximately 400 to 800 cycles, occurs for each access to global memory. Global memory accesses are not cached at any level, which serves to further compound this latency issue. Thus, every access to global memory will result in the same latency hit. The GPU contains, however, some auxiliary memory systems that *are* cached at the SM level. Each SM has access to caches for the constant and texture memory of the GPU. While these two memories are still technically part of global memory (that is, data stored in these memories are stored in the global memory space) their caches help to reduce the latency penalty by exploiting data locality.

Based on what we have learned about the memory systems within the GPU, we clearly want to place an emphasis on exploiting shared memory as much as possible. With comparatively fast access speed and no dependencies on data locality to mitigate high latencies, shared memory represents the most optimal location for storage. Unfortunately, we run into many situations where the small size of shared memory results in insufficient storage space for the data required at a given moment in time. Due to the stringent size constraints, along with the unpredictable nature of irregular algorithms, our irregular algorithms in particular rely heavily on global memory, while still attempting to exploit shared memory where possible.

While global memory clearly represents a major area of performance loss due to latency, there is one important technique we can use to mitigate the damage: global memory coalescing. In order to understand how coalescing works, we must first revisit the idea of a warp. As we described earlier, a thread warp is composed of 32 threads, all of which are given the same instruction to execute. In the worst case, we would expect there to be 32 individual requests to global memory if the instruction in question requires data from global memory. With coalescing, however, we have the ability to reduce the total number of requests down to only two requests in the best case. The reason for this lies with how memory requests are handled at the warp level: they are performed in a half-warp fashion. That is, 16 threads request data from memory first, followed by the remaining 16 shortly thereafter. As a result, the best scenario for coalescing combines all memory requests from each half-warp.

In the GT200 architecture, coalescing occurs when at least two threads in one half of a warp are accessing from the same memory segment in global memory. This technique is very powerful and leads to tremendous improvements in the performance of global memory. Unfortunately, data access patterns must be very structured in order to ensure threads will access data from the same memory segment as one another, something that is not guaranteed when working with irregular algorithms. The easiest way to achieve this result is ensuring that each thread accesses data from global memory that is one element over from the previous thread's access location. As we will show, we make use of coalescing as much as possible in our algorithms in order to achieve greater memory performance.

We close this chapter off with a brief discussion on the isolation between thread blocks enforced by CUDA. Recall that shared memory is exclusive to a thread block other threads in other blocks cannot access the shared memory allocated by the block. Furthermore, there are no built-in mechanisms for communication or synchronization between thread blocks <sup>2</sup>. All of these items combine to show one of the main tenets of CUDA: thread blocks are isolated units of computation. Threads within a thread block communicate with one another, but they cannot readily communicate with other thread blocks. Due to this lack of thread-grid-wide communication, we will show that our algorithm design changes from what it would otherwise be with full communication functionality. In essence, we rely on multiple kernels for the processing of an algorithm, rather than packing all program code into a single kernel.

#### 2.4 Parallel Techniques and Performance Metrics

In this section we describe two of the basic parallel techniques that we use a number of times throughout our GPU implementations. In essense, these techniques form a base for many algorithms in parallel computing, and, true to this, we make use of them in almost every algorithm we investigate. Following a description of these

<sup>&</sup>lt;sup>2</sup>Of course, the availability of global memory means that there will always exist a method for communication if desired. The latency of global memory coupled with the overhead of potentially thousands (if not more) of threads accessing a single data element (say, as a synchronization flag) results in an entirely unacceptable solution with a tremendous degree of performance degradation.

techniques, we describe the *speedup* performance metric.

#### 2.4.1 Parallel Reduction

A parallel reduction involves reducing a set of values into a single result, in parallel. More formally, given a set of values,  $v_1, v_2, ..., v_n$ , we apply some associative operator,  $\oplus$ , to the elements:  $v_1 \oplus v_2 \oplus ... \oplus v_n$ , resulting in a single value, w. We consider the structure of a parallel reduction to be that of a binary tree. At the leaf nodes, we have the original set of values. We apply  $\oplus$  to each pair of leaf nodes stemming from a parent node one layer up the tree (closer to the root node), giving us the value for that parent node. We repeat this process until we reach the root node, providing us with the final result, w.

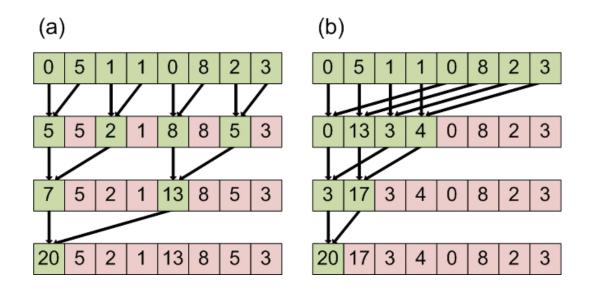

When we want to parallelize this reduction technique, we first note that layer iof the tree (where the root node is layer 0, and the leaves layer  $\log n$ ) requires the accumulated partial solution values from layer i + 1. This requirement results in synchronization; we can compute one layer of the tree in parallel, but we must wait for all threads to complete their processing of nodes in that layer before moving on to the next. Figure 2.3a provides an example of performing an addition reduction (that is,  $\oplus = +$ ) in parallel. Each subsequent array represents the next layer of computations. In the first layer, we have the initial array. In parallel, we add up each pair of elements (four parallel operations in total) and place the results back into the array. The next layer we have two remaining parallel operations which we use to add up the partial sums from the previous layer. Finally, we add the remaining two partial sums together and end up with the final result in element zero of the array

Figure 2.3: Two styles of parallel add reduction on an array of elements.

which contains the total sum of all initial values.

On the GPU, we typically perform a parallel reduction within a single thread block if possible. This allows us to use thread block level synchronization rather than the more costly thread grid level synchronization. As parallelism is plentiful on the GPU, we assign one thread per node in the current layer of the tree. To further optimize this algorithm for the GPU, we do not use the interleaving method shown in Figure 2.3a but, rather, split the layer into halves, and work on one side (pulling data from the other). We show this technique in Figure 2.3b. By working on contiguous areas/halves we ensure coalescing takes place as we read data from global memory, and bank conflicts do not occur as we read data from shared memory.

Figure 2.4: Example of an additive scan initial value and result.

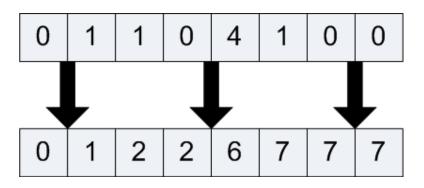

#### 2.4.2 Scan

The scan (sometimes referred to as a "parallel prefix sum") operation takes a set of values,  $v_1, v_2, ..., v_n$  and an associative operator,  $\oplus$ , and returns another set of values,  $v'_1, v'_2, ..., v'_n$  such that  $v'_1 = v_1, v'_2 = (v_1 \oplus v_2), v'_3 = (v_1 \oplus v_2 \oplus v_3), ..., v'_n =$  $(v_1 \oplus v_2 \oplus ... \oplus v_n)$ . We provide an example of the resulting data from a scan operation where  $\oplus = +$  in Figure 2.4.

While we implement the parallel reduction algorithm ourselves, we use the high performance scan operation provided in the CUDA Data Parallel Primitives (CUDPP) Library [43, 42] in cases where we require it. Sengupta et al. [41] thoroughly describe and explain the design and optimization of the scan algorithm present within CUDPP. The authors describe the build up from a warp-level scan, to a block-level scan, to a grid/global-level scan. They emphasize further optimizations such as the increased workload provided to each thread to better hide global memory latency, and the focus on reducing per-thread register use to ensure that a large number of threads may be active at one time within a block (which serves to further help hide the latency of global memory accesses). We chose this library as it has been extensively optimized for the GPU and offers all the functionality we require.

#### 2.4.3 Speedup

Speedup is a frequently used performance metric for parallel applications. Basic speedup measures the difference in execution time for the same application when executed on one processing element versus n processing elements. Equation 2.1 provides the formula for speedup, where  $T_1$  is the execution time on one processing element, and  $T_n$  the execution time on n processing elements.

$$S(n) = \frac{T_1}{T_n} \tag{2.1}$$

We believe that the standard speedup metric as shown in Equation 2.1 is unfair not only for the GPU, but for parallel systems in general. When developing an application for parallel execution, the developer generally ensures the application is optimized for parallel execution. That is, we assume we have a parallel computing environment and develop the application accordingly. Thus, executing such an application on a single processing element and comparing its execution time against the same application running on n processing elements does not provide very useful results. Instead, we turn to *absolute* speedup, which we believe creates a more suitable environment for comparison.

Unlike speedup, absolute speedup measures the difference in execution time between the parallel application running on n processing elements, and an optimal sequential application. Thus, two applications must be created in order to measure absolute speedup: the parallel application, and a sequential application. In this case, both implementations are designed around the type of system (parallel or sequential) they will execute on, resulting in a fairer measurement. The formula for absolute speedup replaces  $T_1$  from Equation 2.1 with  $T_s$ , where  $T_s$  is the execution time of the sequential application.

Throughout this work we use the absolute speedup metric when measuring performance, but refer to it as "speedup" for simplicity.

### Chapter 3

# Binomial Lattice for Pricing Lookback Options

In this chapter we discuss our work on lookback option pricing for GPUs. The pricing of options represents a fundamental problem in finance and is useful for a variety of purposes from risk analysis to portfolio management. Due to the dynamic and volatile nature of the market, pricing options quickly represents an advantage for the players in the market. As a result, advanced algorithms and hardware platforms are always in demand for real-time pricing.

We chose to investigate this problem on the GPU not only for the reasons described above, but also because of the structured nature of a particular solution to this problem. As we will explain, we investigate the binomial lattice method of pricing options due to its very regular, very structured nature. This binomial lattice algorithm serves as a helpful benchmark to determine the level of effort required for the optimization of a regular problem, as well as a base measure of performance/speedup. We first lead in with a description of option pricing, followed by the related work in this area, and conclude with details on the mapping and implementation of our algorithm itself.

### **3.1** Introduction to Option Pricing

Financial options form a contract between two parties. The holder of an option gains the right to exercise the option up to the end of the contract period, otherwise referred to as the maturity date of the option. On the opposite side, we have the writer of an option. While an option grants its holder the right to exercise, an option obligates its writer to follow the whims of the holder. If the holder decides to exercise the option, the writer must comply, and if the holder decides not to exercise the option, the writer cannot force the holder to exercise.

We categorize options into two main types: call options and put options. A call option gives the holder the right to buy an underlying asset (such as a stock) at a price specified at the time of writing the option (the strike price). A put option provides the opposite scenario; it gives the holder the right to sell an underlying asset at a pre-specified price.

Alongside these two types of options are a variety of different styles as well. European and American represent the two "vanilla" (simple) option styles. A European option grants the holder the right to exercise the option only at the maturity date, while the holder of an American option may exercise at any point in time during the contract period. There exist other styles of options as well, generally referred to as exotic options, which include Asian options, chooser options, and the particular

exotic option style we focus on in this Chapter: lookback options.

In terms of exercise style, lookback options may be treated as either a European or American option. For this work, we consider the American-style put lookback option. The payoff of a lookback option is based on the maximum (for a put) or minimum (for a call) value of the underlying asset between the purchase date and the maturity date of the option.

We are, of course, interested in the pricing of these lookback options. We define an option price as the premium associated with the option — the price the holder must pay to the writer in order to purchase the option. In other words, the option price represents the cost associated with the actual purchase of the option. A variety of methods exist for pricing options of various styles, and we explore one such technique in this work: the binomial lattice method for option pricing.

#### 3.1.1 Binomial Lattice Method for Option Pricing

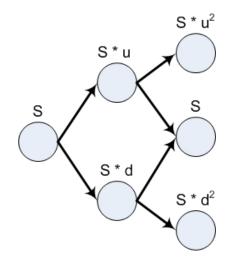

The binomial lattice, as described by Cox et al. [3], is a popular method for approximating the movement of an underlying asset's value, which enables the pricing of an option. A binomial lattice is essentially a binary tree, where the root represents time zero (of the option contact) and the leaf nodes represent the maturity date of the option. The binomial lattice method assumes the value of the underlying asset follows some random walk from the root node to a leaf node of the lattice.

As we move from one node in the lattice to the next, we have a choice of moving "up" or "down". An up movement corresponds to an increase in the value of the underlying asset, S and a downward movement a decrease in the value. We represent

Figure 3.1: Structure of a three-layer binomial lattice.

the increased value via an upward movement with u, and the decreased value via a downward movement with d. The lattice also contains a probability (based on the volatility of the asset) of an upward movement, p, and a probability of a downward movement, 1-p. We compute a value for p using the formula provided by Haug [16]:

$$p = \frac{e^{r*\delta t} - d}{u - d}$$

We provide a simple example of a three-layer binomial lattice structure in Figure 3.1. We note that this figure does not exactly resemble a binary tree, as we combine nodes at each layer, forming a recombining binomial lattice. This combining of nodes helps to reduce redundant computations as we move through the lattice. The binomial lattice supports this recombining strategy as an upward movement followed by a downward movement in the lattice is equivalent to a downward movement followed by an upward movement. For this reason, we combine these equal nodes at each level in the lattice, resulting in the structure shown in Figure 3.1.

The binomial lattice method offers us a very iterative, structured algorithm to

work with. We start at the leaves of the lattice, and work backwards, layer-by-layer, until we reach the root node (at which point we compute the option price). We label the root node as layer zero, and the leaf nodes as layer L - 1, where L equals the total number of layers in the lattice. Hence, any node in layer i + 1 represents one time step in the future from any node in layer i. As we reach a node at each layer we need to compute the option payoff at that node. As an example, for a European-style option we compute the option payoff of a node in layer i of the lattice based on the option payoff value of the two adjacent nodes in layer i + 1 using the formula provided by Haug [16]:

$$C_{i,j} = e^{-r*\delta t} * \left( pC_{i+1,j+1} + (1-p)C_{i+1,j-1} \right)$$

(3.1)

where r is the risk-free interest rate,  $\delta t$  is the change in time between each level in the lattice, p is the probability of an up movement in the lattice, and  $C_{i,j}$  represents the option payoff for node j at level i in the lattice. Essentially, the option payoff at  $C_{i,j}$  is influenced by the up and down movements of the underlying asset at a future time (level i + 1) as well as the probability of either movement. Of course, we use an alternative formula for the leaf nodes, as they do not have any adjacent nodes at a higher level to use in the option payoff calculation. For leaf nodes, the payoff equation (for a put option) becomes:

$$C_{i,j} = max(S - K, 0)$$

where S is, again, the price of the underlying asset and K is the strike price of the option.

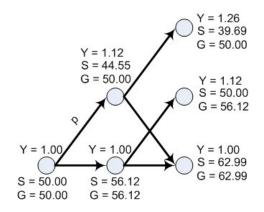

### 3.1.2 Pricing Lookback Options using the Binomial Lattice

While the basic binomial lattice works for vanilla American and European options, we cannot use it as-is for American-style lookback options. Hull [17] (Technical Note 13) describes how to modify the binomial lattice method in order to support lookback option pricing. Hull suggests a new parameter, Y(t). Y(t) takes the place of the asset price at each node in the lattice, and the author defines it with the following equation: Y(t) = G(t)/S(t) where G(t) represents the maximum asset price achieved up to time t, and S(t) the current asset price at t. We compute the value for Y(t) at each node in the lattice using the following rules:

- 1. Y is equal to 1 at the root node of the lattice.

- 2. When we move to the next time step from a node where Y = 1, Y = u if the move is an upward move, or 1 if the move is a downward move.

- 3. When we move to the next time step from a node where  $Y = u^m$  for  $m \ge 1$ ,  $Y = u^{m+1}$  for an upward move, or  $Y = u^{m-1}$  for a downward move.

We provide an example of the modified binomial lattice in Figure 3.2, complete with the associated Y(t), G(t), and S(t) values for each node, given that u = 1.12. We orient the lattice in the traditional manner in Figure 3.2, where increasing values at each node (represented by Y(t) instead of the asset value in this case) are preceded by an upward movement in the lattice. However, we note a few key differences from the original binomial lattice. First, we stress that while an upward movement in the original binomial lattice was paired with an upward movement in the asset price, an upward movement in this modification of the binomial lattice represents a *downward*

Figure 3.2: An example of the binomial lattice for an American put lookback option and the associated Y(t), G(t), and S(t) values for each node.

movement in the asset price, but an upward movement in Y(t), our new "parameter of importance". This reversal results from how we construct Y(t). In order for Y(t) to increase, S(t) must decrease, as G(t) cannot, by definition, decrease (recall that G(t)represents the maximum asset price observed thus far, hence it can only increase). As a result, a downward movement in the lattice corresponds to an increase in the value of S(t).

As a further example, consider the first choice of movement from the root node, with values S(0) and G(0). Clearly, G(0) = S(0) as the highest asset price we have observed thus far can only be the initial asset price. If we take a downward movement in the lattice (in Figure 3.2 this is simply a horizontal movement as Y(t)will not change), then S(i) increases. This increase implies that S(i) > S(0), and G(i) = S(i), and, therefore Y(i) = 1.

The modifications to the binomial lattice do not end with this new parameter, however. We must also modify the option payoff formula for each node to correspond with the formula required for lookback option payoff/pricing. We replace the original formula defined in Equation 3.1 with one defined in Hull [17], resulting in the following formula:

$$C_{i,j} = \max(Y_{i,j} - 1, e^{-r\delta t} * ((1 - p)C_{i+1,j+1}d + pC_{i+1,j-1}u))$$

(3.2)

for  $j \ge 1$ , and

$$C_{i,j} = \max(Y_{i,j} - 1, e^{-r\delta t} * ((1-p)C_{i+1,j+1}d + pC_{i+1,j}u))$$

(3.3)

for j = 1. All parameters remain the same as in the original binomial approach, and *i* represents the current time step (which, to reiterate, is further represented by a vertical layer in the lattice). The introduction of *u* and *d* represent the proportional movement of the asset price, up or down respectively, at each time step (layer in the lattice).

The first argument inside the max function on the right-hand side of each equation represents the local payoff, or option value at that particular node, in terms of Y. The second argument provides the computed option value for node  $C_{i,j}$  based on its children nodes at  $C_{i+1,j+1}$  and  $C_{i+1,j-1}$ . Put another way, we weight the local payoffs at nodes  $C_{i+1,j+1}$  and  $C_{i+1,j-1}$  by their probabilities of achieving these payoffs. As these children nodes represent a time in the future (from  $C_{i,j}$ ), we discount this weighted sum in order to simulate its value at the current layer, i, in the lattice. We then compare the resulting discounted option value with the local payoff at that node, and denote the maximum of these two values as the option value  $C_{i,j}$ .

Due to the very structured, regular nature of the binomial lattice, we believe it represents a "good fit" for the GPU architecture. We compute each time step/layer in the lattice synchronously, and we know ahead of time what data will be required at what step in the computations, hence the algorithm contains very regular, predictable properties. This well-suited nature of the algorithm motivated us to choose to work with the binomial lattice method on the GPU. We extended this choice to cover lookback options, as they had not been previously studied on the GPU hardware. Further, due to the ever-present need for faster and faster algorithms in the finance industry, a comparison to sequential CPU will help to show how beneficial a GPU may or may not be for financial applications.

### 3.2 Related Work

The traditional binomial lattice method for vanilla options has been studied on the GPU in the past. Podlozhnyuk [38] provided one such example of the binomial lattice method on GPUs using CUDA. The author describes a novel technique where they divide the lattice into sub-trees. A thread block then processes each sub-tree independently. Podlozhnyuk explains that this method allows for computations to take place solely within shared memory. The author admits, however, that redundant computations take place as a side effect of splitting the lattice into sub-trees. The improved speed of shared memory, however, may more than compensate for the redundant computations required. Unlike the work of Podlozhnyuk, we target an alternative method for the binomial lattice method that exploits global memory coalescing and removes all redundant computations.

Jauvion and Nguyen [23] further extended the work of Podlozhnyuk to the trinomial lattice, an incremental improvement over the binomial lattice. In their case, however, the authors investigate the potential for pricing one option per thread block, effectively pricing multiple options in parallel. The authors describe the GPU's precision as being sufficient, and claim that they achieve four decimal points of precision with 1000 time steps. Jauvion and Nguyen further show a speedup of up to 31.6 when parallelizing the pricing of 64 options over 1024 time steps.

As discussed earlier, we base our work around the lookback option pricing method described by Hull [17] (Technical Note 13). To the best of our knowledge, outside of our own work by Solomon et al. [46], there does not exist any other existing work studying the design, implementation, and performance of the binomial lattice method for pricing lookback options on the GPU.

## 3.3 Option Pricing on the GPU

In this section, we discuss the actual design and implementation of our GPU algorithm. As mentioned before, we do not follow the work of Podlozhnyuk [38] and, instead, choose a design technique that exploits global memory coalescing instead of shared memory and removes the redundant computations associated with dividing the lattice up into sub-trees.

Furthermore, we exploit the synchronous, iterative nature of the binomial lattice in our implementation. Computations start at the leaf nodes of the lattice and progress backwards, layer-by-layer (synchronously), until we reach the root node and compute the final option price. Due to this synchronous, layer-by-layer nature, each invocation of our GPU kernel handles one layer of the lattice. In other words, an invocation of our GPU kernel processes all nodes within a given layer, and, as a result, we require N invocations of the GPU kernel in order to complete the processing of a lattice with

#### N time steps/layers.

Although we are aware of the general structure of the computations, we have to map these computations to threads on the GPU. As the GPU is a very highly parallel architecture we take a fine-grained approach: we assign one thread to each node in the current layer of the lattice being processed. As we cover a single layer with each kernel invocation, this implies that we require only as many threads as there are nodes within the current active layer.

Within a given lattice layer t, we have t + 1 nodes that require processing <sup>1</sup>, and, thus, we must launch that exact number of threads for each layer. We note that this implies a reduction in the number of threads launched as the algorithm progresses. Clearly, we will have the most threads, and thus the most parallelism, at the first phase of the algorithm (covering the leaf-node layer of the lattice). Each subsequent phase of the algorithm reduces the number of threads we require by one.

In our algorithm, we store the data in global memory. Since global memory access carries a high latency penalty, we try to avoid as many accesses to global memory as possible. We also reduce the memory footprint of the algorithm by taking into account the structure of the computations. For example, if our problem instance has N time steps, and thus, N layers in the lattice, we initially require a maximum of N + 1 nodes allocated in the GPU's global memory. Note that we do not store the nodes for every layer in the lattice into memory. Consider that we work layer-bylayer through the lattice; clearly, by Equations 3.2 and 3.3 we only need data from the previous layer in order to generate the new layer.

<sup>&</sup>lt;sup>1</sup>Layer t does not contain 2 \* t + 1 nodes, as one might expect, due to the recombining nature of the lattice.

Therefore, we require at least N + 1 nodes of the lattice stored in global memory in the worst case. Our actual memory requirements double, however, due to not knowing which threads will execute when during each phase. We cannot simply write over the current node data in global memory as one thread may still require the data from the previous layer when another thread is attempting to write new data into that location for the node in the current layer. As a result, our memory requirements increase to 2 \* (N + 1) in order to maintain two sets of lattice node data in global memory and double-buffer the data. At each phase, we swap the lattice node data set that we update with the new option payoffs for the given layer.

Finally, we make use of a small amount of shared memory. As we have shown in Figure 3.2, a node requires multiple values from the previous layer, and multiple nodes in the current layer may require data from the same node in the previous layer. In order to avoid redundant accesses to global memory from threads requiring the same data to update their respective nodes, we perform an initial load of the required data for all nodes in a thread block into shared memory. When the algorithm begins, each thread accesses the required data from shared memory, rather than global memory. In this way, we eke out a small amount of extra performance by reducing the overall global memory accesses.

Furthermore, our reading of data in global memory (in order to populate shared memory) makes full use of global memory coalescing. We have each thread store a single value from global memory into the shared memory space. The other piece of data a thread requires is written to shared memory by the thread's neighbor. Figure 3.3 provides an example of this data access pattern — each thread pushes one

Figure 3.3: Thread-level data access patterns in the lookback GPU kernel.

value from global memory to shared memory, but reads two from shared memory. In this way, we exploit coalescing and improve the overall performance of all but one (per thread block) of our global memory reads <sup>2</sup> due to the structured, regular nature of the binomial lattice algorithm. Writing data back to global memory exploits coalescing as well, as each thread writes its value at the same time as its neighbors.

Our completed algorithm consists of two parts: the GPU kernel and the CPU control loop. The GPU kernel is shown in pseudocode in Algorithm 1. The OptionVals[] and TempOptionVals[] arrays are the two lattice node data sets. TempOptionVals[] contains the data that will be replaced with the current nodes data that we compute using the previous layer's values found in the OptionVals[] array. The first major if block (line 3) handles the loading of required data into shared memory (from global memory), and the second major if block (line 11) performs the actual computations to update a node. The CPU control loop manages the kernel invocations, the doublebuffering of the node arrays, and decides when to terminate the algorithm (which

$<sup>^{2}</sup>$ As shown in Algorithm 1 the last thread in a block must perform one extra global memory read to finish populating the shared memory buffer. This single read is uncoalesced as there are no other threads available in the warp to combine memory requests.

occurs when the algorithm completes processing of the root node).

| Algorithm 1 Lookback GPU Kernel |

|---------------------------------|

|---------------------------------|

Require: u, d, pu, pd, disc, OptionVals[], TempOptionVals[], timeStepNodeCount

- 1: threadID  $\leftarrow$  blockIdx.x \* blockDim.x + threadIdx.x

- 2: sVal[] //Location in shared memory

- 3: if thread ID < timeStepNodeCount then

- 4:  $sVal[threadIdx.x] \leftarrow OptionVals[threadID]$

- 5: if This thread is the last in the block, or the last node in the lattice then

- 6:  $sVal[threadIdx.x + 1] \leftarrow OptionVals[threadID + 1]$

```

7: end if

```

8: yValue  $\leftarrow u^{\text{threadID}}$  //Compute y-value for this node

### 9: end if

```

10: __syncthreads()

```

11: if threadID < timeStepNodeCount then

```

12: if threadID == 0 then

```

- 13: optionValue  $\leftarrow \max(yValue 1, (pu * sVal[1] * d) + (pd * sVal[0] * u)$

- 14: **else**

- 15: optionValue  $\leftarrow \max(yValue 1, (pu * sVal[threadIdx.x + 1] * d) + (pd * sVal[threadIdx.x] * u)$

- 16: **end if**

- 17: TempOptionVals[threadID]  $\leftarrow$  optionValue

- 18: end if

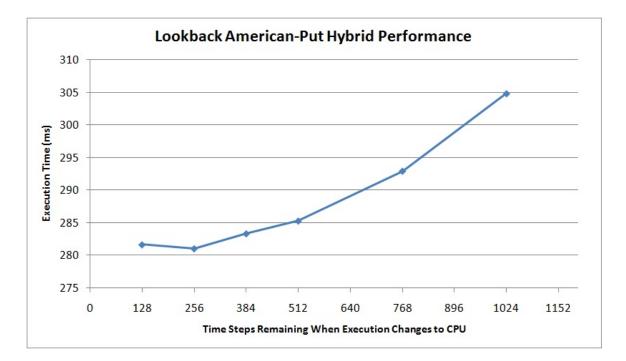

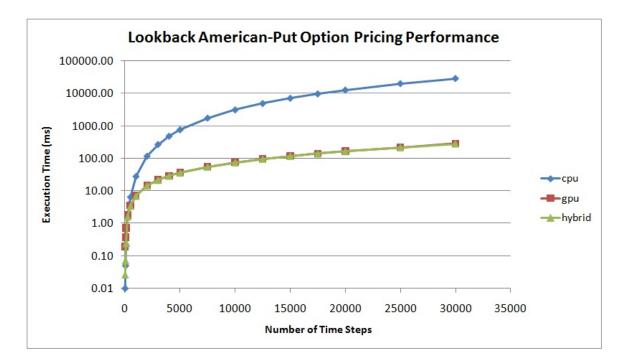

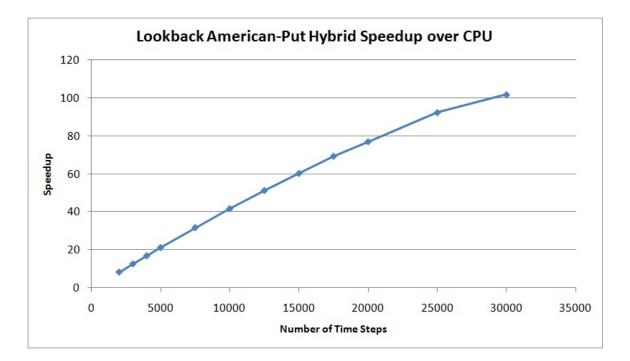

### 3.3.1 Hybrid Computations

Before closing this section, we want to bring attention back to the reduction in parallelism throughout the algorithm. Recall that each subsequent phase of the algorithm (covering a subsequent layer in the lattice) requires one less thread than the previous phase. With the GPU, we have an architecture that places a strong emphasis on parallel execution. Due to the structure of the lattice, we are reduced to throwing only a few threads at a time at the hardware by the close of the algorithm. In order to try to combat the reduction in performance this may imply, we investigated the potential of a hybrid algorithm that moves the computations over to the CPU when the number of threads required for an iteration has dipped below a certain threshold. The threshold value defines how few iterations must remain before switching to CPU computations. For example, a threshold value of 128 implies that when there are 128 iterations remaining (that is: 128 layers left to be processed in the lattice), we cease computations on the GPU and shift to the CPU.